1.本发明属于集成电路设计技术领域,尤其涉及一种抗单粒子翻转的掉电数据保持触发器电路。

背景技术:

2.太空辐射环境中高能粒子撞击所引发的单粒子翻转(seu)效应是造成宇航集成电路失效的主要因素之一。包括局部掉电技术在内的低功耗设计技术在集成电路设计领域被广泛使用,具有降低能耗、降低散热成本、增强可靠性等优势。局部掉电时需要将该区域内的重要数据或状态进行保存,防止数据丢失,便于后续查找和恢复。掉电数据保持触发器是实现局部掉电后存储相关数据,并在电路重新上电后将存储的数据输出的触发器电路。该电路在宇航应用过程中会面临严重的seu问题,造成存储的数据出错。

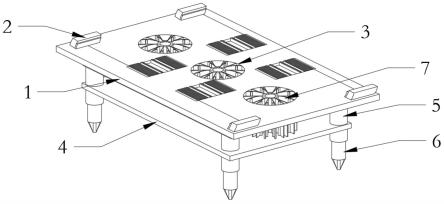

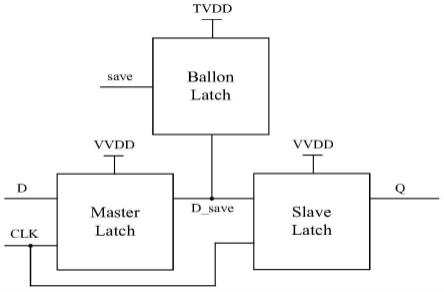

3.如图1,为一种常见的掉电数据保持触发器电路的原理示意图,该掉电数据保持触发器电路由主锁存器(master latch)、从锁存器(slave latch)和掉电贮存锁存器(balloon latch)构成。在空间环境中,master latch、slave latch和balloon latch均会受到单粒子的干扰,造成各锁存器存储的数据或状态发生改变。在正常工作模式下,master latch和slave latch会发生单粒子翻转导致掉电数据保持触发器输出错误结果,在掉电贮存模式下,balloon latch会发生单粒子翻转导致掉电过程中贮存的数据或状态出现错误,待再次上电后,掉电数据保持触发器会输出与掉电前存储的不一致的信息,造成整个电路无法复原。

4.可见,现有的掉电数据保持触发器电路对单粒子翻转效应非常敏感,当高能粒子轰击到master latch、slave latch或balloon latch的存储节点时,存储节点的数据或状态会发生从“0”到“1”或“1”到“0”的跳变,导致电路输出错误的数据。特别是掉电贮存锁存器在掉电后长期保持某种状态,该数据被单粒子“篡改”的概率更大,由于该数据涉及到上电后的初始化问题,后果也可能更严重。

5.如何避免掉电数据保持触发器存储的数据因单粒子事件出现错误,实现一种抗单粒子翻转效应的掉电数据保持触发器电路,是本领域技术人员亟待解决的技术问题之一。

技术实现要素:

6.本发明的技术解决问题:克服现有技术的不足,提供一种抗单粒子翻转的掉电数据保持触发器电路,旨在降低因单粒子翻转效应造成的电路正常工作和掉电保持状态下存储的数据和状态发生错误的概率,实现掉电数据保持触发器电路在低功耗宇航集成电路中的应用。

7.为了解决上述技术问题,本发明公开了一种抗单粒子翻转的掉电数据保持触发器电路,包括:

8.主锁存器电路,用于接收输入数据信号d和互补时钟信号的输入,根据互补时钟信号对输入数据信号d进行处理,输出第一数据信号d_save_1和第二数据信号d_save_2;

9.具备掉电贮存功能的从锁存器电路,用于接收第一数据信号d_save_1、第二数据信号d_save_2、互补时钟信号和互补贮存信号的输入,根据互补时钟信号和互补贮存信号分别对第一数据信号d_save_1和第二数据信号d_save_2进行处理,输出第一输出数据信号output1和第二输出数据信号output2;

10.输出驱动级缓冲器,用于接收第一输出数据信号output1或第二输出数据信号output2的输入;根据第一输出数据信号output1或第二输出数据信号output2,生成整个掉电数据保持触发器电路的总输出信号q;

11.第一反相器,用于生成并输出反相时钟信号ckn;其中,反相时钟信号ckn为时钟信号ck的反相信号,时钟信号ck和反相时钟信号ckn构成互补时钟信号;

12.第二反相器,用于生成并输出反相贮存使能信号saven;其中,反相贮存使能信号saven为贮存使能信号save的反相信号,贮存使能信号save和反相贮存使能信号saven构成互补贮存信号。

13.在上述抗单粒子翻转的掉电数据保持触发器电路中,

14.主锁存器电路,包括:两个c2mos单元和一个dice双互锁结构;其中,两个c2mos单元分别为:c2mos单元ⅰ和c2mos单元ⅱ;c2mos单元ⅰ和c2mos单元ⅱ并联设置,分别接dice双互锁结构;

15.具备掉电贮存功能的从锁存器电路,包括:两个带贮存开关的c2mos单元和一个带掉电贮存功能的dice双互锁结构;其中,两个带贮存开关的c2mos单元分别为:带贮存开关的c2mos单元ⅰ和带贮存开关的c2mos单元ⅱ;带贮存开关的c2mos单元ⅰ和带贮存开关的c2mos单元ⅱ并联设置,分别接带掉电贮存功能的dice双互锁结构。

16.在上述抗单粒子翻转的掉电数据保持触发器电路中,所述抗单粒子翻转的掉电数据保持触发器电路的工作原理如下:

17.当ck=0时,c2mos单元ⅰ输出输入数据信号d的第一反相信号dn1,c2mos单元ⅱ输出输入数据信号d的第二反相信号dn2,此时dice双互锁结构等效为两个反相器,dice双互锁结构输出两个与输入数据信号d同相的信号:第一数据信号d_save_1和第二数据信号d_save_2;当ck=1时,c2mos单元ⅰ和c2mos单元ⅱ阻断输入数据信号d向后级电路传播,此时dice双互锁结构存储当前状态,即d_save_1和d_save_2保持不变直至ck再次变为0后被新的输入数据信号改写;

18.dice双互锁结构输出的第一数据信号d_save_1和第二数据信号d_save_2分别传递至带贮存开关的c2mos单元ⅰ和带贮存开关的c2mos单元ⅱ;

19.当整个电路处于常规工作模式时,save=0,带贮存开关的c2mos单元ⅰ和带贮存开关的c2mos单元ⅱ等效为常规的c2mos单元,带掉电贮存功能的dice双互锁结构等效为常规的dice双互锁结构,在此前提下有:当ck=0时,带贮存开关的c2mos单元ⅰ和带贮存开关的c2mos单元ⅱ阻断第一数据信号d_save_1和第二数据信号d_save_2向后级电路传播,带掉电贮存功能的dice双互锁结构存储当前状态,即总输出信号q维持上一个状态;当ck=1时,带贮存开关的c2mos单元ⅰ输出第一数据信号d_save_1的反相信号d_save_1n,带贮存开关的c2mos单元ⅱ输出第二数据信号d_save_1的反相信号d_save_2n,带掉电贮存功能的dice双互锁结构等效为两个反相器,带掉电贮存功能的dice双互锁结构输出与第一数据信号d_save_1同相的第一输出数据信号output1、以及与第二数据信号d_save_2同相的第二输出

数据信号output2,即总输出信号q被改写为第一数据信号d_save_1或第二数据信号d_save_2。

20.在上述抗单粒子翻转的掉电数据保持触发器电路中,c2mos单元,包括:第一pmos管、第二pmos管、第二nmos管和第一nmos管;

21.第一pmos管的栅极接输入数据信号d,第一pmos管的源极接可关断电源vvdd,第一pmos管的漏极接第二pmos管的源极;

22.第二pmos管的栅极接c2mos单元的时钟输入端,第二pmos管的漏极接第二nmos管的漏极和c2mos单元的数据输出端;

23.第二nmos管的栅极接c2mos单元的反相时钟输入端,第二nmos管的源极接第一nmos管的漏极;

24.第一nmos管的栅极接输入数据信号d,第一nmos管的源极接地。

25.在上述抗单粒子翻转的掉电数据保持触发器电路中,dice双互锁结构,包括:第一支路、第二支路、第三支路和第四支路;其中,第一支路和第三支路为前向支路且互为备份,第二支路和第四支路为反馈支路且互为备份;

26.第一支路包括:第三pmos管和第三nmos管;其中,第三pmos管的栅极接dice双互锁结构的第一数据输入端,第三pmos管的源极接可关断电源vvdd,第三pmos管的漏极接第三nmos管的漏极及dice双互锁结构的第一数据输出端;第三nmos管的栅极接dice双互锁结构的第二数据输入端,第三nmos管的源极接地;

27.第二支路包括:第四pmos管、第五pmos管、第四nmos管和第五nmos管;其中,第四pmos管的栅极接dice双互锁结构的第一数据输出端,第四pmos管的源极接可关断电源vvdd,第四pmos管的漏极接第五pmos管的源极;第五pmos管的栅极接dice双互锁结构的反相时钟输入端,第五pmos管的漏极接第四nmos管的漏极及dice双互锁结构的第二数据输入端;第四nmos管的栅极接dice双互锁结构的时钟输入端,第四nmos管的源极接第五nmos管的漏极;第五nmos管的栅极接dice双互锁结构的第二数据输出端,第五nmos管的源极接地;

28.第三支路包括:第六pmos管和第六nmos管;其中,第六pmos管的栅极接dice双互锁结构的第二数据输入端,第六pmos管的源极接可关断电源vvdd,第六pmos管的漏极接第六nmos管漏极及dice双互锁结构的第二数据输出端;第六nmos管的栅极接dice双互锁结构的第一数据输入端,第六nmos管的源极接地;

29.第四支路包括:第七pmos管、第八pmos管、第七nmos管和第八nmos管;其中,第七pmos管的栅极接dice双互锁结构的第二数据输出端,第七pmos管的源极接可关断电源vvdd,第七pmos管的漏极接第八pmos管的源极;第八pmos管的栅极接dice双互锁结构的反相时钟输入端,第八pmos管的漏极接第七nmos管的漏极及dice双互锁结构的第一数据输入端;第七nmos管的栅极接dice双互锁结构的时钟输入端,第七nmos管的源极接第八nmos管的漏极;第八nmos管的栅极接dice双互锁结构的第一数据输出端,第八nmos管的源极接地。

30.在上述抗单粒子翻转的掉电数据保持触发器电路中,带贮存开关的c2mos单元,包括:第九pmos管、第十pmos管、第十一pmos管、第九nmos管、第十nmos管和第十一nmos管;

31.第九pmos管栅极接带贮存开关的c2mos单元的数据输入端,第九pmos管的源极接可关断电源vvdd,第九pmos管的漏极接第十pmos管的源极;

32.第十pmos管的栅极接带贮存开关的c2mos单元的反相时钟输入端,第十pmos管的

漏极接第十一pmos管的源极;

33.第十一pmos管的栅极接带贮存开关的c2mos单元的贮存使能输入端,第十一pmos管的漏极接第十一nmos管的漏极及带贮存开关的c2mos单元的数据输出端;

34.第十一nmos管的栅极接带贮存开关的c2mos单元的反相贮存使能输入端,第十一nmos管的源极接接第十nmos管的漏极;

35.第十nmos管的栅极接带贮存开关的c2mos单元的时钟输入端,第十nmos管的源极接第九nmos管的漏极;

36.第九nmos管的栅极接带贮存开关的c2mos单元的数据输入端,第九nmos管的源极接地。

37.在上述抗单粒子翻转的掉电数据保持触发器电路中,带掉电贮存功能的dice双互锁结构,包括:第五支路、第六支路、第七支路、第八支路、第九支路和第十支路;其中,第五支路和第八支路为前向支路且互为备份,第六支路和第九支路为反馈支路且互为备份,第七支路和第十支路为掉电贮存支路且互为备份;

38.第五支路包括:第十二pmos管和第十二nmos管;其中,第十二pmos管的栅极接带掉电贮存功能的dice双互锁结构的第一数据输入端,第十二pmos管的源极接恒通电源tvdd,第十二pmos管的漏极接第十二nmos管的漏极及带掉电贮存功能的dice双互锁结构的第一数据输出端;第十二nmos管的栅极接带掉电贮存功能的dice双互锁结构的第二数据输入端,第十二nmos管的源极接地;

39.第六支路包括:第十三pmos管、第十四pmos管、第十三nmos管和第十四nmos管;其中,第十三pmos管的栅极接带掉电贮存功能的dice双互锁结构的第一数据输出端,第十三pmos管的源极接可关断电源vvdd,第十三pmos管的漏极接第十四pmos管的源极;第十四pmos管的栅极接带掉电贮存功能的dice双互锁结构的时钟输入端,第十四pmos管的漏极接第十三nmos管的漏极及带掉电贮存功能的dice双互锁结构的第二数据输入端;第十三nmos管的栅极接带掉电贮存功能的dice双互锁结构的反相时钟输入端,第十三nmos管的源极接第十四nmos管的漏极;第十四nmos管的栅极接带掉电贮存功能的dice双互锁结构的第二数据输出端,第十四nmos管的源极接地;

40.第七支路包括:第十五pmos管、第十六pmos管、第十五nmos管和第十六nmos管;其中,第十五pmos管的栅极第十三pmos管的栅极,第十五pmos管的源极接恒通电源tvdd,第十五pmos管的漏极接第十六pmos管的源极;第十六pmos管的栅极接带掉电贮存功能的dice双互锁结构的反相贮存使能输入端,第十六pmos管的漏极、第十五nmos管的漏极、第十四pmos管的漏极、第十三nmos管的漏极连在一起;第十五nmos管的栅极接带掉电贮存功能的dice双互锁结构的贮存使能输入端,第十五nmos管的源极接第十六nmos管的漏极;第十六nmos管的栅极与第十四nmos管的栅极连接在一起,第十六nmos管的源极接地;

41.第八支路包括:第十七pmos管和第十七nmos管;其中,第十七pmos管的栅极接带掉电贮存功能的dice双互锁结构的第二数据输入端,第十七pmos管的源极接恒通电源tvdd,第十七pmos管的漏极接第十七nmos管的漏极及带掉电贮存功能的dice双互锁结构的第二数据输出端;第十七nmos管的栅极接带掉电贮存功能的dice双互锁结构的第一数据输入端,第十七nmos管的源极接地;

42.第九支路包括:第十八pmos管、第十九pmos管、第十八nmos管和第十九nmos管;其

中,第十八pmos管的栅极接带掉电贮存功能的dice双互锁结构的第二数据输出端,第十八pmos管的源极接可关断电源vvdd,第十八pmos管的漏极接第十九pmos管的源极;第十九pmos管的栅极接带掉电贮存功能的dice双互锁结构的时钟输入端,第十九pmos管的漏极接第十八nmos管的漏极及带掉电贮存功能的dice双互锁结构的第一数据输入端;第十八nmos管的栅极接带掉电贮存功能的dice双互锁结构的反相时钟输入端,第十八nmos管的源极接第十九nmos管的漏极;第十九nmos管的栅极接带掉电贮存功能的dice双互锁结构的第一数据输出端,第十九nmos管的源极接地;

43.第十支路包括:第二十pmos管、第二十一pmos管、第二十nmos管和第二十一nmos管;其中,第二十pmos管的栅极接带掉电贮存功能的dice双互锁结构的第二数据输出端,第二十pmos管的源极接恒通电源tvdd,第二十pmos管的漏极接第二十一pmos管的源极;第二十一pmos管的栅极接带掉电贮存功能的dice双互锁结构的反相贮存使能输入端,第二十一pmos管的漏极接第二十nmos管的漏极及带掉电贮存功能的dice双互锁结构的第一数据输入端;第二十nmos管的栅极接带掉电贮存功能的dice双互锁结构的贮存使能输入端,第二十nmos管的源极接第二十一nmos管的漏极;第二十一nmos管的栅极接接带掉电贮存功能的dice双互锁结构的第一数据输出端,第二十一nmos管的源极接地。

44.在上述抗单粒子翻转的掉电数据保持触发器电路中,输出驱动级缓冲器,包括:第三反相器和第四反相器;其中,第三反相器和第四反相器级联构成所述输出驱动级缓冲器;第三反相器的输入端即为所述输出驱动级缓冲器的输入端,第四反相器的输出端即为所述输出驱动级缓冲器的输出端;第三反相器和第四反相器的电源均为可关断电源vvdd。

45.在上述抗单粒子翻转的掉电数据保持触发器电路中,

46.第三反相器,包括:第二十二pmos管和第二十二nmos管;其中,第二十二pmos管的源极接可关断电源vvdd,第二十二pmos管的栅极接输出驱动级缓冲器的输入端,第二十二pmos管的漏极接第二十二nmos管的漏极及第二十三pmos管的栅极和第二十三nmos管的栅极;第二十二nmos管的栅极接输出驱动级缓冲器的输入端,第二十二nmos管的源极接地;

47.第四反相器,包括:第二十三pmos管和第二十三nmos管;其中,第二十三pmos管的源极接可关断电源vvdd,第二十三pmos管的漏极接第二十三nmos管的漏极及输出驱动级缓冲器的输出端;第二十三nmos管的源极接地。

48.在上述抗单粒子翻转的掉电数据保持触发器电路中,在逻辑上:d_save_1=d_save_2,output1=output2,dn1=dn2。

49.本发明具有以下优点:

50.(1)本发明公开了一种抗单粒子翻转的掉电数据保持触发器电路,针对掉电贮存锁存器结构进行抗单粒子翻转加固设计,实现了宇航集成电路在掉电等低功耗模式下数据和状态的可靠贮存。

51.(2)本发明公开了一种抗单粒子翻转的掉电数据保持触发器电路,将从锁存器和掉电贮存锁存器在一个具备掉电贮存功能的从锁存器电路中实现,带掉电贮存功能的dice双互锁结构中常规存储部分和掉电存储部分共用前向支路,反馈支路和掉电贮存支路连接前向支路相同节点,均与前向支路构成互锁结构,在正常工作模式下反馈支路起作用而掉电贮存支路断开,在掉电工作模式下掉电贮存支路起作用,反馈支路因断电失去作用,这种设计简化了电路结构,有效降低了面积和功耗等开销。

52.(3)本发明公开了一种抗单粒子翻转的掉电数据保持触发器电路,提出一种具备掉电贮存功能的从锁存器电路,该具备掉电贮存功能的从锁存器电路构成了两套dice双互锁结构,第五支路、第六支路、第八支路、第九支路构成一套正常工作模式下的dice双互锁结构,第五支路、第七支路、第八支路、第十支路构成一套掉电贮存模式下的dice双互锁结构,互为备份的两个支路中任意一个支路被高能粒子轰击时,其备份支路存储的正确信息会避免整个带掉电贮存功能的dice双互锁结构发生最终存储数据的翻转,利用带掉电贮存功能的dice双互锁结构抵抗单粒子翻转的特点实现正常工作模式和掉电贮存模式下均能降低单粒子翻转发生的概率。

53.(4)本发明公开了一种抗单粒子翻转的掉电数据保持触发器电路,提出一种带贮存开关的c2mos单元,正常工作模式下该带贮存开关的c2mos单元等效为一个常规的c2mos单元,掉电模式下该带贮存开关的c2mos单元能够阻止主锁存器等前级电路混乱的数据传递到带掉电贮存功能的dice双互锁结构。

附图说明

54.图1是一种常见的掉电数据保持触发器电路的原理示意图;

55.图2是本发明实施例中一种抗单粒子翻转的掉电数据保持触发器电路的电路示意图;

56.图3是本发明实施例中一种c2mos单元的电路示意图;

57.图4是本发明实施例中一种dice双互锁结构的电路示意图;

58.图5是本发明实施例中一种带贮存开关的c2mos单元的电路示意图;

59.图6是本发明实施例中一种带掉电贮存功能的dice双互锁结构的电路示意图;

60.图7是本发明实施例中一种输出驱动级缓冲器的电路示意图;

61.图8是本发明实施例中一种掉电数据保持触发器电路工作模式切换过程中各信号时序关系的示意图;

62.图9是本发明实施例中又一种一种掉电数据保持触发器电路工作模式切换过程中各信号时序关系的示意图。

具体实施方式

63.为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明公开的实施方式作进一步详细描述。

64.如图2,在本实施例中,该抗单粒子翻转的掉电数据保持触发器电路,其包括:主锁存器电路21、具备掉电贮存功能的从锁存器电路22、第一反相器23、第二反相器24和输出驱动级缓冲器25。具体的:

65.主锁存器电路21,用于接收输入数据信号d和互补时钟信号的输入,根据互补时钟信号对输入数据信号d进行处理,输出第一数据信号d_save_1和第二数据信号d_save_2。

66.具备掉电贮存功能的从锁存器电路22,用于接收第一数据信号d_save_1、第二数据信号d_save_2、互补时钟信号和互补贮存信号的输入,根据互补时钟信号和互补贮存信号分别对第一数据信号d_save_1和第二数据信号d_save_2进行处理,输出第一输出数据信号output1和第二输出数据信号output2。

67.输出驱动级缓冲器25,用于接收第一输出数据信号output1或第二输出数据信号output2的输入;根据第一输出数据信号output1或第二输出数据信号output2,生成整个掉电数据保持触发器电路的总输出信号q。

68.第一反相器23,用于生成并输出反相时钟信号ckn。其中,反相时钟信号ckn为时钟信号ck的反相信号,时钟信号ck和反相时钟信号ckn构成互补时钟信号。

69.第二反相器24,用于生成并输出反相贮存使能信号saven。其中,反相贮存使能信号saven为贮存使能信号save的反相信号,贮存使能信号save和反相贮存使能信号saven构成互补贮存信号。

70.在本实施例中,主锁存器电路21具体可以包括:两个c2mos单元和一个dice双互锁结构213。其中,两个c2mos单元分别为:c2mos单元ⅰ211和c2mos单元ⅱ212;c2mos单元ⅰ211和c2mos单元ⅱ212并联设置,分别接dice双互锁结构213。具备掉电贮存功能的从锁存器电路22具体可以包括:两个带贮存开关的c2mos单元和一个带掉电贮存功能的dice双互锁结构223。其中,两个带贮存开关的c2mos单元分别为:带贮存开关的c2mos单元ⅰ221和带贮存开关的c2mos单元ⅱ222;带贮存开关的c2mos单元ⅰ221和带贮存开关的c2mos单元ⅱ222并联设置,分别接带掉电贮存功能的dice双互锁结构223。

71.在本实施例中,该抗单粒子翻转的掉电数据保持触发器电路的工作原理如下:当ck=0时,c2mos单元ⅰ211输出输入数据信号d的第一反相信号dn1,c2mos单元ⅱ212输出输入数据信号d的第二反相信号dn2,此时dice双互锁结构213等效为两个反相器,dice双互锁结构213输出两个与输入数据信号d同相的信号:第一数据信号d_save_1和第二数据信号d_save_2;当ck=1时,c2mos单元ⅰ211和c2mos单元ⅱ212阻断输入数据信号d向后级电路传播,此时dice双互锁结构213存储当前状态,即d_save_1和d_save_2保持不变直至ck再次变为0后被新的输入数据信号改写。dice双互锁结构213输出的第一数据信号d_save_1和第二数据信号d_save_2分别传递至带贮存开关的c2mos单元ⅰ221和带贮存开关的c2mos单元ⅱ222。当整个电路处于常规工作模式时,save=0,带贮存开关的c2mos单元ⅰ221和带贮存开关的c2mos单元ⅱ222等效为常规的c2mos单元,带掉电贮存功能的dice双互锁结构223等效为常规的dice双互锁结构,在此前提下有:当ck=0时,带贮存开关的c2mos单元ⅰ221和带贮存开关的c2mos单元ⅱ222阻断第一数据信号d_save_1和第二数据信号d_save_2向后级电路传播,带掉电贮存功能的dice双互锁结构223存储当前状态,即总输出信号q维持上一个状态;当ck=1时,带贮存开关的c2mos单元ⅰ221输出第一数据信号d_save_1的反相信号d_save_1n,带贮存开关的c2mos单元ⅱ222输出第二数据信号d_save_1的反相信号d_save_2n,带掉电贮存功能的dice双互锁结构223等效为两个反相器,带掉电贮存功能的dice双互锁结构223输出与第一数据信号d_save_1同相的第一输出数据信号output1、以及与第二数据信号d_save_2同相的第二输出数据信号output2,即总输出信号q被改写为第一数据信号d_save_1或第二数据信号d_save_2。

72.在本实施例中,c2mos单元ⅰ211包括:一个数据输入端(用于接收输入数据信号d)、一个数据输出端(用于输出第一反相信号dn1)、一个时钟输入端(用于接收时钟信号ck)、一个反相时钟输入端(用于接收反相时钟信号ckn)。c2mos单元ⅱ212包括:一个数据输入端(用于接收输入数据信号d)、一个数据输出端(用于输出第二反相信号dn2)、一个时钟输入端(用于接收时钟信号ck)、一个反相时钟输入端(用于接收反相时钟信号ckn)。dice双互锁

结构213包括:第一数据输入端(用于接收第一反相信号dn1)、第二数据输入端(用于接收第二反相信号dn2)、第一数据输出端(用于输出第一数据信号d_save_1)、第二数据输出端(用于输出第二数据信号d_save_2),一个时钟输入端(用于接收时钟信号ck)、一个反相时钟输入端(用于接收反相时钟信号ckn)。带贮存开关的c2mos单元ⅰ221包括:一个数据输入端(用于接收第一数据信号d_save_1)、一个数据输出端(用于输出反相信号d_save_1n)、一个时钟输入端(用于接收时钟信号ck)、一个反相时钟输入端(用于接收反相时钟信号ckn)、一个贮存使能输入端(用于接收贮存使能信号save)、一个反相贮存使能输入端(用于接收反相贮存使能信号saven)。带贮存开关的c2mos单元ⅱ222包括:一个数据输入端(用于接收第二数据信号d_save_2)、一个数据输出端(用于输出反相信号d_save_2n)、一个时钟输入端(用于接收时钟信号ck)、一个反相时钟输入端(用于接收反相时钟信号ckn)、一个贮存使能输入端(用于接收贮存使能信号save)、一个反相贮存使能输入端(用于接收反相贮存使能信号saven)。带掉电贮存功能的dice双互锁结构223包括:第一数据输入端(用于接收反相信号d_save_1n)、第二数据输入端(用于接收反相信号d_save_2n)、第一数据输出端(用于输出第一输出数据信号output1)、第二数据输出端(用于输出第二输出数据信号output21)、一个时钟输入端(用于接收时钟信号ck)、一个反相时钟输入端(用于接收反相时钟信号ckn)、一个贮存使能输入端(用于接收贮存使能信号save)、一个反相贮存使能输入端(用于接收反相贮存使能信号saven)。第一反相器23包括:一个输入端(用于接收时钟信号ck)和一个输出端(用于输出反相时钟信号ckn)。第二反相器24包括:一个输入端(用于接收贮存使能信号save)和一个输出端(用于输出反相贮存使能信号saven)。输出驱动级缓冲器25包括:一个输入端(用于接收第一输出数据信号output1或第二输出数据信号output2)和一个输出端(用于输出总输出信号q)。

73.在本实施例中,如图3,c2mos单元具体可以包括:第一pmos管301、第二pmos管302、第二nmos管303和第一nmos管304。

74.第一pmos管301的栅极接输入数据信号d,第一pmos管301的源极接可关断电源vvdd,第一pmos管301的漏极接第二pmos管302的源极。第二pmos管302的栅极接c2mos单元的时钟输入端,第二pmos管302的漏极接第二nmos管303的漏极和c2mos单元的数据输出端。第二nmos管303的栅极接c2mos单元的反相时钟输入端,第二nmos管303的源极接第一nmos管304的漏极。第一nmos管304的栅极接输入数据信号d,第一nmos管304的源极接地。

75.优选的,c2mos单元的基本功能和信号传递关系如下:当ck=0时,c2mos单元的数据输出端输出所述输入数据信号d的第一反相信号dn1或第二反相信号dn2;当ck=1时,c2mos单元的数据输出端为高阻态,即输入数据信号d被阻断向后级电路传播。

76.在本实施例中,如图4,dice双互锁结构213具体可以包括:第一支路41、第二支路42、第三支路43和第四支路44;其中,第一支路41和第三支路43为前向支路且互为备份,第二支路42和第四支路44为反馈支路且互为备份。

77.第一支路41包括:第三pmos管411和第三nmos管412。其中,第三pmos管411的栅极接dice双互锁结构213的第一数据输入端,第三pmos管411的源极接可关断电源vvdd,第三pmos管411的漏极接第三nmos管412的漏极及dice双互锁结构213的第一数据输出端;第三nmos管412的栅极接dice双互锁结构213的第二数据输入端,第三nmos管412的源极接地。

78.第二支路42包括:第四pmos管421、第五pmos管422、第四nmos管423和第五nmos管

424。其中,第四pmos管421的栅极接dice双互锁结构213的第一数据输出端,第四pmos管421的源极接可关断电源vvdd,第四pmos管421的漏极接第五pmos管422的源极;第五pmos管422的栅极接dice双互锁结构213的反相时钟输入端,第五pmos管422的漏极接第四nmos管423的漏极及dice双互锁结构213的第二数据输入端;第四nmos管423的栅极接dice双互锁结构213的时钟输入端,第四nmos管423的源极接第五nmos管424的漏极;第五nmos管424的栅极接dice双互锁结构213的第二数据输出端,第五nmos管424的源极接地。

79.第三支路43包括:第六pmos管431和第六nmos管432。其中,第六pmos管431的栅极接dice双互锁结构213的第二数据输入端,第六pmos管431的源极接可关断电源vvdd,第六pmos管431的漏极接第六nmos管432漏极及dice双互锁结构213的第二数据输出端;第六nmos管432的栅极接dice双互锁结构213的第一数据输入端,第六nmos管432的源极接地。

80.第四支路44包括:第七pmos管441、第八pmos管442、第七nmos管443和第八nmos管444。其中,第七pmos管441的栅极接dice双互锁结构213的第二数据输出端,第七pmos管441的源极接可关断电源vvdd,第七pmos管441的漏极接第八pmos管442的源极;第八pmos管442的栅极接dice双互锁结构213的反相时钟输入端,第八pmos管442的漏极接第七nmos管443的漏极及dice双互锁结构213的第一数据输入端;第七nmos管443的栅极接dice双互锁结构213的时钟输入端,第七nmos管443的源极接第八nmos管444的漏极;第八nmos管444的栅极接dice双互锁结构213的第一数据输出端,第八nmos管444的源极接地。

81.优选的,dice双互锁结构(213)包括两个方面的功能:其一是作为锁存器的基本功能,其二是抗单粒子翻转的功能。作为锁存器的基本功能是:

82.当ck=0时,反馈支路(第二支路42和第四支路44)的输出端为高阻态,第一反相信号dn1和第二反相信号dn2通过前向支路(第一支路41和第三支路43)输出第一数据信号d_save_1和第二数据信号d_save_2(第一数据信号d_save_1为第一反相信号dn1的反相信号,二数据信号d_save_2为第二反相信号dn2的反相信号),即电路处于前向导通状态。

83.当ck=1时,反馈支路(第二支路42和第四支路44)导通,当dn1=dn2=0时,控制第三pmos管411和第六pmos管431将第一数据信号d_save_1和第二数据信号d_save_2上拉为1,第一数据信号d_save_1和第二数据信号d_save_2第八nmos管444和第五nmos管424将第一反相信号dn1和第二反相信号dn2下拉为0,整个锁存器将输入数据0锁定在0;同理,当dn1=dn2=1时,整个锁存器将输入数据1锁定在1,即电路处于锁存状态。抗单粒子翻转的功能主要考量的是电路处于锁存状态下受到高能粒子轰击时是否能避免发生存储状态翻转,而电路处于前向导通状态下时,由于电路输出始终被输入数据决定,所以高能粒子仅能导致短时间的瞬态变化,而不会导致存储状态发生改变。在dice双互锁结构处于锁存状态且dn1=dn2=0的情况下,当高能粒子轰击到第一支路41导致d_save_1被下拉到0时,第四pmos管421导通使dn2被上拉,但第三支路43的第六pmos管431和第四支路44的第八nmos管444均不导通,因此第三支路43和第四支路44存储的状态均未发生改变,即d_save_2仍为1,dn1仍为0,使得第一支路41的第三pmos管411仍开启使d_save_1上拉,第二支路42的第五nmos管424仍开启使dn2下拉,即与单粒子事件造成的状态改变趋势是竞争关系,阻碍状态改变,当单粒子事件结束后,d_save_1被下拉、dn2被上拉的趋势停止,在第三支路43和第四支路44的作用下,d_save_1和dn2恢复原状态,同理,高能粒子轰击到其他支路或者dn1=dn2=1的情况与以上描述类似,dice双互锁结构避免了单粒子翻转事件的发生。

84.在本实施例中,如图5,带贮存开关的c2mos单元具体可以包括:第九pmos管501、第十pmos管502、第十一pmos管503、第九nmos管506、第十nmos管505和第十一nmos管504。

85.第九pmos管501栅极接带贮存开关的c2mos单元的数据输入端,第九pmos管501的源极接可关断电源vvdd,第九pmos管501的漏极接第十pmos管502的源极。第十pmos管502的栅极接带贮存开关的c2mos单元的反相时钟输入端,第十pmos管502的漏极接第十一pmos管503的源极。第十一pmos管503的栅极接带贮存开关的c2mos单元的贮存使能输入端,第十一pmos管503的漏极接第十一nmos管504的漏极及带贮存开关的c2mos单元的数据输出端。第十一nmos管504的栅极接带贮存开关的c2mos单元的反相贮存使能输入端,第十一nmos管504的源极接接第十nmos管505的漏极。第十nmos管505的栅极接带贮存开关的c2mos单元的时钟输入端,第十nmos管505的源极接第九nmos管506的漏极。第九nmos管506的栅极接带贮存开关的c2mos单元的数据输入端,第九nmos管506的源极接地。

86.优选的,带贮存开关的c2mos单元的基本功能和信号传递关系如下:当save=0时,电路处于正常工作模式,在此模式下,当ck=0时,带贮存开关的c2mos单元的数据输出端处于高阻状态,即输入数据被阻断向后级电路传播,当ck=1时,d_saven为d_save的反相信号d_save_1或d_save_2;当save=1时,电路处于掉电工作模式带贮存开关的c2mos单元的数据输出端处于高阻状态,即前级电路的混乱状态被阻断向后级电路传播。

87.在本实施例中,如图6,带掉电贮存功能的dice双互锁结构223具体可以包括:第五支路61、第六支路62、第七支路63、第八支路64、第九支路65和第十支路66;其中,第五支路61和第八支路64为前向支路且互为备份,第六支路62和第九支路65为反馈支路且互为备份,第七支路63和第十支路66为掉电贮存支路且互为备份。

88.第五支路61包括:第十二pmos管611和第十二nmos管612。其中,第十二pmos管611的栅极接带掉电贮存功能的dice双互锁结构223的第一数据输入端,第十二pmos管611的源极接恒通电源tvdd,第十二pmos管611的漏极接第十二nmos管612的漏极及带掉电贮存功能的dice双互锁结构223的第一数据输出端;第十二nmos管612的栅极接带掉电贮存功能的dice双互锁结构223的第二数据输入端,第十二nmos管612的源极接地。

89.第六支路62包括:第十三pmos管621、第十四pmos管622、第十三nmos管623和第十四nmos管624。其中,第十三pmos管621的栅极接带掉电贮存功能的dice双互锁结构223的第一数据输出端,第十三pmos管621的源极接可关断电源vvdd,第十三pmos管621的漏极接第十四pmos管622的源极;第十四pmos管622的栅极接带掉电贮存功能的dice双互锁结构223的时钟输入端,第十四pmos管622的漏极接第十三nmos管623的漏极及带掉电贮存功能的dice双互锁结构223的第二数据输入端;第十三nmos管623的栅极接带掉电贮存功能的dice双互锁结构223的反相时钟输入端,第十三nmos管623的源极接第十四nmos管624的漏极;第十四nmos管624的栅极接带掉电贮存功能的dice双互锁结构223的第二数据输出端,第十四nmos管624的源极接地。

90.第七支路63包括:第十五pmos管631、第十六pmos管632、第十五nmos管633和第十六nmos管634。其中,第十五pmos管631的栅极第十三pmos管621的栅极,第十五pmos管631的源极接恒通电源tvdd,第十五pmos管631的漏极接第十六pmos管632的源极;第十六pmos管632的栅极接带掉电贮存功能的dice双互锁结构223的反相贮存使能输入端,第十六pmos管632的漏极、第十五nmos管633的漏极、第十四pmos管622的漏极、第十三nmos管623的漏极连

在一起;第十五nmos管633的栅极接带掉电贮存功能的dice双互锁结构223的贮存使能输入端,第十五nmos管633的源极接第十六nmos管634的漏极;第十六nmos管634的栅极与第十四nmos管624的栅极连接在一起,第十六nmos管634的源极接地。

91.第八支路64包括:第十七pmos管641和第十七nmos管642。其中,第十七pmos管641的栅极接带掉电贮存功能的dice双互锁结构223的第二数据输入端,第十七pmos管641的源极接恒通电源tvdd,第十七pmos管641的漏极接第十七nmos管642的漏极及带掉电贮存功能的dice双互锁结构223的第二数据输出端;第十七nmos管642的栅极接带掉电贮存功能的dice双互锁结构223的第一数据输入端,第十七nmos管642的源极接地。

92.第九支路65包括:第十八pmos管651、第十九pmos管652、第十八nmos管653和第十九nmos管654。其中,第十八pmos管651的栅极接带掉电贮存功能的dice双互锁结构223的第二数据输出端,第十八pmos管651的源极接可关断电源vvdd,第十八pmos管651的漏极接第十九pmos管652的源极;第十九pmos管652的栅极接带掉电贮存功能的dice双互锁结构223的时钟输入端,第十九pmos管652的漏极接第十八nmos管653的漏极及带掉电贮存功能的dice双互锁结构223的第一数据输入端;第十八nmos管653的栅极接带掉电贮存功能的dice双互锁结构223的反相时钟输入端,第十八nmos管653的源极接第十九nmos管654的漏极;第十九nmos管654的栅极接带掉电贮存功能的dice双互锁结构223的第一数据输出端,第十九nmos管654的源极接地。

93.第十支路66包括:第二十pmos管661、第二十一pmos管662、第二十nmos管663和第二十一nmos管664。其中,第二十pmos管661的栅极接带掉电贮存功能的dice双互锁结构223的第二数据输出端,第二十pmos管661的源极接恒通电源tvdd,第二十pmos管661的漏极接第二十一pmos管662的源极;第二十一pmos管662的栅极接带掉电贮存功能的dice双互锁结构223的反相贮存使能输入端,第二十一pmos管662的漏极接第二十nmos管663的漏极及带掉电贮存功能的dice双互锁结构223的第一数据输入端;第二十nmos管663的栅极接带掉电贮存功能的dice双互锁结构223的贮存使能输入端,第二十nmos管663的源极接第二十一nmos管664的漏极;第二十一nmos管664的栅极接接带掉电贮存功能的dice双互锁结构223的第一数据输出端,第二十一nmos管664的源极接地。

94.优选的,带掉电贮存功能的dice双互锁结构223的工作模式包括常规模式和掉电贮存模式。其中,常规模式下,save=0,且vvdd正常供电,此时第七支路63和第十支路66输出高阻态,带掉电贮存功能的dice双互锁结构223等效为常规的dice双互锁结构,其工作机理与主锁存器电路21中的dice双互锁结构213类似,区别在于当ck=0时电路处于锁存状态,而当ck=1时电路处于前向导通状态。常规模式下、且电路处于锁存状态时,高能粒子轰击到第五支路61、第六支路62、第八支路64、第九支路65的任一支路时,单粒子响应机理与常规的dice双互锁结构一致,高能粒子轰击到第五支路61或第十支路66时,由于其输出节点与第六支路62和第九支路65连接到一起,其单粒子响应机理与高能粒子轰击到第六支路62或第九支路65一致,仍然能够被第五支路61和第八支路64纠正;常规模式下且电路处于前向导通状态下时,由于电路输出始终被输入数据决定,所以高能粒子仅能导致短时间的瞬态变化,而不会导致存储状态发生改变。掉电模式时,vvdd掉电,tvdd恒通,save=1,此时第六支路62和第九支路65掉电不再工作,电路等效为由第五支路61、第七支路63、第八支路64、第九支路65构成的dice双互锁结构并处于锁存状态,基于同样的机理,在掉电模式下发

生单粒子事件时,电路能够阻止发生单粒子翻转。

95.在本实施例中,如图7,输出驱动级缓冲器25具体可以包括:第三反相器71和第四反相器72。其中,第三反相器71和第四反相器72级联构成所述输出驱动级缓冲器25;第三反相器71的输入端即为所述输出驱动级缓冲器25的输入端,第四反相器72的输出端即为所述输出驱动级缓冲器25的输出端;第三反相器71和第四反相器72的电源均为可关断电源vvdd。

96.进一步的,第三反相器71具体可以包括:第二十二pmos管711和第二十二nmos管712。其中,第二十二pmos管711的源极接可关断电源vvdd,第二十二pmos管711的栅极接输出驱动级缓冲器25的输入端,第二十二pmos管711的漏极接第二十二nmos管712的漏极及第二十三pmos管721的栅极和第二十三nmos管722的栅极;第二十二nmos管712的栅极接输出驱动级缓冲器25的输入端,第二十二nmos管712的源极接地。第四反相器72具体可以包括:第二十三pmos管721和第二十三nmos管722;其中,第二十三pmos管721的源极接可关断电源vvdd,第二十三pmos管721的漏极接第二十三nmos管722的漏极及输出驱动级缓冲器25的输出端;第二十三nmos管722的源极接地。

97.在本实施例中,在逻辑上:d_save_1=d_save_2,output1=output2,dn1=dn2。

98.综上所述,本发明所述的一种抗单粒子翻转的掉电数据保持触发器电路包括两种工作模式:正常工作模式和掉电贮存模式。两种工作模式能够自由切换:(1)save有效(即save由0变为1),此时带掉电贮存功能的dice双互锁结构内部将当前存储的状态进行备份;(2)vvdd掉电,tvdd保持恒通,此时仅有带掉电贮存功能的dice双互锁结构中的第五支路、第七支路、第八支路、第十支路存储掉电前的状态,其余电路均掉电失去功能,进行休眠;(3)vvdd再次上电,所有电路均被唤醒,整个触发器输出掉电时贮存的状态;(4)时钟信号ck为低电平,此时带掉电贮存功能的dice双互锁结构中的第六支路、第九支路导通并复制第七支路和第十支路存储的状态;(5)save失效(即save由1变为0),此时整个电路恢复为正常工作模式;(6)时钟信号ck上升沿来临(即从低电平变为高电平),整个触发器输出新的数据。

99.在本实施例中,两种工作模式在切换过程中各信号时序关系有如下两种情况:其一,save的上升沿早于时钟信号ck的上升沿,这种情况的时序关系如图8所示,在ck=0且save=0时,具备掉电贮存功能的从锁存器电路处于锁存状态,此时输出记为qn;当save=1且ck=0时,带贮存开关的c2mos单元关闭,带掉电贮存功能的dice双互锁结构中的第五支路、第七支路、第八支路、第十支路形成一个常规的dice双互锁结构,对qn进行存储,此时输出仍为qn;当save=1且ck=1时,由于带贮存开关的c2mos单元已经关闭,所以整个电路的输出仍为qn,电源vvdd掉电后,输出处于不定态,电源恢复后输出掉电贮存的状态qn。其二,save的上升沿晚于时钟信号ck的上升沿,这种情况的时序关系如图9所示,在ck=0且save=0时,具备掉电贮存功能的从锁存器电路处于锁存状态,此时输出记为qn;当save=0且ck=1时,具备掉电贮存功能的从锁存器电路处于前向导通状态,将新的输入数据输出,记为qn 1;当save=1且ck=1时,带贮存开关的c2mos单元关闭,带掉电贮存功能的dice双互锁结构中的第五支路、第七支路、第八支路、第十支路形成一个常规的dice双互锁结构,对qn 1进行存储,此时输出为qn 1;电源vvdd掉电后,输出处于不定态,电源恢复后输出掉电贮存的状态qn 1。

100.本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

101.本发明说明书中未作详细描述的内容属于本领域专业技术人员的公知技术。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。