经边缘凹槽、虚拟枢轴和自由边界提高mut耦合效率和带宽

交叉引用

1.本专利申请要求2019年9月12日提交的美国临时申请第62/899,602号的权益,该申请通过引用整体并入本文。

背景技术:

2.微加工超声换能器(mut)是在电域和声域之间转换能量的器件。它们通常有两种类型:电容mut(cmut)和压电mut(pmut)。cmut利用两个板之间的电容来进行机电换能,而pmut利用压电薄膜的压电特性来实现机电换能。

技术实现要素:

3.在图1a至图1b和图2a至图2d中相应地图示了常规圆形隔膜pmut和cmut的示例。隔膜101由衬底100形成。在pmut的情况下,由底部电极200、压电层201和顶部电极202组成的压电叠堆放置在电介质层102顶部的隔膜101上或附近。在cmut的情况下,衬底附接到处理衬底103的顶部上的电介质层102。假设隔膜101是导电的,并且第二底部电极200放置在隔膜下面以形成101和200之间的电容器。

4.尽管有许多指标描述mut,但是其中两个最重要的指标是mut的有效机电耦合k

eff2

及其电品质因数qe和机械品质因数qm。器件的k

eff2

决定了其将电能转化为声能的效率。因此,k

eff2

是使用该mut的产品的功率规格的关键驱动因素。k

eff2

通常在0和1之间变化,其中1更好。机械品质因数和电品质因数驱动换能器的带宽,其是换能器在其上最有效的频率。对于大多数应用,尤其是成像,带宽越大越好,这意味着品质因数越低越好。

5.有利地,机电耦合和品质因数是相关的:[1]这意味着最大化k

eff2

将最大化换能效率以及最小化系统的品质因数两者。

[0006]

尽管有多种方式来影响k

eff2

,但是本公开将关注于mut隔膜的夹紧条件。根据[2],对于以第n个轴线对称模式振荡的圆形pmut,具有:[2]其中k

312

是材料的耦合系数(材料常数),λ

0n

是第n模式的固有频率参数(高度依赖于边缘夹紧条件),j0是第一类0阶贝塞尔函数,以及cn是依赖于特定pmut设计的常数(电极耦合常数、抗弯刚度和电极面积与隔膜面积的比率;完整公式见[2])。对于给定的k

312

耦合系数和设计常数cn、k

eff,n2

,可以通过将λ

0n

驱向0来实现最大化。

[0007]

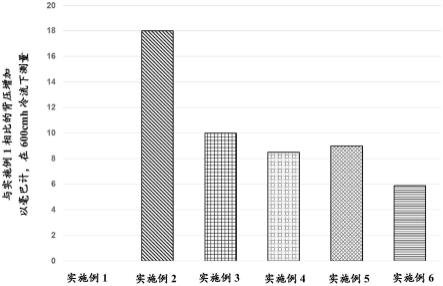

如图3的对比柱状图所示,固有频率参数高度依赖于所考虑的边界条件。常规的mut设计利用夹紧的边缘。图3中的“自由边缘”相当于理想的活塞运动,并且表示最佳耦合。在这两个极端之间,多个边缘条件有利于改善机电耦合和带宽。

[0008]

尽管有多个因素影响k

eff2

,但是直观上,增加的耦合因数可以与归一化体积位移

相关联。例如,图4的比较曲线图图示了三种标准圆形隔膜mut的归一化位移曲线:夹紧的边缘(类似于图1a至图1b和图2a至图2d);简单支撑的边缘(即,允许旋转但是不允许位移的边缘);以及自由边缘夹紧的中心。对表面积的位移进行积分,可以计算出每个mut相对于理想活塞的位移体积:

[0009]

夹紧的边缘=活塞位移体积的31%。

[0010]

简单支撑边缘mut=活塞位移体积的45%。

[0011]

自由边缘,夹紧的中心mut=活塞位移体积的54%。

[0012]

更高的位移体积指示更好的耦合。

[0013]

在一个方面,本文公开了一种微加工超声换能器(mut),其包括:具有基本上自由边缘的隔膜;一个或多个电极;以及一个或多个锚,其在隔膜周边内、沿着隔膜周边、或在隔膜周边内和沿着隔膜周边的位置将隔膜夹紧到衬底。隔膜、一个或多个电极以及一个或多个锚可以具有任何形状。在一些实施方式中,边缘是自由的,并且锚完全位于隔膜内。在一些实施方式中,mut是包括压电薄膜的pmut。在其他实施方式中,一个或多个电极电耦合到压电薄膜。在其他实施方式中,压电薄膜位于一个或多个锚的对面。在其他实施方式中,压电薄膜与一个或多个锚位于同一侧。在一些实施方式中,压电薄膜位于一个或多个锚和隔膜之间。在一些实施方式中,隔膜包括凹槽。在一些实施方式中,mut包括多个锚,其中多个锚的子集附接到一个或多个竖直悬臂外壳。在一些实施方式中,mut包括多个锚,其中多个锚的子集附接到一个或多个竖直悬臂外壳,并且其中隔膜包括凹槽。在一些实施方式中,mut是cmut。在其他实施方式中,一个或多个电极电耦合到间隙之间的隔膜。在其他实施方式中,隔膜包括凹槽。在此外其他的实施方式中,mut包括多个锚,其中多个锚的子集附接到一个或多个竖直悬臂外壳。在此外其他的实施方式中,mut包括多个锚,其中多个锚的子集附接到一个或多个竖直悬臂外壳,并且其中隔膜包括凹槽。

[0014]

在另一方面,本文公开了一种微加工超声换能器(mut),其包括夹紧的隔膜,该夹紧的隔膜包括竖直悬臂外壳,该竖直悬臂外壳附接到隔膜的边缘。隔膜可以具有任何形状。在一些实施方式中,竖直悬臂外壳形成虚拟枢轴,该虚拟枢轴基本上防止平面外运动,但是允许隔膜边缘旋转,同时施加反扭矩。在各种实施方式中,该竖直悬臂外壳的厚度在0.1μm和50μm之间,并且其中该竖直悬臂外壳具有比其厚度大1倍至100倍的高度。在此外其他的实施方式中,竖直悬臂外壳在隔膜边缘周围不是连续的,而是具有没有虚拟枢轴的区域。在此外其他的实施方式中,mut是多模态的。

[0015]

在另一方面,本文公开了一种微加工超声换能器(mut),其包括夹紧的隔膜,该夹紧的隔膜包括凹槽。夹紧的隔膜可以具有任何形状。在一些实施方式中,mut是pmut。在各种实施方式中,凹槽在隔膜边界的20个隔膜厚度内,并且其中凹槽具有不大于10个隔膜厚度的宽度,并且其中凹槽具有在隔膜厚度的1%到100%之间的深度。在一些实施方式中,凹槽具有恒定的宽度。在其他实施方式中,凹槽具有可变宽度。在一些实施方式中,凹槽在一个或多个位置处被中断,以允许电布线。在一些实施方式中,mut是多模态的。在一些实施方式中,mut是cmut。在各种实施方式中,凹槽在隔膜边界的20个隔膜厚度内,并且其中凹槽具有不大于10个隔膜厚度的宽度,并且其中凹槽具有在隔膜厚度的1%到100%之间的深度。在一些实施方式中,凹槽具有恒定的宽度。在其他实施方式中,凹槽具有可变宽度。在一些实施方式中,凹槽在一个或多个位置处被中断,以允许电布线。在一些实施方式中,mut是多模

态的。

[0016]

在又一方面,本文公开了mut阵列,其被配置为用于超声成像,其中该阵列包括本文所描述的多个mut。在一些实施方式中,多个mut中的每个mut是pmut。在其他实施方式中,多个mut中的每个mut是cmut。在一些实施方式中,多个mut中的每个mut包括由多个蚀刻形成的竖直悬臂外壳。

[0017]

在又一方面,本文公开了制造本文所描述的mut和mut阵列的方法。

[0018]

在一个方面,本文公开了一种微加工超声换能器(mut),其包括:压电叠堆,其包括衬底、绝缘层、顶部电极、压电层和底部电极,其中压电叠堆具有边缘部分和中心部分,其中压电叠堆具有一个或多个凹槽,该一个或多个凹槽延伸穿过至少顶部电极、压电层、底部电极和绝缘层并且进入衬底的至少一部分,并且其中该一个或多个凹槽设置在压电叠堆的边缘部分和中心部分之间;基部;一个或多个锚,其将压电叠堆的中心部分耦合到基部,留下压电叠堆的边缘部分自由,并且压电叠堆的中心部分被夹紧到基部,一个或多个锚在基部和压电叠堆之间提供电耦合;以及多个导体,所述多个导体包括(i)第一导体,其通过穿过压电叠堆的厚度的第一通孔将压电叠堆的顶部电极电耦合到基部,以及(ii)第二导体,其通过穿过压电叠堆的厚度的第二通孔将压电叠堆的底部电极电耦合到基部,其中第一通孔和第二通孔设置在压电叠堆的边缘部分和中心部分之间。

附图说明

[0019]

将通过参考以下阐述了说明性实施方式和附图的详细描述来获得对本主题的特征和优点的更好地理解,在附图中:

[0020]

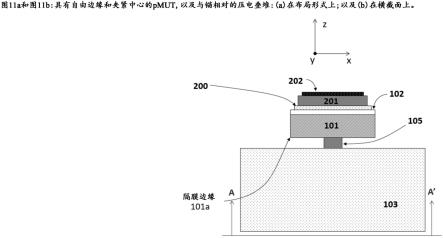

图1a和图1b相应地以以下方式示出了常规的圆形隔膜pmut:(a)在布局形式上;以及(b)在横截面上。

[0021]

图2a和图2b相应地以以下方式示出了常规的圆形隔膜cmut:(a)在布局形式上;以及(b)在横截面上。

[0022]

图2c和图2d相应地以以下方式示出了用在处理衬底顶部的导电部分代替图2a和图2b的cmut中的底部电极的常规的圆形隔膜cmut:(c)在布局形式上;以及(d)在横截面上。

[0023]

图3是示出了作为边界条件函数的基本模式的固有频率参数λ

01

的柱状图。由[2]根据[1]进行解释。蓝色指示最常见的mut边缘条件:已夹紧。红色指示[2]假设“物理上可实现”的边界条件。

[0024]

图4示出了半径为a的圆形隔膜在不同边缘条件下的归一化位移曲线图。

[0025]

图5a和图5b相应地以以下方式示出了具有顶侧凹槽的示例性圆形隔膜pmut:(a)在布局形式上;以及(b)在横截面上。

[0026]

图5c和图5d相应地以以下方式示出了具有顶侧凹槽并且使用绝缘体上硅(soi)晶片(包括在器件层和处理层之间的掩埋氧化物层)的示例性圆形隔膜pmut:(c)在布局形式上;以及(d)在横截面上。

[0027]

图6a和图6b相应地以以下方式示出了具有顶侧凹槽的示例性圆形隔膜cmut:(a)在布局形式上;以及(b)在横截面上。

[0028]

图6c和图6d相应地以以下方式示出了具有凹槽并且用在处理衬底顶部的导电部分代替图6a和图6b的cmut中的底部电极的示例性圆形隔膜cmut:(c)在布局形式上;以及

(d)在横截面上。

[0029]

图7a和图7b相应地以以下方式示出了具有顶侧虚拟枢轴蚀刻的示例性圆形隔膜pmut:(a)在布局形式上;以及(b)在横截面上。

[0030]

图7c和图7d相应地以以下方式示出了具有顶侧虚拟枢轴蚀刻并且使用绝缘体上硅(soi)晶片(包括在器件层和处理层之间的掩埋氧化物层)的示例性圆形隔膜pmut:(c)在布局形式上;以及(d)在横截面上。

[0031]

图8a和图8b相应地以以下方式示出了具有顶侧虚拟枢轴蚀刻的示例性圆形隔膜cmut:(a)在布局形式上;以及(b)在横截面上。

[0032]

图8c和图8d相应地以以下方式示出了具有顶侧虚拟枢轴蚀刻并且用在处理衬底顶部的导电部分代替图8a和图8b的cmut中的底部电极的示例性圆形隔膜cmut:(c)在布局形式上;以及(d)在横截面上。

[0033]

图9a至图9d相应地以以下方式示出了边缘凹槽的示例性变化:(a)任意隔膜形状;(b)多个凹槽;(c)可变宽度的凹槽;以及(d)没有凹槽的选择区域。为简单起见,仅示出了隔膜边缘(虚线)和凹槽(实线)。

[0034]

图10a至图10d相应地以以下方式示出了虚拟枢轴的示例性变化:(a)任意隔膜形状;(b)多个虚拟枢轴沟槽;(c)可变宽度的虚拟枢轴沟槽;以及(d)没有虚拟枢轴沟槽的选择区域。为简单起见,仅示出了隔膜边缘(虚线)以及第一虚拟枢轴蚀刻和第二虚拟枢轴蚀刻(实线,相应地为黑色和灰色)。

[0035]

图11a和图11b相应地以以下方式示出了具有自由边缘和夹紧中心的示例性pmut,以及与锚相对的压电叠堆:(a)在布局形式上;以及(b)在横截面上。

[0036]

图12a和图12b相应地以以下方式示出了具有自由边缘和夹紧中心的示例性pmut,以及与锚同一侧的压电叠堆:(a)在布局形式上;以及(b)在横截面上。

[0037]

图13a和图13b相应地以以下方式示出了具有自由边缘和夹紧中心的示例性cmut,以及位于衬底和隔膜之间的相对电极(在此示例实施方式中假设其是导电的):(a)在布局形式上;以及(b)在横截面上。

[0038]

图14a至图14d示出了具有固定内部区域和/或固定边缘区域的自由边缘的示例性变化:(a)任意隔膜形状;(b)多个锚区域;(c)具有任意形状的多个锚区域;以及(d)具有固定边缘的选择区域,其中锚相应地与边缘重叠。为简单起见,仅示出了隔膜101和锚(虚线为深灰色内部)。

[0039]

图15a和图15b相应地以以下方式示出了具有边缘凹槽和虚拟枢轴蚀刻两者的示例性圆形隔膜pmut:(a)在布局形式上;以及(b)在横截面上。

[0040]

图15c和图15d相应地以以下方式示出了具有边缘凹槽和虚拟枢轴蚀刻两者并且使用绝缘体上硅(soi)晶片(包括在器件层和处理层之间的掩埋氧化物层)的示例性圆形隔膜pmut:(c)在布局形式上;以及(d)在横截面上。

[0041]

图16a和图16b相应地以以下方式示出了具有边缘凹槽和虚拟枢轴蚀刻两者的示例性圆形隔膜cmut:(a)在布局形式上;以及(b)在横截面上(边缘凹槽300是米色的,而虚拟枢轴蚀刻301b是灰色的)。

[0042]

图16c和图16d相应地以以下方式示出了具有边缘凹槽和虚拟枢轴蚀刻两者并且用在处理衬底顶部的导电部分代替图16a和图16b的cmut中的底部电极的示例性圆形隔膜

cmut:(c)在布局形式上;以及(d)在横截面上(边缘凹槽300是米色的,而虚拟枢轴蚀刻301b是灰色的)。

[0043]

图16e和图16f相应地以以下方式示出了具有边缘凹槽和虚拟枢轴蚀刻两者并且具有在处理部中形成的限定隔膜的间隙的示例性圆形隔膜cmut:(e)在布局形式上;以及(f)在横截面上(边缘凹槽300是米色的,而虚拟枢轴蚀刻301b是灰色的)。

[0044]

图16g和图16h相应地以以下方式示出了具有边缘凹槽和虚拟枢轴蚀刻两者并且具有在处理部中形成的限定隔膜的间隙的示例性圆形隔膜cmut:(g)在布局形式上;以及(h)在横截面上(边缘凹槽300是米色的,而虚拟枢轴蚀刻301b是灰色的)。

[0045]

图17a和图17b相应地以以下方式示出了具有自由边缘和夹紧中心的示例性pmut,以及与锚相对的压电叠堆:(a)在布局形式上;以及(b)在横截面上(为了清楚起见,在布局形式中没有示出虚拟枢轴蚀刻301b)。

[0046]

图18a和图18b相应地以以下方式示出了具有自由边缘和夹紧中心的示例性pmut,以及与锚同一侧的压电叠堆:(a)在布局形式上;以及(b)在横截面上(为了清楚起见,在布局形式中没有示出虚拟枢轴蚀刻301b)。

[0047]

图19a和图19b相应地以以下方式示出了具有自由边缘和夹紧中心的示例性cmut,以及位于衬底和隔膜之间的相对电极(在此示例实施方式中假设其是导电的):(a)在布局形式上;以及(b)在横截面上(为了清楚起见,在布局形式中没有示出虚拟枢轴蚀刻301b)。

[0048]

图20a和图20b以以下方式示出了具有自由边缘和夹紧中心的示例性pmut,该pmut具有并排的两个独立电极以及再分配层,以与压电叠堆的顶部和底部电极接触:(a)在布局形式上;以及(b)在横截面上。

具体实施方式

[0049]

在一些实施方式中,本文公开了一种微加工超声换能器(mut),其包括:具有基本上自由边缘的隔膜;一个或多个电极;以及一个或多个锚,其在隔膜周边内、沿着隔膜周边、或在隔膜周边内和沿着隔膜周边的位置将隔膜夹紧到衬底。隔膜、一个或多个电极以及一个或多个锚可以具有任何形状。在一些实施方式中,边缘是自由的,并且锚完全位于隔膜内。在一些实施方式中,mut是包括压电薄膜的pmut。在其他实施方式中,一个或多个电极电耦合到压电薄膜。在其他实施方式中,压电薄膜位于一个或多个锚的对面。在其他实施方式中,压电薄膜与一个或多个锚位于同一侧。在一些实施方式中,压电薄膜位于一个或多个锚和隔膜之间。在一些实施方式中,隔膜包括凹槽。在一些实施方式中,mut包括多个锚,其中多个锚的子集附接到一个或多个竖直悬臂外壳。在一些实施方式中,mut包括多个锚,其中多个锚的子集附接到一个或多个竖直悬臂外壳,并且其中隔膜包括凹槽。在一些实施方式中,mut是cmut。在其他实施方式中,一个或多个电极电耦合到间隙之间的隔膜。在其他实施方式中,隔膜包括凹槽。在此外其他的实施方式中,mut包括多个锚,其中多个锚的子集附接到一个或多个竖直悬臂外壳。在此外其他的实施方式中,mut包括多个锚,其中多个锚的子集附接到一个或多个竖直悬臂外壳,并且其中隔膜包括凹槽。

[0050]

在一些实施方式中,本文公开了一种微加工超声换能器(mut),其包括夹紧的隔膜,该夹紧的隔膜包括竖直悬臂外壳,该竖直悬臂外壳附接到隔膜的边缘。隔膜可以具有任何形状。在一些实施方式中,竖直悬臂外壳形成虚拟枢轴,该虚拟枢轴基本上防止平面外运

动,但是允许隔膜边缘旋转,同时施加反扭矩。在各种实施方式中,该竖直悬臂外壳的厚度在0.1μm和50μm之间,并且其中该竖直悬臂外壳具有比其厚度大1倍至100倍的高度。在此外其他的实施方式中,竖直悬臂外壳在隔膜边缘周围不是连续的,而是具有没有虚拟枢轴的区域。在此外其他的实施方式中,mut是多模态的。

[0051]

在一些实施方式中,本文公开了一种微加工超声换能器(mut),其包括夹紧的隔膜,该夹紧的隔膜包括凹槽。夹紧的隔膜可以具有任何形状。在一些实施方式中,mut是pmut。在各种实施方式中,凹槽在隔膜边界的20个隔膜厚度内,并且其中凹槽具有不大于10个隔膜厚度的宽度,并且其中凹槽具有在隔膜厚度的1%到100%之间的深度。在一些实施方式中,凹槽具有恒定的宽度。在其他实施方式中,凹槽具有可变宽度。在一些实施方式中,凹槽在一个或多个位置处被中断,以允许电布线。在一些实施方式中,mut是多模态的。在一些实施方式中,mut是cmut。在各种实施方式中,凹槽在隔膜边界的20个隔膜厚度内,并且其中凹槽具有不大于10个隔膜厚度的宽度,并且其中凹槽具有在隔膜厚度的1%到100%之间的深度。在一些实施方式中,凹槽具有恒定的宽度。在其他实施方式中,凹槽具有可变宽度。在一些实施方式中,凹槽在一个或多个位置处被中断,以允许电布线。在一些实施方式中,mut是多模态的。

[0052]

在各种实施方式中,本文公开了mut阵列,其被配置为用于超声成像,其中该阵列包括本文所描述的多个mut。在一些实施方式中,多个mut中的每个mut是pmut。在其他实施方式中,多个mut中的每个mut是cmut。在一些实施方式中,多个mut中的每个mut包括由多个蚀刻形成的竖直悬臂外壳。

[0053]

在各种实施方式中,本文公开了制造本文所描述的mut和mut阵列的方法。

[0054]

在特定实施方式中,本文公开了一种微加工超声换能器(mut),其包括:压电叠堆,其包括衬底、绝缘层、顶部电极、压电层和底部电极,其中压电叠堆具有边缘部分和中心部分,其中压电叠堆具有一个或多个凹槽,该一个或多个凹槽延伸穿过至少顶部电极、压电层、底部电极和绝缘层并且进入衬底的至少一部分,并且其中该一个或多个凹槽设置在压电叠堆的边缘部分和中心部分之间;基部;一个或多个锚,其将压电叠堆的中心部分耦合到基部,留下压电叠堆的边缘部分自由,并且压电叠堆的中心部分被夹紧到基部,一个或多个锚在基部和压电叠堆之间提供电耦合;以及多个导体,所述多个导体包括(i)第一导体,其通过穿过压电叠堆的厚度的第一通孔将压电叠堆的顶部电极电耦合到基部,以及(ii)第二导体,其通过穿过压电叠堆的厚度的第二通孔将压电叠堆的底部电极电耦合到基部,其中第一通孔和第二通孔设置在压电叠堆的边缘部分和中心部分之间。某些定义

[0055]

除非另外定义,否则本文中使用的所有技术术语具有与本发明所属领域的普通技术人员通常所理解的相同含义。如本说明书及所属权利要求中所使用的,单数形式的“一个”、“一种”和“所述”包括复数形式,除非上下文另外明确指出。除非另有说明,否则本文中对“或”的任何引用旨在涵盖“和/或”。方法概述

[0056]

提出了三种用于改善微加工超声换能器或mut的机电耦合系数和带宽的方法:

[0057]

1)沿着夹紧的隔膜的边缘形成凹槽,以在其边缘局部增加隔膜的顺从性;

[0058]

2)经由竖直悬臂外壳形成虚拟枢轴,该竖直悬臂外壳约束平面外运动,但是允许

由反扭矩抵抗的旋转,从而形成类似于由扭转弹簧约束的简单支撑边缘的边界条件;以及

[0059]

3)形成具有大部分自由边缘的隔膜,并且在隔膜内或其周边的一个或多个位置被夹紧。具有边缘凹槽的隔膜

[0060]

本文公开了一种通过在隔膜边缘附近蚀刻凹槽来降低隔膜边缘附近的隔膜刚度的方法。这导致具有如下边界的隔膜,该边界表现在具有扭转弹簧的夹紧边缘和简单支撑边缘之间。此“边缘凹槽”促进了类似活塞的运动、更好的耦合和更宽的带宽。

[0061]

如图5a至图5b和图6a至图6b所示,此边缘凹槽300可以应用于pmut和cmut的实施方式。为了有效,它应在隔膜边缘101a的约五个隔膜厚度内。凹槽的宽度影响刚度,更宽的凹槽促进简单支撑行为,同时降低板的抗弯刚度,并且因此更多地转变其频率。具有虚拟枢轴的隔膜

[0062]

还公开了一种形成“虚拟枢轴”的方法,该“虚拟枢轴”的行为类似于由扭转弹簧约束的简单支撑边缘。这是通过在隔板边缘形成竖直悬臂外壳来实现的。此悬臂外壳对于竖直位移非常坚硬,有效地防止了在z方向上的位移。悬臂外壳相对于隔膜边缘处的扭转是相对顺从的,允许旋转,但是基于外壳的尺寸施加反力矩。悬臂外壳还容易经由外部横向力受到在x方向和y方向上的横向位移。因此,在没有此类横向力的情况下,悬臂外壳防止隔膜边缘的位移,同时允许旋转并且施加反力矩。

[0063]

悬臂外壳的形成可以以多种方式实现。在图7a和图7b中描绘了pmut的一个示例,其中虚拟枢轴沟槽301a被蚀刻在隔膜边缘101a的外部,并且比隔膜厚度更深。悬臂外壳由虚拟枢轴蚀刻301a和形成隔膜101的空腔100之间的其余材料形成。虚拟枢轴的特性(例如,扭转弹簧的刚度、其对侧向力的抵抗力等)由悬臂外壳的尺寸决定。外壳越长越薄,虚拟枢轴就越顺从。

[0064]

如图8a和图8b所示,类似的方法可以用于cmut。虚拟枢轴沟槽301a围绕隔膜的周边进行蚀刻。对于最常见的cmut结构,在隔膜101和底部电极之间形成的空腔非常窄。利用单个虚拟枢轴沟槽301a,所得到的悬臂外壳10b将短且宽,导致非常硬的扭转弹簧。为了创建更顺从的悬臂外壳101b,可在第一沟槽301a内部蚀刻第二虚拟枢轴沟槽301b,其中两个沟槽都延伸穿过电介质层102并且进入处理衬底103。这将提供更顺从的虚拟枢轴。具有边缘凹槽的任意形状的隔膜

[0065]

鉴于本文的公开内容,本领域技术人员将会清楚,边缘凹槽的基本设计特征可以应用于任意隔膜形状,如图9a所描绘的。也可以改变凹槽的数量和位置(图9b),以及凹槽的宽度(图9c)。事实上,边缘凹槽不必具有均匀的宽度来提供有益的效果。出于路由电信号的实际目的,可能有必要在选择的区域断开凹槽,而不损失凹槽的整体优势(图9d)。具有虚拟枢轴的任意形状的隔膜

[0066]

类似地,鉴于本文的公开内容,对本领域技术人员来说容易理解的是,虚拟枢轴的基本设计特征可以应用于任意隔膜形状,如图10a所描绘的。还可以改变虚拟枢轴蚀刻的数量和位置(图10b),以及蚀刻的宽度(图10c)。与凹槽相比甚至更重要的是,虚拟枢轴蚀刻不需要均匀的宽度来实现其预期功能。与凹槽一样,虚拟枢轴沟槽可以在选择的区域被断开,以允许诸如电布线的任务(图10d)。具有自由边缘和夹紧中心区域的隔膜

[0067]

为了进一步增加机电耦合系数并拓宽带宽,公开了一种设计方法,其中隔膜很大

程度上具有自由边缘,并且被一个或多个锚任意地夹紧在中心。此设计具有类似于图3中提到的自由边缘夹紧中心设计的优点。

[0068]

图11a和图11b描绘了pmut形式的表示性实施方式,该pmut具有位于处理衬底103顶上的圆形隔膜101和中心锚105。在此情况下,压电叠堆(底部电极200、压电薄膜201和顶部电极202)位于隔膜101上的电介质薄膜102的顶部。图12a和图12b描绘了另一pmut配置,其中压电叠堆位于隔膜101和锚105之间。

[0069]

图13a和图13b描绘了类似配置的cmut,其中电极200和电极202位于处理衬底103上的电介质薄膜102的顶部。锚105将电极202附接到隔膜101。许多配置都可以创建具有自由边缘的隔膜,该具有自由边缘的隔膜固定在一个或多个锚处,其形成由彼此间隔开的两个电极构成的电容器。任意形状的隔膜,具有在一个或多个任意区域内部夹紧的自由边缘或附接到自由边缘,具有任意形状的电极

[0070]

鉴于本文的公开内容,对于本领域技术人员来说容易理解的是,自由边缘mut的概念可以应用于任意形状的隔膜,具有一个或多个任意形状的夹紧区域,具有任意形状的顶部电极和底部电极。图14a至图14c提供此类变化的若干示例。重要的是,可以将锚与隔膜的边缘重叠,以产生具有变化的自由和夹紧边界的隔膜,如图14d所示。组合边缘凹槽和虚拟枢轴

[0071]

鉴于本文的公开内容,对于本领域技术人员来说容易理解的是,边缘凹槽和虚拟枢轴的概念可以组合起来,以创建比单独应用概念中的任一个更加顺从的边缘条件。图15a至图15d和图16a至图16d相应地图示了用这两个创意配置的pmut和cmut的示例。组合自由边缘、边缘凹槽和虚拟枢轴

[0072]

鉴于本文的公开内容,对于本领域技术人员来说,将同样容易理解的是,边缘凹槽和虚拟枢轴的概念可以一起或单独应用于自由边缘mut创意。图17a至图17b、图18a至图18b和图19a至图19b相应地图示了压电叠堆位于隔膜101顶部的pmut、压电叠堆位于隔膜101和锚105之间的pmut以及cmut的概念。具有凹槽和虚拟枢轴的pmut的制造方法

[0073]

现在描述具有凹槽和虚拟枢轴的pmut(诸如图15a至图15b和图15c至图15d中示出的pmut)的示例性制造方法。

[0074]

(a)首先,提供衬底,通常是单晶硅。

[0075]

(b)然后可在衬底上方沉积绝缘层102。绝缘层102通常是某种形式的sio2,约0.1μm到3μm厚。它通常经由热氧化、pecvd沉积或其他技术来沉积。

[0076]

(c)然后可以沉积第一金属层200(也称为m1或金属1)。通常,这是粘合到衬底、防止压电体扩散、帮助压电体结构化沉积/生长并且导电的薄膜的组合。sro(srruo3)可以用于结构化膜生长,在pt的顶部用于扩散势垒和导电,在ti的顶部作为粘合层(用于pt到sio2)。通常,这些层是薄的,小于200nm,其中一些薄膜为10nm到40nm。压力、制造和成本问题通常会将此叠堆限制在小于1μm。导体(pt)通常比结构化层(sro)和粘合层(ti)更厚。除了sro之外,其他常见的结构化层包括(la

0.5

sr

0.5

)coo3、(la

0.5

sr

0.5

)mno3、lanio3、ruo2、iro2、bapbo3等。pt可以用其他导电材料代替,诸如cu、cr、ni、ag、al、mo、w和nicr。这些其他材料通常具有诸如差的扩散势垒、脆性或不利的粘合等缺点,并且pt是最常用的导体。粘合层ti

可以用任何常见的粘合层(诸如,tiw、tin、cr、ni、cr等)代替。

[0077]

(d)然后可以沉积压电材料201。一些合适压电材料的常见示例包括:pzt、knn、pzt-n、pmn-pt、aln、sc-aln、zno、pvdf和linio3。压电层的厚度可在100nm和5μm或可能更大之间变化。

[0078]

(e)然后可以沉积第二金属层202(也称为m2或金属2)。此第二金属层202可以类似于第一金属层200,并且可以用于类似的目的。对于m2,可以使用与m1相同的叠堆,但是方向相反:ti用于粘合在pt的顶部上,以防止结构在sro的顶部上扩散。

[0079]

(f)然后可以图案化和蚀刻第二金属层或m2 202,在压电层上停止。本文可以以多种方式进行蚀刻,例如,经由rie(反应离子蚀刻)、离子研磨、湿化学蚀刻、各向同性气体蚀刻等。在图案化和蚀刻之后,可以经由湿法蚀刻和/或干法蚀刻剥离用于图案化m2的光致抗蚀剂。在本文所描述的用于制造cmut和pmut的许多实施方式中,可以使用任何数量的蚀刻方式,并且通常在大部分图案化和蚀刻步骤之后剥离光致抗蚀剂。

[0080]

(g)然后可以类似地图案化和蚀刻压电层,在第一金属层或m1 200处停止。通常,使用湿法、rie和/或离子研磨蚀刻。

[0081]

(h)然后可以类似地图案化和蚀刻第一金属层或m1 100,在电介质102上停止。

[0082]

(i)如果需要,可以添加以下一项或两项:(1)h2势垒。进入压电层的h2扩散会限制其寿命。为了防止此情况,可以使用h2势垒。40nm的ald(原子层沉积)氧化铝(al2o3)可以用来实现这一点。其他合适的材料可以包括sic、类金刚石碳等。(2)再分配层(rdl)。此层可以提供m1和m2之间的连接以及其他连接(例如,引线结合、凸块结合等)。可以经由首先添加诸如氧化物的电介质、在电介质中蚀刻通孔、沉积导体(通常为al)以及最后图案化导体来形成rdl。此外,可以添加钝化层(通常是氧化物 氮化物)来防止物理划痕、意外短路和/或湿气进入。

[0083]

(j)然后可以图案化凹槽300。电介质层102可以经由rie或湿法蚀刻来蚀刻。可以蚀刻衬底100,并且由于衬底100通常是硅,因此蚀刻通常是drie(深度反应离子蚀刻)。这些凹槽300可以具有100nm和1000μm之间的横向尺寸,但是通常在2μm和10μm之间。凹槽300可以具有器件100厚度的0.1%到100%的任何深度,但是通常在器件100厚度的25%%到75%的范围内。

[0084]

(k)可以图案化和蚀刻虚拟枢轴301a。电介质层102可以经由rie或湿法蚀刻来蚀刻。衬底100通常是硅,并且通常可以经由drie(深度反应离子蚀刻)来蚀刻。这些虚拟枢轴301a可以具有100nm到1000μm之间(但是通常在2μm到10μm之间)的横向尺寸。虚拟枢轴可以具有处理部103厚度的0.1%到99.9%的任何深度,但是通常在处理部103厚度的10%到50%的范围内(约10μm到100μm)。

[0085]

(l)通常,使用soi衬底,如图15c至图15d中所示。在此情况下,在隔膜101的正下方有掩埋的绝缘层或box层104。然后,隔膜由“器件”层100(box上面的层)和box下面的“处理”层103组成。100中的空腔可在box上停止,并且可以蚀刻出处理层103。在此情况下,301a蚀刻可以包括两个额外的步骤:(1)在经由drie蚀刻器件层之后,蚀刻box(通常经由干法rie蚀刻,或在一些情况下,经由湿法蚀刻);以及(2)经由drie将处理层蚀刻到期望的深度。大多数soi晶片是硅,这意味着器件层和处理层通常是单晶硅。在此情况下,绝缘体box通常是

称为“掩埋氧化物”的热生长的二氧化硅,这就是术语“box”的来源。通常可以使用拥有具有氧化物box的单晶硅处理层和器件层的硅soi晶片。器件层可以是5μm,但是通常在100nm和100μm之间变化,而处理层厚度通常在100μm和1000μm之间变化。box通常在100nm和5μm之间,但是在许多情况下可以使用1μm。

[0086]

(m)如果需要,可以经由研磨使晶片或处理部的背面变薄,并且可选地在此时抛光。在许多实施方式中,处理层从500μm变薄到300μm厚。常见的厚度通常在50μm和1000μm之间变化。

[0087]

(n)可在晶片或处理部的背面图案化空腔,并且可以蚀刻空腔。通常,晶片/处理部由硅组成,并且用drie实现蚀刻。在图15a至图15b的情况下,蚀刻可以定时。在图15c至图15d中,蚀刻可以选择性地在box上停止。可以经由其他技术(诸如,koh、tmah、hna和rie)来蚀刻空腔。在光致抗蚀剂剥离之后,可以认为晶片完成。具有凹槽的pmut的制造方法

[0088]

还提供具有凹槽的pmut(诸如图5a至图5d中示出的pmut)的示例性制造方法。此方法可以类似于上述具有凹槽和虚拟枢轴的pmut的制造方法(图15a至图15b和图15c至图15d),除了步骤(k),虚拟枢轴的图案化和蚀刻,通常被跳过。具有虚拟枢轴的pmut的制造方法

[0089]

还提供具有悬臂外壳的pmut(诸如图7a至图7d中示出的pmut)的示例性制造方法。此方法可以类似于上述具有凹槽和虚拟枢轴的pmut的制造方法(图15a至图15b和图15c至图15d),除了步骤(j),凹槽的图案化和蚀刻,通常被跳过。具有凹槽和虚拟枢轴的cmut的制造方法

[0090]

现在描述具有凹槽和虚拟枢轴的cmut(诸如图16e和图16f中示出的cmut)的示例性制造方法。

[0091]

(a)该方法通常从将成为处理部103的衬底开始。通常,此衬底是单晶硅。

[0092]

(b)然后可以图案化和蚀刻浅空腔。此空腔通常为10nm到5μm,最常见的是在100nm到1μm之间。对于常见的单晶硅衬底,此空腔是使用drie、rie、hna或氧化的定时蚀刻。

[0093]

(c)然后可以沉积绝缘层102。通常,此绝缘层是某种形式的sio2,约0.1μm到3μm厚。它通常经由热氧化来沉积,并且在一些情况下经由pecvd或lpcvd沉积或一些其他技术来沉积。

[0094]

(d)然后可以沉积金属层或导体200,此类导体的示例包括如al、au、cr、cu、pt等。此导体可在诸如ti、tiw、tin、cr等的粘合层和/或扩散势垒层上。

[0095]

(e)可以图案化和蚀刻导体(以及粘合层和/或扩散势垒层),在绝缘体上停止。

[0096]

(f)可以图案化和蚀刻虚拟枢轴301b和虚拟枢轴301a的底部分。首先,绝缘体102可以经由rie、湿法蚀刻或另一种技术来蚀刻。接下来,可以蚀刻处理部103。通常,处理部103是硅,并且此蚀刻经由drie进行,并且是定时的。如同上面参考图15a至图15b和图15c至图15d描述的过程,虚拟枢轴的深度范围可以从1μm到1000μm,但是通常在10μm和100μm之间,或处理部103的约10%到50%。

[0097]

(g)器件100层可以结合到处理部103上的绝缘体102。这可以经由许多技术来实现,包括但是不限于熔合、al-ge、au-si、阳极、slid(固液互扩散)、粘合、au-au、au-sn、cu-cu、cu-sn等。结合的选择可能取决于允许的热预算和可用的过程以及集成要求。图16e和图

16f中示出的结合是氧化物102到硅100的熔合结合。

[0098]

(h)可以将边缘凹槽300图案化和蚀刻到器件100中。这通常通过定时drie来实现。与图15a至图15b和图15c至图15d的过程一样,这些凹槽的横向尺寸可在100nm和1000μm之间,但是通常在2μm和10μm之间。凹槽可以具有器件100厚度的0.1%到100%的任何深度,但是通常在器件100厚度的25%到75%的范围内。

[0099]

(i)可以图案化和蚀刻虚拟枢轴301a的顶部分。这通常通过定时drie来实现。301a的顶部分的横向尺寸通常小于或大于301a的底部分的横向尺寸,以克服对准问题。

[0100]

此方法可以以多种方式变化。在一些实施方式中,可以跳过步骤(d)和(e)来制造图16g和图16h中示出的cmut。在一些实施方式中,反而可以在器件的底部上执行步骤(b)来制造图16a和图16b中示出的cmut。在一些实施方式中,反而可以跳过步骤(d)和步骤(e)并且可以在器件的底部上执行步骤(b)来制造图16c和图16d中示出的cmut。标称自由边缘设计和制造方法

[0101]

pmut的标称自由边缘设计通常需要两个独立的衬底触点。这是因为pmut通常需要跨其压电材料的电压差,因此需要至少两个电压。有许多方法可以施加至少两种电压。图20a和图20b示出了一种示例性pmut自由边缘设计,其制造过程或方法描述如下。

[0102]

(a)该方法可以从soi晶片开始。通常,这是在处理层的顶部上的box(氧化物)的顶部上的单晶硅的器件层。此晶片的此器件层在图20a和图20b中被颠倒示出。

[0103]

(b)然后可以沉积绝缘层102。通常,此沉积物是某种形式的sio2,约0.1μm到3μm厚。它通常经由热氧化、pecvd沉积或其他技术来沉积。

[0104]

(c)可以沉积第一金属层或m1(金属1)200。通常,此沉积是粘合到衬底、防止压电体扩散、帮助压电体结构化沉积/生长并且导电的薄膜的组合。sro(srruo3)可以用于结构化膜生长,在pt的顶部上用于扩散势垒和导电,在ti的顶部上作为粘合层(用于pt到sio2)。通常,这些层是薄的,小于200nm,其中一些薄膜为10nm到40nm。压力、制造和成本问题通常会将此叠堆限制在小于1μm。导体(pt)通常比结构化层(sro)和粘合层(ti)更厚。除了sro之外,其他常见的结构化层包括(la

0.5

sr

0.5

)coo3、(la

0.5

sr

0.5

)mno3、lanio3、ruo2、iro2、bapbo3等。pt可以用其他导电材料代替,诸如cu、cr、ni、ag、al、mo、w和nicr。这些其他材料通常具有诸如差的扩散势垒、脆性或不利的粘合等缺点,并且pt是最常用的导体。粘合层ti可以用任何常见的粘合层(诸如tiw、tin、cr、ni、cr等)代替。

[0105]

(d)然后可以沉积压电材料201。压电材料的常见示例包括:pzt、knn、pzt-n、pmn-pt、aln、sc-aln、zno、pvdf和linio3。压电材料的厚度可以在100nm和5μm(可能更大)之间变化。

[0106]

(e)可以沉积第二金属层或m2(金属2)202。m2可以类似于m1 200并且可以用于类似的目的。对于m2,可以使用与m1相同的叠堆,但是方向相反:ti用于粘合在pt的顶部上,以防止结构在sro的顶部上扩散。

[0107]

(f)可以图案化和蚀刻m2 202,在压电上停止。本文可以以多种方式进行蚀刻,例如,经由rie(反应离子蚀刻)、离子研磨、湿化学蚀刻、各向同性气体蚀刻等。在图案化和蚀刻之后,可以剥离、润湿和/或干燥用于图案化m2的光致抗蚀剂。在本文所描述的用于制造cmut和pmut的许多实施方式中,可以使用任何数量的蚀刻方式,并且通常在大部分图案化和蚀刻步骤之后剥离光致抗蚀剂。

[0108]

(g)然后可以类似地图案化和蚀刻压电层,在第一金属层或m1 200处停止。通常,使用湿法、rie和/或离子研磨蚀刻。

[0109]

(h)然后可以类似地图案化和蚀刻第一金属层或m1 100,在电介质102上停止。

[0110]

(i)如果需要,可以添加h2势垒。进入压电层的h2扩散会限制其寿命。为了防止此情况,可以使用h2势垒。40nm的ald(原子层沉积)氧化铝(al2o3)可以用来实现这一点。其他合适的材料可以包括sic、类金刚石碳等。

[0111]

(j)可以沉积电介质层106。此层通常是氧化物和/或氮化物层(通常为pecvd),厚度通常在100nm到2μm之间。

[0112]

(k)可以在电介质层106中图案化和蚀刻通孔(或孔)108。这通常经由rie蚀刻或某种形式的湿法蚀刻来完成。蚀刻可能会在m1或m2上停止。

[0113]

(l)可以沉积、图案化和蚀刻再分配导体107。典型的导体是金属(al、cu、au、ti、cr等)和/或半导体,诸如多晶硅、多晶锗或多晶硅锗。此层通常相对较厚(在100nm和5μm之间,尽管通常在0.5μm和2μm之间)以克服形貌和较低的阻抗。在示例中,使用在1.6μm al顶部上的100nm ti顶部上的1μm au。au用于步骤s中的集成结合,这将在下面进一步描述。

[0114]

(m)然后可以图案化凹槽300。电介质层102可以经由rie或湿法蚀刻来蚀刻。可以蚀刻衬底100,并且由于衬底100通常是硅,因此蚀刻通常是drie(深度反应离子蚀刻)。这些凹槽300可以具有100nm和1000μm之间的横向尺寸,但是通常在2μm和10μm之间。凹槽300可以具有从器件100厚度的0.1%到99.9%的任何深度,但是通常在器件100厚度的25%到75%的范围内。

[0115]

(n)可以图案化和蚀刻器件层101。电介质层106可以经由rie或湿法蚀刻来蚀刻。可以蚀刻衬底100(通常是硅),因此蚀刻通常是drie(深度反应离子蚀刻)。此蚀刻可以穿过整个器件层100,直到它在box上停止。这些蚀刻可以具有100nm到几cm之间(但是通常在5μm到1000μm之间)的横向尺寸。

[0116]

(o)可选地,可以沉积、图案化和蚀刻钝化层,以防止物理划痕、意外短路和/或湿气进入。此钝化层通常是氧化物和/或氮化物,厚度通常在300nm到2μm之间。

[0117]

(p)如果需要,可以经由研磨使晶片或处理部的背面变薄,并且可选地在此时抛光。在许多实施方式中,处理层从500μm变薄到300μm厚。常见的厚度通常在50μm和1000μm之间变化。

[0118]

(q)现在切割mems晶片(101-102、106-9、200-202、300、101a和处理层)以准备结合。

[0119]

(r)可在基部衬底111上沉积、图案化和蚀刻导电结合材料110。例如,基部衬底111可以是平坦化的asic晶片。导电结合材料可以是1μm的au,以使能步骤s中的结合。

[0120]

(s)mems裸片(101-102、106-9、200-202、300、101a和处理层)可以与基部衬底111对准并且结合,在再分配导体107和导电结合材料110之间形成导电结合物109。可选地,仅选择良好的mems裸片。mems裸片可以仅结合到经过验证的良好asic裸片以保持良品率。不良asic裸片与哑mems裸片结合用于蚀刻载荷(在步骤t中)。该结合可以是任何导电结合,包括au-au热压、slid、al-ge、au-sn、cu-cu等。例如,可以使用au-au热压。

[0121]

(t)基部衬底111可以填充有mems裸片。可以以drie工具蚀刻mems裸片的背面,以移除处理硅(未示出),在box上停止。

[0122]

(u)可以以氧化物rie蚀刻mems裸片的背面以移除box,在器件层101上停止。一旦完成,就可以认为实现了图20a和图20b的布局和横截面。

[0123]

对于图20a和图20b的pmut值得注意的是:

[0124]

(a)导电结合物109可以允许电信号从基部衬底111通过导电结合材料110到再分配导体107来传递到mems裸片。

[0125]

(b)可以有至少两个独立的信号,一个通过通孔108连接到m1层202,并且另一个通过类似的通孔108连接到m2层200。这可以允许设计者在压电层201上施加已知的电压差,使能启动pmut。

[0126]

(c)边缘凹槽300可以提供增强的k

eff2

。

[0127]

(d)可选地,可以形成虚拟枢轴以进一步增加k

eff2

。如果导电结合材料110具有比其横向尺寸大得多的高度,则结合物可以形成悬臂式外壳。

[0128]

(e)上述过程可以创建具有自由边缘、凹槽和悬臂外壳的pmut,并且可以仅组合已知的良好裸片来提高良品率。

[0129]

(f)本领域的技术人员可以使用此制造方法,结合凹槽、自由边缘和虚拟枢轴的设计概念,来形成各种各样的新型pmut。

[0130]

尽管上面根据许多实施方式描述了制造pmut和cmut的各种方法,但是本领域的普通技术人员将认识到基于本文所描述的教导的许多变化。这些步骤可以以不同的顺序完成。可以添加或删除步骤。一些步骤可以包括子步骤。本领域已知的制造技术可以应用于一个或多个步骤。许多步骤可以根据需要经常重复。参考文献

[0131]

[1]r.d.blevins.固有频率和振型的公式。kreiger,1979。

[0132]

[2]k.m.smyth.用于医学成像的压电微机械超声换能器。麻省理工学院,2017。

[0133]

尽管已经在本文中示出和描述了本发明的优选实施方式,但是对于本领域技术人员而言容易理解的是,这些实施方式仅以示例的方式提供。在不脱离本发明的情况下,本领域技术人员现在将想到许多变化、改变和替换。应理解,本文所述的本发明的实施方式的各种可替选方案可以用于实施本发明。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。