打印机驱动系统的系统级封装芯片

【技术领域】

1.本案是有关一种系统级芯片封装技术,特别是指一种打印机驱动系统的系统级封装芯片。

背景技术:

2.近年来打印机技术不断突破创新,其制作技术可参考已知的半导体制程以降低制作成本,尤其应用在芯片封装元件的可靠度及减少元件尺寸的方面,在半导体工艺领域,为了增加速度、功率与效率,同时为了减少整体元件的尺寸,芯片做得愈来愈小,在一些情形中,芯片并列地安装在封装基材上,且通过封装基材连在一起,或直接与布线连接。在其它情形中,芯片一个接着另一个地安装于基板上,以直接连而没有任何中间布线或封装基材。这有时称为堆叠芯片封装。使用取放(pick and pick)机或许多其他类型的设备,将一个芯片放置在另一个芯片上,可将其组合封装,就像是具有两倍高度的单一个芯片。

3.举例一实施例,芯片可使用不同技术点,例如22nm、14nm、10nm等等来制作,可将该多个不同点组合,且与其它类型不同点组合,使得可将来自不同制程与不同制造商的不同类型芯片放在单一个封装体内。在半导体芯片封装领域中,将多个芯片组合成单一个封装,以允许两个或更多个不同类型的芯片放入单一个封装内,这可称为芯片对芯片连接的异质整合。

4.在封装技术中,可在一芯片上方形成重布层(rdl)并将其电连接至芯片中的主动装置。然后可形成输入/输出(i/o)连接器(诸如凸块下金属(ubm)上的焊球)以通过rdl将其电连接至芯片。此封装技术有利特征是形成扇出型封装的可能性。因此,芯片上的i/o垫可经重布以覆盖比芯片大的一区,且因此可增加包装于经封装芯片的表面上的i/o垫的数目。整合式扇出型(info)封装技术正变得愈加流行,当与晶圆级封装(wlp)技术组合时尤其如此。此等所得封装结构提供高功能密度,具有相对低成本及高效能封装。

技术实现要素:

5.本案是为一种打印机驱动系统的系统级封装芯片,其主要目的是将多个不同功效的芯片进行一次性封装,不仅可提升工作效率,同时可降低制作成本及元件尺寸。

6.为达上述目的,本案的打印机驱动系统的系统级封装芯片,适用于一打印机,包含布置在一共同封装中的一第一芯片、一第二芯片及一第三芯片;其中第一芯片及第二芯片被并排布置在共同封装中一载体上;以及第三芯片被布置在共同封装中的第一芯片的顶部上;以及一导线载体结构被放置第三芯片之前形成在第一芯片的顶部。

7.为达上述目的,本案的打印机驱动系统的系统级封装芯片,适用于一打印机,包含布置在一共同封装中的一第一芯片、一第二芯片及一第三芯片;其中第一芯片、第二芯片及第三芯片以平行、并排设置于共同封装中。

8.为达上述目的,本案的打印机驱动系统的系统级封装芯片,适用于一打印机,包含布置在一共同封装中的一第一芯片、一第二芯片及一第三芯片;其中第一芯片、第二芯片及

第三芯片以垂直、堆叠设置于共同封装中。

9.较佳地,第一芯片为一无线通信芯片,第二芯片为一电源整合驱动芯片,第三芯片为一打印系统单芯片。

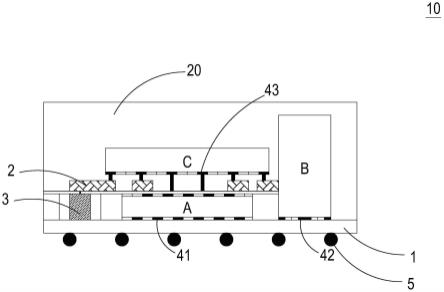

10.较佳地,第一芯片为一无线通信芯片,第二芯片为一打印系统单芯片,第三芯片为一电源整合驱动芯片。

11.较佳地,第一芯片为一电源整合驱动芯片,第二芯片为一无线通信芯片,第三芯片为一打印系统单芯片。

12.较佳地,第一芯片为一电源整合驱动芯片,第二芯片为一打印系统单芯片,第三芯片为一无线通信芯片。

13.较佳地,第一芯片为一打印系统单芯片,第二芯片为一无线通信芯片,第三芯片为一电源整合驱动芯片。

【附图说明】

14.图1是本案第一实施例封装示意图(一)。图2是本案第一实施例封装示意图(二)。图3是本案第一实施例封装示意图(三)。图4是本案第二实施例封装示意图(一)。图5是本案第二实施例封装示意图(二)。图6是本案第二实施例封装示意图(三)。图7是本案第三实施例封装示意图(一)。图8是本案第三实施例封装示意图(二)。【符号说明】

15.1:载体2:导线载体结构3:垂直导电结构5:金属球10:系统级封装装置20:共同封装41、42、43、44、45、46、47、48:接触界面a:第一芯片b:第二芯片c:第三芯片h1:第一垂直尺寸h2:第二垂直尺寸h3:第三垂直尺寸

【具体实施方式】

16.体现本案特征与优点的实施例将在后段的说明中详细叙述。应理解的是本案能够在不同的态样上具有各种的变化,其皆不脱离本案的范围,且其中的说明及图示在本质上

当作说明之用,而非用以限制本案。

17.请综合参阅图1至图8所示,以下详细说明本案实施例。本案是为一种系统级芯片封装技术,应用实施于打印机驱动系统的系统级封装芯片。

18.如图1及图2所示,其为本案第一实施例。系统级封装装置10包含设置在一共同封装20中的一第一芯片a、一第二芯片b及一第三芯片c,第一芯片a包含一第一垂直尺寸h1,第二芯片b包含一第二垂直尺寸h2,第三芯片c包含一第三垂直尺寸h3,其中第一芯片a与第二芯片b并排设置于共同封装20中,而第三芯片c直接或间接的设置于第一芯片a之上。借由把第一芯片a、第二芯片b及第三芯片c设置于共同封装20内,并且把薄的芯片设置在一堆叠中,而较厚的芯片与较薄的芯片堆叠设置,借此可减小系统级封装装置10的尺寸。

19.于本实施例中,第一芯片a为一无线通信芯片,第二芯片b为一电源整合驱动芯片,第三芯片c为一打印系统单芯片;或第一芯片a为一无线通信芯片,第二芯片b为一打印系统单芯片,第三芯片c为一电源整合驱动芯片;或第一芯片a为一电源整合驱动芯片,第二芯片b为一无线通信芯片,第三芯片c为一打印系统单芯片;或第一芯片a为一电源整合驱动芯片,第二芯片b为一打印系统单芯片,第三芯片c为一无线通信芯片;或第一芯片a为一打印系统单芯片,第二芯片b为一无线通信芯片,第三芯片c为一电源整合驱动芯片;或第一芯片a为一打印系统单芯片,第二芯片b为一电源整合驱动芯片,第三芯片c为一无线通信芯片,以上第一芯片a、第二芯片b及第三芯片c欲选择何种芯片进行系统级封装,是可依实际需求选用。

20.以及,共同封装20可为一扇出晶圆级系统级封装、一扇出面板系统级封装或一覆晶系统级封装。

21.请再一并参阅图1~图3所示,进一步说明本案第一实施例的元件关系,其中,系统级封装装置10是包含位于共同封装20中的第一芯片a与第三芯片c之间的一导线载体结构2,其中,导线载体结构2把位于第一芯片a的一横向覆盖区域外部的至少一个垂直导电结构3连接到第一芯片a,以及至少一垂直导电结构3把导线载体结构2连接到一载体1,且载体1的底面是附接外部一金属球5与一印刷电路板(pcb)连接。其中,第一芯片a的一底面表面及第二芯片b的一底面表面被布置在实质上相同的载体1基准面上。以及在第一芯片a的一底面处的一接触界面41及在第二芯片b的一底面处的一接触界面42被连接到载体1。其中在第三芯片c的一底面处的一接触界面43被连接到导线载体结构2,据此第一芯片a、第二芯片b及第三芯片c形成一部分平行并排,部分垂直重叠设置,且形成电性连接。

22.以及,于本实施例中,导线载体结构2可为一共同正面重新分布层结构、一共同面板结构或一共同覆晶基板的群组中的一者;载体1可为一金属载体、一扇出面板或一覆晶基板的群组中的一者。

23.再请参阅图1~图3所示,系统级封装装置10包含布置在共同封装20中的至少三芯片,包含第一芯片a、第二芯片b及第三芯片c分别以第一垂直尺寸h1、第二垂直尺寸h2及第三垂直尺寸h3被并排或垂直布置在共同封装20中,使其不同垂直尺寸的各芯片布置于共同封装20内,其中,第三芯片c的第三垂直尺寸h3小于第二芯片b的第二垂直尺寸h2,第三芯片c可被间接地布置在共同封装中的第一芯片a之上,据此,借由将第一芯片a、第二芯片b及第三芯片c先预先整合后,再以系统级封装装置10将第一芯片a、第二芯片b及第三芯片c封装并且设置于共同封装20之内,俾能完成一次性的芯片封装技术,俾使制造成本呈现显著的

降低。

24.请参阅图4~图5所示,其为本案第二实施例,本实施例是为一种系统级芯片封装技术,应用实施于打印机驱动系统的系统级封装芯片,系统级封装装置10包含设置在一共同封装20中的一第一芯片a、一第二芯片b及一第三芯片c,第一芯片a包含一第一垂直尺寸h1,第二芯片b包含一第二垂直尺寸h2,第三芯片c包含一第三垂直尺寸h3,其中第一芯片a与第二芯片b及第三芯片c平行并排地设置于共同封装20中。

25.于本实施例中,第一芯片a为一无线通信芯片,第二芯片b为一电源整合驱动芯片,第三芯片c为一打印系统单芯片;或第一芯片a为一无线通信芯片,第二芯片b为一打印系统单芯片,第三芯片c为一电源整合驱动芯片;或第一芯片a为一电源整合驱动芯片,第二芯片b为一无线通信芯片,第三芯片c为一打印系统单芯片;或第一芯片a为一电源整合驱动芯片,第二芯片b为一打印系统单芯片,第三芯片c为一无线通信芯片;或第一芯片a为一打印系统单芯片,第二芯片b为一无线通信芯片,第三芯片c为一电源整合驱动芯片;或第一芯片a为一打印系统单芯片,第二芯片b为一电源整合驱动芯片,第三芯片c为一无线通信芯片,以上第一芯片a、第二芯片b及第三芯片c欲选择何种芯片进行系统级封装,是可依实际需求选用。

26.以及,共同封装20可为一扇出晶圆级系统级封装、一扇出面板系统级封装或一覆晶系统级封装。

27.请一并参阅图4~图6所示,进一步说明本案第二实施例的元件关系,其中,系统级封装装置10是包含位于共同封装20中的第一芯片a、第二芯片b与第三芯片c之间的一导线载体结构2,其中,导线载体结构2使得第一芯片a、第二芯片b及第三芯片c的一横向覆盖区域形成电性连接。其中,第一芯片a的一底面表面、第二芯片b及第三芯片c的一底面表面被布置在实质上相同的载体1基准面上。以及在第一芯片a的一底面处的一接触界面41、第二芯片b的一底面处的一接触界面42及第三芯片c的一底面处的一接触界面43连接至载体1,据此,第一芯片a、第二芯片b、第三芯片c形成一平行并排设置且形成电性连接。

28.于本实施例中,载体1可为一金属载体、一扇出面板或一覆晶基板的群组中的一者。

29.如图4、图5所示,系统级封装装置10包含布置在共同封装20中的至少三芯片,其中第一芯片a、第二芯片b及第三芯片c分别以第一垂直尺寸h1、第二垂直尺寸h2及第三垂直尺寸h3被并排布置在共同封装20中,使其不同垂直尺寸的各芯片布置于共同封装20内,其中,第三芯片c的第三垂直尺寸h3小于第二芯片b的第二垂直尺寸h2。据此,借由将第一芯片a、第二芯片b及第三芯片c先预先整合后,再以系统级封装装置10将第一芯片a、第二芯片b及第三芯片c封装置于共同封装20之内,俾能完成一次性的芯片封装技术,俾使制造成本呈现显著的降低。

30.请参阅图7及图8所示,其为本案第三实施例,本案是为一种系统级芯片封装技术,应用实施于打印机驱动系统的系统级封装芯片,系统级封装装置10包含设置在一共同封装20中的一第一芯片a、一第二芯片b及一第三芯片c,第一芯片a包含一第一垂直尺寸h1,第二芯片b包含一第二垂直尺寸h2,第三芯片c包含一第三垂直尺寸h3,其中第一芯片a与第二芯片b及第三芯片c垂直堆叠设置于共同封装20中。

31.于本实施例中,第一芯片a为一无线通信芯片,第二芯片b为一电源整合驱动芯片,

第三芯片c为一打印系统单芯片;或第一芯片a为一无线通信芯片,第二芯片b为一打印系统单芯片,第三芯片c为一电源整合驱动芯片;或第一芯片a为一电源整合驱动芯片,第二芯片b为一无线通信芯片,第三芯片c为一打印系统单芯片;或第一芯片a为一电源整合驱动芯片,第二芯片b为一打印系统单芯片,第三芯片c为一无线通信芯片;或第一芯片a为一打印系统单芯片,第二芯片b为一无线通信芯片,第三芯片c为一电源整合驱动芯片;或第一芯片a为一打印系统单芯片,第二芯片b为一电源整合驱动芯片,第三芯片c为一无线通信芯片,以上第一芯片a、第二芯片b及第三芯片c欲选择何种芯片进行系统级封装,是可依实际需求选用。

32.以及,共同封装20可为一扇出晶圆级系统级封装、一扇出面板系统级封装或一覆晶系统级封装。

33.请一并参阅图7~图8所示,进一步说明本案第三实施例的元件关系,其中,系统级封装装置10是包含位于共同封装20中的第一芯片a、第二芯片b与第三芯片c之间的一导线载体结构2,其中,导线载体结构2使位于第一芯片a、第二芯片b及第三芯片c的一纵覆盖区域形成电性连接。其中,第一芯片a的一顶面处及底面处的一接触界面44、45与导线载体结构2及载体1连接,第二芯片b的一顶面处及底面处的一接触界面46、47共同与导线载体结构2连接,第三芯片c的一底面处的一接触界面48连接至导线载体结构2,据此第一芯片a、第二芯片b及第三芯片c形成一垂直堆叠设置且形成电性连接。

34.于本实施例中,载体1可为一金属载体、一扇出面板或一覆晶基板的群组中的一者。

35.如图7、图8所示,系统级封装装置10包含布置在共同封装20中的至少三芯片,其中第一芯片a、第二芯片b及第三芯片c分别以第一垂直尺寸h1、第二垂直尺寸h2及第三垂直尺寸h3被垂直堆叠设置在共同封装20中,使其不同垂直尺寸的各芯片布置于共同封装20内,其中,第三芯片c的第三垂直尺寸h3大于第二芯片b的第二垂直尺寸h2,而第二芯片b直接或间接的设置于第一芯片a,第三芯片c直接或间接的设置于第一芯片a之上。据此,借由将第一芯片a、第二芯片b及第三芯片c先预先整合后,再以系统级封装装置10将第一芯片a、第二芯片b及第三芯片c封装置于共同封装20之内,俾能完成一次性的芯片封装技术,俾使制造成本呈现显著的降低。

36.不论是第一实施例、第二实施例、或第三实施例,虽然三个芯片被叙述来配合图式所示的实施例,但实际使用上,可以在共同封装20内设置超过三的任何数量的芯片。

37.优先地,系统级封装装置10可以包含一内部重新分布结构,用于实现在系统级封装装置10的第一芯片a~第三芯片c之间的电气连接/或用在实现从外部装置或一印刷电路板到设置在共同封装20内的一或多个芯片(例如第三芯片c),而不用直接接取系统级封装装置10的正面。内部重新分布层结构可包含至少一结构化金属(例如铜层)来实现金属线用于在电绝缘材料中做嵌入式的布线。

38.综上所述,本案为一种打印机驱动系统的系统级封装芯片,提供系统级封装装置10将第一芯片a、第二芯片b及第三芯片c一次性地封装于共同封装20内,有效改善已知的封装方式,避免一个芯片就执行一次封装,除此,第一芯片a、第二芯片b及第三芯片c可依实际需求选择采用无线通信芯片或电源整合驱动芯片或打印系统单芯片。如此一来,已知的封装方式是对应欲封装的芯片数量决定封装次数,而反观本案的系统级封装,是可将多个芯

片进行一次性地封装,有效减少制造成本,及封装后的元件尺寸。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。