1.本发明涉及引线框架、引线框架的制造方法以及半导体装置。

背景技术:

2.公知有将半导体芯片搭载于引线框架,并且用树脂进行密封的半导体装置。这样的半导体装置因动作时的发热而反复膨胀、收缩。因此,为了提高引线框架与树脂的密合性,在引线框架的表面进行粗化处理。

3.《现有技术文献》

4.《专利文献》

5.专利文献1:日本国特开2017-5149号公报

6.专利文献2:日本国特开2008-187045号公报

技术实现要素:

7.《本发明要解决的问题》

8.在引线框架的表面进行粗化处理的情况下,用于半导体芯片向引线框架的固定的粘合剂(芯片附着膏)中含有的溶剂成分容易在引线框架的表面浸润扩展。担心溶剂成分使引线框架与树脂之间的密合性降低。另外,在与用于搭载半导体芯片的部位连续的部位(例如,芯片焊盘之上)进行引线接合的情况下,担心浸润扩展的溶剂成分阻碍引线接合。

9.本发明的目的在于,提供一种引线框架、引线框架的制造方法以及半导体装置,其能够抑制因粘合剂中含有的溶剂成分导致的与密封树脂的密合性降低,并且能够回避引线接合障碍。

10.《用于解决问题的手段》

11.根据本发明的一个方式,提供一种引线框架,其在一个面具有用于搭载半导体芯片的第一区域以及上述第一区域的周围的第二区域,上述第二区域具有:粗化区域;以及粗化缓和区域,其设于上述粗化区域和上述第一区域之间,该粗化缓和区域的平坦度比上述粗化区域的平坦度高。

12.《发明的效果》

13.根据本发明,能够抑制因粘合剂中含有的溶剂成分导致的与密封树脂的密合性的降低,并且能够回避引线接合障碍。

附图说明

14.图1是示出第一实施方式的引线框架的俯视图。

15.图2是放大示出图1中的一部分的图。

16.图3是示出第一实施方式的引线框架的剖视图。

17.图4是示出粗化区域以及粗化缓和区域的扫描型电子显微镜照片的例子的图。

18.图5是示出溶剂成分的浸润扩展被抑制的样子的示意图。

19.图6是示出s比例的计算方法的图。

20.图7是示出第一实施方式的引线框架的制造方法的图(其1)。

21.图8是示出第一实施方式的引线框架的制造方法的图(其2)。

22.图9是示出第一实施方式的引线框架的制造方法的图(其3)。

23.图10是示出第一实施方式的引线框架的制造方法的图(其4)。

24.图11是示出第一实施方式的引线框架的制造方法的图(其5)。

25.图12是示出第一实施方式的引线框架的制造方法的图(其6)。

26.图13是示出第一实施方式的引线框架的制造方法的图(其7)。

27.图14是示出粗化部的扫描型电子显微镜照片的例子的图。

28.图15是示出第二实施方式的半导体装置的剖视图。

29.图16是示出第二实施方式的半导体装置的制造方法的图(其1)。

30.图17是示出第二实施方式的半导体装置的制造方法的(其2)。

31.图18是示出第二实施方式的半导体装置的制造方法的(其3)。

32.图19是示出第二实施方式的半导体装置的制造方法的(其4)。

33.图20是示出粘合剂中含有的溶剂成分的举动的剖视图。

34.图21是示出变形例的半导体装置的剖视图。

35.附图标记的说明:

36.100、201:引线框架

37.10:板材

38.11:芯片焊盘

39.12:引线

40.17:粘合剂

41.19:溶剂成分

42.20:半导体芯片

43.40:树脂部

44.100a:上表面

45.100b:下表面

46.101:基部

47.102:粗化面

48.110:第一区域

49.116:ag糊料

50.117:溶剂成分

51.120:第二区域

52.121:粗化区域

53.122:粗化缓和区域

54.200、200a:半导体装置

具体实施方式

55.以下,参照附图对实施方式具体进行说明。需要说明的是,在本说明书以及附图

中,对于实质上具有相同功能构成的构成元件,有时通过付与相同的附图标记而省略重复的说明。在本发明中,为了方便,将引线框架的用于搭载半导体芯片侧设定为一侧或上侧,将其相反侧设定为另一侧或下侧。另外,将引线框架的用于搭载半导体芯片的面设定为一个面或上表面,将其相反侧的面设定为另一面或下表面。但是,引线框架以及半导体装置可以在上下颠倒的状态下使用,或者以任意的角度进行配置。另外,俯视是指,自引线框架的一个面的法线方向观察对象物,俯视形状是指,自引线框架的一个面的法线方向观察对象物的形状。

56.(第一实施方式)

57.首先,对第一实施方式进行说明。第一实施方式涉及引线框架。

58.[引线框架的构造]

[0059]

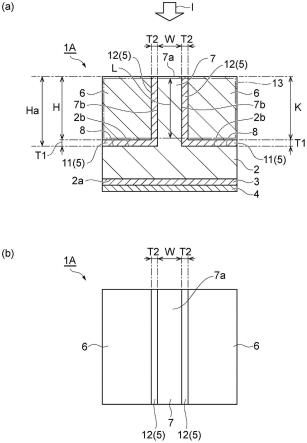

首先,对引线框架的构造进行说明。图1是示出第一实施方式的引线框架的俯视图。图2是放大示出图1中的一部分的图。图3是示出第一实施方式的引线框架的剖视图。图3的(a)相当于沿图1以及图2中的iiia-iiia线的剖视图,图3的(b)相当于沿图1以及图2中的iiib-iiib线的剖视图,图3的(c)相当于沿图1以及图2中的iiic-iiic线的剖视图。

[0060]

第一实施方式的引线框架100是在一个面上搭载半导体芯片,并且被密封树脂覆盖而成为半导体装置的引线框架。在引线框架100中,在基部101的表面局部形成有粗化面102。

[0061]

如图1~图3所示,引线框架100具有多个单片化区域c通过连结部15连结的构造。连结部15具有外框部151、阻隔条152、以及支撑条153。外框部151设于各单片化区域c的外侧,其具有在引线框架100的外缘部形成为框状的部分、以及在相邻的单片化区域c之间形成为直线状的部分。阻隔条152在各单片化区域c内沿外框部151以包围芯片焊盘11的方式配置为字状。支撑条153在各单片化区域c内倾斜配置。阻隔条152配置在被树脂密封的树脂密封区域d的外侧,支撑条153的大部分配置在树脂密封区域d的内侧。

[0062]

阻隔条152的四角与外框部151的四角连结。在阻隔条152中设有多个引线12。引线12具有自阻隔条152向芯片焊盘11侧延伸的内引线12a、以及自阻隔条152向与内引线12a相反侧延伸的外引线12b。支撑条153的一端与外框部151连结,另一端与芯片焊盘11的四角连结,其支承芯片焊盘11。

[0063]

引线框架100的上表面100a具有用于搭载半导体芯片的第一区域110、以及在第一区域110的周围与密封树脂接触的第二区域120。第一区域110设于芯片焊盘11的大致中心部,具有矩形的俯视形状。第二区域120设于芯片焊盘11的第一区域110的周围、连结部15、以及引线12。第二区域120是上表面100a中的第一区域110之外的区域。例如,芯片焊盘11具有1边的长度为约5mm~15mm的俯视形状,第一区域110具有1边的长度为约4mm~13mm的俯视形状。

[0064]

第二区域120具有粗化区域121和粗化缓和区域122。粗化缓和区域122例如具有字型的俯视形状,其在俯视中沿第一区域110的外缘包围第一区域110。粗化区域121是第二区域120中的粗化缓和区域122之外的部分。因此,粗化缓和区域122设于粗化区域121和第一区域110之间。例如,在俯视中的粗化缓和区域122的宽度为约0.1mm~1.0mm。在粗化区域121中形成有粗化面102,在粗化缓和区域122中未形成粗化面102。粗化缓和区域122的平坦度比粗化区域121的平坦度高,粗化缓和区域122的s比例比粗化区域121的s比例低。例如,

粗化缓和区域122的s比例为1.01~1.10,粗化区域121的s比例为1.05~2.20。图4是示出粗化区域以及粗化缓和区域的扫描型电子显微镜(scanning electron microscopy:sem)照片的例子的图。图4的(a)示出了粗化区域的sem照片的例子,图4的(b)示出了粗化缓和区域的sem照片的例子。对于s比例后述。需要说明的是,图4的(a)中的粗化区域通过氧化处理形成。

[0065]

单片化区域c以及连结部15的下表面100b和侧面的平坦度不特别限定,但是优选为与粗化区域121的平坦度相同程度。优选也在单片化区域c以及连结部15的下表面100b和侧面形成粗化面102。第一区域110的平坦度不特别限定,但是优选例如为与粗化区域121的平坦度相同程度。优选也在第一区域110形成粗化面102。

[0066]

支撑条153被弯曲加工成两个阶段,芯片焊盘11的上表面位于比引线12的上表面靠下侧。芯片焊盘11的上表面与引线12的上表面大致平行。

[0067]

在引线12的内引线12a的顶端的上表面局部形成有电镀膜18。电镀膜18形成于金属线例如通过引线接合而进行连接的部分。电镀膜18例如为ag膜、au膜、ni/au膜(将ni膜和au膜依次层叠的金属膜)、ni/pd/au膜(将ni膜、pd膜以及au膜依次层叠的金属膜)等。需要说明的是,也可以不形成电镀膜18。

[0068]

详细后述,在使用引线框架100来制造半导体装置时,在第一区域110涂敷ag糊料等的粘合剂(芯片附着膏),在粘合剂之上搭载半导体芯片。并且,通过密封树脂覆盖半导体芯片以及引线框架100。

[0069]

在粗化区域121与第一区域110连续的情况下,粘合剂中含有的溶剂成分通过毛细管现象而易于在粗化区域121的表面浸润扩展。若溶剂成分在粗化区域121浸润扩展,则密封树脂与粗化区域121之间的密合性降低。与此相对,在本实施方式中,在第一区域110和粗化区域121之间,设有平坦度比粗化区域121高的粗化缓和区域122。因此,抑制了因溶剂成分的毛细管现象导致的向粗化区域121的浸润扩展。因此,抑制了因粘合剂中含有的溶剂成分导致的密合性的降低,能够在密封树脂和粗化区域121之间获得优异的密合性。

[0070]

图5是示出溶剂成分的浸润扩展被抑制的样子的示意图。在图5中,在第一区域110内的一部分的圆状的区域中作为粘合剂涂敷有ag糊料116。ag糊料116自粗化缓和区域122离开地被涂敷。第一区域110的平坦度为与粗化区域121的平坦度相同程度,第一区域110的平坦度比粗化缓和区域122的平坦度低。因此,ag糊料116中含有的溶剂成分117在第一区域110内在ag糊料116的周围浸润扩展为圆状。另一方面,溶剂成分117没有越过第一区域110与粗化缓和区域122的边界,而是停留在第一区域110内。如此,溶剂成分117向粗化区域121的浸润扩展被抑制。

[0071]

需要说明的是,为了抑制粘合剂中含有的溶剂成分的浸润扩展,也可以考虑在粗化面之上局部涂敷具有疏水性的有机溶剂。但是,担心这样的有机溶剂反而使引线框架与密封树脂的密合性降低。另外,有机溶剂的使用导致成本上升。另外,为了将有机溶剂以期望的量涂敷于期望的位置,花费大量功夫。另外,担心有机溶剂在进行热处理的情况下性质改变。特别是,在一个芯片焊盘11之上搭载多个半导体芯片的情况下,有时进行多次热处理,担心在该情况下性质容易改变。

[0072]

另外,由于可见光的反射率在粗化区域121和粗化缓和区域122之间不同,因此通过眼睛或光学显微镜能够容易确认粗化缓和区域122。与此相对,在涂敷有密合性不降低程

度的量的有机溶剂的情况下,难以确认是否涂敷有有机溶剂。

[0073]

需要说明的是,粗化缓和区域122不需要在第一区域110的周围连续形成。例如,粗化缓和区域122可以在第一区域110的周围断续形成。另外,根据引线12的配置,在俯视中,可以在第一区域110的任一边的附近不设置粗化缓和区域122。

[0074]

这里,对s比例进行说明。图6是示出s比例的计算方法的图。s比例是指,如图6所示,在俯视中的面积为s0的区域t的实际表面积为s的情况下的实际表面积s与面积s0的比。也就是说,s比例由“s/s

0”表示。

[0075]

[引线框架的制造方法]

[0076]

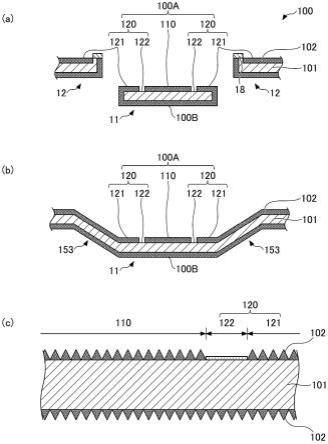

接下来,对第一实施方式的引线框架100的制造方法进行说明。图7~图13是示出第一实施方式的引线框架100的制造方法的图。图7的(a)~图13的(a)为俯视图,图7的(b)~图13的(b)分别为沿图7的(a)~图13的(a)中的i-i线的剖视图。图8~图13示出了一个单片化区域c。

[0077]

首先,如图7所示,准备规定形状的金属制的板材10。板材10是最终沿由虚线所示切割线被切割而针对每个单片化区域c进行单片化的部件。作为板材10的材料,例如能够使用cu、cu合金、42合金等。板材10的厚度能够设定为例如为约100μm~200μm。板材10的表面的s比例例如整体为约1.00~1.03。

[0078]

接下来,如图8所示,在板材10的上表面形成感光性的抗蚀剂161,在板材10的下表面形成感光性的抗蚀剂162。然后,对抗蚀剂161以及162进行曝光以及显影,从而在规定的位置形成开口部161x以及162x。开口部161x以及162x是用于在板材10上形成芯片焊盘11、引线12以及支撑条153的开口部,其彼此在俯视中完全重叠。

[0079]

接下来,如图9所示,将抗蚀剂161以及162作为蚀刻掩模,对板材10进行蚀刻(例如,湿蚀刻)。通过蚀刻,于开口部161x和162x在俯视中重叠形成的部分,板材10贯通。

[0080]

接下来,如图10所示,去除抗蚀剂161以及162。如此,在板材10中形成多个单片化区域c和连结部15。连结部15具有外框部151、阻隔条152以及支撑条153。另外,与外框部151以及阻隔条152连接的多个引线12以包围各单片化区域c内的芯片焊盘11的方式形成。引线12包括内引线12a和外引线12b。板材10的上表面包括第一区域110和第二区域120。

[0081]

接下来,如图11所示,引线12的内引线12a的顶端的上表面局部形成电镀膜18。电镀膜18形成于金属线例如通过引线接合而进行连接的部分。

[0082]

接下来,如图12所示,对板材10的表面整体进行粗化处理。其结果,在板材10的表面形成粗化面102。板材10的残留部成为基部101。粗化面102的表面的s比例根据粗化处理的种类而不同,例如为1.05~2.20。可以在电镀膜18的形成前进行粗化处理。作为粗化处理,例如进行氧化处理、微蚀刻处理、粗化cu电镀处理或粗化ni电镀处理。

[0083]

在氧化处理中,通过将由cu或cu合金构成的板材10在黑化处理液中进行阳极氧化,在其表面形成包括氢氧化物且具有针状结晶的氧化铜的皮膜。也就是说,对板材10的cu进行阳极氧化。通过氧化处理形成的粗化面102的s比例例如为1.05~1.50。

[0084]

在微蚀刻处理中,使用添加了抑制剂且包括硫酸以及过氧化氢的蚀刻液对由cu或cu合金构成的板材10的表面进行蚀刻。在该蚀刻中,抑制剂吸附于板材10的表面,在表面的溶解速度产生差异。因此,优先进行溶解的部分成为凹部,溶解较晚的部分成为凸部。通过微蚀刻处理形成的粗化面102的s比例例如为1.05~1.50。

[0085]

在粗化cu电镀处理中,在使用硫酸铜类的电镀液在板材10的表面进行基于阴极电解的电镀处理时,使高电流密度区域的粗大的结晶局部析出。通过粗化cu电镀处理形成的粗化面102的s比例例如为1.20~2.20。

[0086]

在粗化ni电镀处理中,通过阴极电解依次进行ni电镀、pd电镀、au电镀,在ni电镀时使用包括溴化ni等的卤素的酸性电镀浴。通过使用包括卤素的酸性电镀浴,与不包括卤素的酸性电镀浴相比,能够获得结晶粒较大的ni。通过粗化ni电镀处理形成的粗化面102的s比例例如为1.20~1.80。

[0087]

图14是示出粗化部的sem照片的例子的图。图14的(a)示出了未实施粗化处理的cu素材的sem照片。图14的(b)示出了通过微蚀刻处理获得的粗化部的sem照片的例子。图14的(c)示出了通过氧化处理获得的粗化部的sem照片的例子。图14的(d)示出了通过粗化cu电镀处理获得的粗化部的sem照片的例子。图14的(e)示出了通过粗化ni电镀处理获得的粗化部的sem照片的例子。需要说明的是,在图14的(e)所示样品中,虽然在实施了粗化ni电镀处理后,实施了pd电镀处理以及au电镀处理,但是pd电镀以及au电镀的厚度极薄为约0.005μm~0.05μm。因此,pd电镀以及au电镀沿粗化ni电镀的粗化面形成,粗化面的粗糙度与粗化ni电镀的表面的粗糙度为同等的值。

[0088]

粗化处理后,如图13所示,使用模具(未图示),进行支撑条153的弯曲加工,并且对第二区域120的一部分进行按压来进行缓和粗化的粗化缓和加工。其结果,被模具按压的部分的粗化面102被压溃,被按压的部分的平坦度变得比未被押压的部分的平坦度高,从而在第二区域120形成粗化缓和区域122。第二区域120的未被按压的部分成为粗化区域12。粗化面102例如以约1μm~2μm的深度被压溃。粗化缓和区域122的s比例设定为例如1.01~1.10。压溃粗化面102的加工有时被称为压印加工。

[0089]

如此,能够制造第一实施方式的引线框架100。

[0090]

需要说明的是,不需要同时进行支撑条153的弯曲加工以及第二区域120的粗化缓和加工,可以在支撑条153的弯曲加工之前先进行第二区域120的粗化缓和加工,也可以在第二区域120的粗化缓和加工之前先进行支撑条153的弯曲加工。

[0091]

另外,可以不进行支撑条153的弯曲加工,使芯片焊盘11的上表面与引线12的上表面处于同一平面。

[0092]

(第二实施方式)

[0093]

接下来,对第二实施方式进行说明。第二实施方式涉及使用第一实施方式的引线框架100制造的半导体装置。

[0094]

[半导体装置的构造]

[0095]

首先,对半导体装置的构造进行说明。图15是示出第二实施方式的半导体装置的剖视图。

[0096]

如图15所示,第二实施方式的半导体装置200大致具有引线框架201、半导体芯片20、金属线30(接合线)、以及树脂部40(密封树脂)。

[0097]

引线框架201是引线框架100的单片化区域c的内侧的部分,包括用于搭载半导体芯片20的芯片焊盘11(芯片搭载部)、多个引线12(端子部)、以及支撑条153。引线12与芯片焊盘11在电气上独立,在俯视中,其在芯片焊盘11的周围以规定的间距设有多个。但是,引线12并非必须设于芯片焊盘11的周围4个方向,例如,可以仅设于芯片焊盘11的两侧。引线

12的宽度可以设定为例如约0.2mm。引线12的间距可以设定为例如约0.4mm。

[0098]

半导体芯片20以面朝上的状态搭载于芯片焊盘11之上。半导体芯片20例如可以通过ag糊料等的粘合剂17搭载(芯片接合)于芯片焊盘11之上。形成于半导体芯片20的上表面侧的各电极端子通过金线、铜线等的金属线30与形成于引线12的上表面的电镀膜18电连接(引线接合)。

[0099]

树脂部40设于树脂密封区域d,并且将引线框架201、半导体芯片20以及金属线30密封。各引线12的外引线12b(参照图2)自树脂部40突出。即,树脂部40以使引线12的外引线12b露出的方式将半导体芯片20等密封。引线12的外引线12b成为外部连接端子。引线12的自树脂部40突出的外引线12b被弯曲加工成例如两个阶段。各引线12的内引线12a(参照图2)被树脂部40覆盖。作为树脂部40,例如可以使用在环氧树脂中含有填料的所谓模塑树脂等。

[0100]

需要说明的是,若水分进入半导体装置的树脂部内(树脂部与引线框架的界面),则在将半导体装置安装于安装基板时的回流工序等中,树脂部内的水分急剧膨胀以及气化,担心在树脂部产生裂纹等。若产生这样的裂纹等,则半导体装置被破坏。

[0101]

与此相对,在第二实施方式的半导体装置200中,引线框架201由引线框架100形成,引线框架201包括与树脂部40的密合性优异的粗化区域121。因此,能够抑制上述水分的进入,从而能够抑制半导体装置200的破坏。

[0102]

[半导体装置的制造方法]

[0103]

接下来,对第二实施方式的半导体装置200进行说明。图16~图19是示出第二实施方式的半导体装置200的制造方法的图。图16的(a)~图19的(a)为俯视图,图16的(b)~图19的(b)分别为沿图16的(a)~图19的(a)中的i-i线的剖视图。

[0104]

首先,如图16所示,在各单片化区域c的芯片焊盘11的第一区域110涂敷粘合剂17,以面朝上状态将半导体芯片20搭载于粘合剂17之上,通过加热使粘合剂17固化。由此,半导体芯片20被固定于芯片焊盘11。例如,作为粘合剂17,使用包括环氧类树脂、聚酰亚胺类树脂等的树脂的粘合剂。或者,使用在这些树脂中含有银、铜等的导电性填料的粘合剂17。

[0105]

这里,对粘合剂17中含有的溶剂成分的举动进行说明。图20是示出粘合剂17中含有的溶剂成分的举动的剖视图。如图20所示,由于第一区域110成为粗化面,因此粘合剂17中含有的溶剂成分19通过毛细管现象而在第一区域110内浸润扩展。但是,在第二区域120中,在俯视中沿第一区域110的外缘以包围第一区域110的方式形成有粗化缓和区域122。因此,溶剂成分19不浸润扩展至粗化缓和区域122内,而是停留在第一区域110内。因此,抑制了溶剂成分19向粗化区域121的浸润扩展。

[0106]

半导体芯片20固定后,如图17所示,通过金属线30将形成于半导体芯片20的上表面侧的电极端子与形成于引线12的上表面的电镀膜18电连接。金属线30例如可以通过引线接合而与半导体芯片20的电极端子以及电镀膜18连接。

[0107]

接下来。如图18所示,在树脂密封区域d形成密封引线框架100、半导体芯片20以及金属线30的树脂部40。作为树脂部40,例如,可以使用在环氧树脂中含有填料的所谓模塑树脂等。树脂部40例如能够通过传递模塑法或压缩模塑法等形成。

[0108]

接下来,如图19所示,去除阻隔条152的引线12之间的部分、以及阻隔条152的引线12与支撑条153之间的部分。而且,对外引线12b与外框部151的连接部分、以及支撑条153与

外框部151的连接部分进行切割,针对每个单片化区域c进行单片化。针对被单片化的每个构造体,由引线框架100获得引线框架201。之后,进行引线12的自树脂部40突出的部分的弯曲加工,从而完成多个半导体装置200(参照图15)。

[0109]

(第二实施方式的变形例)

[0110]

接下来,对第二实施方式的变形例进行说明。图21是示出第二实施方式的变形例的半导体装置的剖视图。

[0111]

在第二实施方式的变形例的半导体装置200a中,如图21所示,在芯片焊盘11上设置引线接合部,并且在该引线接合部上形成有电镀膜18a。电镀膜18a可以与电镀膜18同时形成。而且,设有将电镀膜18a和形成于半导体芯片20的上表面侧的作为接地端子使用的电极端子电连接的金属线30a。

[0112]

在半导体装置200a中,例如,将芯片焊盘11作为接地导体使用,可以通过金属线30a将半导体芯片20的接地端子和芯片焊盘11连接。

[0113]

需要说明的是,使用本发明的引线框架的封装的方式不特别限定。本发明的引线框架可以用于例如qfp(quad flat package:)、qfn(quad flat non-leaded package)等的各种封装。

[0114]

以上,对优选实施方式等进行了详细说明,但是不限于上述实施方式等,在不超出权利要求书记载的范围的情况下,能够对上述实施方式等施加各种变形和置换。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。