1.本发明涉及半导体集成电路领域,特别涉及一种金属栅(metal gate,mg)。本发明还涉及一种金属栅的制造方法。

背景技术:

2.在现有半导体产业中,多晶硅广泛地应用于半导体元件如mos晶体管中,一般被作为标准的栅极填充材料。然而,随着mos晶体管尺寸减小,传统多晶硅栅极因硼穿透(boron penetration)效应导致元件效能降低,及难以避免的空乏效应(depletion effect)等问题,使得等效栅极介电层厚度增加、栅极电容值下降,进而导致元件性能衰退等。因此,半导体业界便尝试以新的栅极填充材料,例如利用功函数(work function,wf)金属层来取代传统的多晶硅栅极,功函数金属层顶部还需要叠加金属导电材料层并一起作为金属栅。金属栅的底部往往还需要匹配具有高介电常数层(hk)的栅介质层,具有高介电常数层和金属栅的栅极结构往往称为高介电常数金属栅(hkmg)。

3.在金属栅工艺中,由于关键尺寸的减小,使金属栅的填充难度增加;而且pmos和nmos集成在一起时,往往还会出现功函数金属层的叠加,如pmos的p型功函数金属层的底部还会叠加n型功函数金属层,这都使得金属栅的填充非常具有挑战,往往对工艺填充能力的要求很高,当关键尺寸较小,容易产生金属填充问题,在金属栅中出现空洞,造成良率损失。

4.现有方法是通过适当增大栅极尺寸如宽度,或者降低栅极高度,这样都能降低金属栅填充的栅极凹槽的高宽比,从而能降低填充难度。但是栅极宽度为栅极关键尺寸,和沟道长度对应,故栅极宽度的增加会影响器件的性能;而栅极高度的降低会影响到金属栅极电阻,所以工艺调整的窗口往往很小。

技术实现要素:

5.本发明所要解决的技术问题是提供一种金属栅,能使栅极关键尺寸保持不变或降低的条件下,降低金属栅的填充难度、由于金属栅填充的工艺窗口并提高工艺健康度。为此,本发明还提供一种金属栅的制造方法。

6.为解决上述技术问题,本发明提供的金属栅中,由栅介质层和金属栅叠加形成的栅极结构形成于栅极凹槽中,所述栅极凹槽分成底部凹槽和顶部凹槽。

7.所述底部凹槽由伪栅极结构的去除区域组成,在所述伪栅极结构的侧面形成有侧墙,在所述侧墙外的半导体衬底表面形成有顶部表面和所述伪栅极结构的顶部表面相平的第零层层间膜,所述伪栅极结构去除后,所述侧墙的内侧面组成所述底部凹槽的侧面,所述底部凹槽的宽度由所述伪栅极结构的宽度定义且所述底部凹槽的宽度设置为栅极关键尺寸;所述底部凹槽的高度由所述第零层层间膜和所述伪栅极结构的平坦化工艺调节,通过降低所述底部凹槽的高度降低所述底部凹槽的高宽比且将所述底部凹槽的高宽比调节到使所述金属栅无空洞的填充所述底部凹槽。

8.所述顶部凹槽位于所述底部凹槽的正上方,所述顶部凹槽的宽度大于所述底部凹

槽的宽度且所述顶部凹槽的侧面分别延伸到所述底部凹槽的侧面的外侧;所述顶部凹槽穿过第一介质层,所述第一介质层形成于所述第零层层间膜表面;所述顶部凹槽的高宽比小于所述底部凹槽的高宽比,使所述金属栅无空洞的填充所述顶部凹槽;所述顶部凹槽的高度用于补偿所述底部凹槽的高度降低,使所述金属栅的厚度增加并从而降低栅极电阻。

9.进一步的改进是,所述栅介质层中包括高介电常数层。

10.进一步的改进是,所述金属栅包括功函数金属层和金属导电材料层。

11.进一步的改进是,在所述高介电常数层和所述半导体衬底表面之间还形成有界面层。

12.进一步的改进是,所述栅极结构形成于nmos的形成区域中且为第一栅极结构,所述第一栅极结构中,所述功函数金属层为n型功函数金属层。

13.或者,所述栅极结构形成于pmos的形成区域中且为第二栅极结构,所述第二栅极结构中,所述功函数金属层为p型功函数金属层。

14.进一步的改进是,所述nmos和所述pmos同时集成在同一所述半导体衬底上。

15.进一步的改进是,所述p型功函数金属层仅位于所述pmos的形成区域中。

16.所述n型功函数金属层仅位于所述nmos的形成区域中;或者所述n型功函数金属层也延伸到所述pmos的形成区域,在所述第二栅极结构中,所述n型功函数金属层叠加在所述p型功函数金属层表面上。

17.进一步的改进是,所述金属导电材料层的材料包括al。

18.为解决上述技术问题,本发明提供的金属栅的制造方法包括如下步骤:

19.步骤一、提供完成了第零层层间膜沉积的半导体衬底;在所述半导体衬底上形成有伪栅极结构,在所述伪栅极结构的侧面自对准形成有侧墙,所述第零层层间膜覆盖在所述伪栅极结构和所述侧墙的顶部以及所述侧墙外的所述半导体衬底表面;所述伪栅极结构的宽度为栅极关键尺寸。

20.进行化学进行研磨工艺,使所述伪栅极结构和所述侧墙的顶部的所述第零层层间膜去除以及使所述侧墙外的所述第零层层间膜和所述伪栅极结构的表面相平;所述化学机械研磨工艺还调节平坦化后的所述伪栅极结构的高度;通过降低所述伪栅极结构的高度降低所述伪栅极结构的高宽比。

21.步骤二、形成第一介质层,所述第一介质层形成于所述第零层层间膜、所述伪栅极结构和所述侧墙的表面。

22.步骤三、光刻定义出顶部凹槽的形成区域,对所述第一介质层进行刻蚀形成所述顶部凹槽;所述顶部凹槽位于所述伪栅极结构的正上方,所述顶部凹槽的宽度大于所述伪栅极结构的宽度且所述顶部凹槽的侧面分别延伸到所述伪栅极结构的侧面的外侧。

23.步骤四、去除所述伪栅极结构形成底部凹槽;由所述底部凹槽和所述顶部凹槽叠加形成栅极凹槽。

24.所述底部凹槽的高宽比由所述伪栅极结构的高宽比确定。

25.步骤五、在所述栅极凹槽中形成栅介质层和金属栅并叠加形成栅极结构。

26.所述底部凹槽的高宽比使所述金属栅无空洞的填充所述底部凹槽。

27.所述顶部凹槽的高宽比小于所述底部凹槽的高宽比,使所述金属栅无空洞的填充所述顶部凹槽;所述顶部凹槽的高度还用于补偿所述底部凹槽的高度降低,使所述金属栅

的厚度增加并从而降低栅极电阻。

28.进一步的改进是,步骤五中,所述栅介质层中包括高介电常数层。

29.进一步的改进是,所述金属栅包括功函数金属层和金属导电材料层。

30.进一步的改进是,在形成所述高介电常数层之前,还包括在所述半导体衬底表面形成有界面层。

31.进一步的改进是,所述栅极结构形成于nmos的形成区域中且为第一栅极结构,所述第一栅极结构中,所述功函数金属层为n型功函数金属层;

32.或者,所述栅极结构形成于pmos的形成区域中且为第二栅极结构,所述第二栅极结构中,所述功函数金属层为p型功函数金属层。

33.进一步的改进是,所述nmos和所述pmos同时集成在同一所述半导体衬底上。

34.进一步的改进是,所述p型功函数金属层仅位于所述pmos的形成区域中;

35.所述n型功函数金属层仅位于所述nmos的形成区域中;或者所述n型功函数金属层也延伸到所述pmos的形成区域,在所述第二栅极结构中,所述n型功函数金属层叠加在所述p型功函数金属层表面上。

36.进一步的改进是,所述金属导电材料层的材料包括al。

37.本发明金属栅对应的栅极凹槽并不直接由伪栅极结构去除后形成的凹槽组成,而是将伪栅极结构去除后的凹槽作为底部凹槽,这样能使金属栅的底部宽度依然能由伪栅极结构定义,从而使得金属栅的栅极关键尺寸能得到保持或降低,能使器件的性能得到保持或提高。

38.本发明的金属栅对应的栅极凹槽还包括叠加在底部凹槽之上的顶部凹槽,顶部凹槽是通过对第一介质层进行图形化刻蚀形成,顶部凹槽大于底部凹槽的宽度,使得顶部凹槽比底部凹槽更容易填充;同时,利用顶部凹槽增加整个栅极凹槽的高度,这样,就能使得底部凹槽的高度降低,这样使得底部凹槽的高宽比降低,从而能降低底部凹槽的填充难度,这样,由于底部凹槽和顶部凹槽的填充难度都得到降低,故本发明降低金属栅的填充难度、提高金属栅填充的工艺窗口和提高工艺健康度。

39.另外,本发明在保持栅极关键尺寸不变或降低的条件下,能通过降低底部凹槽的高度来降低底部沟槽的填充难度,但是顶部凹槽能补偿底部凹槽的高度损失,故最后能使金属栅的最终厚度得到保持或提高,从而能使金属栅的电阻得到保持或降低。

40.总之,本发明能解决现有方法中的金属栅填充问题,避免出现栅极金属孔洞,从而能提高良率;不需降低金属栅高度,从而能使金属栅的电阻得到保持或降低;不需要增加栅极关键尺寸,从而能提高器件性能;最后本发明能降低金属栅的填充难度、提高金属栅填充的工艺窗口和提高工艺健康度,改善金属栅质量,提高产品良率。

附图说明

41.下面结合附图和具体实施方式对本发明作进一步详细的说明:

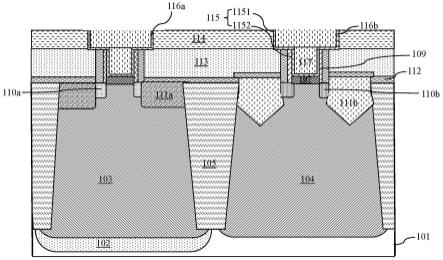

42.图1是本发明实施例金属栅的结构示意图;

43.图2a-图2e是本发明实施例金属栅的制造方法的各步骤中的器件结构示意图。

具体实施方式

44.如图1所示,是本发明实施例金属栅的结构示意图;本发明实施例金属栅中,由栅介质层107和金属栅叠加形成的栅极结构形成于栅极凹槽115中,所述栅极凹槽115分成底部凹槽1152和顶部凹槽1151。

45.所述底部凹槽1152由伪栅极结构106的去除区域组成,所述伪栅极结构106请参考图2a所示,在所述伪栅极结构106的侧面形成有侧墙109,在所述侧墙109外的半导体衬底101表面形成有顶部表面和所述伪栅极结构106的顶部表面相平的第零层层间膜113,所述伪栅极结构106去除后,所述侧墙109的内侧面组成所述底部凹槽1152的侧面,所述底部凹槽1152的宽度由所述伪栅极结构106的宽度定义且所述底部凹槽1152的宽度设置为栅极关键尺寸;所述底部凹槽1152的高度由所述第零层层间膜113和所述伪栅极结构106的平坦化工艺调节,通过降低所述底部凹槽1152的高度降低所述底部凹槽1152的高宽比且将所述底部凹槽1152的高宽比调节到使所述金属栅无空洞的填充所述底部凹槽1152。

46.所述顶部凹槽1151位于所述底部凹槽1152的正上方,所述顶部凹槽1151的宽度大于所述底部凹槽1152的宽度且所述顶部凹槽1151的侧面分别延伸到所述底部凹槽1152的侧面的外侧;所述顶部凹槽1151穿过第一介质层114,所述第一介质层114形成于所述第零层层间膜113表面;所述顶部凹槽1151的高宽比小于所述底部凹槽1152的高宽比,使所述金属栅无空洞的填充所述顶部凹槽1151;所述顶部凹槽1151的高度用于补偿所述底部凹槽1152的高度降低,使所述金属栅的厚度增加并从而降低栅极电阻。

47.本发明实施例中,所述栅介质层107中包括高介电常数层。在所述高介电常数层和所述半导体衬底101表面之间还形成有界面层。在高介电常数层表面上通常还形成有氮化钛覆盖层。故所述栅介质层107是由界面层、高介电常数层和氮化钛覆盖层叠加而成。

48.所述金属栅包括功函数金属层和金属导电材料层117。

49.在所述氮化钛覆盖层和所述功函数金属层之间通常还会形成氮化钽覆盖层,由所述氮化钛覆盖层和所述氮化钽覆盖层叠加形成底部阻障层。

50.形成于nmos的形成区域中的所述栅极结构为第一栅极结构,所述第一栅极结构中,所述功函数金属层为n型功函数金属层116a。

51.形成于pmos的形成区域中的所述栅极结构为第二栅极结构,所述第二栅极结构中,所述功函数金属层为p型功函数金属层116b。

52.所述nmos和所述pmos同时集成在同一所述半导体衬底101上。

53.在所述半导体衬底101上还形成有器件结构,包括:

54.浅沟槽隔离(sti)105,用于在所述半导体衬底101上隔离出有源区。

55.在所述nmos的形成区域中形成有n型深阱(dnw)102,在所述n型深阱102中形成有p型阱(pw)103。

56.在所述pmos的形成区域中形成有n型阱(nw)104。

57.所述nmos还包括:

58.和所述伪栅极结构106自对准的n型浅掺杂漏区110a以及和所述侧墙109自对准的源漏区111a。通常,在所述源漏区111a的形成区域中还会形成第一嵌入式外延层如嵌入式sip层。在所述n型浅掺杂漏区110a的内侧还形成有p型袋型注入区。

59.所述pmos还包括:

60.和所述伪栅极结构106自对准的p型浅掺杂漏区110b以及和所述侧墙109自对准的源漏区111b。通常,在所述源漏区111b的形成区域中还会形成第二嵌入式外延层如嵌入式sige层。在所述n型浅掺杂漏区110b的内侧还形成有n型袋型注入区。

61.所述p型功函数金属层116b仅位于所述pmos的形成区域中。

62.图1中,所述n型功函数金属层116a仅位于所述nmos的形成区域中。在其他实施例中也能为:所述n型功函数金属层116a也延伸到所述pmos的形成区域,在所述第二栅极结构中,所述n型功函数金属层116a叠加在所述p型功函数金属层116b表面上。

63.所述金属导电材料层117的材料包括al。

64.本发明实施例中,在所述第零层层间膜113的底部还形成有一层接触刻蚀停止层(cesl)112,接触刻蚀停止层112通常采用氮化硅层组成。

65.本发明实施例金属栅对应的栅极凹槽115并不直接由伪栅极结构106去除后形成的凹槽组成,而是将伪栅极结构106去除后的凹槽作为底部凹槽1152,这样能使金属栅的底部宽度依然能由伪栅极结构106定义,从而使得金属栅的栅极关键尺寸能得到保持或降低,能使器件的性能得到保持或提高。

66.本发明实施例的金属栅对应的栅极凹槽115还包括叠加在底部凹槽1152之上的顶部凹槽1151,顶部凹槽1151是通过对第一介质层114进行图形化刻蚀形成,顶部凹槽1151大于底部凹槽1152的宽度,使得顶部凹槽1151比底部凹槽1152更容易填充;同时,利用顶部凹槽1151增加整个栅极凹槽115的高度,这样,就能使得底部凹槽1152的高度降低,这样使得底部凹槽1152的高宽比降低,从而能降低底部凹槽1152的填充难度,这样,由于底部凹槽1152和顶部凹槽1151的填充难度都得到降低,故本发明实施例降低金属栅的填充难度、提高金属栅填充的工艺窗口和提高工艺健康度。

67.另外,本发明实施例在保持栅极关键尺寸不变或降低的条件下,能通过降低底部凹槽1152的高度来降低底部沟槽的填充难度,但是顶部凹槽1151能补偿底部凹槽1152的高度损失,故最后能使金属栅的最终厚度得到保持或提高,从而能使金属栅的电阻得到保持或降低。

68.总之,本发明实施例能解决现有方法中的金属栅填充问题,避免出现栅极金属孔洞,从而能提高良率;不需降低金属栅高度,从而能使金属栅的电阻得到保持或降低;不需要增加栅极关键尺寸,从而能提高器件性能;最后本发明实施例能降低金属栅的填充难度、提高金属栅填充的工艺窗口和提高工艺健康度,改善金属栅质量,提高产品良率。

69.如图2a至图2e所示,是本发明实施例金属栅的制造方法的各步骤中的器件结构示意图;本发明实施例金属栅的制造方法包括如下步骤:

70.步骤一、如图2a所示,提供完成了第零层层间膜113沉积的半导体衬底101;在所述半导体衬底101上形成有伪栅极结构106,在所述伪栅极结构106的侧面自对准形成有侧墙109,所述第零层层间膜113覆盖在所述伪栅极结构106和所述侧墙109的顶部以及所述侧墙109外的所述半导体衬底101表面;所述伪栅极结构106的宽度为栅极关键尺寸。

71.进行化学进行研磨工艺,使所述伪栅极结构106和所述侧墙109的顶部的所述第零层层间膜113去除以及使所述侧墙109外的所述第零层层间膜113和所述伪栅极结构106的表面相平;所述化学机械研磨工艺还调节平坦化后的所述伪栅极结构106的高度;通过降低所述伪栅极结构106的高度降低所述伪栅极结构106的高宽比。

72.本发明实施例方法中,所述伪栅极结构106由栅介质层107和多晶硅伪栅108叠加而成。所述栅介质层107作为后续的栅极结构中栅介质层。在其他实施例方法中,所述伪栅极结构106中的所述栅介质层107也能替换为伪栅介质层,伪栅介质层在后续去除所述多晶硅伪栅108时一并被去除。

73.本发明实施例方法中,nmos和pmos同时集成在同一所述半导体衬底101上。

74.在所述半导体衬底101上还形成有器件结构,包括:

75.浅沟槽隔离(sti)105,用于在所述半导体衬底101上隔离出有源区。

76.在所述nmos的形成区域中形成有n型深阱(dnw)102,在所述n型深阱102中形成有p型阱(pw)103。

77.在所述pmos的形成区域中形成有n型阱(nw)104。

78.所述nmos还包括:

79.和所述伪栅极结构106自对准的n型浅掺杂漏区110a以及和所述侧墙109自对准的源漏区111a。通常,在所述源漏区111a的形成区域中还会形成第一嵌入式外延层如嵌入式sip层。在所述n型浅掺杂漏区110a的内侧还形成有p型袋型注入区(未显示)。

80.所述pmos还包括:

81.和所述伪栅极结构106自对准的p型浅掺杂漏区110b以及和所述侧墙109自对准的源漏区111b。通常,在所述源漏区111b的形成区域中还会形成第二嵌入式外延层如嵌入式sige层。在所述n型浅掺杂漏区110b的内侧还形成有n型袋型注入区(未显示)。

82.在所述第零层层间膜113的底部还形成有一层接触刻蚀停止层(cesl)112,接触刻蚀停止层112通常采用氮化硅层组成。

83.步骤二、如图2b所示,形成第一介质层114,所述第一介质层114形成于所述第零层层间膜113、所述伪栅极结构106和所述侧墙109的表面。

84.步骤三、如图2c所示,光刻定义出顶部凹槽1151a的形成区域,对所述第一介质层114进行刻蚀形成所述顶部凹槽1151a;所述顶部凹槽1151a位于所述伪栅极结构106的正上方。

85.本发明实施例方法中,所述顶部凹槽1151a的宽度较小。如图2d所示,之后还需进行:对所述第一介质层114进行横向刻蚀,使所述顶部凹槽1151a的宽度扩大,宽度扩大后的所述顶部凹槽单独采用标记1151表示。在其他实施例方法中,也能在图2c对应的步骤中直接定义较大的所述顶部凹槽1151的尺寸,之后图2d的步骤能省略。

86.如图2d所示,所述顶部凹槽1151的宽度大于所述伪栅极结构106的宽度且所述顶部凹槽1151的侧面分别延伸到所述伪栅极结构106的侧面的外侧。

87.步骤四、如图2e所示,去除所述伪栅极结构106形成底部凹槽1152;由所述底部凹槽1152和所述顶部凹槽1151叠加形成栅极凹槽115。

88.所述底部凹槽1152的高宽比由所述伪栅极结构106的高宽比确定。

89.步骤五、如图1所示,在所述栅极凹槽115中形成栅介质层107和金属栅并叠加形成栅极结构。

90.所述底部凹槽1152的高宽比使所述金属栅无空洞的填充所述底部凹槽1152。

91.所述顶部凹槽1151的高宽比小于所述底部凹槽1152的高宽比,使所述金属栅无空洞的填充所述顶部凹槽1151;所述顶部凹槽1151的高度还用于补偿所述底部凹槽1152的高

度降低,使所述金属栅的厚度增加并从而降低栅极电阻。

92.由于本发明实施例方法中,所述栅介质层107采用先栅介质层工艺,所以,步骤四中,去除所述伪栅极结构106的工艺仅去除所述多晶硅伪栅108,所述栅介质层107保留。

93.所述栅介质层107中包括高介电常数层。在形成所述高介电常数层之前,还包括在所述半导体衬底101表面形成有界面层。在高介电常数层表面上通常还形成有氮化钛覆盖层。故所述栅介质层107是由界面层、高介电常数层和氮化钛覆盖层叠加而成。

94.所述金属栅包括功函数金属层和金属导电材料层117。

95.形成于nmos的形成区域中的所述栅极结构为第一栅极结构,所述第一栅极结构中,所述功函数金属层为n型功函数金属层116a;

96.形成于pmos的形成区域中的所述栅极结构为第二栅极结构,所述第二栅极结构中,所述功函数金属层为p型功函数金属层116b。

97.所述p型功函数金属层116b仅位于所述pmos的形成区域中。

98.所述n型功函数金属层116a仅位于所述nmos的形成区域中。或者所述n型功函数金属层也延伸到所述pmos的形成区域,在所述第二栅极结构中,所述n型功函数金属层116a叠加在所述p型功函数金属层116b表面上。

99.所述金属导电材料层117的材料包括al。

100.以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。