技术特征:

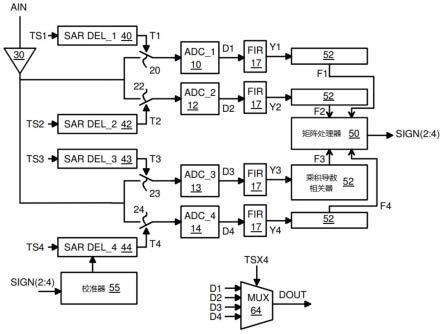

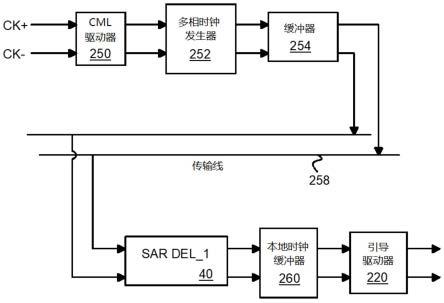

1.一种矩阵校准的交替式模数转换器(adc),包括:n个通道,其中n是至少4的整数,其中所述n个通道中的每个通道包括:用于将采样的模拟输入转换为具有代表所述采样的模拟输入的数字值的数字输出的adc;响应于延迟的时钟,用于对模拟输入进行采样的模拟开关;在校准期间,用延迟值编程的逐次逼近寄存器(sar);具有由存储在所述sar中的所述延迟值控制的可变延迟的可变延迟元件,所述可变延迟元件使输入采样时钟延迟所述可变延迟,以便对所述模拟开关生成所述延迟的时钟;用于使某个通道的所述数字输出与所述多个通道中的相邻通道的所述数字输出相互关联以生成所述通道的乘积导数因子的乘积导数相关器;以及矩阵处理器,它用于接收所述n个通道中的每个通道的所述乘积导数因子,并用于将多个所述乘积导数因子与相关矩阵相乘以生成具有所述n个通道中的n-1个通道的相关符号的符号向量;其中,用延迟值对所述sar编程,以使用逐次逼近校准流程补偿所述n个通道中的时间相位失配,所述逐次逼近校准流程检查所述符号向量中的所述相关符号以确定何时接受或拒绝某个通道的所述sar中与所述符号向量中的所述相关符号对应的测试位。2.如权利要求1所述的矩阵校准的交替式adc,其中,当前通道的所述乘积导数相关器包括:第一样本延迟,它将所述当前通道的所述数字输出延迟样本时钟的一个脉冲以生成第一延迟的样本;第二样本延迟,它将所述当前通道的第一相邻通道的所述数字输出延迟样本时钟的一个脉冲以生成第二延迟的样本;第三样本延迟,它将所述当前通道的第二相邻通道的所述数字输出延迟样本时钟的一个脉冲以生成第三延迟的样本;其中,所述第一相邻通道和所述第二相邻通道位于所述n个通道中;第一加法器,它从所述第二延迟的样本中减去所述第一延迟的样本以生成第一和;以及第一乘数器,它将所述第一和与所述第一延迟的样本相乘以生成第一乘积,所述第一乘积是对于某个样本所述通道的所述乘积导数因子。3.如权利要求2所述的矩阵校准的交替式adc,其中,所述乘积导数相关器进一步包括:平均发生器,用以对所述模拟输入的m个样本中的所述第一乘积求平均,以作为平均的乘积导数因子生成所述乘积导数因子,其中m是整数。4.如权利要求3所述的矩阵校准的交替式adc,其中,每个通道中的所述乘积导数相关器进一步包括:用于对来自所述adc的所述数字输出进行滤波的有限脉冲响应(fir)滤波器,其中所述数字输出是经过滤波的数字输出。5.如权利要求4所述的矩阵校准的交替式adc,其中,n是非二进制数。6.如权利要求4所述的矩阵校准的交替式adc,其中n是奇数。

7.如权利要求4所述的矩阵校准的交替式adc,进一步包括:逐次逼近校准器;所述逐次逼近校准器对于所述符号向量中的每个相关符号,具有:(a)在通道的所述符号向量中具有值为1的对应相关符号时,在所述通道的所述sar添加测试位;(b)在通道的所述符号向量中具有值为0的对应相关符号时,将测试位从所述通道的所述sar中减去;以及,对于所述sar中的下一个比特位置,从(a)开始重复,由此,利用所述符号向量中的所述相关符号来在所述sar中添加或减去连续比特位置。8.如权利要求7所述的矩阵校准的交替式adc,其中,所述逐次逼近校准器将所述多个通道中的参考通道的所述sar设置为固定值;其中,所述逐次逼近校准器不对所述参考通道的所述sar中的所述固定值进行调整,所述逐次逼近校准器调整所述n通道中的其余n-1个通道的所述sar。9.如权利要求4所述的矩阵校准的交替式adc,其中来自所述adc的所述数字输出至少为6位。10.如权利要求2所述的矩阵校准的交替式adc,其中,所述可变延迟元件包括多个二进制加权电容,每个二进制加权电容由所述sar中的一个位启用。11.一种用于减少交替式模数转换器(adc)的通道中的时间相位失配的校准矩阵方法,所述方法包括:将用于设置从模拟输入到交替的adc的可变输入延迟的所有逐次逼近寄存器(sar)中的所有位清零,每个adc对所述模拟输入进行采样并生成adc数字输出;将参考通道的sar中的位设置为中点值;其中,每个通道具有sar、adc和具有由所述sar设置的可变输入延迟的输入延迟元件;(a)对于每个通道:将来自当前通道、来自前一个相邻通道和来自下一个相邻通道的所述adc数字输出输入到乘积导数相关器,所述乘积导数相关器生成用于量化所述当前通道的所述adc数字输出与前一个相邻通道的所述adc数字输出和下一个相邻通道的所述adc数字输出的相关性的采样的乘积导数因子;对所述模拟输入的多个样本中的的乘积导数因子采样结果求平均,以生成所述当前通道的乘积导数因子;将所有通道的所述乘积导数因子排列成因子矩阵;将所述因子矩阵与相关矩阵相乘,以生成具有与通道对应的符号位的符号向量;将当前比特位置设置为所述sar中的第1级的最高有效位(msb)位置;对于除了所述参考通道以外的所有通道:(b)当所述符号向量中与选择的通道对应的符号位为1时,在所述选择的通道的所述sar中的所述当前比特位置处设置测试位以调整所述可变输入延迟;(c)当所述符号向量中与选择的通道对应的所述符号位为0时,在所述选择的通道的所述sar中的所述当前比特位置处清除测试位以调整所述可变输入延迟;从所述当前比特位置降低位次,并从步骤(a)重复,直到所述当前比特位置是所述sar

中的最低有效位(lsb)为止;当已经使用所有乘积导数相关器来调整所述sar中的设置以调整所述可变输入延迟、从而使所有通道中的时间相位失配最小化时,结束校准。12.如权利要求11所述的校准矩阵方法,进一步包括:激活背景校准流程以调整之前通过校准设置的所述sar中的设置,所述背景校准流程包括:(a)对于每个通道:将来自当前通道、来自前一个相邻通道和来自下一个相邻通道的所述adc数字输出输入到乘积导数相关器,所述乘积导数相关器生成用于量化当前通道的所述adc数字输出与前一个相邻通道的所述adc数字输出和下一个相邻通道的所述adc数字输出的相关性的乘积导数因子采样结果;对所述模拟输入的多个样本中的所述乘积导数因子的采样结果求平均,以生成所述当前通道的乘积导数因子;将所有通道的所述乘积导数因子排列成因子矩阵;将所述因子矩阵与相关矩阵相乘,以生成具有与通道对应的符号位的符号向量;将当前比特位置设置为所述sar中的第1级的最高有效位(msb)位置;对于除了所述参考通道以外的所有通道:(b)当所述符号向量中与选择的通道对应的所述符号位为1并且来自前一次迭代的所述符号位为1时,在所述选择的通道的所述sar中的最低有效位(lsb)比特位置处添加lsb测试位以调整所述可变输入延迟;(c)当所述符号向量中与所述选择的通道对应的所述符号位为0并且对于前一次迭代所述符号位为0时,在所述选择的通道的所述sar中的所述lsb比特位置处减去所述lsb测试位以调整所述可变输入延迟;从步骤(a)重复,直到到达终点。13.如权利要求11所述的校准矩阵方法,其中,并行校准同一级中的所有乘积导数相关器。14.如权利要求11所述的校准矩阵方法,其中,重复利用一个乘积导数相关器硬件来实现串行处理的多级乘积导数相关器。15.一种校准矩阵交替式模数转换器(adc),包括:n个通道,其中n是至少3的整数,每个通道包括:具有采样的模拟输入和数字输出的adc;模拟输入和所述采样的模拟输入之间的采样开关,所述采样开关响应于延迟的时钟;用于存储延迟设置的逐次逼近寄存器(sar);用于在输入时钟和所述延迟的时钟之间生成可变延迟的延迟元件,其中所述可变延迟由所述sar中的所述延迟设置确定;用于从所述adc的所述数字输出生成经过滤波的通道输出的滤波器;用于接收某个通道的所述经过滤波的通道输出和来自相邻通道的所述经过滤波的通道输出的乘积导数相关器,所述乘积导数相关器生成指示所述通道与所述相邻通道的相关性的乘积导数因子;

矩阵处理器,所述矩阵处理器从所述n个通道的所述乘积导数相关器接收多个所述乘积导数因子,并通过将所述多个所述乘积导数因子与相关矩阵相乘来生成符号位向量;以及校准器,所述校准器使用所述符号位向量中的每个符号位来决定何时在某个通道的所述sar中添加测试位以及何时从所述通道的所述sar中移除所述测试位,其中,所述符号位向量中的每个符号位用于向所述n个通道的不同通道中的sar添加或移除测试位。16.如权利要求15所述的校准矩阵交替式adc,其中,所述矩阵处理器将来自所述n个通道的多个所述乘积导数因子形成为具有n行和1列的乘积导数因子矩阵,其中,所述相关矩阵具有n-1行和n列,并且所述符号位向量具有n-1个符号位。17.如权利要求16所述的校准矩阵交替式adc,其中,所述相关矩阵由具有n行和n-1列的移位矩阵生成,其中,所述相关矩阵是所述移位矩阵的转置除以所述移位矩阵的转置和所述移位矩阵的乘积。18.如权利要求15所述的校准矩阵交替式adc,其中,所述相邻通道包括2个邻接通道,其中,所述乘积导数相关器生成指示所述通道与所述2个邻接通道的相关性的所述乘积导数因子。19.如权利要求15所述的校准矩阵交替式adc,其中,所述乘积导数相关器进一步包括:平均器,所述平均器用于对m个模拟输入样本,来自所述乘积导数相关器的样本乘积导数因子求平均,从而生成输出到所述矩阵处理器的所述乘积导数因子,其中m是整数。20.如权利要求15所述的校准矩阵交替式adc,其中,所述校准器进一步包括:测试器,所述测试器用于对于在所述符号位向量中具有值为1的所述符号位的所有通道在所述sar中设置测试位,用于对于在所述符号位向量中具有值为0的所述符号位的所有通道在所述sar中清除所述测试位,并且对于所述sar中相邻的比特位置进行重复上述操作;由此,利用每个通道的所述符号位来在所述sar中添加或减去连续的比特位。

技术总结

一种具有添加到每个ADC的输入采样时钟中的可变延迟的N-通道交替式模数转换器(ADC)。在校准期间,这些可变延迟均由逐次逼近寄存器(SAR)进行编程,以便使通道之间的时间相位失配最小化。在每个通道中,对ADC输出进行滤波,并且乘积导数相关器生成两个相邻ADC通道相关性的乘积导数因子。矩阵处理器将来自乘积导数相关器的乘积导数因子排列成矩阵,将该矩阵乘以相关矩阵。相关矩阵是由N

技术研发人员:骆智峯 李志俊

受保护的技术使用者:奇力士技术有限公司

技术研发日:2022.04.06

技术公布日:2022/6/21

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。