一种fa级输入偏置电流的运算放大器

【技术领域】

1.本发明涉及模拟集成电路设计领域,尤其涉及一种fa级输入偏置电流的运算放大器。

背景技术:

2.在静电计等高精度电流前端设备的应用场合下,需要对fa级别的微弱电流信号进行检测。为了对上述fa级别的微弱电流信号进行精确检测,首先需要对微弱电流信号进行放大。而对微弱电流信号进行放大与检测的难点在于待检测电流信号自身十分微弱,容易受到电路中漏电流的干扰,其中漏电流主要包括来自印刷电路板pcb上的漏电流或者芯片内部静电防护器件esd的漏电流。此外漏电流通常可达数十pa的级别,这样会覆盖淹没只有fa级别的待检测电流信号。

3.虽然现有技术可通过在电路内部设置一个缓冲器,用于跟随输入共模电压,并且缓冲器的输出端与静电防护器件esd的另一端连接,使得静电防护器件esd两端的电压被缓冲器的输出钳位至零伏,从而对漏电流进行屏蔽处理。上述屏蔽处理的过程不仅需要高精度的运算放大其充当缓冲器,而且对运算放大器的失调电压有较高的要求,通常需要借助trim技术对运算放大器的失调电压进行校准,从而增大了芯片的面积与功耗开销,以及增加芯片内部电路的设计复杂性。

技术实现要素:

4.本发明的目的在于提供一种fa级输入偏置电流的运算放大器,其通过在主运算放大器模块输入端设置互补源级跟随器电路模块,对静电防护器件esd两端的电压进行钳位,其中使用互补源级跟随器电路模块的面积与功耗开销更小,并且还简化可芯片内部电路设计的复杂性和提高运算放大器工作的可靠性。

5.本发明的目的是通过以下技术方案实现:

6.一种fa级输入偏置电流的运算放大器,所述运算放大器分别与正电源v

dd

、负电源v

ss

、同相输入端v

in

、反相输入端v

in-和保护输出端grd连接;其包括:

7.esd保护电路模块,所述esd保护电路模块包括若干相互连接的二极管,限流电阻r1,限流电阻r2,防闩锁电阻r3;

8.互补源级跟随器电路模块,所述互补源级跟随器电路模块包括相互级联的nmos源级跟随器和pmos源级跟随器;所述互补源级跟随器电路模块分别与正电源v

dd

、负电源v

ss

、限流电阻r1、限流电阻r2连接;

[0009]vgs

校准电路模块,所述v

gs

校准电路模块包括v

gs

校准逻辑电路;所述v

gs

校准电路模块与所述互补源级跟随器电路模块连接,用于调整pmos源级跟随器的栅源电压;

[0010]

主运算放大电路模块a1,所述主运算放大电路模块a1分别与限流电阻r1、限流电阻r2连接;所述主运算放大电路模块a1用于进行电流放大。

[0011]

在其中一实施例中,所述esd保护电路模块包括相互连接的二极管d1、二极管d2、

二极管d3、二极管d4、二极管d5、二极管d6;二极管d1的阳极与保护输出端grd连接,阴极与同相输入端v

in

连接;二极管d2的阳极与同相输入端v

in

连接,阴极与保护输出端grd连接;二极管d3的阳极与反相输入端v

in-连接,阴极与保护输出端grd连接;二极管d4的阳极与保护输出端grd连接,阴极与反相输入端v

in-连接;二极管d5的阳极与保护输出端grd连接,阴极与正电源v

dd

连接;二极管d6的阳极与负电源v

ss

连接,阴极与保护输出端grd连接。

[0012]

在其中一实施例中,所述限流电阻r1的一端与同相输入端v

in

连接,另一端与所述主运算放大电路模块a1的同相输入端连接;所述限流电阻r2的一端与反相输入端v

in-连接,另一端与所述主运算放大电路模块a1的反相输入端连接。

[0013]

在其中一实施例中,所述防闩锁电阻r3的一端与保护输出端grd连接,另一端与所述互补源级跟随器电路模块的输出端连接。

[0014]

在其中一实施例中,所述nmos源级跟随器包括nmos晶体管m1和可变电流源i1;所述pmos源级跟随器包括pmos晶体管m2和电流源i2。

[0015]

在其中一实施例中,所述nmos晶体管m1的栅极与所述主运算放大电路模块a1的同相输入端连接;所述nmos晶体管m1的漏极与正电源v

dd

连接;所述nmos晶体管m1的源极通过可变电流源i1与负电源v

ss

连接。

[0016]

在其中一实施例中,所述pmos晶体管m2的栅极与nmos晶体管m1的源级连接;所述pmos晶体管m2的漏极与负电源v

ss

连接,所述pmos晶体管m2的漏极还通过限流电阻r2与保护输出端grd连接;所述pmos晶体管m2的源极通过电流源i2与正电源v

dd

连接。

[0017]

在其中一实施例中,所述v

gs

校准电路模块的v

gs

校准逻辑电路与所述可变电流源i1连接,用于调整所述可变电流源i1的电流大小,从而使nmos晶体管m1的栅源电源与所述pmos晶体管m2的栅源电压的绝对值相等。

[0018]

在其中一实施例中,当v

gs

校准逻辑电路增大所述可变电流源i1的电流时,所述nmos晶体管m1的栅源电压相应增大;当v

gs

校准逻辑电路减小所述可变电流源i1的电流时,所述nmos晶体管m1的栅源电压相应减小。

[0019]

与现有技术相比,本发明具有如下有益效果:

[0020]

本技术提供的fa级输入偏置电流的运算放大器,通过在主运算放大器模块输入端设置互补源级跟随器电路模块,对静电防护器件esd两端的电压进行钳位,其中使用互补源级跟随器电路模块的面积与功耗开销更小,并且还简化可芯片内部电路设计的复杂性和提高运算放大器工作的可靠性。

【附图说明】

[0021]

为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。其中:

[0022]

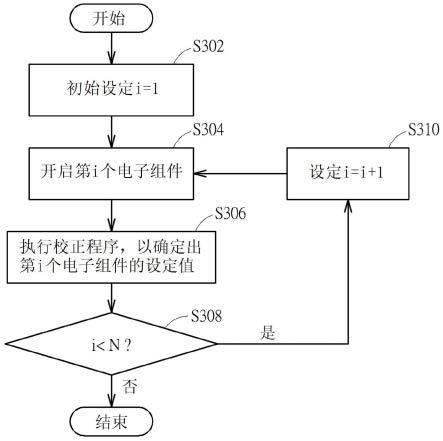

图1是本技术提供的fa级输入偏置电流的运算放大器的结构框图。

[0023]

图2是图1所示的fa级输入偏置电流的运算放大器的电路原理图。

[0024]

图3是现有技术中未设置esd保护电路模块的运算放大器的漏电流随输入共模电压的变化曲线示意图。

[0025]

图4是图1所示的fa级输入偏置电流的运算放大器的漏电流随输入共模电压的变化曲线示意图。

【具体实施方式】

[0026]

为使本技术的上述目的、特征和优点能够更为明显易懂,下面结合附图,对本技术的具体实施方式做详细的说明。可以理解的是,此处所描述的具体实施例仅用于解释本技术,而非对本技术的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本技术相关的部分而非全部结构。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本技术保护的范围。

[0027]

本技术中的术语“包括”和“具有”以及它们任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可选地还包括没有列出的步骤或单元,或可选地还包括对于这些过程、方法、产品或设备固有的其它步骤或单元。

[0028]

在本文中提及“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本技术的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合。

[0029]

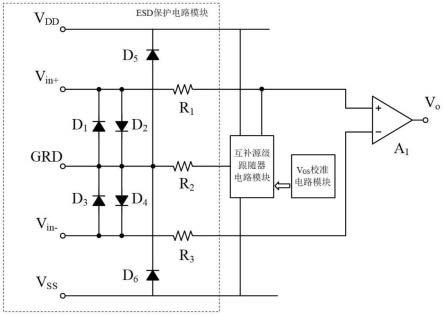

请参阅图1至图2所示,本技术一实施例提供的fa级输入偏置电流的运算放大器,其包括esd保护电路模块,互补源级跟随器电路模块,v

gs

校准电路模块,主运算放大电路模块a1。

[0030]

esd保护电路模块用于当运算放大器与静电防护器件esd连接时,对静电防护器件esd进行漏电流屏蔽,从而降低静电防护器件esd中漏电流的干扰。

[0031]

互补源级跟随器电路模块用于当运算放大器与静电防护器件esd连接时,对静电防护器件esd两端的电压进行钳位,使得静电防护器件esd两端的电压被钳位至零伏。

[0032]vgs

校准电路模块用于对互补源级跟随器电路模块中晶体管的栅源电压进行校准,使得互补源级跟随器电路模块能够对静电防护器件esd进行精确的电压钳位,提高互补源级跟随器电路模块的工作精确性和可靠性。

[0033]

主运算放大电路模块a1用于对待检测电流信号进行放大,并通过其输出端vo向外输出放大的待检测电流信号。。

[0034]

此外,该fa级输入偏置电流的运算放大器还分别与正电源v

dd

、负电源v

ss

、同相输入端v

in

、反相输入端v

in-和保护输出端grd连接。其中,正电源v

dd

和负电源v

ss

为运算放大器的正常工作提供稳定的正电源和负电源供电。同相输入端v

in

和反相输入端v

in-则为运算放大器的正常工作提供稳定的同相输入信号和反向输入信号。保护输出端grd则为esd保护电路模块输出进行保护。

[0035]

请继续参阅图1至图2,esd保护电路模块包括若干相互连接的二极管,限流电阻r1,限流电阻r2,防闩锁电阻r3。其中esd保护电路模块可具体包括六个二极管,即二极管d1、二极管d2、二极管d3、二极管d4、二极管d5、二极管d6。二极管d1的阳极与保护输出端grd连接,阴极与同相输入端v

in

连接;二极管d2的阳极与同相输入端v

in

连接,阴极与保护输出端grd连接;二极管d3的阳极与反相输入端v

in-连接,阴极与保护输出端grd连接;二极管d4的

阳极与保护输出端grd连接,阴极与反相输入端v

in-连接;二极管d5的阳极与保护输出端grd连接,阴极与正电源v

dd

连接;二极管d6的阳极与负电源v

ss

连接,阴极与保护输出端grd连接。

[0036]

此外,限流电阻r1的一端与同相输入端v

in

连接,另一端与主运算放大电路模块a1的同相输入端连接。限流电阻r2的一端与反相输入端v

in-连接,另一端与主运算放大电路模块a1的反相输入端连接。防闩锁电阻r3的一端与保护输出端grd连接,另一端与互补源级跟随器电路模块的输出端连接。

[0037]

互补源级跟随器电路模块包括相互级联的nmos源级跟随器和pmos源级跟随器。互补源级跟随器电路模块分别与正电源v

dd

、负电源v

ss

、限流电阻r1、限流电阻r2连接。nmos源级跟随器可包括但不限于nmos晶体管m1和可变电流源i1,可变电流源i1能够在v

gs

校准电路模块的校准作用下输出可变的电流。pmos源级跟随器可包括但不限于pmos晶体管m2和电流源i2,电流源i2可为但不限于是恒电流源。

[0038]

具体而言,nmos晶体管m1的栅极与主运算放大电路模块a1的同相输入端连接;nmos晶体管m1的漏极与正电源v

dd

连接;nmos晶体管m1的源极通过可变电流源i1与负电源v

ss

连接。pmos晶体管m2的栅极与nmos晶体管m1的源级连接;pmos晶体管m2的漏极与负电源v

ss

连接,pmos晶体管m2的漏极还通过限流电阻r2与保护输出端grd连接;pmos晶体管m2的源极通过电流源i2与正电源v

dd

连接。

[0039]vgs

校准电路模块包括v

gs

校准逻辑电路。其中,v

gs

校准电路模块与互补源级跟随器电路模块连接,用于调整pmos源级跟随器的栅源电压。具体而言,v

gs

校准逻辑电路与可变电流源i1连接,用于调整可变电流源i1的电流大小,从而使nmos晶体管m1的栅源电源与所述pmos晶体管m2的栅源电压的绝对值相等。当v

gs

校准逻辑电路增大可变电流源i1的电流时,nmos晶体管m1的栅源电压相应增大;当v

gs

校准逻辑电路减小可变电流源i1的电流时,nmos晶体管m1的栅源电压相应减小。通过v

gs

校准逻辑电路对可变电流源i1的输出电流进行调整,可同步调整nmos晶体管m1的栅源电压,而当nmos晶体管m1的栅源电源与pmos晶体管m2的栅源电压的绝对值相等时,运算放大器的输入偏置电流达到最小值。通过上述调整方式,能够在不需要设计复杂电路的情况下,也能够准确地对静电防护器件esd两端的电压进行钳位,提高运算放大器整体的工作稳定性和可靠性。

[0040]

主运算放大电路模块a1,作为运算放大器的功能部件,其用于对电流进行放大。其中,互补源级跟随器电路模块和v

gs

校准电路模块两者共同作用。使得主运算放大电路模块a1的输入偏置电流达到最小值,这样能够有效对主运算放大电路模块a1在进行电流放大过程中屏蔽漏电流的干扰,提高主运算放大电路模块a1放大后的电流的信噪比。

[0041]

请参阅图3所示,在现有技术中未设置esd保护电路模块的运算放大器工作过程中,当输入共模电压从1.0v增大到3.3v过程中,运算放大器的漏电流从1.49pa变化至-0.81pa。相应地,请参阅图4所示,在本技术的fa级输入偏置电流的运算放大器工作过程中,当输入共模电压从1.0v增大到3.3v过程中,运算放大器的漏电流从91.43fa变化至-109.73fa,整体降低了11.5倍。可见,本技术的fa级输入偏置电流的运算放大器相比于现有技术未设置esd保护电路模块的运算放大器,在相同输入共模电压变化的条件下,能够使运算放大器的漏电流具有更加显著的降低,从而有效降低漏电流对运算放大器的干扰影响。

[0042]

上述仅为本发明的一个具体实施方式,其它基于本发明构思的前提下做出的任何

改进都视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。