1.本文中描述的示例一般来说涉及用于诸如双列直插式存储器模块(dual in-line memory module,dimm)之类的存储器模块的篡改检测和保护的技术。

背景技术:

2.双列直插式存储器模块(dimm)通常部署在计算平台(例如,服务器)中来提供系统存储器。一些类型的dimm被设计成包括永久类型的存储器,该永久类型的存储器包括能够在断电之后维持数据状态的非易失性存储器设备或管芯。与仅包括易失性存储器设备的非永久性dimm相比,在断电之后维持数据状态的dimm可能会对数据造成更大的安全风险。例如,非永久性dimm在断电时会丢失数据状态,并且在从计算平台移除时,对数据结果几乎不造成或不造成安全风险。然而,在永久性dimm断电之后,数据状态不会丢失,并且dimm可能会从计算平台中移除,并且可能会尝试从非易失性存储器设备中提取数据。

技术实现要素:

3.根据本公开的一个实施例,提供了一种装置,包括:控制器,驻留在存储器模块的印刷电路板(pcb)上,所述控制器包括电路用于:响应于所述存储器模块的第一次启动,确定在散热器盖的一侧上喷涂的字符图案的第一电阻值,所述一侧面向驻留在所述pcb的第一侧上的非易失性存储器设备,其中,所述字符图案是使用导电墨进行喷涂的;响应于所述存储器模块的第二次启动,确定所述字符图案的第二电阻值;以及基于在阈值电阻值内所述第二电阻值不匹配所述第一电阻值,断言所述电路能够访问的寄存器的位,以指示对所述存储器模块的篡改。

4.根据本公开的另一个实施例,提供了一种方法,包括:在存储器模块的第一次启动之后,确定在散热器盖的一侧上喷涂的字符图案的第一电阻值,所述一侧面向驻留在所述存储器模块的印刷电路板(pcb)的第一侧上的非易失性存储器设备,其中,所述字符图案是使用导电墨进行喷涂的;在所述存储器模块的第二次启动之后,确定所述字符图案的第二电阻值;以及基于在阈值电阻值内所述第二电阻值不匹配所述第一电阻值,断言控制器的电路能够访问的寄存器的位,以指示对所述存储器模块的篡改,所述控制器驻留在所述pcb的所述第一侧或第二侧。

5.根据本公开的另一个实施例,提供了至少一种机器可读介质,包括多个指令,所述多个指令响应于被系统执行,使得所述系统执行上述方法。

6.根据本公开的另一个实施例,提供了一种设备,包括用于执行上述方法的装置。

7.根据本公开的另一个实施例,提供了一种双列直插式存储器模块(dimm),包括:印刷电路板(pcb);第一非易失性存储器设备,驻留在所述pcb的第一侧上;第二非易失性存储器设备,驻留在所述pcb的第二侧上;第一散热器盖,在面向所述第一非易失性存储器设备的一侧上喷涂有第一字符图案,其中,所述第一字符图案是使用导电墨进行喷涂的;第二散热器盖,在面向所述第二非易失性存储器设备的一侧上喷涂有第二字符图案,其中,所述第

二字符图案是使用导电墨进行喷涂的;以及控制器,驻留在所述pcb的所述第一侧上,所述控制器包括电路用于:响应于所述dimm的第一次启动,确定所述第一字符图案和所述第二字符图案的第一电阻值;响应于所述dimm的第二次启动,确定所述第一字符图案和所述第二字符图案的第二电阻值;以及基于在阈值电阻值内所述第二电阻值不匹配所述第一电阻值,断言所述电路能够访问的寄存器的位,以指示对所述dimm的篡改。

附图说明

8.图1图示了示例系统。

9.图2图示了模块的第一示例图。

10.图3图示了模块的第二示例图。

11.图4图示了用于测量字符图案的电阻的子系统的第一示例。

12.图5图示了示例寄存器表。

13.图6图示了用于测量字符图案的电阻的子系统的第二示例。

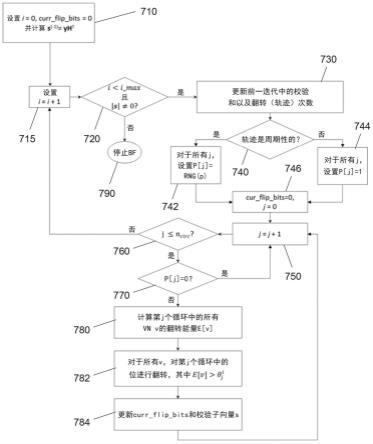

14.图7图示了示例第一逻辑流程。

15.图8图示了示例第二逻辑流程。

16.图9图示了示例装置。

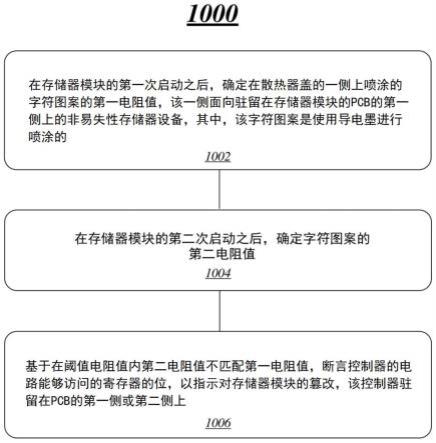

17.图10图示了示例第三逻辑流程。

18.图11图示了示例存储介质。

19.图12图示了示例计算平台。

具体实施方式

20.如本公开所预期,与仅包括易失性存储器设备的非永久性dimm相比,在断电之后维持数据状态的永久性dimm可能会对数据造成更大的安全风险。一些用于减轻这些风险的技术可以包括使用绕存储器模块(诸如,永久性dimm)缠绕的防篡改带。可以通过目视检查防篡改带来检测对存储器模块的任何篡改。例如,断带部分造成断带部分周围的颜色变化。然而,一些类型的永久性dimm可能具有能够使防篡改带无效(例如,熔化)和/或干扰热缓解的操作热特性,该永久性dimm诸如包括具有3维(3d)交叉点存储器结构的字节或块可寻址类型的非易失性存储器,该3d交叉点存储器结构包括但不限于硫族化物相变材料(例如,硫族化物玻璃),在下文中被称为“3d交叉点存储器”。虽然防篡改带可以被设计成对具有硫族化物3d交叉点存储器的永久性dimm的操作热特性有效,但是这些带技术可能无法提供任何类型的电子检测和信令(signaling)。此外,防篡改带仅提供篡改的直观指示,并不能阻止对手提取数据。

21.其他技术可以包括诸如篡改开关之类的篡改机构。当对手试图物理篡改存储器模块时,篡改开关可以响应于机械扰动而被触发。一旦被触发,篡改开关就即激活篡改电路以擦除数据。这些篡改机构技术的可靠性和敏感性可能有限。例如,将触发器设置为捕获相对较小的机械扰动可能会导致在正常操作期间触发篡改开关。然而,将触发器调整到更高水平的机械扰动可能会增加对手击败篡改开关的可能性。

22.一种用于军事或高安全政府情报机构的独特篡改机构可以在存储器模块中包括篡改振动传感器。触发篡改振动传感器会引起受控爆炸,物理粉碎存储器模块。存储器模块

的爆炸性破碎可以保护数据,但是会破坏存储器模块,并且对于能够使用永久性dimm的大多数类型的操作来说,可能并不是合适的解决方案。

23.图1图示了示例系统100。在一些示例中,如图1中所示,系统100包括电路板101(例如,印刷电路板)。如图1中所示,电路板101可以包括处理器插口110-1和110-2以及模块112-1至112-16。系统100例如可以包括在计算平台中,所述计算平台包括但不限于服务器。对于这些示例,模块112-1至112-16可以被配置为插入在电路板101上的插槽(未示出)中的dimm。模块112-1至112-16可以被配置为与电子设备工程联合协会(jedec)颁布的一个或多个标准中描述的dimm形状因子相似的dimm。例如,jedec描述了与jesd79-4a(ddr4)或jesd 79-5(ddr5)标准相关联的dimm形状因子。

24.模块112-1至112-16可以仅包括永久性dimm,或者可以包括永久性和非永久性dimm的任何组合。在一个示例中,模块112-1至112-7可以被布置为与插入在处理器插口110-1中的第一处理器(未示出)耦合,并且模块112-8至112-16可以被布置为与插入在处理器插口110-2中的第二处理器(未示出)耦合。如下文更详细描述的,包括在模块112-1至112-16中的永久性存储器模块可以被制成包括无源和有源篡改检测元件的组合,用于保护驻留在这些永久性存储器模块上的非易失性存储器设备中存储的数据。例如,数据是由插入在处理器插口110-1和110-2中的第一处理器或第二处理器在执行应用或处理应用负载时生成的。

25.图2图示了模块200的第一示例图。在一些示例中,如图2中所示,第一示例图包括描绘模块200的两个单独侧的视图的侧视图201和侧视图202。如图2中所示,侧视图201示出了设备盖210-1。非易失性存储器(nvm)设备230-1至230-6的虚线指示这些存储器设备位于设备盖210-1的后面(不可见)。控制器240的虚线指示控制器240也位于设备盖210-1的后面。nvm设备230-1至230-6和控制器240可以与印刷电路板(pcb)220附接到或耦合,该印刷电路板(pcb)220的一部分在模块200的底部边缘处可见。侧视图201还示出了可以与包括在电路板(例如,电路板110)的插槽中的第一组触点耦合的触点220-1。模块200可以与在一个或多个jedec标准(诸如但不限于jesd79-4a(ddr4)标准或jesd 79-5(ddr5)标准)中描述的dimm的形状因子相似。触点220-1可以与jesd79-4a(ddr4)或jesd 79-5(ddr5)标准中描述的方式相似地布置。

26.如图2中所示,侧视图202示出了设备盖210-2。非易失性存储器(nvm)设备230-7至230-12的虚线指示这些存储器设备位于设备盖210-2的后面(不可见)。易失性存储器设备250的虚线也指示易失性存储器设备250位于设备盖210-2的后面。nvm设备230-1至230-6和易失性存储器设备250可以与印刷电路板(pcb)220附接到或耦合,该印刷电路板(pcb)220的一部分在模块200的底部边缘处可见。侧视图202示出了可以与包括在电路板(例如,电路板110)的插槽中的第二组触点耦合的触点220-2。如上文针对触点220-1提到的,触点220-2可以与jesd79-4a(ddr4)或jesd 79-5(ddr5)标准中描述的方式相似地布置。

27.在一些示例中,设备盖210-1和设备盖210-2可以用作散热器,用于在模块200正在操作(例如,通电)的同时,促进从nvm设备230-1至230-12、控制器240或易失性存储器设备250生成的热能的消散。对于这些示例,设备盖210-1和210-2可以是一种类型的金属板,或者是能够吸收和消散至少一部分生成的热能的其他类型的材料。金属的示例类型可以包括但不限于阳极氧化铝。

28.根据一些示例,易失性存储器设备250可以用作一种类型的缓冲器或缓存,用于对nvm设备230-1至230-12进行读或写访问。虽然在图2中未示出,但是模块200可以包括掉电在即(power loss imminent,pli)电路(例如,电池和/或电容器,未示出),用于使存储在易失性存储器设备250中的数据能够移动到非易失性存储器设备,作为预期或意外断电或掉电(power loss)事件的一部分。响应于pli事件保存数据的能力可以将模块200分类为一种类型的永久性存储器模块。

29.如本文中所公开的,提及的诸如nvm设备230-1至230-12的非易失性存储器设备可以包括一个或多个不同的非易失性存储器类型,该一个或多个不同的非易失性存储器类型可以是字节或块可寻址类型的非易失性存储器,诸如3d交叉点存储器。非易失性类型的存储器还可以包括其他类型的字节或块可寻址非易失性存储器,诸如但不限于单级或多级相变存储器(pcm)、电阻式存储器、纳米线存储器、铁电晶体管随机存取存储器(fetram)、反铁电存储器、包括金属氧化物基的电阻式存储器、氧空位基和导电桥接随机存取存储器(cb-ram)、自旋电子磁结存储器、磁隧道结(mtj)存储器、域壁(dw)和自旋轨道转移(sot)存储器、基于晶闸管的存储器、合并了忆阻器技术的磁阻式随机存取存储器(mram)、自旋转移矩mram(stt-mram)、或上述任何存储器的组合。

30.如本文中所公开的,提及的诸如易失性存储器设备250之类的易失性存储器设备可以包括一个或多个不同的易失性存储器类型。易失性类型的存储器包括但不限于随机存取存储器(ram)、动态ram(dram)、双倍数据速率同步动态ram(ddr sdram)、静态随机存取存储器(sram)、晶闸管ram(t-ram)、或零电容ram(z-ram)。

31.图3图示了模块200的第二示例视图。在一些示例中,如图3中所示,第二示例视图包括描绘模块200的两个单独侧的视图的侧视图301和侧视图302,其中,相应的设备盖210-1和210-2被移除和翻转以示出背面。对于这些示例,设备盖210-1可以具有字符图案360,并且设备盖210-2可以具有字符图案370。字符图案360和370可以是同一图案或分开图案,代表每模块唯一字符图案,其可以在模块200的制造和/或组装期间通过在相应的设备盖210-1和210-2的背面上喷涂(spraying)、涂刷(painting)或绘制(drawing)导电墨而生成。每模块唯一字符图案例如可以包括字母字符、数字字符或符号字符。每模块唯一字符图案中包括的字符可以以连接字符以使电流能够从输入触点流动到输出触点的方式布置。例如,对于字符图案360来说,从输入触点362到输出触点364,或者对于字符图案370来说,从输入触点372到输出触点374。导电墨可以包括但不限于碳墨、导电聚合物墨、或金属纳米粒子墨(例如,铜、银或金)。在一些示例中,导电墨可以是与设备盖210-1和210-2的背面颜色相匹配的颜色,或者是透明/无色,以使字符图案360和370几乎不可见。图3中示为黑色“pattern”,以更清楚地描绘在设备盖210-1和210-2的背面上喷涂、涂刷或绘制的连接字符。

32.根据一些示例,如图3中所示,侧视图301示出了pcb 220包括输入短截线(stub)320和输出短截线322。对于这些示例,当设备盖210-1位于pcb 220之上时,输入短截线320将连接到输入触点362,并且输出短截线322将连接到输出触点364。可以与nvm设备230-1至230-6紧密接触地放置设备盖210-1。输入短截线320和输出短截线322可以具有足够的高度以升至高于nvm设备230-1至230-6的高度,以便与相应的输入触点362和输出触点364耦合。如下文更详细描述的,控制器240包括电路241。电路241可以包括电路或逻辑,用于基于通

过输入短截线320/输入触点362施加的输入电压和对应输入电流、字符图案360、和通过输出触点364/输出短截线322输出的结果输出电压和电流,来确定字符图案360的电阻值。并且,如下文更详细描述的,控制器240可以包括控制寄存器(cr)242,该cr 242由电路241的电路或逻辑用于存储字符图案360的确定电阻值。在一些示例中,控制器240的电路241可以包括附加电路或逻辑,诸如但不限于模数转换器(adc)(未示出),用于将测量的电阻值转换成后续由电路241存储在cr 242中的数字(数字格式)。对于这些示例,这些数字值可能是几个位长(例如,32-64位),并且可以提供细粒度自定义格式的数字值。

33.根据一些示例,如图3中所示,侧视图302示出了pcb 220包括输入短截线324和输出短截线326。对于这些示例,当设备盖210-2位于pcb220之上时,输入短截线324连接到输入触点372,并且输出短截线326连接到输出触点374。类似于设备盖210-1,可以与nvm装置230-7至230-12紧密接触地放置设备盖210-2。输入短截线324和输出短截线326可以具有足够的高度以升至高于nvm设备230-7至230-12的高度,以便与相应的输入触点372和输出触点374耦合。如下文更详细描述的,控制器240的电路241可以包括用于实现模块的启动或加电动作的电路或逻辑。这些动作可以包括基于经由输入短截线324/输入触点372、字符图案370、和输出触点374/输出短截线326施加的电压和电流,来确定字符图案370的电阻值。如下文更详细描述的,cr 242也可以由电路241的与启动相关的电路或逻辑用来存储字符图案370的确定电阻值。

34.图4图示了用于测量字符图案360和370的电阻的子系统400的第一示例。对于该第一示例,子系统400包括在模块200中,并且子系统400包括如图3所示和上文中描述的控制器240、电路241、cr 242、输入短截线320、324、输出短截线322、326、输入触点362、372、输出触点364、374和字符图案360、370。对于这些示例,如图4中所示,子系统400还包括迹线402、404(例如,金属迹线),其允许通过输入短截线320/输入触点362施加输入电压(v

in

)和输入电流(i

in

),然后通过字符图案360,从而通过输出触点364/输出短截线322产生输出电压(v

out

)和输出电流(i

out

)。如图4中所示,子系统400还包括迹线406、408(例如,金属迹线),其允许通过输入短截线324/输入触点372施加v

in

和i

in

,然后通过字符图案370,从而通过输出触点374/输出短截线326产生v

out

和i

out

。

35.在一些示例中,如图4中所示,控制器240的电路241包括控制电路441和感测电路443。感测电路443可以包括电路或逻辑,用于使得施加v

in

,该v

in

使i

in

经过迹线402流动过输入短截线320和输入触点362。然后,电流可以流过字符图案360,并且i

out

流过输出触点364和输出短截线322并且经由迹线404输出。感测电路443可以测量迹线404上的v

out

和i

out

。在一些示例中,控制电路441可以获得测量的v

out

和i

out

并且基于r

value

=v

out

/i

out

确定字符图案360的电阻值(r

value

)。然后,控制电路441可以使确定的r

value

被存储到cr 242。例如,如下文更详细描述的,cr242可以具有可被选择性设置为指示字符图案360的确定的r

value

的位。在其他示例中,感测电路443而不是控制电路441可以确定r

value

并且选择性地设置cr 242的用于指示确定的r

value

的位。

36.根据一些示例,感测电路443可以使得施加v

in

,该v

in

使i

in

经过迹线406流动过输入短截线324和输入触点372。然后,电流可以流过字符图案370,并且i

out

流过输出触点374和输出短截线326并经由迹线408输出。感测电路443可以测量迹线408上的v

out

和i

out

。在一些示例中,控制电路441可以获得测量的v

out

和i

out

并且基于r

value

=v

out

/i

out

确定字符图案370

的r

value

。然后,控制电路441可以使确定的r

value

被存储到cr 242。在其他示例中,感测电路443而不是控制电路441可以确定r

value

并且使确定的r

value

被存储到cr 242。如上文简要提到的,电路241可以包括adc。adc可以将确定r

value

转换为数字并且使数字被存储到cr 242。

37.在一些示例中,可以在模块200的制造期间初步确定字符图案360和370的相应r

value

。对于这些示例,在模块200的第一次启动或加电时,确定字符图案360和370的r

value

,然后将r

value

存储到cr 242作为基础r

value

。如下文更详细描述的,字符图案360和370的基础r

values

可以用于与在模块200的后续启动或加电之后确定的r

values

进行比较,然后,如果比较指示r

values

的差异大于阈值数,则制定篡改协议或策略。换句话说,差异指示可能的篡改。可能的篡改可以包括设备盖210-1或设备盖210-2的移除。设备盖210-1或210-2的移除可能会导致相应字符图案360或370的至少一部分被改动(例如,一些导电墨被刮掉)。在一些示例中,粘合剂或粘性材料可以将设备盖210-1至210-2粘附到存储器设备,而破坏该粘附可能会增加字符图案360或370在设备盖210-1或210-2移除时被改动的可能性。作为改动结果,字符图案360或370的确定的r

values

可能在模块200的启动之间显著变化。

38.图5图示了示例寄存器表500。在一些示例中,如图5中所示,寄存器表500可以用于8位寄存器(示例不限于8位寄存器)。对于这些示例,8位寄存器包括位[2:0]中的base_r

value

。位[2:0]可以被选择性地断言,以指示在模块(诸如,模块200)的第一次启动之后测量的一个或多个字符图案的多达8个电阻范围。例如,每个范围可以覆盖0.01欧姆的范围(例如,0.040至0.049、0.050至0.059等)。8位寄存器还包括位[5:3]中的most_recent_r

value

。位[5:3]可以被选择性地断言,以指示在模块的最新启动之后测量的一个或多个字符图案的多达8个电阻范围。8位寄存器还包括位[6]中的tamper_flag。如果模块的控制器的逻辑和/或电路确定在位[2:0]中指示的base_r

value

与在位[5:3]中指示的most_recent_r

value

的比较指示了模块的篡改,则位[6]可以断被言。在一些示例中,tamper_flag指示也可以保存在非易失性存储器的某个部分中,以永久通告模块已被篡改。该永久通告可以用于未来的取证调查。在其他示例中,控制器可以使可编程熔丝位能够被激活以指示对存储器模块的篡改。如下文更详细描述的,对位[6]进行断言可以是基于检测到的篡改而制定的篡改协议或策略的初始部分。8位寄存器还包括位[7]中的debug_flag。如下文更详细描述的,位[7]可以被断言,以禁用任何篡改响应动作(但不是检测),从而允许调试模块。在一些示例中,位[7]可以仅经由严格控制的调试接口被断言,该严格控制的调试接口仅允许授权访问以使得模块的控制器的逻辑和/或特征对位[7]进行断言或取消断言。在一些示例中,严格控制的调试接口可能仅允许或者限制对与模块的预制造生命周期相关的篡改响应的禁用。

[0039]

图6图示了用于测量字符图案360和370的电阻的子系统400的第二示例。根据一些示例,子系统400的第二示例是模块200的后制造或非第一次启动。例如,在数据中心部署的计算平台中启动。对于这些示例,如图6中所示,字符图案360包括改动部分601,该改动部分601包括稍微改动的“pattern”的“a”、第一个“t”和“r”。并且,字符图案370包括改动部分602,该改动部分602包括稍微改动的“pattern”的“a”、第一个“t”和“e”。这些改动可能是在设备盖240-1和240-2移除期间刮掉一些导电墨而导致的。当将设备盖240-1和240-2放回到nvm设备230-1至230-12之上时,也可能产生进一步的改动。

[0040]

根据一些示例,如上文针对子系统400所述,由控制器240的逻辑和/或特征确定具有如图6中所示的相应改动部分601和602的字符图案360和370的r

values

。对于这些示例,控

制器240可以选择性地断言cr 242的位[5:3],以将r

value

记录为most_recent_r

value

。控制器240的逻辑和/或特征(例如,实现固件逻辑的控制电路441)可以从cr 242的位[2:0]获得base_r

value

并与most_recent_r

value

进行比较。对于该示例,比较将示出从制造以来改动部分601和602在r

value

中引起的可检测变化(例如,δ》0.01欧姆)。然后,控制器240的逻辑和/或特征可以断言cr 242的位[6],以指示已经检测到篡改。对cr 242的位[6]的断言充当指示模块200自从制造以来已被篡改的不可变位,并且在模块200的后续启动时可以实现篡改策略。这些篡改策略可以包括但不限于篡改检测的警报、使得存储到nvm设备230-1至230-12的所有数据被擦除、防止/限制存储到nvm设备230-1至230-12的数据的解密、或停用模块200。在一些示例中,可以允许用户在用户的第一次启动期间重新配置某些风格的篡改检测和抵抗策略(例如,作为选择进入机制)。

[0041]

图7图示了示例逻辑流程700。在一些示例中,逻辑流程700可以图示永久性存储器模块的控制器的逻辑和/或特征的动作。对于这些示例,逻辑流程700可以由永久性存储器模块的控制器的电路和/或逻辑(诸如,如上文针对图2至图6所提及的模块200的控制器240中包括的电路241)来实现。并且,可以如上文针对图5所提及的寄存器表500中所指示,对控制器的电路和/或逻辑所使用的控制寄存器进行设置或编程。如图4或图6中所示,可以通过电路241的控制电路441或感测电路443对寄存器进行设置或编程。示例不限于用于实现逻辑流程700的至少部分的图2至图4和图6中所示的控制器240中包括的电路241、或者图5中所示的寄存器表500中指示的寄存器位。

[0042]

从决策块705开始,确定模块是否正在第一次启动。例如,制造商组装之后的初始启动或通电。如果是第一次启动,则逻辑流程700移动到块710。否则,逻辑流程700移动到块725。

[0043]

从块705移动到块710,控制器电路241的感测电路443感测在覆盖nvm设备230-1至230-12的设备盖240-1和240-2(例如,散热器板)的背面上喷涂的字符图案360和370的电阻。

[0044]

移动到块715,电路241的控制电路441可以断言cr 242的位[2:0]以指示base_r

values

。

[0045]

移动到块720,模块200断电。在一些示例中,断电可以在与篡改检测不相关的其他操作之后。

[0046]

从决策块705移动到决策块725,控制电路441可以确定是否已将模块200置于调试模式。如果已置于调试模式,则逻辑流程700移动到块730。否则,逻辑流程700移动到块745。

[0047]

从决策块725移动到块730,控制电路441可以断言cr 242的位[7]以指示模块200处于调试模式。

[0048]

移动到块735,完成对模块200的调试操作,并且cr 242的位[7]被取消断言以指示模块200不再处于调试模式。

[0049]

移动到块740,模块200断电。

[0050]

从决策块725移动到块745,感测电路443感测字符图案360和370的电阻,并且控制电路441确定r

values

并断言cr 242的位[5:3]以存储图案360和370的most_resent_r

values

。

[0051]

移动到决策块750,控制电路441可以实现固件以将cr 242的位[2:0]中维护的base_r

values

与位[5:3]中维护的most_recent_r

values

进行比较,以确定图案360和370的最新rvalues

是否在预定容差内(例如,彼此在0.01欧姆内)。如果比较的r

values

在预定容差内,则逻辑流程700移动到块755。否则,逻辑流程700移动到块765。

[0052]

移动到块755,模块200继续正常操作。换句话说,没有篡改检测协议或策略被激活。

[0053]

移动到块760,模块200断电。

[0054]

从决策块750移动到块765,控制电路441可以设置或断言cr 242的位[6],以指示检测到对模块200的篡改。

[0055]

移动到块770,模块200继续遵循已采用的篡改检测策略。在一些示例中,在下次启动期间可以遵循已采用的篡改检测策略。在任何情况下,当检测到篡改时,模块200将不允许访问在nvm设备230-1至230-12中维护的先前存储的数据。

[0056]

移动到块775,模块200断电。在一些示例中,逻辑流程700移动到图8中所示的逻辑流程800(b)而不是移回到逻辑流程700(a)的开始处。响应于cr 242的位[6]设置为指示检测到的篡改,移动到逻辑流程800。

[0057]

图8图示了示例逻辑流程800。在一些示例中,逻辑流程800可以图示永久性存储器模块的控制器的逻辑和/或特征的动作,如上文针对逻辑流程700所提到的,针对该永久性存储器模块已经检测到篡改。对于这些示例,类似于逻辑流程700,逻辑流程800可以由永久性存储器模块的控制器的电路和/或固件逻辑(诸如,上文针对图2至图6所提及的控制器240中包括的电路241的控制电路441)来实现。

[0058]

从块805开始,启动模块200。

[0059]

移动到块810,控制电路441可以读取cr 242的位[6],并且基于位[6]被断言,检测到篡改位已经被断言。

[0060]

移动到决策块815,控制电路441确定要实施哪个策略动作。如果是警报策略动作,则逻辑流程800移动到块825。如果是停用策略,则逻辑流程800移动到块820。如果是可能包括警报、停用、限制或其他篡改相关策略的任何组合的其他策略动作,则逻辑流程移动到块830。

[0061]

从决策块815移动到块820,控制电路441可以发起使模块200变得不可操作的停用策略。动作可以包括防止对nvm设备230-1至230-12进行访问或者防止解密存储在nvm设备230-1至230-12中的任何加密数据。

[0062]

从决策块815移动到块825,控制电路441可以使得生成警报。在一些示例中,警报可以向计算平台的操作者指示针对哪个模块200可以断言已检测到对模块200的篡改。对于这些示例,操作者可以采取校正动作,诸如,从模块200中移除所有敏感数据并仅允许将非敏感数据存储到模块200。

[0063]

从决策块815移动到块830,控制电路441可以发起其他策略动作,该其他策略动作可以包括针对模块200的使用的警告、停用、限制或其他篡改相关策略的组合。例如,擦除存储到nvm设备230-1至230-12的至少一部分(或全部)数据。

[0064]

从任一块820、825或835移动到块835,模块200断电。在一些示例中,如果再次通电或启动模块200,则可以重新启动逻辑流程800。

[0065]

图9图示了装置900的示例框图。虽然图9中所示的装置900在特定拓扑中具有有限数量的元件,但是可以理解装置900针对给定的实施方式可以按照需要在替代拓扑中包括

更多或更少的元件。

[0066]

根据一些示例,装置900可以由控制器的电路920(诸如,用于诸如模块200之类的存储器模块的控制器240的电路241)支持。可以将电路920中包括的电路(诸如,控制电路822-1或感测电路822-2)布置为执行逻辑、或执行由逻辑的模块、组件或特征实现的一个或多个固件。并且,“模块(module)”、“组件(component)”或“特征(feature)”还可以包括存储在计算机可读介质或机器可读介质(例如,在控制器240处维持的或可由控制器240访问的非易失性存储介质)中的固件,并且虽然在图9中将电路类型示为离散框,但是这并不将这些类型特征限制为由不同硬件组件(例如,单独的专用集成电路(asic)或现场可编程门阵列(fpga))实现。

[0067]

根据一些示例,电路920可以包括一个或多个asic或fpga,并且在一些示例中,可以将控制电路922-1或822-2中的至少一些实现为这些asic或fpga的硬件元件。

[0068]

在一些示例中,如图9中所示,电路920可以包括控制电路922-1和感测电路922-2。对于这些示例,控制电路922-1可以响应于存储器模块的第一次启动,确定在散热器盖的一侧上喷涂的字符图案的第一电阻值,该一侧面向驻留在第一存储器模块的pcb的第一侧上的非易失性存储器设备,其中,字符图案是使用导电墨进行喷涂的。第一次启动905可以指示控制电路922-1以确定第一电阻值。并且,对于这些示例,感测电路922-2可以感测来自字符图案的输出电流和电压,并且提供输出电流和电压,以使控制电路922-1能够确定第一电阻值。控制电路922-1可以将该第一电阻值存储到电路920能够访问的寄存器中。base_r

value 930例如可以包括存储到寄存器中的第一电阻值。

[0069]

根据一些示例,控制电路922-1可以响应于存储器模块的第二次启动,确定字符图案的第二电阻值。第二次启动910可以指示控制电路922-1以确定第二电阻值。对于这些示例,感测电路922-2可以感测来自字符图案的输出电流和电压,并且提供输出电流和电压,以使控制电路922-1能够确定第二电阻值。控制电路922-1可以将该第二电阻值存储到电路920能够访问的寄存器中。最新r

value 935例如可以包括存储到寄存器中的第二电阻值。

[0070]

在一些示例中,控制电路922-1还可以基于在阈值电阻值内第二电阻值不匹配第一电阻值,断言寄存器的位,以指示对存储器模块的篡改。对于这些示例,篡改指示940可以指示位的断言。经断言的位与用于将第一电阻值和第二电阻值存储到寄存器的任何位分开。

[0071]

装置900的各种组件可以通过各种类型的通信介质相互通信耦合以协调操作。协调可能涉及信息的单向或双向交换。例如,组件可以以通过通信介质传送的信号的形式传送信息。信息可被实现为分配给各种信号线的信号。在此类分配中,每条消息都是信号。然而,其他实施例可以替代地采用数据消息。此类数据消息可以通过各种连接发送。示例连接包括并行接口、串行接口和总线接口。

[0072]

本文中包括代表用于执行所公开架构的新颖方面的示例方法的一组逻辑流程。虽然出于便于解释的目的,将本文中所示的一个或多个方法示出和描述为一系列动作,但是本领域技术人员将明白和理解,这些方法不受动作顺序的限制。据此,一些动作可以以与本文中所示和描述的动作不同的顺序发生和/或与其他动作同时发生。例如,本领域技术人员将明白和理解,可将方法替代地表示为诸如状态图中的一系列相互关联的状态或事件。此外,并非方法中图示的所有动作对新颖的实现方式都是必需的。

[0073]

逻辑流程可以在软件、固件和/或硬件中实现。在软件和固件实施例中,逻辑流程可以通过存储在至少一个非暂态计算机可读介质或机器可读介质(诸如,光、磁或半导体存储器设备)上的计算机可执行指令来实现。实施例并不限于该上下文。

[0074]

图10图示了示例逻辑流程1000。逻辑流程1000可以代表由本文中描述的一个或多个逻辑、特征或设备(诸如,装置900)执行的一些或全部操作。更具体而言,逻辑流程1000可以通过控制电路922-1实现。

[0075]

根据一些示例,块1002处的逻辑流程1000可以在存储器模块的第一次启动之后,确定在散热器盖的一侧上喷涂的字符图案的第一电阻值,该一侧面向驻留在存储器模块的pcb的第一侧上的非易失性存储器设备,该字符图案是使用导电墨进行喷涂的。对于这些示例,控制电路922-1确定第一电阻值。

[0076]

在一些示例中,块1004处的逻辑流程1000可以在存储器模块的第二次引导之后,确定字符图案的第二电阻值。对于这些示例,控制电路922-1确定第二电阻值。

[0077]

根据一些示例,块1006处的逻辑流程1000可以基于在阈值电阻值内第二电阻值不匹配第一电阻值,断言控制器的电路能够访问的寄存器的位,以指示对存储器模块的篡改,该控制器驻留在pcb的第一侧或第二侧上。对于这些示例,控制电路922-1可以断言该位,以指示对存储器模块的篡改。

[0078]

图11图示了示例存储介质1100。在一些示例中,存储介质1100可以是制造产品。存储介质1100可以包括任何非暂态计算机可读介质或机器可读介质,诸如,光、磁或半导体存储器设备。存储介质1100可以存储各种类型的计算机可执行指令,诸如,实现逻辑流程1000的指令。计算机可读存储介质或机器可读存储介质的示例可以包括能够存储电子数据的任何有形介质,包括易失性存储器或非易失性存储器、可移动或不可移动存储器、可擦除或不可擦除存储器、可写或可重写存储器等。计算机可执行指令的示例可以包括任何合适类型的代码,诸如,源代码、编译代码、解译代码、可执行代码、静态代码、动态代码、面向对象的代码、视觉代码等。示例不限于该上下文。

[0079]

图12图示了示例计算平台1200。在一些示例中,如图12中所示,计算平台1200可以包括存储器系统1230、处理组件1240、其他平台组件1250或通信接口1260。根据一些示例,计算平台1200可以在计算设备中实现。

[0080]

根据一些示例,存储器系统1230可以包括控制器1232和存储器设备1234。对于这些示例,控制器1232的电路可以为装置900执行至少一些处理操作或逻辑并且可以包括存储介质,该存储介质包括存储介质1100。并且,存储器设备1234可以包括上文针对图2至图3中所示的非易失性存储器设备230-1至230-12和易失性存储器设备250所述的相似类型的易失性存储器或非易失性存储器(未示出)。

[0081]

根据一些示例,处理组件1240可以包括各种硬件元件、软件元件或两者的组合。硬件元件的示例可以包括设备、逻辑设备、组件、处理器、微处理器、管理控制器、配套管芯、电路、处理器电路、电路元件(例如,晶体管、电阻器、电容器、电感器等)、集成电路、asic、可编程逻辑设备(pld)、数字信号处理器(dsp)、fpga、存储器单元、逻辑门、寄存器、半导体设备、芯片、微芯片、芯片组等。软件元件的示例可以包括软件组件、程序、应用、计算机程序、应用程序、设备驱动器、系统程序、软件开发程序、机器程序、操作系统软件、中间件、固件、软件模块、例程、子例程、功能、方法、过程、软件接口、应用程序接口(api)、指令集、计算代码、计

算机代码、代码段、计算机代码段、字、值、符号或其任何组合。针对给定的示例,确定是否使用硬件元件和/或软件元件来实现示例可以按照需求根据任何数量的因素而变化,诸如所需的计算速率、电力水平、耐热性、处理周期预算、输入数据速率、输出数据速率、存储器资源、数据总线速度和其他设计或性能限制。

[0082]

在一些示例中,其他平台组件1250可以包括通用计算元件、存储器单元(包括系统存储器)、芯片组、控制器、外围设备、接口、振荡器、定时设备、视频卡、声卡、多媒体输入/输出(i/o)组件(例如,数字显示器)、电源等。其他平台组件1250中包括的存储器单元或存储器设备的示例可以包括但不限于以一个或多个高速存储器单元形式的各种类型的计算机可读存储介质和机器可读存储介质,诸如,只读存储器(rom)、随机存取存储器(ram)、动态ram(dram)、双倍数据速率dram(ddram)、同步dram(sdram)、静态ram(sram)、可编程rom(prom)、可擦除可编程rom(eprom)、电可擦除可编程rom(eeprom)、快闪存储器、诸如铁电聚合物存储器的聚合物存储器、奥氏存储器、相变或铁电存储器、硅-氧化物-氮化物-氧化物-硅(sonos)存储器、磁卡或光卡、一系列诸如独立磁盘冗余阵列(raid)驱动器、固态存储器设备(例如,usb存储器)、固态驱动器(ssd)和任何适于存储信息的其他类型的存储介质的设备。

[0083]

在一些示例中,通信接口1260可以包括支持通信接口的逻辑和/或特征。对于这些示例,通信接口1260可以包括根据各种通信协议或标准操作以通过直接或网络通信链路进行通信的一个或多个通信接口。直接通信可以通过使用一个或多个行业标准(包括后代和变体)中描述的通信协议或标准(诸如,与pcie规范、nvme规范或i3c规范相关联的通信协议或标准)发生。网络通信可以通过使用通信协议或标准(诸如,电气和电子工程师协会(ieee)颁布的一个或多个以太网标准中描述的通信协议或标准)发生。例如,ieee颁布的一种这样的以太网标准可以包括但不限于在2018年8月发布的ieee 802.3-2018,“带冲突检测的载波监听多路访问(csma/cd)的访问方法和物理层规范”(以下简称“ieee 802.3规范”)。网络通信也可以根据一个或多个开放流规范(诸如,开放流硬件抽象api规范)发生。网络通信也可以根据一个或多个无限带宽架构规范发生。

[0084]

计算平台1200可以是计算设备的一部分,该计算设备可以是例如用户装备、计算机、个人计算机(pc)、台式电脑、膝上电脑、笔记本电脑、上网本电脑、平板、智能手机、嵌入式电子设备、游戏机、服务器、服务器阵列或服务器群、web服务器、网络服务器、因特网服务器、工作站、小型计算机、大型计算机、超级计算机、网络设备、web设备、分布式计算系统、多处理器系统、基于处理器的系统或其组合。因此,根据适当需要,可以在计算平台1200的各种实施例中包括或省略本文中描述的计算平台1200的功能和/或具体配置。

[0085]

可以使用离散电路、asic、逻辑门和/或单芯片架构的任何组合来实现计算平台1200的组件和特征。此外,计算平台1200的特征可以在适当的情况下使用微控制器、可编程逻辑阵列和/或微处理器或前述的任何组合来实现。应注意,本文中可以将硬件、固件和/或软件元件统称或单独为“逻辑(logic)”、“电路(circuit)”或“电路(circuitry)”。

[0086]

应理解,图12的框图中所示的示例计算平台1200可以表示若干潜在实施例的一个功能描述性示例。因此,附图中描绘的块功能的划分、省略或包括并不意味着用于实现这些功能的硬件组件、电路、软件和/或元件必然会被划分、省略或包括在实施例中。

[0087]

至少一个示例的一个或多个方面可以通过存储在至少一种机器可读介质上的表

示处理器内的各种逻辑的代表指令来实现,当机器、计算设备或系统读取这些指令时,使机器、计算设备或系统制造逻辑来执行本文中描述的技术。这些表示称为“ip核”并且可能类似于ip块。ip核可以存储在有形的机器可读介质上,并且被提供给各种客户或制造设备以加载到实际制造逻辑或处理器的制造机器中。

[0088]

可以使用硬件元件、软件元件或两者的组合来实现各种示例。在一些示例中,硬件元件可以包括设备、组件、处理器、微处理器、电路、电路元件(例如,晶体管、电阻器、电容器、电感器等)、集成电路、asic、pld、dsp、fpga、存储器单元、逻辑门、寄存器、半导体设备、芯片、微芯片、芯片组等。在一些示例中,软件元件可以包括软件组件、程序、应用、计算机程序、应用程序、系统程序、机器程序、操作系统软件、中间件、固件、软件模块、例程、子例程、功能、方法、过程、软件接口、api、指令集、计算代码、计算机代码、代码段、计算机代码段、字、值、符号或其任何组合。针对给定的实施方式,确定是否使用硬件元件和/或软件元件来实现示例可以按照需求根据任何数量的因素而变化,诸如所需的计算速率、电力水平、耐热性、处理周期预算、输入数据速率、输出数据速率、存储器资源,数据总线速度和其他设计或性能限制。

[0089]

一些示例可以包括制造产品或至少一种计算机可读介质。计算机可读介质可以包括用于存储逻辑的非暂时性存储介质。在一些示例中,非暂时性存储介质可以包括一种或多种类型的能够存储电子数据的计算机可读存储介质,包括易失性存储器或非易失性存储器、可移动或不可移动存储器、可擦除或不可擦除存储器、可写或可重写存储器等。在一些示例中,逻辑可以包括各种软件元件,诸如软件组件、程序、应用、计算机程序、应用程序、系统程序、机器程序、操作系统软件、中间件、固件、软件模块、例程、子例程、功能、方法、过程、软件接口、api、指令集、计算代码、计算机代码、代码段、计算机代码段、字、值、符号或其任何组合。

[0090]

根据一些示例,计算机可读介质可以包括用于存储或维护指令的非暂时性存储介质,在由机器、计算设备或系统执行所述指令时,使机器、计算设备或系统执行根据所描述示例的方法和/或操作。指令可以包括任何合适类型的代码,诸如源代码、编译代码、解译代码、可执行代码、静态代码、动态代码等。指令可以根据预定义的计算机语言、方式或语法来实现,用于指示机器、计算设备或系统执行特定功能。指令可以使用任何合适的高级、低级、面向对象、可视、编译和/或解译的编程语言来实现。

[0091]

一些示例可以使用表述“在一个示例中(in one example)”或“示例(an example)”连同它们的派生词来描述。这些术语意指结合示例描述的特定特征、结构或特性包括在至少一个示例中。说明书中各处出现的短语“在一个示例中(in one example)”并非必须完全指代同一示例。

[0092]

一些示例可以使用表述“耦合(coupled)”或“连接(connected)”连同它们的派生词来描述。这些术语不一定是彼此的同义词。例如,使用术语“连接(connected)”和/或“耦合(coupled)”的描述可以指示两个或多个元件彼此直接物理或电接触。然而,术语“耦合(coupled)”或“与

……

耦合(coupled with)”也可以意指两个或多个元件彼此不直接接触,但仍彼此协作或相互作用。

[0093]

就本文中描述的各种操作或功能而言,可将它们描述或定义为软件代码、指令、配置和/或数据。内容可以是直接可执行的(“对象”或“可执行”形式)、源代码或差异代码

(“δ”或“补丁”代码)。本文中描述的软件内容可以经由上面存储有内容的制造产品提供,或者经由操作通信接口以经由通信接口发送数据的方法提供。机器可读存储介质可使机器执行所描述的功能或操作,并且包括以机器(例如,计算设备、电子系统等)可访问的形式存储信息的任何机制,诸如可记录/不可记录介质(例如,只读存储器(rom)、随机存取存储器(ram)、磁盘存储介质、光存储介质、快闪存储器设备等)。通信接口包括与硬连线、无线、光学等介质中的任一种接口连接以与另一设备通信的任何机制,诸如,存储器总线接口、处理器总线接口、互联网连接、磁盘控制器等。通信接口可被配置为,通过提供准备通信接口的配置参数和/或发送信号,来提供描述软件内容的数据信号。可以经由发送到通信接口的一个或多个命令或信号来访问通信接口。

[0094]

以下示例属于本文中公开的技术的附加示例。

[0095]

示例1:一种示例装置可以包括控制器,所述控制器驻留在存储器模块的印刷电路板(pcb)上。所述控制器可以包括电路,用于响应于所述存储器模块的第一次启动,确定在散热器盖的一侧上喷涂的字符图案的第一电阻值,所述一侧面向驻留在所述pcb的第一侧上的非易失性存储器设备,其中,所述字符图案是使用导电墨进行喷涂的。所述电路还可以响应于所述存储器模块的第二次启动,确定所述字符图案的第二电阻值。所述电路还可以基于在阈值电阻值内所述第二电阻值不匹配所述第一电阻值,断言所述电路能够访问的寄存器的位,以指示对所述存储器模块的篡改。

[0096]

示例2:根据示例1的装置,所述电路还可以将所述第一电阻值存储到所述控制器的所述电路能够访问的所述寄存器的第一位集。所述电路还可以将所述第二电阻值存储到所述寄存器的第二位集,其中,所述第一位集和所述第二位集不包括被断言以指示对所述存储器模块的篡改的位。

[0097]

示例3:根据示例2的装置,所述电路还可以将所述第一电阻值转换为第一数字格式的数,并将所述第一数字格式的数存储到所述寄存器的所述第一位集。所述电路还可以将所述第二电阻值转换为第二数字格式的数,并将所述第二数字格式的数存储到所述寄存器的所述第二位集。

[0098]

示例4:根据示例1的装置,所述电路还可以响应于所述存储器模块的第三次启动,检测所述寄存器的指示对所述存储器模块的篡改的经断言位。所述电路还可以发起篡改策略,所述篡改策略包括:停用所述存储模块的策略、向所述存储器模块的用户生成已检测到篡改的警告的策略、防止解密存储在所述非易失性存储器设备中的加密数据的策略、或擦除存储在所述非易失性存储器设备中的数据的至少一部分的策略。

[0099]

示例5:根据示例1的装置,所述电路还可以使篡改指示被存储在所述非易失性存储器设备中的至少一者的物理存储器地址中,或者使可编程熔丝位被激活以指示对所述存储器模块的篡改。

[0100]

示例6:根据示例1的装置,所述字符图案包括使用所述导电墨以如下图案在所述散热器盖上喷涂的每模块唯一字符图案:所述图案将字符进行连接以使电流能够经由所述导热墨从所述散热器盖上的输入触点流动到所述散热器盖上的输出触点。

[0101]

示例7:根据示例1的装置,所述导电墨可以包括碳墨、导电聚合物墨、或金属纳米粒子墨。

[0102]

示例8:根据示例1的装置,所述存储器模块包括双列直插式存储器模块(dimm),所

述dimm还包括:第二非易失性存储器设备,驻留在所述pcb的第二侧上;以及第二散热器盖,在所述第二散热器盖的面向所述第二非易失性存储器设备的一侧上喷涂有第二字符图案,其中,所述第二字符图案是使用导电墨进行喷涂的。

[0103]

示例9:根据示例8的装置,所述电路用于确定所述第一电阻值和所述第二电阻值还包括:所述电路用于响应于所述存储器模块的所述第一次启动,基于所述字符图案和所述第二字符图案的电阻值确定所述第一电阻值。所述电路还可以响应于所述存储器模块的所述第二次启动,基于所述字符图案和所述第二字符图案的电阻值确定所述第二电阻值。

[0104]

示例10:根据示例1的装置,所述非易失性存储器设备包括字节或块可寻址类型的非易失性存储器,该字节或块可寻址类型的非易失性存储器具有包括硫族化物相变材料的3维(3-d)交叉点存储器结构。

[0105]

示例11:根据示例1的装置,所述存储器模块的所述第一次启动包括在所述存储器模块在制造商处组装之后的所述存储器模块的初始启动。

[0106]

示例12:一种示例方法可以包括在存储器模块的第一次启动之后,确定在散热器盖的一侧上喷涂的字符图案的第一电阻值,所述一侧面向驻留在所述存储器模块的印刷电路板pcb的第一侧上的非易失性存储器设备,其中,所述字符图案是使用导电墨进行喷涂的。所述方法还可以包括响应于所述存储器模块的第二次启动,确定所述字符图案的第二电阻值。所述方法还可以包括基于在阈值电阻值内所述第二电阻值不匹配所述第一电阻值,断言控制器的电路能够访问的寄存器的位,以指示对所述存储器模块的篡改,所述控制器驻留在所述pcb的所述第一侧或第二侧。

[0107]

示例13:根据示例12的方法还可以包括将所述第一电阻值存储到所述控制器的所述电路能够访问的所述寄存器的第一位集。所述方法还可以包括将所述第二电阻值存储到所述寄存器的第二位集,其中,所述第一位集和所述第二位集不包括被断言以指示对所述存储器模块的篡改的位。

[0108]

示例14:根据示例13的方法还可以包括将所述第一电阻值转换为第一数字格式的数,并将所述第一数字格式的数存储到所述寄存器的所述第一位集。所述方法还可以包括将所述第二电阻值转换为第二数字格式的数,并将所述第二数字格式的数存储到所述寄存器的所述第二位集。

[0109]

示例15:根据示例12的方法还可以包括在所述存储器模块的第三次启动之后,检测所述寄存器的指示对所述存储器模块的篡改的经断言位。所述方法还可以包括发起篡改策略,所述篡改策略包括:停用所述存储模块的策略、向所述存储器模块的用户生成已检测到篡改的警告的策略、防止解密存储在所述非易失性存储器设备中的加密数据的策略、或擦除存储在所述非易失性存储器设备中的数据的至少一部分的策略。

[0110]

示例16:根据示例15的方法还可以包括使篡改指示被存储在所述非易失性存储器设备中的至少一者的物理存储器地址中,或者使可编程熔丝位被激活以指示对所述存储器模块的篡改。

[0111]

示例17:根据示例12的方法,所述字符图案包括使用所述导电墨以如下图案在所述散热器盖上喷涂的每模块唯一字符图案:所述图案将字符进行连接以使电流能够经由所述导热墨从所述散热器盖上的输入触点流动到所述散热器盖上的输出触点。

[0112]

示例18:根据示例12的方法,所述导电墨可以包括碳墨、导电聚合物墨、或金属纳

米粒子墨。

[0113]

示例19:根据示例12的方法,所述存储器模块可以包括双列直插式存储器模块(dimm),所述dimm还包括:第二非易失性存储器设备,驻留在所述pcb的第二侧上;以及第二散热器盖,在所述第二散热器盖的面向所述第二非易失性存储器设备的一侧上喷涂有第二字符图案,其中,所述第二字符图案是使用导电墨进行喷涂的。

[0114]

示例20:根据示例19的方法,确定所述第一电阻值和所述第二电阻值可以包括在所述存储器模块的所述第一次启动之后,基于所述字符图案和所述第二字符图案的电阻值确定所述第一电阻值。所述方法还可以包括在所述存储器模块的所述第二次启动之后,基于所述字符图案和所述第二字符图案的电阻值确定所述第二电阻值。

[0115]

示例21:根据示例12的方法,所述非易失性存储器设备可以包括字节或块可寻址类型的非易失性存储器,该字节或块可寻址类型的非易失性存储器具有包括硫族化物相变材料的3维(3-d)交叉点存储器结构。

[0116]

示例22:根据示例12的方法,所述存储器模块的所述第一次启动包括在所述存储器模块在制造商处组装之后的所述存储器模块的初始启动。

[0117]

示例23:至少一种示例机器可读介质可以包括多个指令,所述多个指令响应于被系统执行可以使得所述系统执行根据示例12至22中任一项所述的方法。

[0118]

示例24:一种示例设备可以包括用于执行根据示例12至22中任一项所述的方法的装置。

[0119]

示例25:一种双列直插式存储器模块(dimm)可以包括印刷电路板(pcb)。所述dimm可以包括第一非易失性存储器设备,驻留在所述pcb的第一侧上。所述dimm可以包括第二非易失性存储器设备,驻留在所述pcb的第二侧上。所述dimm还可以包括第一散热器盖,在面向所述第一非易失性存储器设备的一侧上喷涂有第一字符图案。所述第一字符图案可以是使用导电墨进行喷涂的。所述dimm还可以包括第二散热器盖,在面向所述第二非易失性存储器设备的一侧上喷涂有第二字符图案。所述第二字符图案可以是使用导电墨进行喷涂的。所述dimm还可以包括控制器,驻留在所述pcb的所述第一侧上。所述控制器包括电路,用于响应于所述dimm的第一次启动,确定所述第一字符图案和所述第二字符图案的第一电阻值。所述电路还可以响应于所述dimm的第二次启动,确定所述第一字符图案和所述第二字符图案的第二电阻值。所述电路还可以基于在阈值电阻值内所述第二电阻值不匹配所述第一电阻值,断言所述电路能够访问的寄存器的位,以指示对所述dimm的篡改。

[0120]

示例26:根据示例25的dimm还可以包括所述电路用于将所述第一电阻值存储到所述电路能够访问的所述寄存器的第一位集。所述电路还可以将所述第二电阻值存储到所述寄存器的第二位集,其中,所述第一位集和所述第二位集不包括被断言以指示对所述dimm的篡改的位。

[0121]

示例27:根据示例26的dimm还可以包括所述电路用于将所述第一电阻值转换为第一数字格式的数,并将所述第一数字格式的数存储到所述寄存器的所述第一位集。所述电路还可以将所述第二电阻值转换为第二数字格式的数,并将所述第二数字格式的数存储到所述寄存器的所述第二位集。

[0122]

示例28:根据示例25的dimm还可以包括所述电路用于在所述dimm的第三次启动之后,检测所述寄存器的指示对所述存储器模块的篡改的经断言位。所述电路还可以发起篡

改策略,所述篡改策略包括:停用所述dimm的策略、向所述dimm的用户生成已检测到篡改的警告的策略、防止解密存储在所述第一非易失性存储器设备或所述第二非易失性存储器设备中的加密数据的策略、或擦除存储在所述第一非易失性存储器设备或所述第二非易失性存储器设备中的数据的至少一部分的策略。

[0123]

示例29:根据示例28的dimm还可以包括所述电路用于使篡改指示被存储在所述第一非易失性存储器设备或所述第二非易失性存储器设备中的至少一个非易失性存储器设备的物理存储器地址中,或者使可编程熔丝位被激活以指示对所述存储器模块的篡改。

[0124]

示例30:根据示例25的dimm,字符图案可以包括使用所述导电墨以如下不同模式在所述第一散热器盖和所述第二散热器盖上喷涂的每dimm唯一字符图案:将字符进行连接以使电流能够经由所述导热墨从所述第一散热器盖和所述第二散热器盖上的各自的输入触点流动到所述第一散热器盖和所述第二散热器盖上的各自的输出触点。

[0125]

示例31:根据示例25的dimm,所述导电墨可以包括碳墨、导电聚合物墨、或金属纳米粒子墨。

[0126]

示例32:根据示例25的dimm,所述第一非易失性存储器设备和所述第二非易失性存储器设备可以包括字节或块可寻址类型的非易失性存储器,该字节或块可寻址类型的非易失性存储器具有包括硫族化物相变材料的3维(3-d)交叉点存储器结构。

[0127]

示例33:根据示例25的dimm,所述dimm的所述第一次启动可以包括在所述dimm在制造商处组装之后的所述dimm的初始启动。

[0128]

需要强调的是,所提供的公开摘要符合37c.f.r.第1.72(b)节,要求摘要允许读者能够快速确定技术公开的性质。将理解的是,所提交的摘要将不用于解释或限制权利要求的范围或含义。另外,在上述具体实施方式中,可以看出,出于简化本公开的目的,将各种特征一起组合在单个示例中。本公开的方法不应被解释为反映所要求保护的示例需要比每个权利要求中明确叙述的特征更多的特征的意图。相反,如所附权利要求所反映的,发明主题不在于单个公开示例的所有特征。因此,所附权利要求在此并入具体实施方式中,每个权利要求独立作为单独的示例。在所附权利要求中,术语“包括(including)”和“其中(in which)”分别用作相应术语“包括(comprising)”和“其中(wherein)”的简明英语等价词汇。此外,术语“第一(first)”、“第二(second)”、“第三(third)”等仅用作标签,并不旨在对其对象强加数字要求。

[0129]

虽然已经以特定于结构特征和/或方法动作的语言描述了主题,但是应当理解,所附权利要求中定义的主题不一定限于上述特定特征或动作。相反,上述特定特征和动作被公开为实施权利要求的示例形式。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。