包括存储器芯片共享通道的存储系统和存储模块

1.相关申请的交叉引用

2.本技术要求2020年12月14日提交的美国临时专利申请63/125062和2021年10月12日提交的申请号为10-2021-0134743的韩国专利申请的优先权,两者均通过引用整体合并于此。

技术领域

3.本发明的各种实施例涉及半导体设计技术,并且更具体地,涉及包括执行目标刷新操作的多个存储器芯片的存储模块。

背景技术:

4.半导体存储器件的存储单元包括用作开关的晶体管和储存电荷(或数据)的电容器。根据存储单元的电容器是否存在电荷,即,电容器的端电压是高还是低,数据被确定为处于逻辑高电平(逻辑电平1)和处于逻辑低电平(逻辑电平0)。

5.数据以电荷被累积在电容器中的形式被储存,并且理论上,不存在功耗。然而,由于晶体管的pn耦接等原因可能会生成泄露电流,因此储存在电容器中的初始电荷量可能会消失,这导致数据丢失。为了防止这种情况发生,应该在数据丢失之前读取存储单元中的数据,并且根据读取数据的正常量的电荷应该被重新充电而回到存储单元中。只有在周期性地重复这种操作时才可以保留数据,并且对单元电荷再充电的过程被称为刷新操作,在下文中将被称为正常刷新操作。

6.近来,除了正常刷新操作之外,对可能由于行锤击(row hammering)而丢失数据的特定字线的存储单元执行额外的刷新操作(在下文中将被称为“目标刷新操作”)。行锤击现象是指与特定字线或与该字线相邻设置的字线耦接的存储单元的数据由于对应字线的大量激活而被损坏的现象。为了防止行锤击现象,对被激活超过预定次数的字线(在下文中被称为“目标字线”)以及与该字线相邻设置的字线执行目标刷新操作。

7.此外,诸如双列直插式存储模块(dimm)等的存储模块包括多个存储器芯片,每个存储器芯片包括多个存储体(bank)。每个存储器芯片可以跟踪对所有存储体具有高行锤击风险的字线(即,访问集中的字线)的地址,并且根据跟踪结果来执行目标刷新操作。

技术实现要素:

8.本发明的实施例涉及一种存储系统,该存储系统包括共享通道的多个存储器芯片和存储器控制器,每个存储器芯片包括多个存储体并且能够提供关于多个存储体之中的分配的存储体的行锤击风险的跟踪信息,并且存储器控制器能够收集从存储器芯片提供的跟踪信息并且向存储器芯片提供行锤击地址。

9.本发明的实施例涉及一种存储系统,该存储系统包括共享通道的多个存储器芯片和存储器控制器,每个存储器芯片能够对分配的存储体的跟踪信息进行加密以将所加密的跟踪信息输出到存储器控制器,并且通过对从存储器控制器传送的行锤击地址进行解密来

执行目标刷新操作。

10.根据本发明的实施例,存储系统包括:多个存储器芯片,每个存储器芯片包括多个存储体,并且每个存储器芯片适于通过对存储体之中的选中的存储体的行锤击风险进行跟踪来生成跟踪地址、使用加密密钥对跟踪地址进行加密以将跟踪信息输出到多个数据总线中的对应的数据总线、以及根据通过命令/地址总线发送的行锤击地址来执行目标刷新操作;以及存储器控制器,该存储器控制器适于收集通过多个数据总线发送的针对存储体的跟踪信息,以生成行锤击地址并将该行锤击地址输出到命令/地址总线。

11.根据本发明的一个实施例,一种存储模块包括:命令/地址总线;多个数据总线;以及多个存储器芯片,每个存储器芯片包括多个存储体,并且每个存储器芯片适于通过对存储体之中的选中的存储体的行锤击风险进行跟踪来生成跟踪地址、使用加密密钥对跟踪地址进行加密以将跟踪信息输出到数据总线中的对应的数据总线、以及根据通过命令/地址总线发送的行锤击地址来执行目标刷新操作。

12.根据本发明的一个实施例,一种存储系统的操作方法包括:在存储器芯片的每个存储器芯片处,通过对存储器芯片的每个存储器芯片中包括的多个存储体之中的选中的存储体的行锤击风险进行跟踪来生成跟踪地址;在存储器芯片的每个存储器芯片处,使用加密密钥对跟踪地址进行加密,以将跟踪信息输出到多个数据总线中的对应的数据总线;在存储器控制器处,收集通过多个数据总线发送的针对存储体的跟踪信息,以生成行锤击地址并将该行锤击地址输出到命令/地址总线;以及在存储器芯片的每个存储器芯片处,根据通过命令/地址总线发送的行锤击地址来执行目标刷新操作。

13.根据本发明的实施例,每个存储器芯片可以仅跟踪存储体之中的分配的存储体的行锤击风险,从而使跟踪电路占用的面积最小化。

14.根据本发明的实施例,每个存储器芯片可以对跟踪信息进行加密并传送,从而提高存储系统的安全性。

附图说明

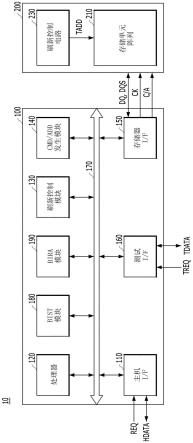

15.图1是示出根据本发明的一个实施例的存储系统的框图。

16.图2是示出在根据本发明的一个实施例的图1的多个存储器芯片内选中的存储体的视图。

17.图3是示出根据本发明的一个实施例的存储器芯片的详细框图。

18.图4是用于描述根据本发明的一个实施例的在pda(每dram寻址能力)模式期间模式设置电路的操作的时序图。

19.图5是示出根据本发明的一个实施例的图3的地址锁存器电路的详细框图。

20.图6是示出根据本发明的一个实施例的图3的解密电路(decryption circuit)的详细框图。

21.图7是示出根据本发明的一个实施例的图3的跟踪电路的详细框图。

22.图8是示出根据本发明的一个实施例的图3的加密电路(encryption circuit)的详细框图。

23.图9和图10是用于描述根据本发明的一个实施例的存储系统的操作的流程图。

具体实施方式

24.下面将参考附图更详细地描述本公开的各种实施例。本公开可以具有不同形式的实施例并且不应被解释为限于本文中所阐述的实施例。相反,提供这些实施例是为了使本公开透彻和完整,并将本发明的范围充分传达给本领域技术人员。贯穿本公开,在本公开的各个图和实施例中,相同的附图标记指代相同的部件。

25.应当理解,当一个元件被称为“耦接”或“连接”到另一元件时,这可能意味着两者直接耦接或两者在另一电路介于其间的情况下彼此电连接。将进一步理解,当在本说明书中使用时,术语“包括”、“包含”、“具有”等指定所述特征、数量、步骤、操作、元件、部件和/或它们的组合的存在,但不排除存在或添加一个或更多个其他特征、数量、步骤、操作、元件、部件和/或它们的组合。在本公开中,单数形式也旨在包括复数形式,除非上下文另有明确指示。

26.图1是示出根据本发明的一个实施例的存储系统100的框图。

27.参考图1,存储系统100可以包括存储器控制器110和存储模块150。

28.存储器控制器110可以控制存储系统100的一般操作并且它可以控制主机与存储模块150之间的一般数据交换。存储器控制器110可以根据来自主机的请求req而生成命令/地址信号c/a,并且将所生成的命令/地址信号c/a提供给存储模块150。存储器控制器110可以将时钟ck与命令/地址信号c/a一起提供给存储模块150。存储器控制器110可以将与从主机提供的请求req相对应的数据段(data piece)data0至data7提供给存储模块150。存储器控制器110可以接收从存储模块150读取的数据段data0至data7,并且将数据段data0至data7提供给主机。根据实施例,存储器控制器110可以将数据段data0至data7和数据选通信号dqs一起发送到存储模块150,或者从存储模块150一起接收数据段data0至data7和数据选通信号dqs。

29.存储模块150可以包括多个存储器芯片(例如,第一存储器芯片151至第八存储器芯片158)。第一存储器芯片151至第八存储器芯片158可以共享通道。即,第一存储器芯片151至第八存储器芯片158可以通过共享信道从存储器控制器110共同接收命令/地址信号c/a和时钟ck。另一方面,第一存储器芯片151至第八存储器芯片158可以向存储器控制器110传送不同的数据段data0至data7,或者从存储器控制器110接收不同的数据段data0至data7。换言之,在存储器控制器110与存储器芯片151至158之间的命令/地址总线可以作为公共总线由存储器芯片151至158共享,而在存储器控制器110与存储器芯片151至158之间的数据总线是对于每个存储器芯片151至158彼此分开的独立总线。存储器芯片151至158中的每一个可以通过数据总线中的专用总线传送/接收不同的数据段data0至data7。

30.第一存储器芯片151至第八存储器芯片158可以在存储器控制器110的控制下执行诸如读取操作、写入操作和刷新操作等的操作。由于第一存储器芯片151至第八存储器芯片158接收来自存储器控制器110的相同的命令/地址信号c/a,第一存储器芯片151至第八存储器芯片158可以同时执行读取操作、写入操作和刷新操作。例如,为了在写入操作中存储器控制器110将512-比特数据写入存储模块150,可以将64-比特数据写入第一存储器芯片151至第八存储器芯片158中的每一个中。另外,在读取操作中,可以从第一存储器芯片151至第八存储器芯片158中的每一个读取64-比特数据,从而可以将512-比特数据从存储模块150传送到存储器控制器110。换言之,在写入操作期间512-比特数据字(data word)可以分

布在第一存储器芯片151至第八存储器芯片158中,而在读取操作期间512-比特数据字可以通过从第一存储器芯片151至第八存储器芯片158读取64-比特数据来读取。存储模块150可以是双列直插式存储模块(dimm)。

31.详细地,存储器控制器110可以包括主机接口111、处理器113、命令/地址(cmd/add)生成模块115、刷新分析模块117、存储器接口119和总线120。

32.主机接口111可以被配置成在处理器113的控制下与连接到存储系统100的主机通信。例如,主机接口111可以接收来自主机的请求req,并且将从存储器接口119读取的数据段data0至data7提供给主机。

33.处理器113可以执行用于控制存储模块150的各种类型的计算和/或其他操作,并且/或者可以执行固件形式或其他类型的软件形式的命令。处理器113可以通过主机接口111接收来自主机的请求req。处理器113可以决定来自主机的请求req之中的、待传送到存储模块150的请求req的顺序。处理器113可以不同地调度从主机接收的请求req和待由存储模块150处理的操作,以提高存储模块150的性能。例如,即使主机首先请求存储模块150的读取操作以及然后请求写入操作,处理器113也可以将顺序调整成在在读取操作之前执行写入操作。处理器113可以将与请求req相对应的数据段data0至data7传送到存储器接口119。处理器113可以控制主机接口111、命令/地址生成模块115、刷新分析模块117和存储器接口119的整体操作。

34.命令/地址生成模块115可以根据由处理器113确定的操作的调度来生成命令/地址信号c/a。例如,命令/地址生成模块115可以将地址与激活命令(图3的act)一起提供而作为命令/地址信号c/a、将地址与模式寄存器命令(图3的mrs)一起提供而作为命令/地址信号c/a、将刷新命令(图3的ref)提供而作为命令/地址信号c/a、以及将行锤击地址与行锤击命令(图3的rh_cmd)一起提供而作为命令/地址信号c/a。模式寄存器命令mrs可以包括用于将设置数据储存和读出到设置于第一存储器芯片151至第八存储器芯片158的每一个中的模式寄存器组(mrs)电路中的模式寄存器写入命令mrw、以及用于读取所储存的设置数据的模式寄存器读取命令mrr。

35.刷新分析模块117可以基于分别从第一存储器芯片151至第八存储器芯片158发送的、经过存储器接口119的数据段data0至data7来生成行锤击地址。第一存储器芯片151至第八存储器芯片158中的每一个可以包括多个存储体。根据一个实施例,分别从第一存储器芯片151至第八存储器芯片158发送来的数据段data0至data7可以包括针对不同存储体的跟踪信息。刷新分析模块117可以通过收集针对包括在数据段data0至data7中的不同存储体的跟踪信息来生成行锤击地址。

36.存储器接口119可以被配置成在处理器113的控制下与存储模块150通信。例如,存储器接口119可以将命令/地址信号c/a和数据段data0至data7发送到存储模块150,并且将从存储模块150读取的数据段data0至data7发送至主机接口111。

37.处理器113可以经由总线120在主机接口111、命令/地址生成模块115、刷新分析模块117和存储器接口119之间传送数据。根据一个实施例,主机接口111、命令/地址生成模块115、刷新分析模块117和存储器接口119可以在不通过总线120的情况下彼此独立地通信。例如,刷新分析模块117和主机接口111可以在不通过总线120的情况下彼此直接通信。刷新分析模块117和存储器接口119可以在不通过总线120的情况下彼此直接通信。主机接口111

和存储器接口119也可以在不通过总线120的情况下彼此直接通信。

38.图2是示出在图1的第一存储器芯片151至第八存储器芯片158的每一个内选中的存储体的视图。

39.参考图2,第一存储器芯片151至第八存储器芯片158中的每一个可以包括第一存储体bk0至第32存储体bk31。根据一个实施例,多个存储器芯片内的多个存储体可以被划分成包括不同存储体的多个组,并且可以在多个存储器芯片的每一个内选择多个组中的一个组。这里,选中的相应存储器芯片的组可以在每个存储器芯片中的不同位置。在每个存储器芯片中储存有关于选中的组中包含的存储体的信息(在下文中,被称为“目标存储体信息”),并且每个存储器芯片可以根据目标存储体信息而仅跟踪选中的存储体的行锤击风险。

40.例如,第一存储器芯片151至第八存储器芯片158中的每一个内的第一存储体bk0至第32存储体bk31被划分为第一组至第八组,其中每个组顺序地包括4个存储体。此时,在第一存储器芯片151内选择第一组中包括的第一存储体bk0至第四存储体bk3,在第二存储器芯片152内选择第二组中包括的第五存储体bk4至第八存储体bk7,并且以这种方式,在第八存储器芯片158内选择第八组中包括的第29存储体bk28至第32存储体bk31。这里,第一存储器芯片151至第八存储器芯片158的选中的组可以在第一存储器芯片151至第八存储器芯片158中的每一个的不同位置。第一存储器芯片151至第八存储器芯片158可以仅跟踪每个选中的组中包括的存储体的行锤击风险。根据模式寄存器命令mrs(例如,模式寄存器读取命令mrr),第一存储器芯片151至第八存储器芯片158可以在模式寄存器组电路中储存选中的存储体的跟踪信息,并且可以通过将选中的存储体的跟踪信息包括在相应数据段data0至data7中来输出所储存的选中的存储体的跟踪信息。

41.尽管作为示例描述了第一存储体bk0至第32存储体bk31被划分成第一组至第八组,在每个组内顺序地包括4个存储体,但是本发明不限于此。根据一个实施例,第一存储体bk0至第32存储体bk31被划分成第一组至第八组,在每个组内随机或非顺序地包括4个存储体。

42.刷新分析模块117可以通过收集相应的数据段data0至data7中包括的不同存储体的跟踪信息来生成行锤击地址。因此,根据一个实施例,可以在最小面积内减轻行锤击风险。

43.此外,根据该实施例,当通过将选中的存储体的跟踪信息包括在相应的数据段data0至data7中而输出该跟踪信息时,存储模块150的第一存储器芯片151至第八存储器芯片158可以加密并输出选中的存储体的跟踪信息,并且通过对从存储器控制器110提供的行锤击地址进行解密来执行目标刷新操作。因此,根据一个实施例,可以提高存储系统的安全性。

44.在下文中,参考图3至图5,将描述第一存储器芯片151至第八存储器芯片158的详细配置。

45.图3是示出根据本发明的一个实施例的第一存储器芯片151的详细框图。第二存储器芯片152至第八存储器芯片158中的每一个可以包括与第一存储器芯片151基本相同的配置。

46.参考图3,第一存储器芯片151可以包括存储单元阵列210、行控制电路212、数据输

入/输出(i/o)电路214、时钟缓冲器221、命令/地址(ca)缓冲器222、命令解码器223、地址锁存器电路240、跟踪控制电路252、密钥生成电路254、解密电路260、跟踪电路270、加密电路280和模式设置电路290。

47.存储单元阵列210可以包括第一存储体至第32存储体。在第一存储体至第32存储体中的每一个中,耦接到字线wl和位线的多个存储单元mc可以以阵列的形式布置。第一存储体至第32存储体的数量或存储单元mc的数量可以根据第一存储器芯片151的容量来确定。

48.时钟缓冲器221可以从存储器控制器110接收时钟ck。时钟缓冲器221可以通过对时钟ck进行缓冲来生成内部时钟clk。根据一个实施例,存储器控制器110可以以差分方式将系统时钟ck_t和ck_c发送到第一存储器芯片151,并且第一存储器芯片151可以包括分别接收差分时钟ck_t和ck_c的时钟缓冲器。

49.ca缓冲器222可以基于时钟ck来从存储器控制器110接收命令/地址信号c/a。ca缓冲器222可以基于时钟ck来对命令/地址信号c/a进行采样并且输出内部命令icmd和内部地址iadd。因此,第一存储器芯片151可以与时钟ck同步。

50.命令解码器223可以对从ca缓冲器222输出的内部命令icmd进行解码以生成激活命令act、刷新命令ref、目标刷新命令tref、模式寄存器命令mrs和行锤击命令rh_cmd。激活命令act可以是用于执行激活至少一个字线wl的激活操作的命令,刷新命令ref可以是用于执行顺序地刷新多个字线wl的正常刷新操作的命令,模式寄存器命令mrs可以是用于将设置数据储存在模式寄存器组电路(即,模式设置电路290)中和/或输出所储存的设置数据的命令。模式寄存器命令mrs可以包括用于将设置数据储存和读出到模式设置电路290中的模式寄存器写入命令mrw、以及用于从模式设置电路290中读出所储存的设置数据的模式寄存器读取命令mrr。每当刷新命令ref的输入数量达到设置数量时,命令解码器223就可以生成目标刷新命令tref。行锤击命令rh_cmd可以是用于通过收集分别从每个存储器芯片发送的数据段data0至data7中包括的不同存储体的跟踪信息而从存储器控制器110向每个存储器芯片提供行锤击地址的命令。尽管未示出,但是命令解码器223可以通过对内部命令icmd进行解码来另外生成读取命令、写入命令、预充电命令等。

51.根据激活命令act、刷新命令ref、目标刷新命令tref和行锤击命令rh_cmd,地址锁存器电路240可以对内部地址iadd进行锁存和解码以生成多个存储体激活信号act_bk《0:31》、多个存储体刷新信号ref_bk《0:31》、激活地址act_add《0:15》、多个目标存储体刷新信号tref_bk《0:31》、行锤击存储体地址rh_ba《0:4》和行锤击行地址(row-hammer row address)rh_add《0:5》。行锤击存储体地址rh_ba《0:4》和行锤击行地址rh_add《0:5》可以定义为行锤击地址。

52.详细地,地址锁存器电路240可以对内部地址iadd进行锁存以生成存储体地址(图5的ba《0:4》)、行地址(图5的radd《0:5》)和列地址(图5的cadd《0:4》)。地址锁存器电路240可以通过根据激活命令act而对存储体地址ba《0:4》进行解码来生成分别对应于存储体的存储体激活信号act_bk《0:31》。地址锁存器电路240可以通过根据刷新命令ref而对存储体地址ba《0:4》进行解码来生成分别对应于存储体的存储体刷新信号ref_bk《0:31》。地址锁存器电路240可以通过根据激活命令act而对内部地址iadd进行锁存来生成激活地址act_add《0:15》。地址锁存器电路240可以通过根据行锤击命令rh_cmd而对存储体地址ba《0:4》

进行锁存来生成行锤击存储体地址rh_ba《0:4》。地址锁存器电路240可以基于行锤击存储体地址rh_ba《0:4》和目标刷新命令tref来生成目标存储体刷新信号tref_bk《0:31》。地址锁存器电路240可以通过根据行锤击命令rh_cmd而对行地址radd《0:5》进行锁存来生成行锤击行地址rh_add《0:5》。尽管未示出,但是存储器芯片151可以进一步包括用于根据读取命令或写入命令而选择对应于列地址cadd《0:4》的位线的列控制电路。将在图5中描述地址锁存器电路240的详细配置。

53.跟踪控制电路252可以通过基于目标存储体信息bk_info而提取来自存储体激活信号act_bk《0:31》中的一些来生成多个每存储体(per-bank)激活信号rh_act《0:3》,所提取的存储体激活信号对应于选中的存储体。例如,在第一存储器芯片151的情况下,跟踪控制电路252可以生成分别与从第一存储体bk0至第32存储体bk31之中选择的第一存储体bk0至第四存储体bk3相对应的第一每存储体激活信号至第四每存储体激活信号rh_act《0:3》。作为参考,目标存储体信息bk_info可以包括在第一存储体bk0至第32存储体bk31之中被选择以进行跟踪的4个存储体的信息。目标存储体信息bk_info可以被储存在模式设置电路290中,并且从模式设置电路290提供给跟踪控制电路252。

54.密钥生成电路254可以响应于复位信号rst来生成加密密钥key。即,每当对应的存储器芯片被复位或初始化时,密钥生成电路254就可以生成加密密钥key。

55.解密电路260可以通过使用加密密钥key对行锤击行地址rh_add《0:5》进行解密来生成目标地址tadd《0:15》。将在图6中描述解密电路260的详细配置。

56.跟踪电路270可以根据第一每存储体激活信号至第四每存储体激活信号rh_act《0:3》来跟踪选中的存储体(例如,第一存储体bk0至第四存储体bk3)的行锤击风险,以及根据目标刷新命令tref来输出跟踪地址track_add《0:63》。根据第一每存储体激活信号至第四每存储体激活信号rh_act《0:3》,跟踪电路270可以通过由对被输入到选中的存储体的激活地址act_add《0:15》进行随机采样而储存选中的存储体的采样地址来执行跟踪操作。跟踪电路270可以根据目标刷新命令tref而将储存在其中的采样地址输出而作为跟踪地址track_add《0:63》。将在图7中描述跟踪电路270的详细配置。

57.加密电路280可以通过使用加密密钥key对跟踪地址track_add《0:63》进行加密来生成跟踪信息track_info《0:5》。将在图8中描述加密电路280的详细配置。

58.模式设置电路290可以通过响应于模式寄存器命令mrs而对内部地址iadd的至少一些比特进行解码来执行各种设置操作。模式设置电路290可以被实现为已知模式寄存器组(mrs)电路。模式设置电路290可以储存从加密电路280输出的跟踪信息track_info《0:5》,以及响应于模式寄存器读取命令mrr而经由内部数据总线将所储存的跟踪信息track_info《0:5》提供给数据i/o电路214。根据一个实施例,模式设置电路290可以根据目标刷新命令tref而储存从加密电路280输出的跟踪信息track_info《0:5》。此外,每dram寻址能力(pda)模式可以被支持以对数据总线与其分离的每个存储器芯片执行独立的模式寄存器组操作(即,设置操作)。模式设置电路290可以根据内部数据idata的特定比特(例如,第一比特idata《0》)来判断是否进入pda模式,在pda模式下根据内部地址iadd来设置目标存储体信息bk_info,以及将所设置的目标存储体信息bk_info提供给跟踪控制电路252。将参考图4描述模式设置电路290在pda模式下的操作。

59.数据i/o电路214可以接收来自存储器控制器110的数据data0以将数据data0加载

到内部数据总线上作为内部数据idata,或者将从存储单元阵列210读取的内部数据idata通过内部数据总线作为数据data0传送至存储器控制器110。具体地,当响应于模式寄存器读取命令mrr而从模式设置电路290输出跟踪信息track_info《0:5》时,数据i/o电路214可以输出跟踪信息track_info《0:5》以包括在数据data0中。

60.行控制电路212可以根据存储体激活命令act_bk《0:31》来将与激活地址act_add《0:15》相对应的至少一个字线wl激活,以及根据预充电命令而对被激活的字线wl进行预充电。为了在正常刷新操作期间选择待刷新的字线,可以额外提供用于生成根据刷新命令ref而顺序地增加的计数地址的刷新计数器(未示出)。行控制电路212可以根据存储体刷新信号ref_bk《0:31》而执行对与计数地址相对应的多个字线wl进行顺序地刷新的正常刷新操作。行控制电路212可以根据目标存储体刷新信号tref_bk《0:31》来执行对与目标地址tadd《0:15》相对应的字线wl的一个或多个相邻字线进行刷新的目标刷新操作。

61.图4是用于描述根据本发明的一个实施例在pda模式期间模式设置电路290的操作的时序图。

62.参考图4,为了进入pda模式,可以根据内部数据idata的特定比特(例如,第一比特idata《0》)的信号电平来确定模式寄存器命令mrs的有效性。如果在从施加模式寄存器命令mrs的时刻开始经过写入等待时间(latency)wl(它是附加等待时间al和cas写入等待时间的总和,wl=al cwl)之后的时刻,第一比特idata《0》的信号电平为“0”,则所施加的模式寄存器命令mrs可以被确定为是有效的;然而,如果第一比特idata《0》的信号电平为“1”,则所施加的模式寄存器命令mrs可能被确定为是无效的并且因此被忽略。

63.例如,在时刻t1,模式寄存器命令mrs可以被施加到存储器芯片。在从时刻t1开始经过了与写入等待时间wl(wl=al cwl)一样多的时间之后的时刻t2,第一比特idata《0》的信号电平可以在预定持续时间内转变为“0”。因此,在时刻t1施加的模式寄存器命令mrs可以被确定为是有效的,并且因此存储器芯片的设置操作可以基于与模式寄存器命令mrs一起输入的内部地址iadd而从时刻t3开始进行持续时间tmrd_pda,该持续时间是模式寄存器组命令周期时间。

64.如果第一比特idata《0》的信号电平在时刻t2被保持为“1”,则在时刻t1施加的模式寄存器命令mrs可以被确定为是无效的并且被忽略。换言之,可以不执行存储器芯片的设置操作。

65.根据一个实施例,模式设置电路290可以根据内部数据idata的第一比特idata《0》来判断是否进入pda模式,并且设置与在pda模式下传送的内部地址iadd相对应的目标存储体信息bk_info,从而将被设置的目标存储体信息bk_info提供给跟踪控制电路252。

66.图5是示出根据本发明的一个实施例的图3的地址锁存器电路240的详细框图。

67.参考图5,地址锁存器电路240可以包括地址锁存器241、存储体激活解码器242、刷新解码器243、激活地址解码器244、第一目标锁存器245、第二目标锁存器246和目标刷新解码器247。

68.地址锁存器241可以对内部地址iadd进行锁存以生成存储体地址ba《0:4》、行地址radd《0:5》和列地址cadd《0:4》。

69.存储体激活解码器242可以通过根据激活命令act而对存储体地址ba《0:4》进行解码来生成第一存储体激活信号至第32存储体激活信号act_bk《0:31》。第一存储体激活信号

至第32存储体激活信号act_bk《0:31》可以分别对应于第一存储体bk0至第32存储体bk31。例如,第一存储体激活信号act_bk《0》用作第一存储体bk0的激活命令。

70.刷新解码器243可以通过根据刷新命令ref而对存储体地址ba《0:4》进行解码来生成第一存储体刷新信号至第32存储体刷新信号ref_bk《0:31》。第一存储体刷新信号至第32存储体刷新信号ref_bk《0:31》可以分别对应于第一存储体bk0至第32存储体bk31。例如,第一存储体刷新信号ref_bk《0》用作第一存储体bk0的刷新命令。

71.激活地址解码器244可以通过根据激活命令act锁存内部地址iadd来生成激活地址act_add《0:15》。

72.第一目标锁存器245可以通过根据行锤击命令rh_cmd而对存储体地址ba《0:4》进行锁存来生成行锤击存储体地址rh_ba《0:4》。

73.第二目标锁存器246可以通过根据行锤击命令rh_cmd而对行地址radd《0:5》进行锁存来生成行锤击行地址rh_add《0:5》。

74.目标刷新解码器247可以通过响应于目标刷新命令tref而对行锤击存储体地址rh_ba《0:4》进行解码来生成第一目标存储体刷新信号至第32目标存储体刷新信号tref_bk《0:31》。当目标刷新命令tref被输入时,目标刷新解码器247可以对行锤击存储体地址rh_ba《0:4》进行解码,从而输出第一目标存储体刷新信号至第32目标存储体刷新信号tref_bk《0:31》。第一目标存储体刷新信号至第32目标存储体刷新信号tref_bk《0:31》可以分别对应于第一存储体bk0至第32存储体bk31。例如,第一目标存储体刷新信号tref_bk《0》用作第一存储体bk0的目标刷新命令。

75.图6是示出根据本发明的一个实施例的图3的解密电路260的详细框图。

76.参考图6,解密电路260可以包括地址解码器262和解密器264。

77.地址解码器262可以通过对行锤击行地址rh_add《0:5》进行解码来生成解码行锤击行地址rh_add_d《0:15》。

78.解密器264可以通过使用加密密钥key对解码行锤击行地址rh_add_d《0:15》进行解密来生成目标地址tadd《0:15》。解密器264可以使用与由加密电路280使用的加密方法相对应的各种类型的解密方法。例如,解密器264可以利用用于对加密密钥key和解码行锤击行地址rh_add_d《0:15》执行异或运算的逻辑异或(xor)门来实现。加密密钥key的比特数和解码行锤击行地址rh_add_d《0:15》的比特数可以不同。在这种情况下,可以复制和使用加密密钥key。例如,当加密密钥key包括4比特并且解码行锤击行地址rh_add_d《0:15》包括16比特时,解密器264可以复制加密密钥key以形成16比特并且对所复制的16比特加密密钥和解码行锤击行地址rh_add_d《0:15》执行异或运算。结果,解密器264可以输出16比特的目标地址tadd《0:15》。

79.图7是示出图3的跟踪电路270的详细框图。

80.参考图7,跟踪电路270可以包括采样信号生成电路272、输入控制电路274和地址储存电路276。

81.采样信号生成电路272可以生成被随机使能的采样信号sam_en。采样信号生成电路272可以用基于伪随机二进制序列(prbs)的随机模式生成器或基于线性反馈移位寄存器(lfsr)的随机模式生成器来实现。

82.输入控制电路274可以根据第一每存储体激活信号至第四每存储体激活信号rh_

act《0:3》和采样信号sam_en来生成第一输入控制信号至第四输入控制信号sam_bk《0:3》。当对应的输入控制信号和采样信号sam_en都被使能时,输入控制电路274可以对相应的输入控制信号进行使能。根据一个实施例,输入控制电路274可以利用用于对第一每存储体激活信号至第四每存储体激活信号rh_act《0:3》和采样信号sam_en执行逻辑与运算的逻辑与门来实现。

83.地址储存电路276可以根据第一输入控制信号至第四输入控制信号sam_bk《0:3》而分别将激活地址act_add《0:15》储存为第一采样地址sam_add0《0:15》至第四采样地址sam_add3《0:15》。地址储存电路276可以根据目标刷新命令tref而将第一采样地址sam_add0《0:15》至第四采样地址sam_add3《0:15》中的全部输出而作为跟踪地址track_add《0:63》。地址储存电路276可以包括分别接收第一输入控制信号至第四输入控制信号sam_bk《0:3》的第一锁存器电路lat_b0至第八锁存器电路lat_b3。在第一存储器芯片151的情况下,地址储存电路276可以包括分别对应于第一存储体bk0至第四存储体bk3的第一锁存器电路lat_b0至第八锁存器电路lat_b3。在第二存储器芯片152的情况下,地址储存电路276可以包括分别对应于第五存储体bk4至第八存储体bk7的第一锁存器电路lat_b0至第八锁存器电路lat_b3。当第一输入控制信号至第四输入控制信号sam_bk《0:3》的对应控制信号被使能时,锁存器电路lat_b0至lat_b3中的每一个都可以储存激活地址act_add《0:15》作为其采样地址。当目标刷新命令tref被输入时,锁存器电路lat_b0到lat_b3可以将第一采样地址sam_add0《0:15》至第四采样地址sam_add3《0:15》的全部输出而作为跟踪地址track_add《0:63》。

84.传统存储器芯片必须具有分别对应于所有存储体的锁存器电路以跟踪行锤击风险。例如,当32个存储体被布置在每个存储器芯片中时,每个存储器芯片需要32个锁存器电路来跟踪32个存储体的行锤击风险。另一方面,在所提出的发明的一个实施例中,即使每个存储器芯片仅针对从32个存储体中选择的四个存储体跟踪行锤击风险,存储器控制器也可以收集从每个存储器芯片提供的特定于存储体的跟踪信息,并且最终提供行锤击地址。相应地,由锁存器电路占用的面积可以减小到4/32,即,1/8。

85.图8是示出根据本发明的一个实施例的图3的加密电路280的详细框图。

86.参考图8,加密电路280可以包括加密器282和地址编码器284。

87.加密器282可以通过使用加密密钥key对跟踪地址track_add《0:63》进行加密来生成加密地址track_add_e《0:63》。加密器282可以使用各种类型的加密方法。例如,加密器282可以利用用于对加密密钥key和跟踪地址track_add《0:63》执行xor运算的逻辑异或(xor)门来实现。加密密钥key的比特数和跟踪地址track_add《0:63》的比特数可以不同。在这种情况下,可以复制和使用加密密钥key。例如,当加密密钥key包括4比特并且跟踪地址track_add《0:63》包括64比特时,加密器282可以将加密密钥key复制以形成为64比特并且对所复制的64比特加密密钥和跟踪地址track_add《0:63》执行异或运算。结果,加密器282可以输出64比特的加密地址track_add_e《0:63》。

88.地址编码器284可以通过对加密地址track_add_e《0:63》进行编码来生成跟踪信息track_info《0:5》。

89.在下文中,参考图1至图10,将详细描述根据本发明的一个实施例的存储系统的操作。

90.图9是用于描述根据本发明的一个实施例的用于将选中的存储体的跟踪信息输出到存储器控制器的存储器芯片的操作的流程图。

91.参考图9,当存储器芯片被初始化时,每个存储器芯片的密钥生成电路254可以生成加密密钥key(在s910)。

92.命令解码器223可以对内部命令icmd进行解码以生成激活命令act、刷新命令ref、目标刷新命令tref和模式寄存器命令mrs。

93.当模式寄存器命令mrs被输入时,模式设置电路290可以根据内部数据idata的第一比特idata《0》来判断是否进入pda模式,以及在pda模式中设置与内部地址iadd相对应的目标存储体信息bk_info,从而将所设置的目标存储体信息bk_info提供给跟踪控制电路252(在s920)。

94.地址锁存器电路240可以通过根据激活命令act对内部地址iadd的存储体地址ba《0:4》进行解码来生成存储体激活信号act_bk《0:31》。因此,行控制电路212可以根据存储体激活命令act_bk《0:31》来执行激活操作以将与激活地址act_add《0:15》相对应的至少一个字线wl激活。

95.此外,跟踪控制电路252可以通过基于目标存储体信息bk_info而提取来自存储体激活信号act_bk《0:31》中的一些来生成与选中的存储体相对应的多个每存储体激活信号rh_act《0:3》,所提取的存储体激活信号对应于选中的存储体(在s930)。例如,在第一存储器芯片151的情况下,跟踪控制电路252可以生成分别与从第一存储体bk0至第32存储体bk31之中选择的第一存储体bk0至第四存储体bk3相对应的第一每存储体激活信号到第四每存储体激活信号rh_act《0:3》。

96.跟踪电路270可以根据第一每存储体激活信号至第四每存储体激活信号rh_act《0:3》来执行跟踪操作以来跟踪选中的存储体(例如,第一存储体bk0至第四存储体bk3)的行锤击风险(在s940)。详细地,跟踪电路270可以根据第一每存储体激活信号至第四每存储体激活信号rh_act《0:3》和采样信号sam_en来生成第一输入控制信号至第四输入控制信号sam_bk《0:3》,并且根据第一输入控制信号到第四输入控制信号sam_bk《0:3》来将激活地址act_add《0:15》分别储存为第一采样地址sam_add0《0:15》至第四采样地址sam_add3《0:15》。

97.此后,每当刷新命令ref的输入数量达到设置数量时,命令解码器223就可以生成目标刷新命令tref。跟踪电路270可以根据目标刷新命令tref来将第一采样地址sam_add0《0:15》至第四采样地址sam_add3《0:15》输出而作为跟踪地址track_add《0:63》(在s950)。

98.加密电路280可以通过使用加密密钥key对跟踪地址track_add《0:63》进行加密来生成跟踪信息track_info《0:5》,并且模式设置电路290可以储存从加密电路280输出的跟踪信息track_info《0:5》(在s960)。

99.模式设置电路290可以响应于模式寄存器命令mrs的模式寄存器读取命令mrr来将所储存的跟踪信息track_info《0:5》提供给数据i/o电路214。数据i/o电路214可以输出跟踪信息track_info《0:5》以包括在数据data0中(在s970)。

100.此后,存储器控制器110的刷新分析模块117可以通过收集从第一存储器芯片151至第八存储器芯片158发送的、经过存储器接口119的数据段data0至data7中包括的不同存储体的跟踪信息track_info《0:5》来生成行锤击地址。命令/地址生成模块115可以与行锤

击命令rh_cmd一起提供行锤击地址作为命令/地址信号c/a。

101.图10是用于描述根据本发明的一个实施例的用于根据从存储器控制器提供的行锤击地址来执行目标刷新操作的存储器芯片的操作的流程图。

102.参考图10,每个存储器芯片的ca缓冲器222可以接收来自存储器控制器110的命令/地址信号c/a以输出内部命令icmd和内部地址iadd。命令解码器223可以对内部命令icmd进行解码以生成刷新命令ref、目标刷新命令tref和行锤击命令rh_cmd(在s1010)。

103.地址锁存器电路240可以通过根据行锤击命令rh_cmd而对存储体地址ba《0:4》和行地址radd《0:5》进行锁存来生成行锤击存储体地址rh_ba《0:4》和行锤击行地址rh_add《0:5》(在s1020)。地址锁存器电路240可以通过根据目标刷新命令tref而对行锤击存储体地址rh_ba《0:4》进行解码来生成第一目标存储体刷新信号至第32目标存储体刷新信号tref_bk《0:31》。

104.解密电路260可以通过使用加密密钥key对行锤击行地址rh_add《0:5》进行解密来生成目标地址tadd《0:15》(在s1030)。

105.行控制电路212可以根据目标存储体刷新信号tref_bk《0:31》来执行对与目标地址tadd《0:15》相对应的字线wl的一个或多个相邻字线进行刷新的目标刷新操作(在s1040)。

106.在上述实施例中,已经描述了第一存储体bk0至第32存储体bk31被顺序地分组为四个并且在第一存储器芯片151至第八存储器芯片158的每一个内选择这些组中的一个组,但是本发明不限于此。根据一个实施例,多个存储体可以以各种方式被划分成组并且在每个存储器芯片内选择这些组中的一个组,并且选中的存储体的信息可以作为目标存储体信息被储存在每个芯片的模式设置电路中。

107.如上所述,在根据本发明的各种实施例的存储系统中,共享通道的存储器芯片可以仅提供每个存储器芯片内的选中的存储体的行锤击风险的跟踪信息,并且存储器控制器可以收集特定于存储体的跟踪信息并且最终提供行锤击地址。因此,可以使由跟踪电路占用的面积最小化。

108.此外,在根据本发明的各种实施例的存储系统中,每个存储器芯片可以对选中的存储体的跟踪信息进行加密并将其传送到存储器控制器,对从存储器控制器传送来的行锤击地址进行解密,以及执行目标刷新操作,从而增强存储系统的安全性。

109.已经在附图和说明书中描述了本公开的各种实施例。尽管这里使用了特定的术语,但这些术语仅用于描述本公开的实施例。因此,本公开不限于上述实施例并且在本公开的精神和范围内可以有许多变化。本领域技术人员应当清楚,除了本文中所公开的实施例之外,还可以在本公开的技术范围的基础上进行各种修改。这些实施例可以被组合以形成额外的实施例。

110.应该注意的是,尽管已经结合本公开的实施例描述了本公开的技术精神,但这仅用于说明目的,不应被理解为限制性的。本领域普通技术人员应当理解,在不脱离本公开和所附权利要求的技术精神的情况下,可以对其进行各种改变。

111.例如,对于在上述实施例中作为示例提供的逻辑门和晶体管,可以根据输入信号的极性而实现不同的位置和类型。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。