半导体存储器装置和包括半导体存储器装置的测试系统

1.于2020年12月14日在韩国知识产权局提交的题为“半导体存储器装置和包括半导体存储器装置的测试系统”的第10-2020-0174328号韩国专利申请通过引用全部包含于此。

技术领域

2.实施例涉及半导体存储器装置和包括半导体存储器装置的测试系统。

背景技术:

3.一旦半导体存储器装置被制造,制造商就可使用测试设备执行测试(例如,并行位测试(parallel bit test)),以测试半导体存储器装置是否正常操作。

技术实现要素:

4.实施例涉及一种半导体存储器装置,所述半导体存储器装置包括:测试模式数据存储装置,被配置为在测试操作期间,响应于寄存器写入命令和寄存器地址而存储具有第一预定数量的位的测试写入模式数据,并且响应于测试读取命令和测试模式数据选择信号而输出具有第一预定数量的位的测试读取模式数据;行解码器,被配置为通过对行地址进行解码来生成多个字线选择信号;列解码器,被配置为通过对列地址进行解码来生成多个列选择信号;存储器单元阵列,包括多个存储器单元并且被配置为从通过所述多个字线选择信号之一和所述多个列选择信号之一选择的存储器单元生成具有多个位的读取数据;读取路径单元,被配置为通过将具有所述多个位的读取数据串行化来生成各自具有第一预定数量的位的n个读取数据;以及测试读取数据生成单元,被配置为在测试操作期间,通过按第二预定数量的位将具有第一预定数量的位的测试读取模式数据与以第一数据速率生成的具有第一预定数量的位的所述n个读取数据中的每个进行比较来生成各自具有第三预定数量的位的n个测试读取数据,并且以低于第一数据速率的第二数据速率生成各自具有第三预定数量的位的所述n个测试读取数据。

5.实施例还涉及一种半导体存储器,所述半导体存储器包括:命令和地址生成器,被配置为在测试操作期间,通过响应于测试时钟信号对测试命令/地址进行接收和解码,来生成寄存器地址以及寄存器写入命令,生成行地址以及测试激活命令,或生成列地址以及测试写入命令,或者通过响应于测试时钟信号对测试命令/地址和专用信号进行接收和解码,来生成列地址和测试模式数据选择信号以及测试读取命令;测试模式数据存储装置,被配置为在测试操作期间,响应于寄存器写入命令和寄存器地址而存储具有第一预定数量的位的测试写入模式数据,并且响应于测试读取命令和测试模式数据选择信号而输出具有第一预定数量的位的测试读取模式数据;行解码器,被配置为通过对行地址进行解码来生成多个字线选择信号;列解码器,被配置为通过对列地址进行解码来生成多个列选择信号;存储器单元阵列,包括多个存储器单元并且被配置为将具有多个位的写入数据存储在通过所述多个字线选择信号之一和所述多个列选择信号之一选择的存储器单元中,或者从选择的存储器单元生成具有多个位的读取数据;测试写入数据生成单元,被配置为在测试操作期间,

响应于测试写入时钟信号,复制以第一数据速率施加的具有第二预定数量的位的n个测试写入数据中的每个或者反转并复制以第一数据速率施加的具有第二预定数量的位的n个测试写入数据,并且以高于第一数据速率的第二数据速率生成各自具有第一预定数量的位的n个写入数据;写入路径单元,被配置为通过将各自具有第一预定数量的位的所述n个写入数据并行化来生成具有多个位的写入数据;读取路径单元,被配置为通过将具有多个位的读取数据串行化来生成具有第一预定数量的位的n个读取数据;以及测试读取数据生成单元,被配置为在测试操作期间,通过按第三预定数量的位的第三预定数量的位将具有第一预定数量的位的测试读取模式数据与以第一数据速率生成的具有第一预定数量的位的所述n个读取数据中的每个进行比较来生成各自具有第四预定数量的位的n个测试读取数据,并且以低于第一数据速率的第三数据速率生成各自具有第四预定数量的位的所述n个测试读取数据。

6.实施例还涉及一种测试系统,所述测试系统包括:测试设备,被配置为:响应于测试时钟信号而施加测试命令/地址,响应于测试写入时钟信号,发送具有第一预定数量的位的测试数据或测试写入模式数据,并且接收测试数据;以及半导体存储器装置,半导体存储器装置包括:测试模式数据存储装置,被配置为在测试操作期间,当测试命令/地址是寄存器写入命令和寄存器地址时,响应于寄存器地址而存储具有第一预定数量的位的测试写入模式数据,并且当测试命令/地址是测试读取命令和测试模式数据选择信号时,响应于测试模式数据选择信号而输出具有第一预定数量的位的测试读取模式数据,行解码器,被配置为通过对行地址进行解码来生成多个字线选择信号,列解码器,被配置为通过对列地址进行解码来生成多个列选择信号,存储器单元阵列,包括多个存储器单元并且被配置为从通过所述多个字线选择信号之一和所述多个列选择信号之一选择的存储器单元生成具有多个位的读取数据,读取路径单元,被配置为通过将具有所述多个位的读取数据串行化来生成各自具有第一预定数量的位的n个读取数据,以及测试读取数据生成单元,被配置为在测试操作期间,通过按第二预定数量的位将具有第一预定数量的位的测试读取模式数据与以第一数据速率生成的具有第一预定数量的位的所述n个读取数据中的每个进行比较来生成各自具有第三预定数量的位的n个测试读取数据,并且以低于第一数据速率的第二数据速率生成各自具有第三预定数量的所述n个测试读取数据。

附图说明

7.通过参照附图详细描述示例实施例,特征对于本领域技术人员来说将变得清楚,在附图中:

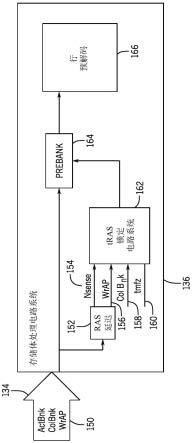

8.图1是示出根据示例实施例的测试系统的框图。

9.图2a和图2b是示出根据示例实施例的半导体存储器装置的框图。

10.图3是示出根据示例实施例的命令和地址生成单元的框图。

11.图4是示出根据示例实施例的从测试设备施加的命令和地址的真值表的示图。

12.图5a是示出根据示例实施例的测试模式数据存储装置的示图,并且图5b是示出根据示例实施例的测试模式数据存储装置的示图。

13.图6是用于描述根据示例实施例的寄存器写入操作的参考的操作时序图。

14.图7是示出根据示例实施例的测试写入数据生成单元的配置的示图。

15.图8是用于描述根据示例实施例的测试写入操作的参考的操作时序图。

16.图9是示出根据示例实施例的测试读取数据生成单元的配置的示图。

17.图10是用于描述根据示例实施例的测试读取操作的参考的操作时序图。

具体实施方式

18.图1是示出根据示例实施例的测试系统的框图。

19.参照图1,测试系统1000可包括测试设备100和半导体存储器装置200。

20.测试设备100可将测试时钟信号tck、测试命令/地址tca、测试时钟启用信号tcke、测试命令/地址总线反转信号tcabi和测试复位信号treset发送到半导体存储器装置200,并且可发送并接收测试数据tdq。

21.半导体存储器装置200可接收测试时钟信号tck、测试命令/地址tca、测试时钟启用信号tcke、测试命令/地址总线反转信号tcabi和测试复位信号treset,并且可发送并接收测试数据tdq。

22.可通过时钟信号端子ckp施加测试时钟信号tck。可通过命令/地址端子cap施加测试命令/地址tca。可通过时钟启用端子ckep施加测试时钟启用信号tcke。可通过命令/地址总线反转信号端子cabip施加测试命令/地址总线反转信号tcabi。可通过复位信号端子resetp施加测试复位信号treset。可通过数据端子dqp输入测试数据tdq并输出测试数据tdq。

23.测试设备100可在测试时钟信号tck的上升沿和下降沿施加测试命令/地址tca,可在测试写入操作期间响应于测试写入时钟信号twck的上升沿以第一数据速率(例如,单倍数据速率(sdr))发送测试数据tdq或测试写入模式数据tpdq,并且可在测试读取操作期间接收以等于或低于第一数据速率的第二数据速率发送的测试数据tdq。

24.半导体存储器装置200可以是在正常操作期间以第三数据速率(例如,双倍数据速率(ddr))操作的半导体存储器装置,并且可以是例如ddr、低功率ddr(lpddr)或图形ddr(gddr)装置。

25.在测试写入操作期间,半导体存储器装置200可接收以第一数据速率输入的测试数据tdq,并且可以以高于第一数据速率的第三数据速率内部生成测试写入数据。

26.半导体存储器装置200可通过将内部预存储的测试模式数据与以第三数据速率内部生成的读取数据进行比较来生成测试读取数据,并且在测试读取操作期间以第二数据速率生成测试读取数据作为测试数据tdq。

27.测试时钟启用信号tcke、测试命令/地址总线反转信号tcabi和测试复位信号treset可在测试读取操作期间用作测试模式数据选择信号。然而,在正常操作期间,时钟启用信号cke(通过时钟启用信号端子ckep施加)可用于对半导体存储器装置200中的内部时钟信号(未示出)、数据输入单元(未示出)和数据输出单元(未示出)进行去激活,命令/地址总线反转信号cabi(通过命令/地址总线反转信号端子cabip施加)可用于对命令/地址总线进行反转,并且复位信号reset(通过复位信号端子resetp施加)可用于对半导体存储器装置200进行复位。也就是说,测试时钟启用信号tcke、测试命令/地址总线反转信号tcabi和测试复位信号treset可以是在正常操作期间用于特殊目的的专用信号。

28.当测试时钟启用信号tcke、测试命令/地址总线反转信号tcabi和测试复位信号

treset处于“低”电平时,这可指示信号被激活。当测试时钟启用信号tcke、测试命令/地址总线反转信号tcabi和测试复位信号treset处于“高”电平时,这可指示信号被去激活。

29.图2a和图2b是示出根据示例实施例的半导体存储器装置的框图。

30.参照图2a和图2b,半导体存储器装置200可包括上电信号生成器20、初始化单元22、命令和地址生成单元24、模式设置寄存器26、内部时钟信号生成器28、延迟控制器30、测试模式数据存储装置32、行解码器34、列解码器36、存储器单元阵列38、读取路径单元40、测试读取数据生成单元42、数据输出单元44、写入路径单元46、测试写入数据生成单元48、数据输入单元50以及第一开关sw1至第六开关sw6。

31.下面将描述图2a和图2b中示出的块的功能。

32.上电信号生成器20可检测存储器电压ev的电平,并且当存储器电压ev达到目标电压电平时生成上电信号pup。

33.初始化单元22可在测试操作期间响应于上电信号pup和测试复位信号treset而生成初始化信号init,或者在正常操作期间响应于上电信号pup和复位信号reset而生成初始化信号init。

34.命令和地址生成单元24可通过响应于测试时钟信号tck对测试命令/地址tca进行解码,来生成模式设置码opc以及模式设置命令mrs。模式设置码opc可包括与测试模式启用信号tmrsen、测试写入模式控制信号twrp、写入延迟wl、读取延迟rl和/或突发长度bl相关的信息。

35.当测试模式启用信号tmrsen被激活时或当测试模式启用信号tmrsen和初始化信号init两者被激活时,命令和地址生成单元24可通过响应于测试时钟信号tck对测试命令/地址tca进行解码,来生成寄存器地址regadd以及寄存器写入命令regwr。

36.此外,当测试模式启用信号tmrsen被激活时,命令和地址生成单元24可响应于测试时钟信号tck而对施加的测试命令/地址tca进行解码,以生成测试激活命令tact和行地址radd,并且生成测试写入命令twr和列地址cadd。

37.此外,当测试模式启用信号tmrsen被激活时,命令和地址生成单元24可使用响应于测试时钟信号tck而施加的测试命令/地址tca、测试时钟启用信号tcke、测试命令/地址反转信号tcabi和测试复位信号treset,来生成测试读取命令trd、列地址cadd和测试模式数据选择信号otfps。

38.在正常操作期间,命令和地址生成单元24可响应于时钟信号ck和时钟启用信号cke而对命令和地址ca进行解码,以生成行地址radd以及激活命令act,生成列地址cadd以及写入命令wr或读取命令rd,并且生成模式设置码opc以及模式设置命令mrs。

39.模式设置寄存器26可通过与模式设置命令mrs一起施加的模式设置码opc,来设置写入延迟wl、读取延迟rl、突发长度bl、测试模式启用信号tmrsen和测试写入模式控制信号twrp。

40.在测试操作期间,内部时钟信号生成器28可接收测试时钟信号tck和测试写入时钟信号twck,并生成内部时钟信号ick和内部写入时钟信号iwck和iwck'。在正常操作期间,内部时钟信号生成器28可接收时钟信号ck和写入时钟信号wck,并生成内部时钟信号ick和内部写入时钟信号iwck。

41.在测试操作或正常操作期间,延迟控制器30可响应于测试写入命令twr或写入命

令wr以及内部时钟信号ick而生成写入延迟信号wlc(写入延迟信号wlc在被延迟与写入延迟wl对应的周期之后被激活,并且在被延迟与突发长度bl对应的周期之后被去激活),并且延迟控制器30可响应于测试读取命令trd或读取命令rd以及内部时钟信号ick而生成读取延迟信号rlc(读取延迟信号rlc在被延迟与读取延迟rl对应的周期之后被激活,并且在被延迟与突发长度bl对应的周期之后被去激活)。

42.测试模式数据存储装置32可包括多个寄存器(未示出)。在测试操作期间,测试模式数据存储装置32可响应于寄存器写入命令regwr和寄存器地址regadd而将测试写入模式数据tpdq存储在从多个寄存器之中选择的一个寄存器中,并且响应于测试读取命令trd和测试模式数据选择信号otfps从多个寄存器之中选择的一个寄存器输出测试读取模式数据tpd。

43.在测试操作或正常操作期间,行解码器34可通过对行地址radd进行解码而生成多个字线选择信号wl。

44.在测试操作或正常操作期间,列解码器36可通过对列地址cadd进行解码而生成多个列选择信号csl。

45.存储器单元阵列38可包括多个存储器单元(未示出)。存储器单元阵列38可将写入数据di存储到多个存储器单元之中的通过多个字线选择信号wl和多个列选择信号csl选择的存储器单元,或从多个存储器单元之中的通过多个字线选择信号wl和多个列选择信号csl选择的存储器单元输出读取数据do。例如,写入数据di和读取数据do中的每个可以是y位数据,并且y位可以是256位。

46.在测试读取操作和正常读取操作期间,读取路径单元40可通过将读取数据do串行化来生成n个m位读取数据do(在此可被称为n个读取数据)(例如,n和m中的每个可以是大于4的整数)。例如,读取路径单元40可通过将256位读取数据do串行化,来以ddr按1位顺序地生成16个16位读取数据do。

47.当第一开关sw1响应于测试读取命令trd被闭合时,测试读取数据生成单元42可通过按l位将n个m位读取数据do中的每个与m位测试读取模式数据tpd进行比较来生成n个(m/l)位测试读取数据tdo(其在此可被称为n个测试读取数据),并且响应于读取延迟信号rlc和内部测试写入时钟信号iwck',以第二数据速率按1位将n个(m/l)位测试读取数据tdo中的每个串行化(例如,l可以是大于2的整数)。例如,测试读取数据生成单元42可通过按2位、按4位、按8位或按16位将16个16位读取数据do中的每个与16位测试读取模式数据tpd进行比较来生成16个8位、4位、2位或1位测试读取数据tdo,并且将16个8位、4位、2位或1位测试读取数据tdo中的每个按1位顺序地串行化。

48.当第二开关sw2响应于测试读取命令trd被闭合时,数据输出单元44可以以第二数据速率按1位驱动n个(m/l)位测试读取数据tdo中的每个,以生成n个测试数据tdq。当第三开关sw3响应于读取命令rd被闭合时,数据输出单元44可以以第三数据速率按1位驱动n个m位正常读取数据ndo中的每个,以生成n个数据dq。例如,数据输出单元44可在测试读取操作期间通过以第二数据速率按1位顺序地驱动16个8位、4位、2位或1位测试读取数据tdo中的每个来生成16个8位、4位、2位或1位测试数据tdq,而数据输出单元44可在正常读取操作期间通过以第三数据速率按1位顺序地驱动16个16位正常读取数据ndo中的每个来生成16个16位数据dq。

49.在测试写入操作和正常写入操作期间,写入路径单元46可通过将n个m位写入数据di并行化来生成y位写入数据di。例如,写入路径单元46可通过将16个16位写入数据di并行化来生成256位写入数据di。

50.在测试写入操作期间,当第四开关sw4和第五开关sw5闭合时,测试写入数据生成单元48可响应于内部写入时钟信号iwck接收以第一数据速率施加的n个x位测试写入数据tdi,并以第三数据速率生成n个m位写入数据di。例如,测试写入数据生成单元48可响应于测试写入时钟信号twck的上升沿而接收以sdr施加的16个8位、4位、2位或1位测试写入数据tdi,以响应于内部写入时钟信号iwck(具有与测试写入时钟信号twck的频率相同的频率)的上升沿和下降沿而以ddr生成16个16位写入数据di。

51.在测试写入操作期间,当第五开关sw5闭合时,数据输入单元50可响应于测试写入时钟信号twck而按1位接收并缓冲以第二数据速率输入的n个测试数据tdq中的每个,并生成n个x位测试写入数据tdi。在正常写入操作期间,当第六开关sw6闭合时,数据输入单元50可响应于写入时钟信号wck而按1位接收并缓冲以第三数据速率输入的n个数据tq中的每个,并以第三数据速率生成n个m位的正常写入数据ndi。

52.图3是示出根据示例实施例的命令和地址生成单元的框图。

53.参照图3,命令和地址生成单元24可包括测试命令和地址生成器24-2以及正常命令和地址生成器24-4。

54.下面将描述图3中示出的块的功能。

55.当测试模式启用信号tmrsen被激活时,测试命令和地址生成器24-2可响应于测试时钟信号tck对测试命令/地址tca进行解码,并且可生成寄存器写入命令regwr和寄存器地址regadd,生成模式设置码opc以及模式设置命令mrs,生成行地址radd以及测试激活命令tact,或者生成列地址cadd以及测试写入命令twr。

56.此外,当测试模式启用信号tmrsen被激活时,测试命令和地址生成器24-2可使用响应于测试时钟信号tck而施加的测试时钟启用信号tcke、测试命令/地址总线反转信号tcabi和测试复位信号treset以及测试命令/地址tca,来生成测试读取命令trd、列地址cadd和测试模式数据选择信号otfps。在一个示例中,测试命令和地址生成器24-2可通过响应于测试时钟信号tck而对测试时钟启用信号tcke、测试命令/地址总线反转信号tcabi和测试复位信号treset中的至少一个以及测试命令/地址tca进行接收和解码,来生成列地址cadd和测试模式数据选择信号otfps以及测试读取命令trd。

57.测试模式数据选择信号otfps可以是预定数量的位的数据。例如,测试模式数据选择信号otfps可由测试时钟启用信号tcke、测试命令/地址总线反转信号tcabi和测试复位信号treset中的至少一个以及测试命令/地址tca中的未用于指示测试读取命令trd和列地址cadd(或未用于指示列地址cadd)的至少一个地址信号生成的数据组成。

58.在正常操作期间,正常命令和地址生成器24-4可响应于时钟信号ck和时钟启用信号cke而对命令和地址ca进行解码,并且可生成行地址radd以及激活命令act,生成列地址cadd以及写入命令wr或读取命令rd,并且生成模式设置码opc以及模式设置命令mrs。

59.图4是示出根据示例实施例的从测试设备施加的命令和地址的真值表的示图。

60.参照图4,当包括在测试命令/地址tca中的命令信号tca9和tca8在测试时钟信号tck的上升沿(r)分别处于“高”电平h和“低”电平l时,并且当包括在测试命令/地址tca中的

命令信号tca9和tca8在测试时钟信号tck的下降沿(f)分别处于“高”电平h和“低”电平l时,模式设置命令mrs可被指示。图4中的阴影区域ⅰ中的地址信号可指示模式设置寄存器26的地址,并且图4中的阴影区域ⅱ中的地址信号可指示模式设置码opc。

61.当包括在测试命令/地址tca中的命令信号tca9和tca8两者在测试时钟信号tck的上升沿处于“高”电平h时,并且当包括在测试命令/地址tca中的命令信号tca9、tca8、tca7和tca6在测试时钟信号tck的下降沿分别处于“高”电平h、“低”电平l、“高”电平h和“低”电平l时,寄存器写入命令regwr可被指示。图4中的阴影区域ⅲ中的地址信号可指示测试模式数据存储装置32的寄存器地址regadd。

62.与图4的示出的情况不同,标记有“x”的区域也可用于指示测试模式数据存储装置32的寄存器地址regadd。

63.当包括在测试命令/地址tca中的命令信号tca9在测试时钟信号tck的上升沿处于“低”电平l时,测试激活命令tact可被指示。图4中的阴影区域ⅳ中的地址信号可指示存储体地址。图4中的阴影区域

ⅴ

中的地址信号可指示行地址radd。

64.当包括在测试命令/地址tca中的命令信号tca9和tca8两者在测试时钟信号tck的上升沿处于“高”电平h时,并且当包括在测试命令/地址tca中的命令信号tca9至tca6中的全部在测试时钟信号tck的下降沿处于“低”电平l时,测试写入命令twr可被指示。图4中的阴影区域iv中的地址信号可指示存储体地址。图4中的阴影区域ⅵ中的地址信号可指示列地址cadd。“v”表示“高”电平h或“低”电平l(定义的逻辑电平)。

65.当包括在测试命令/地址tca中的命令信号tca9和tca8两者在测试时钟信号tck的上升沿处于“高”电平h时,并且当包括在测试命令/地址tca中的命令信号tca9、tca8、tca7和tca6在测试时钟信号tck的下降沿分别处于“低”电平l、“高”电平h、“低”电平l和“低”电平l时,测试读取命令trd可被指示。图4中的阴影区域ⅳ中的地址信号可指示存储体地址。图4中的阴影区域ⅵ中的地址信号可指示列地址cadd。

66.此外,在测试时钟信号tck的上升沿和下降沿施加的测试时钟启用信号tcke、测试命令/地址总线反转信号tcabi和测试复位信号treset以及在测试时钟信号tck的下降沿施加的地址信号tca5和tca3(其不用于指示列地址)可指示测试模式数据选择信号otfps。

67.图5a是示出根据示例实施例的测试模式数据存储装置的示图。

68.参照图5a,测试模式数据存储装置32可包括地址解码器32-2、寄存器单元32-4和输入/输出单元32-6。

69.地址解码器32-2可响应于寄存器写入命令regwr对寄存器地址regadd进行解码,以激活k个寄存器选择信号rsel1至rselk之中的一个(k可以是大于2的整数)。地址解码器32-2可响应于测试读取命令trd对测试模式数据选择信号otfps进行解码,以激活k个寄存器选择信号rsel1至rselk之中的一个。

70.寄存器单元32-4可包括k个寄存器reg1至regk。k个寄存器reg1至regk可响应于k个选择信号rsel1至rselk而存储或输出m位测试模式数据tpd。

71.输入/输出单元32-6可响应于寄存器写入命令regwr,输出m位测试写入模式数据tpdq作为m位测试模式数据tpd。输入/输出单元32-6可响应于测试读取命令trd,输出m位测试模式数据tpd作为m位测试读取模式数据tpd。

72.图5b是示出根据示例实施例的测试模式数据存储装置的示图。

73.参照图5b,测试模式数据存储装置32'可包括地址解码器32-2'、寄存器单元32-4'和选择器32-6'。

74.地址解码器32-2'可通过响应于寄存器写入命令regwr对寄存器地址regadd进行解码,激活k个寄存器选择信号rsel1至rselk之中的一个。

75.寄存器单元32-4'可包括k个寄存器reg1至regk。k个寄存器reg1至regk可响应于k个选择信号rsel1至rselk而存储m位测试模式数据tpd,并且响应于测试读取命令trd而输出k个m位测试模式数据tpd。

76.选择器32-6'可响应于测试读取命令trd和测试模式数据选择信号otfps,选择k个m位测试模式数据tpd之中的一个,并且输出选择的m位测试模式数据tpd作为m位测试读取模式数据tpd。

77.图6是用于描述根据示例实施例的寄存器写入操作的参考的操作时序图。

78.参照图6,可分别在测试时钟信号tck的上升沿和下降沿施加测试命令/地址tca_f11和测试命令/地址tca_s11,并且可响应于测试写入时钟信号twck施加m位测试模式数据tpd1作为测试写入模式数据tpdq。包括在测试命令/地址tca_f11和测试命令/地址tca_s11中的命令com可指示寄存器写入命令regwr。包括在测试命令/地址tca_f11和测试命令/地址tca_s11中的地址add可指示寄存器地址regadd1。可响应于寄存器写入命令regwr而生成与寄存器地址regadd1对应的寄存器选择信号rsel1。图5a的测试模式数据存储装置32可响应于寄存器选择信号rsel1将m位测试模式数据tpd1存储在寄存器reg1中。

79.当寄存器地址regadd从regadd2改变为regaddk并且测试模式数据tpd从tpd2改变为tpdk时,上述操作可被重复执行,以将不同的(k-1)个m位测试模式数据tpd2至tpdk分别存储在(k-1)个寄存器reg2至regk中。

80.图7是示出根据示例实施例的测试写入数据生成单元的配置的示图。

81.参照图7,测试写入数据生成单元48可包括复制电路48-2以及复制和反转电路48-4。图7示出与n个数据端子dqp1至dqpn之中的一个对应的测试写入数据生成器的配置。例如,当存在16个数据端子时,测试写入数据生成单元48可包括16个测试写入数据生成器。

82.复制电路48-2可响应于内部写入时钟信号iwck的“高”电平而发送测试写入数据tdi作为写入数据di。

83.复制和反转电路48-4可响应于内部写入时钟信号iwck的“低”电平而发送测试写入数据tdi作为写入数据di,或者发送反转的测试写入数据作为写入数据di。

84.例如,当测试写入模式控制信号twrp处于“低”电平时,复制和反转电路48-4可发送测试写入数据tdi作为写入数据di,并且当测试写入模式控制信号twrp处于“高”电平时,复制和反转电路48-4可将测试写入数据tdi进行反转并发送反转的测试写入数据作为写入数据di。

85.图8是用于描述根据示例实施例的测试写入操作的参考的操作时序图。

86.在执行测试写入操作之前,可响应于模式设置命令mrs执行模式设置操作,以将测试模式启用信号tmrsen设置为激活状态,将写入延迟wl设置为3并且将突发长度bl设置为16,并且设置测试写入模式控制信号twrp。然后,可响应于测试激活命令tact施加行地址radd1。

87.图8是基于这样的假设:在行地址radd1与测试激活命令tact一起被施加之后执行

连续测试写入操作。

88.参照图8,可分别响应于测试时钟信号tck的上升沿和下降沿而施加测试命令/地址tca_f21和测试命令/地址tca_s21。包括在测试命令/地址tca_f21和测试命令/地址tca_s21中的命令com可指示测试写入命令twr。包括在测试命令/地址tca_f21和测试命令/地址tca_s21中的地址add可包括列地址cadd1。

89.参照图2b和图8,行解码器34可对行地址radd1进行解码,以选择多个字线选择信号wl之中的一个字线选择信号(例如,wl1(未示出)),并且列解码器36可对列地址cadd1进行解码,以选择多个列选择信号csl之中的一个列选择信号(例如,csl1(未示出))。存储器单元阵列38的存储器单元可由多个字线选择信号wl中的一个以及多个列选择信号csl中的一个来选择。

90.参照图8,在从施加测试命令和地址tca_f21的测试时钟周期tck的3个周期之后,响应于测试写入时钟信号twck,以sdr施加测试数据tdq“01010101”。

91.参照图2b和图7,当测试写入模式控制信号twrp处于“低”电平时,测试写入数据生成单元48的测试写入数据生成器可复制通过数据输入单元50施加的测试写入数据“01010101”,并且响应于内部写入时钟信号iwck(其与测试写入时钟信号twck具有相同的频率)以ddr生成写入数据di“0011001100110011”。或者当测试写入模式控制信号twrp处于“高”电平时,测试写入数据生成单元48的测试写入数据生成器可复制和反转通过数据输入单元50施加的测试写入数据tdi“01010101”,并且响应于内部写入时钟信号iwck以ddr生成写入数据di“0110011001100110”。测试写入数据生成单元48可按1位顺序地生成16个16位写入数据di中的每个。写入路径单元46可接收16个16位写入数据di,将16个16位写入数据di并行化,并且将256位写入数据di输出到选择的存储器单元。

92.随后,可通过执行上述操作将写入数据di“0000000000000000”或“0101010101010101”存储在通过行地址radd1和列地址cadd2选择的存储器单元中。此外,然后可将写入数据di“1111111111111111”或“1010101010101010”存储在通过行地址radd1和列地址cadd3选择的存储器单元中。

93.在上述测试写入操作中,即使由于图1中示出的测试设备100的操作速度的限制而响应于测试写入时钟信号twck以sdr施加测试数据tdq,半导体存储器装置200也可响应于内部写入时钟信号iwck以ddr内部地生成测试写入数据tdi。

94.图9是示出根据示例实施例的包括在测试读取数据生成单元中的测试读取数据生成器的配置的示图。

95.参照图9,测试读取数据生成器42'可包括比较单元42”和寄存器42-5,比较单元42”包括第一比较器42-1至第四比较器42-4。

96.图9基于这样的假设:16位测试读取模式数据tpd是tpd15至tpd0,并且串行施加的16位读取数据do是do15至do0。

97.图9示出与n个数据端子dqp1至dqpn中的一个对应的测试读取数据生成器42'的配置。例如,当存在16个数据端子时,测试读取数据生成单元42可包括16个测试读取数据生成器42'。

98.参照图9,第一比较器42-1可将4位测试读取模式数据tpd15至tpd12与4位读取数据do15至do12进行比较。当4位测试读取模式数据tpd15至tpd12与4位读取数据do15至do12

匹配时,第一比较器42-1可生成数据“0”,否则,第一比较器42-1可生成数据“1”。

99.第二比较器42-2可将4位测试读取模式数据tpd11至tpd8与4位读取数据do11至do8进行比较。当4位测试读取模式数据tpd11至tpd8与4位读取数据do11至do8匹配时,第二比较器42-2可生成数据“0”,否则,第二比较器42-2可生成数据“1”。

100.类似地,第三比较器42-3和第四比较器42-4中的每个可通过比较不同的4位数据来生成数据“0”或“1”。

101.寄存器42-5可将从第一比较器42-1至第四比较器42-4输出的数据存储为4位测试读取数据tdo3至tdo0,并且响应于内部写入时钟信号iwck'按1位顺序地生成测试读取数据tdo3至tdo0。例如,内部写入时钟信号iwck'是具有比内部写入时钟信号iwck的频率低四倍的频率的信号,并且可与测试时钟信号tck具有相同的频率。可响应于具有等于或低于测试写入时钟信号twck的频率的频率的时钟信号的上升沿而生成测试读取数据tdo3到tdo0。

102.图10是用于描述根据示例实施例的测试读取操作的参考的操作时序图。

103.在执行测试读取操作之前,可响应于模式设置命令mrs来执行模式设置操作,以将测试模式启用信号tmrsen设置为激活状态,并且将读取延迟rl设置为3,将突发长度bl设置为16。然后,可响应于测试激活命令tact施加行地址radd1。

104.图10是基于这样的假设:在行地址radd1与测试激活命令tact一起被施加之后执行连续测试读取操作。

105.参照图10,可分别响应于测试时钟信号tck的上升沿和下降沿而施加测试命令/地址tca_f31和测试命令/地址tca_s31。参照图4,包括在测试命令/地址tca_f31和测试命令/地址tca_s31中的命令com可指示测试读取命令trd,并且包括在测试命令/地址tca_f31和测试命令/地址tca_s31中的地址add可包括列地址cadd1。

106.参照图2b和图10,行解码器34可对行地址radd1进行解码,以选择多个字线选择信号wl之中的一个字线选择信号(例如,wl1(未示出)),并且列解码器36可对列地址cadd1进行解码,以选择多个列选择信号csl之中的一个列选择信号(例如,csl1(未示出))。存储器单元阵列38的存储器单元可由多个字线选择信号wl中的一个以及多个列选择信号csl中的一个来选择,并且生成y位读取数据do。读取路径单元40可通过将y位读取数据do串行化来生成n个m位读取数据do“1011001100110011”。

107.参照图4和图10,包括在测试命令/地址tca_f31和测试命令/地址tca_s31中的地址可指示测试模式数据选择信号otfps的被设置为“0”的部分(例如,最低有效位(lsb)),并且测试时钟启用信号tcke、测试复位信号treset和测试命令/地址总线反转信号tcabi可指示测试模式数据选择信号otfps的被设置为“000000”的剩余部分(例如,高6位)。也就是说,测试模式数据选择信号otfps可以是“0000000”。

108.参照图2a、图5a、图5b和图9,测试模式数据存储装置32可响应于测试模式数据选择信号otfps,输出存储在寄存器单元32-4或32-4'的寄存器reg1中的测试模式数据tpd1“0011001100110011”作为测试读取模式数据tpd。测试读取数据生成单元42的测试读取数据生成器可按4位将16位读取数据do“1011001100110011”与16位测试读取模式数据tpd“0011001100110011”进行比较,并且响应于内部写入时钟信号iwck'按1位顺序地生成4位测试读取数据tdo“1000”。当16位读取数据do与16位测试读取模式数据tpd完全匹配时,可生成4位测试读取数据tdo“0000”。数据输出单元44可按1位串行地生成n个4位测试读取数

据tdo中的每个作为测试数据tdq。

109.虽然在以上示例实施例中已经描述了测试读取数据生成单元42的测试读取数据生成器串行地生成4位测试读取数据tdo,但是测试读取数据生成器可被配置为包括两个比较器并因此串行地生成2位测试读取数据tdo,可被配置为包括八个比较器并因此串行地生成8位测试读取数据tdo,或者可被配置为包括16个比较器并因此生成16位测试读取数据tdo。

110.在上述测试读取操作中,半导体存储器装置200可在内部预先按(m/k)位与(m/k)位将m位测试模式数据与m位读取数据进行比较(这里,k是小于m且大于2的整数),生成比m位少的k位的测试读取数据,并且将测试读取数据发送到测试设备100。因此,半导体存储器装置200可以以等于或低于sdr的数据速率将测试数据tdq发送到测试设备100。因此,尽管测试设备100的操作速度有限,但测试时间不会增加。

111.通过总结和回顾,测试设备可以以与半导体存储器装置利用实际存储器系统中的控制单元(例如,中央处理器(cpu)或图形处理器(gpu))执行正常操作的操作速度相同的操作速度执行测试操作。然而,与半导体存储器装置的不断增大的操作速度相比,测试设备的操作速度没有相应地增大,因此,半导体存储器装置的操作速度先于测试设备的操作速度。例如,虽然半导体存储器装置可能能够以16千兆位(gb)每秒的速率发送并接收数据,但是测试设备可能仅能够以8gb每秒的速率发送并接收数据。因此,花费更长的时间来测试半导体存储器装置。

112.如上所述,实施例可提供一种降低测试时间的半导体存储器装置,以及包括半导体存储器装置的测试系统。

113.根据示例实施例,即使当测试设备的操作速度低于半导体存储器装置的操作速度时,半导体存储器装置也可通过将测试模式数据与以第三数据速率生成的读取数据进行比较来在内部生成测试读取数据,并且以低于第一数据速率的第二数据速率输出测试读取数据。因此,可不增加测试时间。

114.在此已经公开了示例实施例,尽管采用了特定术语,但是它们仅以一般性和描述性的含义被使用并将被解释,而不是为了限制的目的。在一些情况下,如本领域普通技术人员将清楚的,除非另外明确地指示,否则在提交本技术时起,结合特定实施例描述的特征、特性和/或元件可被单独使用或与结合其他实施例描述的特征、特性和/或元件组合使用。因此,本领域技术人员将理解,在不脱离如所附权利要求中阐述的本发明的精神和范围的情况下,可进行形式和细节上的各种改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。