1.本公开的实施例大体上涉及存储器装置领域。更明确来说,本公开的实施例涉及存储器存储体的自动预充电过程(例如,具有自动预充电(wr-autop)的写入)。

背景技术:

2.存储器装置中的各个操作可依赖于存储器装置中的裸片(例如存储器存储体)之间的时钟。例如,时钟可从例如主机装置(例如处理器)的外部装置接收。举例来说,在存储器装置中,利用动态随机可存取存储器(dram)的双倍数据速率版本5(ddr5)可使用裸片间时钟来处理wr-autop过程。随着存储器装置中的速度增加及不同连接技术(例如线接合)的流行,时钟递送可能引起在裸片之间传输高速信号的问题。为了适应,可增加高速信号的驱动强度以适应不同连接技术上的归因于不同连接技术的寄生效应的较高频率信号。

3.本公开的实施例可涉及上文陈述的问题中的一或多者。

技术实现要素:

4.一方面,本公开涉及一种半导体装置,其包括:命令接口,其经配置以接收具有自动预充电命令的写入;存储体特定解码器,其经配置以解码具有用于存储器存储体的自动预充电命令的所述写入及输出写入自动预充电(wrap)信号;及存储体处理电路系统,其包括锁定电路系统,其中所述存储体处理电路系统经配置以接收所述wrap信号及在接收到所述wrap信号之后且至少部分基于所述wrap信号指示具有自动预充电命令的所述写入的接收来施加写入恢复时间(twr)锁定。

5.另一方面,本公开涉及一种方法,其包括:在存储器装置的命令接口处接收写入自动预充电(wr-autop)命令;将所述wr-autop命令传输到解码器;在所述解码器中解码所述wr-autop命令;在所述解码器中产生wr-autop信号并将所述wr-autop信号传输到经标定用于所述wr-autop命令的存储器存储体中的存储体处理电路系统;及响应于在所述存储体处理电路系统处接收到所述wr-autop信号,至少部分基于所述wr-autop信号施加所述存储器存储体的锁定。

6.另一方面,本公开涉及一种存储器装置,其包括:命令接口,其经配置以从主机装置接收写入自动预充电命令;及多个存储器存储体,每一存储器存储体包括:存储体特定解码器,其经配置以响应于解码标定相应存储器存储体的写入自动预充电命令产生写入自动预充电信号(wrap信号);及存储体处理电路系统,其经配置以接收所述wrap信号及响应于接收到所述wrap信号重新使用行地址选通时间(tras)锁定电路系统来施加写入恢复时间(twr)锁定。

附图说明

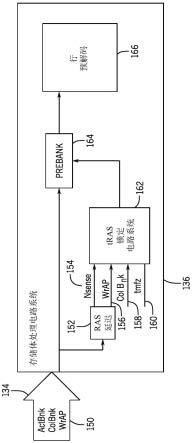

7.图1是说明根据本公开的实施例的存储器装置的特定特征的简化框图;

8.图2是根据本公开的实施例的图1的存储器装置中的存储器存储体堆叠的框图视

图;

9.图3是根据本公开的实施例的使用图2的存储器存储体之间的专用预充电时钟传播的写入自动预充电(wr-autop)的框图;

10.图4是根据本公开的实施例的图3的wr-autop的时序图;

11.图5是根据本公开的实施例的没有在图2的存储器存储体之间传播的专用预充电时钟的使用存储体控制件的wr-autop的框图;

12.图6是根据本公开的实施例的图5的存储体控制件的框图;

13.图7是根据本公开的实施例的具有单独行地址选通时间(tras)及写入恢复时间(twr)锁定信号的使用图5的存储体控制件的时序图;及

14.图8是根据本公开的实施例的将twr锁重新用于tras锁的图5的存储体控制件的框图。

具体实施方式

15.下文将描述一或多个特定实施例。为了提供这些实施例的简洁描述,说明书中未描述实际实施方案的所有特征。应了解,在任何此实际实施方案的开发中,如在任何工程设计或设计项目中,必须作出众多实施方案特定决策以实现开发者的特定目标,例如符合系统相关及商业相关约束,其可因实施方案而异。此外,应了解,此开发努力可能是复杂且耗时的,但对于受益于本公开的所属领域的一般技术人员,这仍是设计及制造(fabrication/manufacture)的例行任务。

16.激活命令可先于对应操作,例如预充电操作。一些预充电操作可专门用于一种类型的操作(例如具有自动预充电的写入操作)。举例来说,写入自动预充电操作可在写入操作之后启用快速、自动预充电。然而,写入操作的自动预充电操作可具有与其它预充电操作不同的时序。例如,写入自动预充电(wr-auotop)可在用于存储器存储体的写入恢复时间(twr)内使用额外时序锁定/延迟。此额外锁定周期可使用移位器及fifo实施以实施wr-autop的额外延迟。然而,这些电路系统可使用利用可增加面积及功耗成本的时钟(例如clkg)的时钟移位器来实施。为了消除额外时钟及时钟限制电路系统,可将wr-autop信号发送到存储体以将tras锁定重新用于twr锁定来将正确时序用于wr-autop操作。

17.现转到图,图1是说明存储器装置10的特定特征的简化框图。明确来说,图1的框图是说明存储器装置10的特定功能性的功能框图。根据一个实施例,存储器装置10可为双倍数据速率5型同步动态随机存取存储器(ddr5 sdram)装置。ddr5 sdram的各个特征允许相较于前几代ddr sdram的减小的功耗、更大的带宽及更大的存储容量。

18.存储器装置10可包含数个存储器存储体12。例如,存储器存储体12可为ddr5sdram存储器存储体。存储器存储体12可经提供于经布置在双列直插式存储器模块(dimms)上的一或多个芯片(例如sdram芯片)上。如应了解,每一dimm可包含数个sdram存储器芯片(例如x8或x16存储器芯片)。每一sdram存储器芯片可包含一或多个存储器存储体12。存储器装置10表示具有数个存储器存储体12的单个存储器芯片(例如sdram芯片)的一部分。针对ddr5,存储器存储体12可进一步经布置以形成存储体群组。例如,针对8千兆字节(gb)ddr5 sdram,存储器芯片可包含布置成8个存储体群组的16个存储器存储体12,每一存储体群组包含2个存储器存储体。例如,针对16gb ddr5 sdram,存储器芯片可包含布置成8个存储体

群组的32个存储器存储体12,每一存储体群组包含4个存储器存储体。可取决于整体系统的应用及设计利用存储器装置10上的存储器存储体12的各种其它配置、组织及大小。在存储器装置10的一些实施例中,存储器存储体12可经堆叠成垂直布置。例如,rank0存储体可经耦合到印刷电路板或控制器裸片,其中rank1到n(例如1、2、3、4)存储体经堆叠于rank0存储体顶部上。在一些实施例中,rank0存储体可用作其它等级的存储器存储体12的“主控”。

19.存储器装置10可包含命令接口14及输入/输出(i/o)接口16。命令接口14经配置以从例如处理器或控制器的外部装置(未展示)提供数个信号(例如信号15)。处理器或控制器可将各种信号15提供给存储器装置10以促进将写入到存储器装置10或从存储器装置10读取的数据的传输及接收。

20.如应了解,命令接口14可包含数个电路,例如时钟输入电路18及命令地址输入电路20,例如以确保信号15的适当处置。命令接口14可从外部装置接收一或多个时钟信号。通常,双倍数据速率(ddr)存储器利用系统时钟信号的差分对,在本文中称为真时钟信号(clk_t)及条状时钟信号(clk_b)。ddr的正时钟边缘指代其中上升真时钟信号clk_t与下降条状时钟信号clk_b交叉的点,而负时钟边缘指示下降真时钟信号clk_t的转变及条状时钟信号clk_b的上升。通常在时钟信号的正边缘上输入命令(例如,读取命令、写入命令等),且在正及负时钟边缘两者上传输或接收数据。

21.时钟输入电路18接收真时钟信号(clk_t)及条状时钟信号(clk_b)并产生内部时钟信号clk。内部时钟信号clk经供应到内部时钟产生器,例如延时锁相环路(dll)电路30。dll电路30基于接收到的内部时钟信号clk产生内部时钟信号lclk。内部时钟信号lclk经供应到(例如)i/o接口16,且用作用于确定读取数据的输出时序的时序信号。时钟输入电路18还可包含门控电路系统,其经配置以门控接收到的时钟到内部时钟的传播以防止移动存储器装置10中的电容器电压及消耗功率。因此,除非将使用内部时钟,否则时钟输入电路18可利用时钟门控来阻止内部时钟的传播。

22.内部时钟信号clk在传播时还可经提供给存储器装置10内的各种其它组件且可用于产生各种额外内部时钟信号。例如,内部时钟信号clk可经提供给命令解码器32。命令解码器32可从命令总线34接收命令信号且可解码命令信号以提供各种内部命令。例如,命令解码器32可经由总线36将命令信号提供给dll电路30以协调内部时钟信号lclk的产生。例如,内部时钟信号lclk可用于对通过io接口16的数据进行时控。

23.此外,命令解码器32可解码命令,例如读取命令、写入命令、模式寄存器设置命令、激活命令等,并经由总线路径40提供对对应于命令的特定存储器存储体12的存取。如应了解,存储器装置10可包含各种其它解码器,例如行解码器及列解码器,以促进对存储器存储体12的存取。在一个实施例中,每一存储器存储体12包含存储体控制件22,其提供必要解码(例如行解码器及列解码器),还包含其它特征,例如时序控制及数据控制,以促进到及来自存储器存储体12的命令的执行。

24.存储器装置10基于从外部装置(例如处理器)接收到的命令/地址信号执行例如读取命令及写入命令的操作。在一个实施例中,命令/地址总线可为适应命令/地址信号(ca《13:0》)的14位总线。使用时钟信号(clk_t及clk_b)将命令/地址信号时控到命令接口14。命令接口可包含命令地址输入电路20,其经配置以接收及传输命令以通过(例如)命令解码器32提供对存储器存储体12的存取。另外,命令接口14可接收芯片选择信号(cs_n)。cs_n信号

使存储器装置10能够处理传入ca《13:0》总线上的命令。对存储器装置10内的特定存储体12的存取与命令一起编码于ca《13:0》总线上。

25.另外,命令接口14可经配置以接收数个其它命令信号。例如,裸片端接命令/地址(ca_odt)信号可经提供以促进存储器装置10内的适当阻抗匹配。复位命令(reset_n)可用于在(例如)加电期间复位命令接口14、状态寄存器、状态机及类似物。命令接口14还可接收命令地址反转(cai)信号,其可经提供以(例如)取决于用于特定存储器装置10的命令/地址路由反转命令/地址总线上的命令/地址信号ca《13:0》的状态。镜像(mir)信号也可经提供以促进镜像功能。mir信号可用于多路复用信号使得其可基于多个存储器装置在特定应用中的配置经交换以实现信号到存储器装置10的特定路由。也可提供用以促进存储器装置10的测试的各种信号,例如测试启用(ten)信号。例如,ten信号可用于将存储器装置10置于测试模式中以进行连接性测试。

26.命令接口14还可用于针对可检测的特定错误将警报信号(alert_n)提供给系统处理器或控制器。例如,如果检测到循环冗余校验(crc)错误,那么可从存储器装置10传输警报信号(alert_n)。也可产生其它警报信号。此外,用于从存储器装置10传输警报信号(alert_n)的总线及引脚在例如使用ten信号执行的连接性测试模式的特定操作期间可用作输入引脚,如上文描述。

27.利用上文论述的命令及计时信号,通过经由io接口16传输及接收数据信号44,可将数据发送到存储器装置10及从存储器装置10发送数据。更明确来说,可经由数据路径46将数据发送到存储器存储体12或从存储器存储体12检索数据,所述数据路径46包含多个双向数据总线。通常称为dq信号的数据io信号通常在一或多个双向数据总线中传输及接收。针对特定存储器装置,例如ddr5 sdram存储器装置,io信号可划分成高位字节及低位字节。例如,针对x16存储器装置,io信号可划分成对应于(例如)数据信号的高位字节及低位字节的高及低io信号(例如,dq《15:8》及dq《7:0》)。

28.为了允许存储器装置10内的较高数据速率,例如ddr存储器装置的特定存储器装置可利用数据选通信号,通常称为dqs信号。dqs信号由发送数据(例如,针对写入命令)的外部处理器或控制器驱动或由存储器装置10(例如,针对读取命令)驱动。针对读取命令,dqs信号实际上是具有预定模式的额外数据输出(dq)信号。针对写入命令,dqs信号用作用以捕获对应输入数据的时钟信号。如同时钟信号(clk_t及clk_b),dqs信号可经提供作为用以在读取及写入期间提供差分对信令的数据选通信号差分对(dqs_t及dqs_b)。针对特定存储器装置,例如ddr5 sdram存储器装置,dqs信号差分对可划分成对应于(例如)发送到存储器装置10及从存储器装置10发送的数据的高位字节及低位字节的高位及低位数据选通信号(例如udqs_t及udqs_b;ldqs_t及ldqs_b)。

29.也可通过io接口16将阻抗(zq)校准信号提供给存储器装置10。zq校准信号可经提供给参考引脚且用于通过跨工艺、电压及温度(pvt)值的变化调整存储器装置10的上拉及下拉电阻器调谐输出驱动器及odt值。因为pvt特性可能会影响zq电阻器值,所以zq校准信号可经提供给zq参考引脚以用于调整电阻来将输入阻抗校准到已知值。如应了解,精密电阻器通常耦合于存储器装置10上的zq引脚与存储器装置10外部的gnd/vss之间。此电阻器充当用于调整内部odt及io引脚的驱动强度的参考。

30.另外,可通过io接口16将环回信号(loopback)提供给存储器装置10。在测试或调

试阶段期间,可使用环回信号来将存储器装置10设置成其中信号通过相同引脚环回通过存储器装置10的模式。例如,环回信号可用于设置存储器装置10来测试存储器装置10的数据输出(dq)。环回可包含数据及选通两者或可能仅包含数据引脚。此通常意在用于监测由存储器装置10在io接口16处捕获的数据。

31.如应了解,也可将例如电力供应器电路(用于接收外部vdd及vss信号)、模式寄存器(用以定义各种模式的可编程操作及配置)、读取/写入放大器(用以在读取/写入操作期间放大信号)、温度传感器(用于感测传感器装置10的温度)等的各种其它组件并入到存储器装置10中。因此,应理解,提供图1的框图仅用来强调存储器装置10的某些功能特征以帮助进行后续详细描述。

32.图2是个别地称为rank0存储体12a、rank1存储体12b、rank2存储体12c及rank3存储体12d的存储器存储体12的堆叠50的框图。每一存储体可包含/利用一或多个裸片。尽管所说明的实施例包含四个存储器存储体12,但存储器装置10的其它实施例可包含不同数目个存储器存储体12,例如2个、4个、8个或多于8个存储体。由于wr-autop命令可独立于堆叠50中的每一裸片而发生,clkg 52可从rank0存储体12a发送到其它存储体(例如rank1存储体12b、rank2存储体12c及rank3存储体12d)中的每一者以帮助存储器存储体12执行wr-autop操作。换句话说,clkg 52由存储体12用于执行wr-autop操作。然而,clkg 52的产生及传输可由于wr-autop突发信息在存储器存储体12(例如rank1存储体12b)处接收而复杂化,其中传回信息从存储器存储体12传输回到对应rank0存储体12a。例如,在存储体控制件22处接收到的标定rank1存储体12b的wr-autop命令经由路径53从rank0存储体12a传输到rank1存储体12b,其中传回信息经由路径54从rank1存储体12b传输回到rank0存储体12a。类似地,在存储体控制件22处(例如,经由命令接口14从主机装置)接收到的标定rank2存储体12c的wr-autop命令经由路径55从rank0存储体12a传输到rank2存储体12c,其中传回信息经由路径56从rank2存储体12c传输回到rank0存储体12a。同样地,在存储体控制件22处接收到的标定rank3存储体12d的wr-autop命令经由路径57从rank0存储体12a传输到rank3存储体12d,其中传回信息经由路径58从rank3存储体12d传输回到rank0存储体12a。无论哪一存储器存储体12被标定,rank0存储体12a可解码及添加接着可由相应存储体12解码的芯片id鉴定。然而,即使在存储器存储体未标定用于wr-autop操作时,存储器存储体12中的每一者也可接收clkg 52并使其内部化。

33.在一些实施例中,rank2存储体12c与rank0存储体12a之间的通信可通过rank1存储体12b传输,其中到rank2存储体12c的通信经由路径53及55传输且传回通信经由路径54及56传输。替代地,经由路径55及56的通信可旁通rank1存储体12b。

34.同样地,在一些实施例中,rank3存储体12d与rank0存储体12a之间的通信可通过rank1存储体12b及/或rank2存储体12c传输,其中到rank3存储体12d的通信经由路径57及53及/或55传输且传回通信经由路径58及54及/或56传输。替代地,经由路径58及57的通信可旁通rank1存储体12b及/或rank2存储体12c。

35.无论所使用的前述实施方案为何,每一传输包含用于wr-autop操作的至少双向通信行进。此外,关于在高速度下进行的一些实施方案(例如线接合3d实施方案),时钟的驱动强度相当高。因此,从rank0存储体12a行进到其它存储器存储体12的时钟可消耗相对高的功率量。信号路径由定位于rank0存储体12a的区域(例如中心区域)中的传输器及经标定存

储器存储体12中的目标接收器组成。此接收器可经定位于裸片内的中心区域中。针对达到经标定存储体12的接收器的clkg 52,clkg 52可在存储体12的边缘接收器处无芯片id鉴定的情况下传递通过存储器存储体12的边缘。因此,clkg52到中心区域中的接收器的传输可致使clkg 52传输通过存储体12中的每一者的至少某个部分,从而增加clkg 52的产生及传输的功耗。

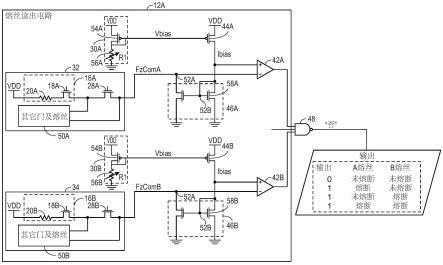

36.图3是可在存储器装置10中执行的wr-auotop过程70的框图。命令71及时钟clkw 72在列地址选通(cas)写入延时(cwl)移位器74处接收。命令71(例如wr-autop命令)在命令接口14处从主机装置接收。clkw 72可与图1中的clk_t/clk_c相同或从clk_t/clk_c产生。cwl移位器74可经定位于命令接口14、命令解码器32、总线路径40或数据路径46中。cwl移位器74含有使用clkw 72使命令71移位的数个移位器(例如触发器/锁存器)。移位量可等于或大于cwl。例如,移位可包含cwl加上等于突发长度除以2的循环数目以实现双倍数据速率。当对应于命令的列地址被接收时,cwl移位器74将列地址推动到列地址存储体群组及存储体地址(bgba)fifo 76上。当命令已传递通过cwl移位器74时,cwl移位器74从bgba fifo 76弹出列地址。在一些实施例中,从bgba fifo 76弹出的列地址指向基于接收到的命令的类型的位置(例如wr-autop特定fifo/移位器)。

37.经移位命令78从cwl移位器74传输到接收时钟clkg 52的wr-autop移位器80。wr-autop移位器80包含使经移位命令78移位达写入恢复时间(twr)的数个移位器(例如触发器/锁存器)。twr可使用存储器装置10的设置循环数目的模式寄存器来设置。举例来说,模式寄存器可包含数个位(例如4个),其可用于选择将延迟twr以允许在写入之后的充分的恢复时间的时钟循环的数目。举例来说,twr可经指定为48、54、60、66、72、78、84、90、96或任何其它数目个时钟循环作为twr来设置特定持续时间(例如30ns)。

38.当经移位命令78进入wr-autop移位器80时,进行到到wr-autop bgba fifo 82上的推动。例如,存储体地址可从bgba fifo 76推动。当经移位命令78完成通过wr-autop移位器80的移位时,经弹出存储体地址84从相应wr-autop bgba fifo 82的堆叠的顶部弹出。接着,将经弹出存储体地址84传输到用于解码对应于经弹出存储体地址84的twr经移位命令88的存储体特定wr-autop解码86。

39.图4是图3的wr-autop过程70的时序图。如说明,时序图100包含对应于存储器装置10的时钟的线102。例如,线102可对应于图1的clk_t/clk_c、图3的clkw 72或图2及3的clkg 52。时序图100还包含对应于传入命令的线104。例如,接收到的命令包含在命令接口14处接收到且在命令解码器32中解码的数个位。所说明的命令包含激活命令105a、105b及105c。命令还包含预充电(pre)命令、读取自动预充电(rdap)命令及wr-autop命令106。wr-autop命令106在时间107经锁存。

40.时序图100还包含对应于指示一行存储器单元/存储体将被激活的存储体激活信号的线108。例如,在激活命令之后,存储器存储体12(例如存储器存储体12a)被激活直到对应预充电发生。例如,当激活命令105a被接收时,存储体激活信号保持被断言直到预充电命令。类似地,当激活命令105b被接收时,存储体激活信号保持被断言直到rdap命令被接收。同样地,当激活命令105c被接收时,存储体激活信号被断言。然而,不同于预充电命令及rdap命令,存储器装置10在一时段109内延迟存储体激活信号的取消断言。此延迟对应于wr-autop移位器80中的移位以基于存储器装置10的设置模式寄存器值添加twr数目个时

钟。

41.时序图100还包含对应于tras锁定的激活及取消激活的线110及指示对应激活及/或存储体激活信号之后的激活及预充电的线112。

42.图5说明在没有使用图2中说明的来回传输及在没有产生及重新传输clkg 52的情况下的wr-autop过程130。如说明,wr-autop过程130还可省略利用clkg 52的wr-autop移位器80。如说明,wr-autop过程130在cwl移位器74处接收clkw 72且利用bgba fifo 76,如先前关于图3论述。然而,在wr-autop过程130中,经移位命令78经传输到存储体特定wr-autop解码86,而无需施加额外移位(例如wr-autop移位器80中的twr)。当经弹出bgba 132从cwl移位器74弹出时,存储体特定wr-autop解码86也从bgba fifo 76接收经弹出bgba 132。存储体特定wr-autop解码86将一或多个信号134传输到对应存储体12的存储体处理电路系统136。

43.图6是存储体处理电路系统136的框图。如说明,一或多个信号134包含存储体激活信号、指示一列单元/存储体激活所述单元/存储体的经指示列与行的相交点处的特定单元/存储体的列存储体激活信号及wr-autop(wrap)信号150。wrap信号150指示是否将在具有接收wrap信号150的相应存储体处理电路系统136的相应存储器存储体12中执行wr-autop过程。

44.存储体处理电路系统136包含rasdelay电路系统152。在接收到激活之后,rasdelay电路系统152延迟激活并等待来自存储器阵列中的差分信号的数据。rasdelay电路系统152输出存储器值(nsense)154及wrap信号156。与从rasdelay电路系统152传输的nsense 154及wrap信号156一起,tras锁定电路系统162接收列存储体激活信号158及测试熔丝信号160。例如,wrap信号156可为不具有特定存储体信息的全局信号。代替地,列存储体激活信号158可与wrap信号156进行and运算以识别对应存储器存储体12。测试熔丝信号可用于添加额外延迟(例如1到2ns)及/或利用测试模式除了使用模式寄存器微调/细调设置持续时间之外还微调/细调使用tras锁定电路系统162添加的延迟。

45.tras锁定电路系统162可包含添加一定量的延迟的任何方法。举例来说,tras锁定电路系统162可包含计数器、锁存器、延迟及/或其它电路系统。延迟量可特定于存储器存储体12的实施方案。举例来说,在一些实施例中,存储器装置10可包含提供足够的时间以使存储器装置10能够存取存储器的量(例如36到36ns)。延迟确保预充电命令锁定确保可在执行操作之前存取行/列。然而,tras锁定电路系统162可用于添加除了具有与tras持续时间相同或不同的tras之外的锁定。例如,tras锁定电路系统162可用于/重新用于wr-autop操作的twr锁定。明确来说,tras锁定电路系统162可复位计数、添加将添加的数个循环、添加额外延迟及/或基于wrap信号156的接收起始不同计数器/延迟路径。

46.存储体处理电路系统136还包含prebank电路系统164,其用于从tras锁定电路系统162接收一或多个信号及/或旁通tras锁定电路系统162。例如,prebank电路系统164可包含多路复用器以多路复用来自存储体特定wr-autop解码86的一或多个信号134及来自tras锁定电路系统162的一或多个信号。prebank电路系统164将命令及相关信号传输到经配置以解码存储器存储体12内的特定行的行预解码电路系统166。

47.图7是使用图6的存储体处理电路系统162实施的wr-autop过程的时序图180。如说明,时序图180包含对应于clkw 72的线102。时序图180还包含对应于命令105及106的线

104。另外,时序图180包含分别对应于存储体激活信号、tras锁定及预充电激活的线108、110及112。时序图180还包含对应于列存储体激活信号158的线188。时序图180进一步包含对应于wrap信号156的线190及对应于twr锁定的线194。如说明,在时间198,接收wr-autop命令106,从而致使wrap信号156被断言,如由脉冲191指示。wrap信号156的断言致使twr锁定被断言。

48.如指出,命令105c中的行存储体激活信号的取消断言可在不执行twr移位200的情况下传输。代替地,twr锁定可使用由相应存储体处理电路系统136中的线194指示的twr锁定的断言202断言。在一些实施例中,tras锁定及twr锁定可使用单独信号断言。替代地,单个锁定信号可用于施加仅反映适用于tras或twr锁定的单个锁定指示符tras锁定及twr锁定。图8说明利用单个信号指示tras及twr两者的锁定的时序图220。如说明,时序图220包含线102、104、188、190及110。然而,线110可用于指示用于twr及tras目的的锁定。如指示,当激活命令222被接收时,tras锁定224被断言,如由线110指示。当wr-autop命令225被接收时,对应于列存储体激活信号158的线188开始切换且致使wrap信号156具有被断言的脉冲226。响应于wrap信号156的脉冲226,twr锁定228可被断言,如由线110指示。类似地,当激活命令230被接收时,tras锁定232被断言,如由线110指示。当wr-autop命令234被接收时,列存储体激活信号158开始切换且致使wrap信号156具有被断言的脉冲236。响应于wrap信号156的脉冲236,twr锁定238可被断言,如由线110指示。如说明,twr与tras锁定之间的间隙240、242及244的持续时间可取决于相应激活命令222、230及相应wr-autop命令225、234的断言的位置而有所变化。

49.如上文展示,可在没有图3的wr-autop移位器80的情况下执行图6的wr-autop过程130。换句话说,wr-autop过程130可消除一个时钟限制器电路,借此简化用于实施的电路系统且减小额外时钟(例如clkg 52)的传输。明确来说,用于图3中的经消除时钟的唤醒可消耗更多能量来将clkg 52传输到多个裸片且还可减少用于执行唤醒操作的双向路径通信的量。另外,移除wr-autop移位器80及wr-autop bgba fifo 82可节省存储器装置10中的额外面积。此外,将tras锁定重新用于twr锁定可实现wr-autop过程130的实施而无需在存储体特定wr-autop解码86或存储体处理电路系统136中实施额外及/或过多电路系统。

50.尽管前文论述了各种逻辑低及/或逻辑高断言极性,但在一些实施例中可反转这些极性中的至少一些极性。虽然本公开可具有各种修改及替代形式,但图中已通过实例展示特定实施例且本文中已详细描述特定实施例。然而,应理解,本公开不希望受限于所公开的特定形式。确切来说,本公开希望涵盖落于由以下所附权利要求书界定的本公开的精神及范围内的所有修改、等效物及替代物。

51.参考本文呈现及主张的技术且将其应用于具有实际性质的物质对象及具体实例,其明确改进本技术领域且因而不是抽象、无形或纯理论的。此外,如果本说明书末尾所附的任何权利要求含有表示为“用于[执行][功能]的构件”或“用于[执行][功能]的步骤”的一或多个元件,那么希望此类元件依据35u.s.c.112(f)来解译。然而,对于含有以任何其它方式表示的元件的任何权利要求,希望不依据35u.s.c.112(f)来解译此类元件。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。