1.本公开涉及半导体设计技术,具体地,涉及一种包括管芯上终端电路和校准电路的半导体装置。

背景技术:

2.在半导体装置中,信号的摆动宽度正在减小以使半导体装置之间接口的信号的传输时间最小化。随着信号的摆动宽度减小,外部噪声对半导体装置的影响增加,并且可能由接口中的阻抗不匹配导致的信号反射成为严重问题。如果发生阻抗不匹配,则可能难以高速传输数据,并且从半导体装置的输出端子输出的数据可能失真。因此,由于接收数据的半导体装置接收失真的输出信号,所以可能频繁地发生诸如设置/保持失败、误判等的问题。

3.为了解决这些问题,需要高速操作的半导体装置包括阻抗匹配电路(称为管芯上终端电路),其与焊盘相邻安装在集成电路(ic)芯片内。通常,对于发送机和接收机之间的管芯上终端方案,在发送机中通过输出电路执行源终端,并且在接收机中通过与联接到输入焊盘的输入电路并联联接的终端电路执行并联终端。可通过管芯上终端电路改进信号完整性(si)特性。

4.半导体装置可包括校准电路以用于生成终端控制码以调节管芯上终端电路的电阻或阻抗。校准电路执行用于生成根据工艺、电压和温度(pvt)条件而变化的终端控制码的校准操作。这通常被称为zq校准操作。

5.此外,管芯上终端电路包括多个上拉晶体管和/或下拉晶体管。由于晶体管根据半导体装置的操作而经受各种类型的应力,随着阻抗匹配特性劣化,可能导致信号失真。

技术实现要素:

6.各种示例性实施方式涉及一种能够生成适合于终端电路中由于诸如负偏压温度不稳定性(nbti)的各种应力而劣化的晶体管的终端控制码的校准电路以及包括其的半导体装置。

7.根据实施方式,一种半导体装置包括:终端电路,其联接到第一焊盘并且适合于在通过第一焊盘输入和输出数据的正常操作期间根据第一控制码和第二控制码来提供终端电阻;应力复制电路,其适合于在正常操作期间复制施加到终端电路的应力并且在第二校准模式期间生成检测码;第一校准电路,其适合于在第一校准模式期间调节第一控制码以使联接到第二焊盘的电阻器部分的阻抗与外部电阻器匹配;以及第二校准电路,其适合于在第二校准模式期间通过根据检测码调节第一控制码来生成第二控制码。

8.根据实施方式,一种半导体装置包括:至少一个第一上拉电阻器组,其联接到第一焊盘并且适合于在读操作期间根据第一上拉控制码来提供第一阻抗;至少一个第二上拉电阻器组,其联接到第一焊盘并且适合于在读操作和写操作中的任一个期间根据第二上拉控制码来提供第二阻抗;应力复制电路,其适合于在写操作期间复制施加到第二上拉电阻器组的应力并且在第二校准模式期间生成检测码;以及校准电路,其适合于在第一校准模式

期间调节第一上拉控制码以使联接到第二焊盘的上拉电阻器部分的阻抗与外部电阻器匹配,并且在第二校准模式期间通过根据检测码调节第一上拉控制码来生成第二上拉控制码。

9.根据实施方式,一种半导体系统包括:第一半导体装置;以及第二半导体装置,其适合于通过第一焊盘与第一半导体装置交换数据,其中,第二半导体装置包括:终端电路,其联接到第一焊盘,并且适合于在通过第一焊盘输入和输出数据的正常操作期间根据第一控制码和第二控制码来提供终端电阻;应力复制电路,其适合于在正常操作期间复制施加到终端电路的应力并且在第二校准模式期间生成检测码;第一校准电路,其适合于在第一校准模式期间调节第一控制码以使联接到第二焊盘的电阻器部分的阻抗与外部电阻器匹配;以及第二校准电路,其适合于在第二校准模式期间通过根据检测码调节第一控制码来生成第二控制码。

10.根据实施方式,提出了一种半导体装置的操作方法,该半导体装置包括均联接到第一焊盘的至少一个第一电阻器组和至少一个第二电阻器组,所述操作方法包括以下步骤:在通过第一焊盘输入和输出数据的正常操作期间复制施加到第二电阻器组的应力;在第一校准模式期间调节第一控制码以使联接到第二焊盘的电阻器部分的阻抗与外部电阻器匹配;以及在第二校准模式期间,根据复制的应力来生成检测码并且通过根据检测码调节第一控制码来生成第二控制码。

11.根据实施方式,一种半导体装置包括:第一电路,其包括第一电阻组并且适合于生成第一控制码以用于使第一电阻组具有与外部电阻阻抗匹配的第一电阻,并且在读操作期间向外部提供包括导通电阻的第一电阻;以及第二电路,其包括第二电阻组并且适合于通过根据检测码调节第一控制码来生成第二控制码以用于使第二电阻组具有第二电阻,并且向外部提供在读操作期间包括导通电阻并且在写操作期间包括管芯上终端电阻的第二电阻,其中,第二电阻组包括一个或更多个晶体管,并且其中,检测码表示在读操作和写操作期间对其施加的电应力所导致的晶体管的复制劣化。

12.根据实施方式,校准电路可通过复制和反映终端电路中的晶体管的劣化来生成终端控制码,从而在改进信号完整性(si)特性的同时改进阻抗匹配特性。

附图说明

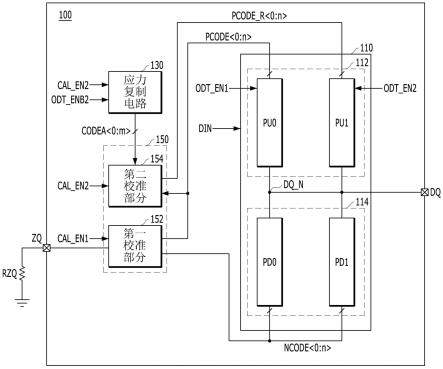

13.图1是示出包括终端电路的半导体装置的配置图。

14.图2a和图2b是示出图1的第二上拉电阻器组和第二下拉电阻器组的详细电路图。

15.图3是用于描述图1的第一上拉电阻器组和第二上拉电阻器组的操作的表。

16.图4是示出根据本发明的实施方式的半导体装置的配置图。

17.图5a和图5b是示出图4的第一上拉电阻器组和第二上拉电阻器组的详细电路图。

18.图6是示出图4的应力复制电路的电路图。

19.图7是示出图4的第一校准电路的电路图。

20.图8是示出图4的第二校准电路的电路图。

21.图9是用于描述根据本发明的实施方式的半导体装置的操作的流程图。

22.图10是示出根据本发明的实施方式的半导体系统的配置图。

具体实施方式

23.下面参照附图描述各种实施方式。然而,实施方式可按不同的形式具体实现,因此不应被解释为限于本文所阐述的实施方式。贯穿本公开,相同的标号贯穿本发明的各种附图和实施方式表示相同的部分。需要注意的是,对“实施方式”、“另一实施方式”等的引用未必仅意指一个实施方式,对任何这样的短语的不同引用未必是指相同的实施方式。术语“实施方式”在本文中使用时未必指所有实施方式。

24.将理解,尽管本文可使用术语“第一”、“第二”、“第三”等来标识各种元件,但是这些元件不受这些术语限制。这些术语用于将一个元件与原本具有相同或相似名称的另一元件相区分。因此,一个实例中的第一元件在另一实例中也可被称为第二或第三元件,而不指示元件本身的任何改变。

25.将进一步理解,当元件被称为“连接到”或“联接到”另一元件时,其可直接在另一元件上、连接到或联接到另一元件,或者可存在一个或更多个中间元件。另外,还将理解,当元件被称为在两个元件“之间”时,其可以是这两个元件之间的仅有元件,或者也可存在一个或更多个中间元件。除非上下文另外指出或指示,否则两个元件(无论直接还是间接连接/联接)之间的通信可以是有线的或无线的。

26.如本文所使用的,除非上下文另外清楚地指示,否则单数形式也可包括复数形式,反之亦然。

27.将进一步理解,当在本说明书中使用时,术语“包括”和“包含”指定存在所述元件并且不排除一个或更多个其它元件的存在或添加。如本文所使用的,术语“和/或”包括一个或更多个相关所列项的任何和所有组合。

28.图1是示出包括终端电路20和40的半导体装置10的配置图。图2a和图2b是示出图1的第二上拉电阻器组pu1和第二下拉电阻器组pd1的详细电路图。图3是用于描述图1的第一上拉电阻器组pu0和第二上拉电阻器组pu1的操作的表。

29.参照图1,半导体装置10可包括用于接收/输出数据的数据焊盘dq、输入缓冲器12和输出驱动器14。

30.输入缓冲器12可在写操作期间通过缓冲通过数据焊盘dq输入的数据来向内部电路(未示出)提供内部数据din。尽管未示出,输入缓冲器12可根据写命令来操作。

31.输出驱动器14可在读操作期间通过驱动从内部电路提供的内部数据din来向数据焊盘dq输出数据。输出驱动器14可包括终端电路20和40以用于在读操作或写操作期间向数据焊盘dq提供上拉阻抗和/或下拉阻抗。尽管图1示出一个数据焊盘dq,但本发明不限于此。根据实施方式,多个数据焊盘以及与这些数据焊盘对应的多个终端电路可设置在半导体装置10中。

32.终端电路20和40可包括通过输出节点dq_n联接到数据焊盘dq的上拉终端电路20和下拉终端电路40。在读操作或写操作期间,半导体装置10与外部装置(未示出)之间的阻抗匹配可通过由从上拉终端电路20提供的上拉阻抗和从下拉终端电路40提供的下拉阻抗确定的终端电阻来实现。

33.上拉终端电路20可包括多个上拉电阻器组(例如,第一上拉电阻器组pu0和第二上拉电阻器组pu1),各个上拉电阻器组包括并联联接的多个电阻器。第一上拉电阻器组pu0和第二上拉电阻器组pu1可根据内部数据din以及第一终端使能信号odt_enb1和第二终端使

能信号odt_enb2中的对应一个而启用,并且根据上拉控制码pcode《0:n》被修整以具有特定目标电阻值(例如,240欧姆)。

34.第一上拉电阻器组pu0和第二上拉电阻器组pu1可具有基本上相同的配置。例如,参照图2a,第二上拉电阻器组pu1可包括上拉控制逻辑21和多个单元电阻器22。

35.上拉控制逻辑21可根据内部数据din和第二终端使能信号odt_enb2来生成上拉选择信号p_sel。上拉控制逻辑21可包括反相器inv11和逻辑与门ad11。反相器inv11可将内部数据din的逻辑电平反相,并且逻辑与门ad11可对反相器inv11的输出和第二终端使能信号odt_enb2执行逻辑与运算。因此,当第二终端使能信号odt_enb2被禁用为逻辑高电平时,上拉控制逻辑21可通过将内部数据din的逻辑电平反相来输出上拉选择信号p_sel。当第二终端使能信号odt_enb2被使能为逻辑低电平时,上拉控制逻辑21可输出逻辑低电平的上拉选择信号p_sel,而不管内部数据din的逻辑电平如何。

36.多个单元电阻器22可并联联接在源极电压(vdd)端子与输出节点dq_n之间,并且响应于上拉选择信号p_sel而导通以接收上拉控制码pcode《0:n》的各个比特。单元电阻器22可与上拉控制码pcode《0:n》的比特数(n 1)对应。各个单元电阻器22可包括串联联接在源极电压(vdd)端子与输出节点dq_n之间的第一上拉晶体管p11、第二上拉晶体管p12和电阻器元件r11。第一上拉晶体管p11可利用p型金属氧化物半导体(pmos)晶体管来实现,并且根据上拉控制码pcode《0:n》当中的对应比特而导通。第二上拉晶体管p12可利用pmos晶体管来实现,并且根据上拉选择信号p_sel而导通。利用上述配置,当第二终端使能信号odt_enb2被禁用为逻辑高电平并且内部数据din具有逻辑高电平时,第二上拉电阻器组pu1可根据上拉控制码pcode《0:n》而被修整为具有特定目标电阻值(例如,240欧姆)。

37.返回参照图1,下拉终端电路40可包括多个下拉电阻器组(例如,第一下拉电阻器组pd0和第二下拉电阻器组pd1),各个下拉电阻器组包括并联联接的多个电阻器。第一下拉电阻器组pd0和第二下拉电阻器组pd1可根据内部数据din而启用,并且根据下拉控制码ncode《0:n》被修整为具有特定目标电阻值(例如,240欧姆)。

38.第一下拉电阻器组pd0和第二下拉电阻器组pd1可具有基本上相同的配置。例如,参照图2b,第二下拉电阻器组pd1可包括下拉控制逻辑41和多个单元电阻器42。

39.下拉控制逻辑41可根据内部数据din来生成下拉选择信号n_sel。下拉控制逻辑41可利用将内部数据din的逻辑电平反相以输出下拉选择信号n_sel的反相器来实现。

40.多个单元电阻器42可并联联接在输出节点dq_n与接地电压(vss)端子之间,并且响应于下拉选择信号n_sel而导通以接收下拉控制码ncode《0:n》的各个比特。单元电阻器42可与下拉控制码ncode《0:n》的比特数(n 1)对应。各个单元电阻器42可包括串联联接在接地电压(vss)端子与输出节点dq_n之间的第一下拉晶体管n11、第二下拉晶体管n12和电阻器元件r12。第一下拉晶体管n11可利用n型金属氧化物半导体(nmos)晶体管来实现,并且根据下拉控制码ncode《0:n》当中的对应比特而导通。第二下拉晶体管n12可利用nmos晶体管来实现,并且根据下拉选择信号n_sel而导通。利用上述配置,当内部数据din具有逻辑低电平时,第二下拉电阻器组pd1可根据下拉控制码ncode《0:n》被修整为具有特定目标电阻值(例如,240欧姆)。

41.此外,终端电路20和40可向数据焊盘dq提供由上拉阻抗和/或下拉阻抗确定的终端电阻。此时,终端电路20和40可根据写操作或读操作提供不同值的终端电阻。例如,如图3

所示,在读操作期间,第一终端使能信号odt_enb1和第二终端使能信号odt_enb2可被禁用为逻辑高电平。根据内部数据din的逻辑电平,终端电路20和40可向输出驱动器14提供终端电阻作为导通电阻ron,终端电阻由从第一上拉电阻器组pu0和第二上拉电阻器组pu1提供的上拉阻抗以及从第一下拉电阻器组pd0和第二下拉电阻器组pd1提供的下拉阻抗确定。此外,如图3所示,在写操作期间,第一终端使能信号odt_enb1可被禁用为逻辑高电平,但是第二终端使能信号odt_enb2可被使能为逻辑低电平。终端电路20和40可向数据焊盘dq提供终端电阻作为管芯上终端电阻rtt,终端电阻由从第二上拉电阻器组pu1提供的上拉阻抗确定。

42.当高电场被施加到pmos晶体管的栅极时,随着时间推移,半导体装置中所使用的负偏压根据温度的改变而变得不稳定。这被称为负偏压温度不稳定性(nbti)应力。当发生nbti应力时,pmos晶体管的阈值电压vth增大,并且半导体存储器装置的性能可能劣化。由于在读操作或写操作期间包括在第二上拉电阻器组pu1中的pmos晶体管(具体地,第二上拉晶体管p12)维持导通状态,所以第二上拉晶体管p12可能由于nbti应力而劣化。此外,与导通状态相比,终端电路20和40可能提供管芯上终端电阻rtt相对更长的时间,从而进一步加速第二上拉电阻器组pu1中的pmos晶体管的劣化。结果,第二上拉电阻器组pu1中的pmos晶体管的阈值电压vth可远大于第一上拉电阻器组pu0中的pmos晶体管的阈值电压,因此,在读操作期间导通电阻ron可增大,导致信号完整性(si)的劣化。因此,第二上拉电阻器组pu1提供准确的上拉阻抗变得困难。

43.以下,将描述根据本发明的实施方式的通过复制由于nbti应力而劣化的pmos晶体管的特性并反映复制的特性以生成上拉控制码来提供准确的阻抗的方法。

44.图4是示出根据本发明的实施方式的半导体装置100的配置图。图5a和图5b是示出图4的第一上拉电阻器组pu0和第二上拉电阻器组pu1的详细电路图。

45.参照图4,半导体装置100可包括第一焊盘dq、第二焊盘zq、终端电路110、应力复制电路130和校准电路150。第一焊盘dq是用于接收/输出数据的数据输入/输出焊盘,第二焊盘zq可包括联接到外部电阻器rzq的校准焊盘。以下,通过第一焊盘dq输入和输出数据的读操作或写操作可被定义为正常操作,通过第二焊盘zq来生成并调节根据工艺、电压和温度(pvt)条件而变化的终端控制码的操作可被定义为校准操作。在此实施方式中,终端控制码可包括第一上拉控制码pcode《0:n》、第二上拉控制码pcode_r《0:n》和下拉控制码ncode《0:n》。

46.终端电路110可联接到第一焊盘dq,并且在通过第一焊盘dq输入和输出数据的正常操作期间根据第一上拉控制码pcode《0:n》、第二上拉控制码pcode_r《0:n》和下拉控制码ncode《0:n》提供终端电阻。终端电路110可包括通过输出节点dq_n联接到第一焊盘dq的上拉终端电路112和下拉终端电路114。在读操作或写操作期间,半导体装置100与外部装置(未示出)之间的阻抗匹配可通过由从上拉终端电路112提供的上拉阻抗和从下拉终端电路114提供的下拉阻抗确定的终端电阻来实现。

47.上拉终端电路112可包括多个上拉电阻器组(例如,第一上拉电阻器组pu0和第二上拉电阻器组pu1),各个上拉电阻器组包括并联联接的多个电阻器。第一上拉电阻器组pu0可联接到第一焊盘dq,并且根据第一终端使能信号odt_enb1和内部数据din而启用以提供根据第一上拉控制码pcode《0:n》调节的第一上拉阻抗。第二上拉电阻器组pu1可联接到第

一焊盘dq,并且根据第二终端使能信号odt_enb2和内部数据din而启用以提供根据第二上拉控制码pcode_r《0:n》调节的第二上拉阻抗。

48.下拉终端电路114可包括多个下拉电阻器组(例如,第一下拉电阻器组pd0和第二下拉电阻器组pd1),各个下拉电阻器组包括并联联接的多个电阻器。第一下拉电阻器组pd0可联接到第一焊盘dq,并且根据内部数据din而启用以提供根据下拉控制码ncode《0:n》调节的第一下拉阻抗。第二下拉电阻器组pd1可联接到第一焊盘dq,并且根据内部数据din而启用以提供根据下拉控制码ncode《0:n》调节的第二下拉阻抗。

49.在读操作期间,第一终端使能信号odt_enb1和第二终端使能信号odt_enb2可被禁用为逻辑高电平,以使得第一上拉/下拉阻抗和第二上拉/下拉阻抗可形成对输出驱动器的导通电阻ron。在写操作期间,第二终端使能信号odt_enb2可被使能为逻辑低电平,以使得第二上拉阻抗可形成对第一焊盘dq的管芯上终端电阻rtt。

50.第一上拉电阻器组pu0和第二上拉电阻器组pu1可具有与图2a的第二上拉电阻器组pu1基本上相同的配置,并且第一下拉电阻器组pd0和第二下拉电阻器组pd1可具有与图2b的第二下拉电阻器组pd1基本上相同的配置。然而,与图1的第一上拉电阻器组pu0和第二上拉电阻器组pu1不同,根据实施方式的第一上拉电阻器组pu0和第二上拉电阻器组pu1可分别接收彼此不同的上拉控制码。

51.详细地,参照图5a,第一上拉电阻器组pu0可包括上拉控制逻辑121和多个单元电阻器122。由于除了上拉控制逻辑121接收第一终端使能信号odt_enb1而非第二终端使能信号odt_enb2之外,上拉控制逻辑121和单元电阻器122可具有与图2a的上拉控制逻辑21和单元电阻器22基本上相同的配置,所以将省略详细说明。当第一终端使能信号odt_enb1被禁用为逻辑高电平并且内部数据din具有逻辑高电平时,第一上拉电阻器组pu0可根据第一上拉控制码pcode《0:n》被修整为具有特定目标电阻值(例如,240欧姆)。如图3所示,由于在读操作或写操作期间第一终端使能信号odt_enb1被禁用为逻辑高电平,所以第一上拉电阻器组pu0可根据第一上拉控制码pcode《0:n》和内部数据din来提供目标电阻值。

52.参照图5b,第二上拉电阻器组pu1可包括上拉控制逻辑124和多个单元电阻器125。同样,由于上拉控制逻辑124和单元电阻器125可具有与图2a的上拉控制逻辑21和单元电阻器22基本上相同的配置,所以将省略详细说明。当第二终端使能信号odt_enb2被禁用为逻辑高电平并且内部数据din具有逻辑高电平时,第二上拉电阻器组pu1可根据第二上拉控制码pcode_r《0:n》被修整为具有特定目标电阻值(例如,240欧姆)。如图3所示,由于在读操作期间第二终端使能信号odt_enb2被禁用为逻辑高电平,所以第二上拉电阻器组pu1可根据第二上拉控制码pcode_r《0:n》和内部数据din来提供目标电阻值。相反,由于在写操作期间第二终端使能信号odt_enb2被使能为逻辑低电平,所以第二上拉电阻器组pu1可根据第二上拉控制码pcode_r《0:n》提供目标电阻值,而不管内部数据din的逻辑电平如何。此时,由于包括在第二上拉电阻器组pu1中的pmos晶体管在读操作或写操作期间维持导通状态,所以pmos晶体管可能由于nbti应力而劣化,从而增大导通电阻ron。根据实施方式,可通过向设置有劣化的pmos晶体管的第二上拉电阻器组pu1施加与第一上拉控制码pcode《0:n》不同的第二上拉控制码pcode_r《0:n》来补偿导通电阻ron。

53.此外,尽管图4示出上拉终端电路112和下拉终端电路114中的每一个具有两个电阻器组,但本发明不限于此。至少两个电阻器组可设置在上拉终端电路112和下拉终端电路

114中的每一个中。此时,随着各个终端使能信号被使能,上拉终端电路112和下拉终端电路114可提供依次减小至例如240ω、120ω、80ω、60ω、48ω、40ω的上拉阻抗和下拉阻抗。

54.应力复制电路130可在正常操作期间复制施加到终端电路110的应力,并且在第二校准模式期间生成检测码codea《0:m》(将稍后描述)。应力复制电路130可包括串联联接在源极电压(vdd)端子与接地电压(vss)端子之间的上拉复制晶体管(图6的rp11)和下拉复制晶体管(图6的rn11)。在正常操作期间,应力复制电路130可根据第二终端使能信号odt_enb2向上拉复制晶体管rp11施加应力(即,施加表示高电场的栅极电压以复制nbti应力效果)。例如,随着在写操作期间第二终端使能信号odt_enb2被使能为逻辑低电平,应力复制电路130可通过使上拉复制晶体管rp11导通来向上拉复制晶体管rp11施加应力。此外,应力复制电路130可根据在第二校准模式期间启用的第二模式信号cal_en2来生成表示通过使上拉复制晶体管rp11和下拉复制晶体管rn11导通而形成的复制阻抗的检测码codea《0:m》。即,应力复制电路130(通过向上拉复制晶体管rp11施加表示高电场的栅极电压)可在正常操作期间通过向上拉复制晶体管rp11施加nbti应力来复制由于nbti应力而劣化的pmos晶体管的特性,该nbti应力与施加到上拉终端电路112的nbti应力基本上相同。此外,在校准操作期间,应力复制电路130可基于复制的特性来提供检测码codea《0:m》。

55.作为参考,在本发明的实施方式中,校准操作可被分类为设定第一上拉控制码pcode《0:n》的第一校准模式和设定第二上拉控制码pcode_r《0:n》的第二校准模式。由于第一校准模式不同于第二校准模式,所以对于校准操作的第一校准模式可将第一模式信号cal_en1使能,而对于校准操作的第二校准模式可将第二模式信号cal_en2使能。即,第一模式信号cal_en1的启用区段可不与第二模式信号cal_en2的启用区段交叠。根据实施方式,校准操作可被分类为两种以上的校准模式。以下,作为示例将说明在校准操作期间第一模式信号cal_en1和第二模式信号cal_en2被依次使能为逻辑高电平的情况。

56.校准电路150可包括上拉电阻器部分(图7的210)和下拉电阻器部分(图7的230)中的至少一个。在第一校准模式期间,校准电路150可调节第一上拉控制码pcode《0:n》和下拉控制码ncode《0:n》以使联接到第二焊盘zq的电阻器部分的阻抗与联接到第二焊盘zq的外部电阻器rzq匹配。此外,在第二校准模式期间,校准电路150可通过根据检测码codea《0:m》调节第一上拉控制码pcode《0:n》来生成第二上拉控制码pcode_r《0:n》。详细地,校准电路150可包括第一校准电路152和第二校准电路154。

57.第一校准电路152可根据第一模式信号cal_en1而启用。在第一校准模式期间,第一校准电路152可调节第一上拉控制码pcode《0:n》以使联接到第二焊盘zq的上拉电阻器部分210的阻抗与外部电阻器rzq匹配,并且调节下拉控制码ncode《0:n》以使下拉电阻器部分230的阻抗与外部电阻器rzq匹配。

58.第二校准电路154可根据第二模式信号cal_en2而启用。在第二校准模式期间,第二校准电路154可通过根据检测码codea《0:m》调节由第一校准电路152生成的第一上拉控制码pcode《0:n》来生成第二上拉控制码pcode_r《0:n》。由第一校准电路152生成的第一上拉控制码pcode《0:n》可以是已在第一校准模式下调节的码。

59.如上所述,根据实施方式的半导体装置100可通过在读操作或写操作期间复制和反映由于始终导通状态而劣化的第二上拉电阻器组pu1中的pmos晶体管的特性来生成第二上拉控制码pcode_r《0:n》。此外,半导体装置100可向第一上拉电阻器组pu0施加第一上拉

控制码pcode《0:n》,同时向包括劣化的pmos晶体管的第二上拉电阻器组pu1施加不同于第一上拉控制码pcode《0:n》的第二上拉控制码pcode_r《0:n》,从而补偿导通电阻ron。因此,可在改进信号完整性(si)特性的同时改进阻抗匹配特性。

60.图6是示出图4的应力复制电路130的电路图。

61.参照图6,应力复制电路130可包括上拉复制晶体管rp11、下拉复制晶体管rn11、复制控制电路132和模数转换器(adc)134。

62.上拉复制晶体管rp11和下拉复制晶体管rn11可串联联接在源极电压(vdd)端子和接地电压(vss)端子之间,并且分别通过其栅极接收第一复制控制信号pu_zqa和第二复制控制信号pd_zqa。上拉复制晶体管rp11可利用pmos晶体管来实现。第一复制控制信号pu_zqa可被使能为逻辑低电平以用于启用pmos晶体管。下拉复制晶体管rn11可利用nmos晶体管来实现。第二复制控制信号pd_zqa可被使能为逻辑高电平以用于启用nmos晶体管。

63.复制控制电路132可在正常操作期间将第一复制控制信号pu_zqa使能,并且在第二校准模式期间将第一复制控制信号pu_zqa和第二复制控制信号pd_zqa二者使能。例如,复制控制电路132可包括反相器inv21和逻辑与门ad21。反相器inv21可将第二模式信号cal_en2反相,并且逻辑与门ad21可对反相器inv21的输出和第二终端使能信号odt_enb2执行逻辑与运算,从而输出第一复制控制信号pu_zqa。复制控制电路132可输出第二模式信号cal_en2作为第二复制控制信号pd_zqa。根据实施方式,复制控制电路132可缓冲第二模式信号cal_en2以输出第二复制控制信号pd_zqa。因此,当第二终端使能信号odt_enb2被使能为逻辑低电平时,复制控制电路132可仅将第一复制控制信号pu_zqa使能。当第二模式信号cal_en2被使能为逻辑高电平时,复制控制电路132可将第一复制控制信号pu_zqa和第二复制控制信号pd_zqa二者使能。

64.adc 134可根据第二模式信号cal_en2而被启用,并且转换上拉复制晶体管rp11与下拉复制晶体管rn11之间的公共节点c_n处的信号tga以输出检测码codea《0:m》。即,adc 134可将模拟类型的信号tga转换为数字类型的检测码codea《0:m》。

65.如上所述,在正常操作期间,应力复制电路130可通过向上拉复制晶体管rp11施加应力来复制上拉复制晶体管rp11的特性。此时,为了复制第二上拉电阻器组pu1中劣化的pmos晶体管的特性,应力复制电路130可根据第二终端使能信号odt_enb2向上拉复制晶体管rp11施加应力。随着劣化程度增加,导通电阻ron增加,这降低了公共节点c_n上的信号tga的电压电平。因此,可确定并最终输出检测码codea《0:m》的值。

66.图7是示出图4的第一校准电路152的电路图。

67.参照图7,第一校准电路152可包括上拉电阻器部分210、虚设电阻器部分220、下拉电阻器部分230、第一比较器242、第二比较器252、第一计数器244、第二计数器254和基准电压发生器260。第一计数器244和第二计数器254可根据第一模式信号cal_en1而被使能。

68.第一比较器242可将第二焊盘zq的电压与从基准电压发生器260生成的基准电压vref进行比较,以根据比较结果生成第一上/下信号up/dn1。第二焊盘zq的电压可由外部电阻器rzq和上拉电阻器部分210的分压比确定。第一计数器244可响应于第一上/下信号up/dn1而增大或减小第一上拉控制码pcode《0:n》的值。上拉电阻器部分210可包括并联联接的多个上拉电阻器,这些上拉电阻器根据第一上拉控制码pcode《0:n》而导通或截止。

69.上拉电阻器部分210可联接到第二焊盘zq,并且通过根据第一上拉控制码pcode《

0:n》使上拉电阻器导通或截止来调节其阻抗。上拉电阻器部分210的调节的阻抗可再次影响第二焊盘zq的电压,并且上述操作可重复。结果,直至联接到第二焊盘zq的上拉电阻器部分210的阻抗与外部电阻器rzq匹配,可重复校准操作。这种校准操作可被定义为上拉校准操作。

70.上拉电阻器部分210可被设计为与驱动第一焊盘dq的上拉终端电路(图4的112)类似,其趋于相同或相似。虚设电阻器部分220可具有与上拉电阻器部分210基本上相同的配置。下拉电阻器部分230可包括并联联接的多个下拉电阻器,这些下拉电阻器根据下拉控制码ncode《0:n》而导通或截止。下拉电阻器部分230可被设计为与下拉终端电路类似,其趋于相同或相似。

71.通过上拉校准操作生成的上拉控制码pcode《0:n》可被提供给虚设电阻器部分220以确定虚设电阻器部分220的阻抗。第二比较器252可将虚设电阻器部分220和下拉电阻器部分230的公共节点nb处的电压与基准电压vref进行比较,以根据比较结果生成第二上/下信号up/dn2。第二计数器254可响应于第二上/下信号up/dn2而增大或减小下拉控制码ncode《0:n》的值。下拉电阻器部分230可包括并联联接的多个下拉电阻器,这些下拉电阻器根据下拉控制码ncode《0:n》而导通或截止。与上拉校准操作类似,直至公共节点nb处的电压与基准电压vref相同,可重复校准操作。这种校准操作可被定义为下拉校准操作。因此,作为包括上拉校准操作和下拉校准操作的zq校准操作的结果,可生成上拉控制码pcode《0:n》和下拉控制码ncode《0:n》,并且将它们提供给终端电路(图4的110)以控制其阻抗。

72.图8是示出图4的第二校准电路154的电路图。

73.参照图8,第二校准电路154可包括劣化确定部分310和码调节部分320。

74.劣化确定部分310可根据第二模式信号cal_en2而被使能。在第二校准模式期间,劣化确定部分310可根据检测码codea《0:m》来生成表示配置第二上拉电阻器组pu1并且其劣化特性由上拉复制晶体管rp11复制的pmos晶体管的劣化程度的调节码inc《0:k》。例如,劣化确定部分310可计算检测码codea《0:m》与配置第二上拉电阻器组pu1的pmos晶体管处于理想条件而没有劣化时可能出现的基准码之间的差,并且生成与所计算的差对应的调节码inc《0:k》。根据实施方式,劣化确定部分310可利用减法器来实现。例如,当基准码由“1111”组成并且可输入“1001”的检测码codea《0:m》时,劣化确定部分310可通过从“1111”减去“1001”来生成“110”的调节码inc《0:k》。

75.码调节部分320可将调节码inc《0:k》反映到第一上拉控制码pcode《0:n》上以生成第二上拉控制码pcode_r《0:n》。根据实施方式,码调节部分320可利用加法器来实现。

76.利用上述配置,在第二校准模式期间,第二校准电路154可通过根据检测码codea《0:m》调节从第一校准电路152生成的第一上拉控制码pcode《0:n》来生成第二上拉控制码pcode_r《0:n》。第二上拉控制码pcode_r《0:n》可被生成为与第一上拉控制码pcode《0:n》相比更多地增加pmos晶体管的驱动性,从而补偿第二上拉电阻器组pu1中的劣化的pmos晶体管的导通电阻ron。

77.以下,参照图4至图9,将说明根据本发明的实施方式的半导体装置的操作。

78.图9是用于描述根据本发明的实施方式的半导体装置的操作的流程图。

79.参照图10,半导体装置100可执行通过第一焊盘dq输入和输出数据的读操作或写操作。此时,联接到第一焊盘dq的第一上拉电阻器组pu0根据第一终端使能信号odt_enb1和

内部数据din而被启用,以提供根据第一上拉控制码pcode《0:n》调节的第一上拉阻抗。联接到第一焊盘dq的第二上拉电阻器组pu1根据第二终端使能信号odt_enb2和内部数据din而被启用,以提供根据第二上拉控制码pcode_r《0:n》调节的第二上拉阻抗。

80.在读操作期间,第一终端使能信号odt_enb1和第二终端使能信号odt_enb2被禁用为逻辑高电平。终端电路110提供终端电阻作为第一焊盘dq的导通电阻ron,该终端电阻由从第一上拉电阻器组pu0和第二上拉电阻器组pu1提供的上拉阻抗以及从第一下拉电阻器组pd0和第二下拉电阻器组pd1提供的下拉阻抗确定。相反,在写操作期间,第一终端使能信号odt_enb1维持逻辑高电平,但是第二终端使能信号odt_enb2被使能为逻辑低电平。终端电路110提供终端电阻作为对第一焊盘dq的管芯上终端电阻rtt,该终端电阻由从第二上拉电阻器组pu1提供的上拉阻抗确定。

81.根据实施方式,应力复制电路130在诸如读操作和写操作的正常操作期间复制施加到终端电路110的应力,并且在校准操作期间生成检测码codea《0:m》(在s910)。应力复制电路130可在写操作期间通过根据第二终端使能信号odt_enb2向上拉复制晶体管rp11施加应力来将由于nbti应力而劣化的pmos晶体管的特性复制到上拉复制晶体管rp11上。

82.此后,半导体装置100进入校准操作的第一校准模式。第一校准电路152可调节第一上拉控制码pcode《0:n》以使上拉电阻器部分210的阻抗与联接到第二焊盘zq的外部电阻器rzq匹配,并且调节下拉控制码ncode《0:n》以使下拉电阻器部分230的阻抗与外部电阻器rzq匹配(在s920)。

83.此后,半导体装置100进入校准操作的第二校准模式(在s930)。应力复制电路130可生成表示通过使上拉复制晶体管rp11和下拉复制晶体管rn11导通而形成的复制阻抗的检测码codea《0:m》(在s932)。第二校准电路154可通过根据检测码codea《0:m》调节第一上拉控制码pcode《0:n》来生成第二上拉控制码pcode_r《0:n》(在s934)。

84.图10是示出根据本发明的实施方式的半导体系统400的配置图。

85.参照图10,半导体系统400可包括第一半导体装置410和第二半导体装置420。第一半导体装置410和第二半导体装置420可以是彼此通信的电子组件。第一半导体装置410可以是主装置,第二半导体装置420可以是由第一半导体装置410控制的从装置。例如,第一半导体装置410可以是诸如处理器或控制器的主机装置,并且可包括例如中央处理单元(cpu)、图形处理单元(gpu)、多媒体处理器(mmp)、数字信号处理器(dsp)和存储控制器中的一个或更多个。此外,第一半导体装置410可通过将具有各种功能的各种处理器芯片(例如,应用处理器(ap))集成到单个芯片中来以系统芯片的形式实现。第二半导体装置420可以是存储器装置,并且存储器装置可包括易失性存储器和非易失性存储器。易失性存储器可包括例如静态ram(sram)、动态ram(dram)或同步dram(sdram),非易失性存储器可包括只读存储器(rom)、可编程rom(prom)、电可擦除可编程rom(eeprom)、电可编程rom(eprom)、闪存、相变ram(pram)、磁性ram(mram)、电阻ram(rram)或铁电ram(fram)。

86.第一半导体装置410和第二半导体装置420可通过信号传输线430彼此联接。第一半导体装置410可包括数据焊盘dq,并且数据焊盘dq可联接到信号传输线430。第二半导体装置420可包括数据焊盘dq,并且数据焊盘dq可联接到信号传输线130。信号传输线430可以是通道、链路或总线。尽管信号传输线430被示出为传输数据的传输线,但是要注意,实施方式不限于此,信号传输线430可传输时钟信号、命令信号或地址信号。第一半导体装置410可

包括发送装置(tx)412和接收装置(rx)413。发送装置(tx)412可生成输出信号并通过信号传输线430将输出信号发送到第二半导体装置420。接收装置(rx)413可通过信号传输线430接收从第二半导体装置420发送的信号。类似地,第二半导体装置420可包括发送装置(tx)422和接收装置(rx)423。发送装置(tx)422可生成输出信号并通过信号传输线430将输出信号发送到第一半导体装置410。接收装置(rx)423可通过信号传输线430接收从第一半导体装置410发送的信号。

87.第一半导体装置410的发送装置(tx)412可对应于图1的终端电路20和40。第一半导体装置410还可包括校准电路414。校准电路414可通过校准焊盘zq联接到外部电阻器rzq。校准电路414可通过执行校准操作来生成终端控制码,并且将终端控制码提供给发送装置(tx)412的终端电路,从而设定发送装置(tx)412的电阻值。例如,根据校准操作的结果,发送装置(tx)412的电阻值被设定为60欧姆、120欧姆或240欧姆。

88.根据实施方式,第二半导体装置420的发送装置(tx)422可包括图4的终端电路110。第二半导体装置420还可包括校准电路424和应力复制电路426。应力复制电路426可在正常操作期间复制施加到终端电路的应力,并且在第二校准模式期间生成检测码codea《0:m》。在校准操作的第一校准模式期间,校准电路424可调节第一上拉控制码pcode《0:n》以使上拉电阻器部分的阻抗与外部电阻器rzq匹配。在校准操作的第一校准模式期间,校准电路424可调节下拉控制码ncode《0:n》以使下拉电阻器部分的阻抗与外部电阻器rzq匹配。此外,在校准操作的第二校准模式期间,校准电路424可通过根据检测码codea《0:m》调节第一上拉控制码pcode《0:n》来生成第二上拉控制码pcode_r《0:n》。包括第一上拉控制码pcode《0:n》、第二上拉控制码pcode_r《0:n》和下拉控制码ncode《0:n》的终端控制码可被提供给发送装置(tx)422的终端电路,从而设定发送装置(tx)422的电阻值。例如,根据校准操作的结果,发送装置(tx)422的电阻值被设定为60欧姆、120欧姆或240欧姆。

89.此外,尽管图10仅示出第二半导体装置420包括应力复制电路426,但本发明不限于此。根据实施方式,应力复制电路426可被包括在第一半导体装置410和第二半导体装置420二者中。

90.如上所述,根据本发明的实施方式,半导体装置可通过复制和反映终端电路中的晶体管的劣化来生成终端控制码,从而在改进信号完整性(si)特性的同时改进阻抗匹配特性。

91.此外,尽管实施方式说明了当pmos晶体管由于nbti应力而劣化时可使用复制上拉终端电路112中的pmos晶体管的劣化的特性的应力复制电路130来补偿导通电阻ron,但本发明不限于此。根据实施方式,当下拉终端电路114中的nmos晶体管由于正偏压温度不稳定性(pbti)应力而劣化时,可使用复制下拉终端电路114中的nmos晶体管的劣化的特性的应力复制电路来补偿导通电阻ron。

92.应该注意,尽管结合其优选实施方式描述了本公开的技术精神,但这仅是为了描述,不应被解释为限制。本领域普通技术人员应该理解,在不脱离本公开的技术精神的情况下,可对其进行各种改变。

93.例如,对于在上述实施方式中作为示例提供的逻辑门和晶体管,可根据输入信号的极性实现不同的位置和类型。

94.相关申请的交叉引用

95.本技术要求2020年12月14日提交的韩国专利申请no.10-2020-0174211的优先权,其整体通过引用并入本文。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。