具有pfc和有线总线接口的led驱动器

技术领域

1.本发明涉及一种led驱动器。本发明还涉及一种用于降低led驱动器上的波动的方法。

背景技术:

2.在用于发光装置的许多操作器件中,以高频率操作发光装置特别是就气体放电灯而言或者借助于脉冲调制操作发光装置例如就led而言是常规的。为此,提供了所谓的驱动电路,该驱动电路可以呈脉冲调制器、全桥电路或半桥电路的形式等。通常,将dc链路电压供应到这些驱动电路,该dc链路电压可以在适当时具有叠加在其上的所谓的纹波。

3.为了提供该dc链路电压,通常使用所谓的pfc(功率因数校正)电路,也称为有源功率因数校正电路。该pfc电路基于大体上整流的市电电压生成dc链路电压,同时保持尽可能高的功率因数。

4.此外,所谓的数字可寻址照明接口(dali)提供建筑物中的照明装置(“灯具”)、镇流器和控制器之间的双向通信。它在iec技术标准iec 62386和iec 60929中定义,这些iec技术标准以最高至1000v的电压以及50hz或60hz的操作频率覆盖在ac电源中使用的led驱动器和电子镇流器。

5.dali使用曼彻斯特编码的0至20v信令,该信令使得控制器能够在网络中寻址单个灯或将命令广播到区中的多组灯。

6.从灯回到控制器的通信也是可能的,以用于报告参数诸如能量消耗和器件故障。

7.dali系统布线要求类似于在商业和工业设施中部署的常规单向0至10v控制电路。然而,利用dali,led驱动器和镇流器可以链接到中央计算机,从而允许各自独立控制。

8.可以连接led驱动器和镇流器以构成一组led驱动器或镇流器。每个器件被分配地址,并且该组连接到dali控制器。dali不需要任何硬连线电源电路对照组,但允许自由形式网络布局:菊花链、星形拓扑和多站通讯网络全部允许。也允许两个或更多个拓扑结构的组合。

9.图1和图2中的图示出了典型的dali帧看起来的样子。

10.具体地,前向帧是由控制器发送到照明/镇流器器件的分组。这些前向帧由一个起始位、八个地址位、八个数据位和两个停止位组成。这些位是首先发送的最高有效位(msb)。

11.后向帧是由控制装置发送回到控制器的响应分组。该后向帧由一个起始位、八个数据位和两个停止位组成。

12.本发明通常在用于照明装置的驱动器的领域中,该照明装置诸如例如led,该驱动器具有集成dali电源。如在现有技术中已知的,dali供电电压可以在pfc电路之后被分接,并且因此在将dc总线电压供应到后面的转换器级诸如例如llc之前被分接。

13.然而,在dali总线活动(dali总线上的下降沿和上升沿)期间,在dc总线级处的这种分接将引起总线电压的波动和/或骤降,这可能导致这些波动在由后面的转换器级供应的照明装置的光输出中实际上可见的问题。

14.目前,一旦调光级低于某个级别,pfc控制器就切换到快速操作,该快速操作降低在v

bus

上的dali帧干扰,但使总谐波失真(thd)性能恶化。

15.因此,目的是为改进的led驱动器提供降低的波动。

技术实现要素:

16.本发明的目的是通过所附独立权利要求中提供的解决方案来实现的。在从属权利要求中进一步限定本发明的有利具体实施。

17.根据本发明的第一方面,提供了一种led驱动器。该led驱动器包括有源切换的pfc电路和针对有线总线的总线接口,其中从有源pfc电路的输出电压分接用于向总线供电的针对总线接口的电压供应源,该led驱动器还包括控制电路,该控制电路用于通过控制有源切换的pfc的开关来反馈控制该pfc的输出电压,其中与不具有活动的时间段相比,控制电路的反馈控制的时间常数在总线接口正在传输或接收信号的时间段期间更快。

18.这提供了这样的优点:在dali总线活动(dali总线上的下降沿和上升沿)期间,降低在由后面的转换器级供应的照明装置的光输出中能够可见的由于在dc总线级处的分接引起的波动。

19.在一个实施方案中,led驱动器包括总线电源单元,该总线电源单元优选地由pfc电路的输出电压供应,向总线接口供应dc电力以供应总线电力。

20.在一个实施方案中,控制电路是asic。

21.这提供了可以使用众所周知的控制电路的优点。

22.在一个实施方案中,微控制器控制总线接口并且被进一步配置为与asic通信。

23.在一个实施方案中,控制电路被进一步配置为检测pfc电路的开关活动的波动,并且其中微控制器被配置为在发生此类波动的情况下控制电路或者asic自身的时间常数变为更快。

24.这提供了这样的优点:在dali总线活动(dali总线上的下降沿和上升沿)期间,降低在由后面的转换器级供应的照明装置的光输出中能够可见的由于在dc总线级处的分接引起的波动。

25.在一个实施方案中,led驱动器包括电磁干扰(emi)滤波器。

26.这提供了这样的优点:显著降低由外部源产生的干扰,该干扰可以通过电磁感应、静电耦合或传导影响电路,并且可能降低电路的性能或甚至使其停止运行。

27.在一个实施方案中,led驱动器包括半桥(hb)llc电路。

28.这提供了提供高效电路的优点。

29.在一个实施方案中,功率因数校正(pfc)电路是升压pfc电路。

30.这提供了这样的优点:功率因数校正整形离线电源的输入电流以使从市电获得的实际功率最大化。

31.在一个实施方案中,led驱动器包括布置在微控制器与总线接口之间的两个光耦合器,其中光耦合器被配置为提供微控制器与总线接口的光学隔离。

32.在一个实施方案中,led驱动器包括两个变压器,其中变压器被配置为向led驱动器提供绝缘。

33.在一个实施方案中,led驱动器包括第一侧和第二侧,并且第二侧包括被配置为对

led驱动器的输出电流执行整流和感测的模块。

34.在一个实施方案中,电压供应源是12v。

35.在一个实施方案中,总线接口是dali接口。

36.这提供了提供众所周知的接口的优点。

37.根据第二方面,本发明涉及一种用于降低led驱动器上的波动的方法,该方法包括从有源pfc的输出电压分接用于向总线供电的针对总线接口的电压供应源,以及通过控制有源pfc的开关来反馈控制该pfc的输出电压,其中与不具有活动的时间段相比,反馈控制的时间常数在总线接口正在通过总线传输或接收信号的时间段期间更快。

38.根据第三方面,本发明涉及一种计算机程序,该计算机程序包括用于执行第二方面的方法的计算机产品。

附图说明

39.下面将连同附图来说明本发明。

40.图1示出了dali前向帧的示例;

41.图2示出了dali后向帧的示例;

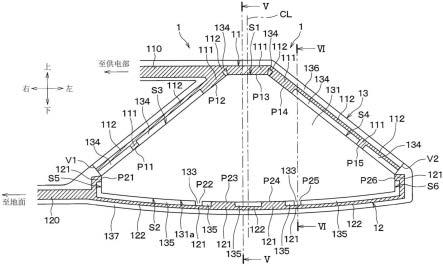

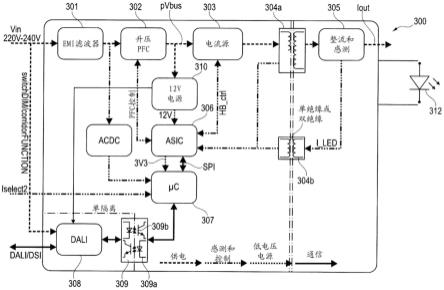

42.图3示出了根据一个实施方案的led驱动器的示意性表示;

43.图4示出了led驱动器中的不同电压(v

bus

、v

dali

和v

ctrl

)随时间变化的示意性表示;并且

44.图5示出了根据一个实施方案的用于降低led驱动器上的波动的方法的示意性表示。

具体实施方式

45.本文在led驱动器的上下文中描述了本发明的各方面。

46.下文参考附图更全面地描述了本发明,其中示出了本发明的各方面。然而,本发明可以多种不同的形式体现,并且不应理解为限于通过本公开呈现的本发明的各方面。相反,提供这些方面使得本公开将是周密且完整的,并且将向本领域的技术人员充分传达本发明的范围。附图中示出的本发明的各方面可能未按比例绘制。相反,为清楚起见,可扩大或减小各种特征结构的尺寸。此外,为清楚起见,可简化一些附图。因此,附图可能未示出给定装置的所有部件。

47.将呈现led驱动器的各个方面。然而,如本领域的技术人员将容易理解的,在不脱离本发明的情况下,这些方面可以扩展到led驱动器的各方面。

48.术语“led灯具”应指具有包括一个或多个led的光源的灯具。led在本领域中是众所周知的,因此,将仅简要讨论以提供对本发明的完整描述。

49.还应当理解,本发明的方面可包含易于使用常规半导体技术(诸如互补金属氧化物半导体技术,简称为“cmos”)制造的集成电路。此外,本发明的各方面可利用用于制造光学器件以及电气器件的其他制造工艺来实现。现在将详细参考如附图所示的示例性方面的具体实施。在整个附图和以下详细描述中将使用相同的附图标记来指代相同或类似的部件。

50.现在参见图3,示出了根据一个实施方案的led驱动器300的示意性表示。

51.led驱动器300包括有源切换的pfc电路302和针对有线总线的总线接口308。优选地,从有源切换的pfc电路302的输出电压分接用于向总线供电的针对总线接口308的低电压电压供应源310。低电压电源在总线上的活动时间段期间汲取更高的电能。

52.低电压电源310还可以供应集成电路,诸如例如asic和μc。

53.led驱动器300还包括控制电路306,该控制电路用于通过控制有源切换的pfc302的开关来反馈控制有源切换的pfc 302的输出电压,其中与不具有活动的时间段相比,控制电路306的反馈控制的时间常数在总线接口308正在传输或接收信号的时间段期间更快。

54.因此,有利地,为了通过反馈控制降低dc总线电压的波动,pfc控制时间常数应该变为快速。为了避免发生不断快速的pfc反馈控制的问题,pfc控制电路的控制时间常数仅在总线接口诸如dali总线上存在通信活动的时间段中变为更快。

55.在一个实施方案中,led驱动器300中的负责通过dali接口308通信的微控制器307选择性地增大有源切换的pfc 302在其中通过dali接口308发送出dali信号或在从总线检测到输入的dali信号时的时间段中的控制速度。

56.在另一个实施方案中,执行pfc电路302的开关的反馈控制的控制电路306(通常为asic)直接检测通常由dali总线活动引起的波动,并且在检测到此类波动时直接增大反馈控制时间常数。

57.此外,dali接口电路308可以被配置为在dali网络和微控制器307之间传输和接收信号。符合dali协议的数字数据可以通过桥式整流器(图3中未示出)在线路上传输。

58.从dali网络接收的数字数据可以被转换成数字信号并且向微控制器307传输和从其接收。微控制器307可以通过发送信号来控制asic 306执行动作诸如例如对灯312进行调光或者打开或关闭asic 306。微控制器307可以从asic 306接收信号,诸如例如灯故障检测目的。asic 306可以基于灯312表现出的故障状况确定灯312是否应该打开或关闭。

59.常规dali接口电路可以包括齐纳二极管和耦合在整流器与接收侧上的光耦合器之间的电阻器。常规dali接口电路还包括双极结型晶体管和耦合到整流器和传输侧上的光耦合器的电阻器。

60.在一个实施方案中,led驱动器300包括电磁干扰(emi)滤波器301、电流源303、整流和感测单元305、变压器304a和304b以及单元309中的两个光耦合器309a和309b。

61.具体地,led驱动器300可以包括两个4引脚光耦合器309a和309b,以便将微控制器307与从dali网络接收的数字数据光学隔离。

62.隔离电路309可以耦合在接口电路308与微控制器307之间,隔离电路309被结构化成将接口电路308与微控制器307光学隔离。隔离电路309可以保护led驱动器300的其他部件(例如,微控制器307)免受瞬时电压或电流影响。

63.隔离电路309可以包括饱和光耦合器309a和309b。在隔离电路309中使用的饱和光耦合器可以包括耦合到光耦合器的bjt的基极的附加端子,该端子耦合到电阻器以实现大体上甚至50%占空比。否则,不需要的电荷在光耦合器的bjt的基极上积聚,这大体上减慢了光耦合器的切换速度。耦合到饱和光耦合器的bjt的基极的端子可以耦合到电阻器,该电阻器耦合到传输晶体管的栅极。电容器也可以耦合到饱和光耦合器的bjt的基极。耦合到饱和光耦合器309a的bjt的基极的端子可以耦合到电阻器,该电阻器可以耦合到接地部。

64.通过dali接口308的端子从网络接收到的数字信号可以经由桥式整流器接收。接

收到的数字信号可以包括至少一个前向帧(参见图1)。类似地,通过dali接口308的端子传输到网络的数字信号可以经由桥式整流器发送。传输的数字信号可以包括至少一个后向帧(参见图2)。

65.前向帧可以是用于将数据从主节点或传输节点传输到从/远程节点或接收节点的位序列。

66.后向帧可以是用于将数据从从/远程节点或接收节点返回到主节点或传输节点的位序列。

67.此外,变压器304a和304b可以被配置为向led驱动器300提供单绝缘或双绝缘。

68.有源切换的pfc可以是升压pfc。

69.在图4中,总线的电压v

bus

、接口的电压v

dali

和控制电路307的电压v

ctrl

的示意性表示随时间变化给出。

70.如从图4可以看出,当存在dali活动时,pfc控制时间常数变为快速的(f),而当不存在dali活动时,pfc控制时间常数变为缓慢的(s)。

71.图5示出了根据一个实施方案的用于降低led驱动器300上的波动的方法500的示意性表示。

72.用于降低led驱动器300上的波动的方法500包括以下步骤:

[0073]-从有源切换的pfc 302的输出电压分接501用于向总线供电的针对总线接口308的电压供应源;以及

[0074]-通过控制有源切换的pfc 302的开关来反馈控制502该pfc的输出电压;其中与不具有活动的时间段相比,反馈控制502的时间常数在总线接口308正在通过总线传输或接收信号的时间段期间更快。

[0075]

本文所述、所示和/或受权利要求书保护的所有实施方案的所有特征可彼此组合。

[0076]

虽然上文已描述了本发明的各种实施方案,但应当理解,这些实施方案仅以举例的方式而非限制的方式给出。在不脱离本发明范围的精神的前提下,可根据本文的公开内容对本发明所公开的实施方案进行多种改变。因此,本发明的广度和范围不应受任何上述实施方案的限制。相反,本发明的范围应根据以下权利要求书及其等同物来限定。

[0077]

虽然已经相对于一个或多个具体实施例示和描述了本发明,但是本领域的技术人员在阅读本说明书和附图的理解后将想到等同的替代形式和修改形式。此外,虽然可仅相对于若干具体实施公开本发明的特定特征,但此类特征可根据任何给定或特定应用的期望和优点与其他具体实施的一个或多个其他特征组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。