1.本文所描述的主题的实施例大体上涉及射频(rf)放大器,且更具体地说,涉及具有谐波频率终端电路的功率晶体管装置和放大器。

背景技术:

2.无线通信系统采用用于增加射频(rf)信号的功率的功率放大器。通常在功率放大器的输入处实施输入阻抗匹配电路以实现最佳性能。在包括特征在于非线性输入电容的功率晶体管装置的放大器中,功率晶体管可在放大器的基本工作频率的谐波下,且具体地说在二次谐波频率下生成相当大的不合需要的信号能量。这种不合需要的二次谐波频率信号能量可能会限制放大器的可实现的性能。因此,二次谐波终端电路可在包括具有非线性输入电容的功率晶体管装置的功率放大器设计的总体性能中起重要作用。然而,常规的二次谐波终端电路可能会不合需要地与输入阻抗匹配电路相互作用,这可能会降低放大器性能。

技术实现要素:

3.根据本发明的第一方面,提供一种射频(rf)放大器,包括:

4.放大器输入;

5.具有晶体管和晶体管输入端的晶体管管芯;

6.耦合在所述放大器输入与所述晶体管输入端之间的基本频率阻抗匹配电路;以及

7.耦合在所述晶体管输入端与接地参考节点之间的谐波频率终端电路,其中所述谐波频率终端电路包括耦合在所述晶体管输入端与第一节点之间的第一电感和耦合在所述第一节点与所述接地参考节点之间的储能电路,其中所述储能电路包括耦合在所述第一节点与所述接地参考节点之间的第一电容和耦合在所述第一节点与所述接地参考节点之间的第二电感。

8.在一个或多个实施例中,所述储能电路被配置成分流二次谐波频率下或约二次谐波频率下的信号能量,同时对所述rf放大器的基本工作频率下的信号能量呈现为开路。

9.在一个或多个实施例中,所述储能电路被配置成针对所述rf放大器的基本工作频率下的信号能量用作到接地的高阻抗路径,并且针对二次谐波频率下或约二次谐波频率下的信号能量用作到接地的低阻抗路径。

10.在一个或多个实施例中,所述基本频率阻抗匹配电路包括:

11.耦合在所述放大器输入与第二节点之间的第三电感;

12.耦合在所述第二节点与所述晶体管输入端之间的第四电感;

13.耦合在所述第二节点与接地参考端之间的第二电容;以及

14.耦合在所述晶体管输入端与所述接地参考节点之间的第五电感。

15.在一个或多个实施例中,所述rf放大器另外包括:

16.在所述晶体管输入端与所述接地参考节点之间与所述第五电感串联耦合的第三

电容。

17.在一个或多个实施例中,所述rf放大器另外包括:

18.在所述第一节点与所述接地参考节点之间与所述第二电感串联耦合的第一dc阻隔电容器。

19.在一个或多个实施例中,所述晶体管具有非线性输入电容。

20.在一个或多个实施例中,所述晶体管为氮化镓晶体管。

21.根据本发明的第二方面,提供一种封装射频(rf)放大器装置,包括:

22.装置基板;

23.耦合到所述装置基板的输入引线;

24.耦合到所述装置基板的晶体管管芯,其中所述晶体管管芯包括具有晶体管输入端的晶体管;

25.耦合在所述输入引线与所述晶体管输入端之间的基本频率阻抗匹配电路;以及

26.耦合在所述晶体管输入端与接地参考节点之间的谐波频率终端电路,其中所述谐波频率终端电路包括耦合在所述晶体管输入端与第一节点之间的第一电感和耦合在所述第一节点与所述接地参考节点之间的储能电路,其中所述储能电路包括耦合在所述第一节点与所述接地参考节点之间的第一电容和耦合在所述第一节点与所述接地参考节点之间的第二电感。

27.在一个或多个实施例中,所述封装rf放大器装置另外包括:

28.耦合到所述装置基板的第一集成无源装置,其中所述第一集成无源装置包括对应于所述第一节点的第一接合垫,且所述第一电容和所述第二电感一体地形成于所述第一集成无源装置内且并联地电耦合在所述第一接合垫与所述接地参考节点之间。

29.在一个或多个实施例中,所述第一电感包括耦合在所述晶体管输入端与所述第一接合垫之间的第一接合线集合。

30.在一个或多个实施例中,所述第一集成无源装置另外包括第二接合垫;并且

31.所述谐波频率终端电路另外包括耦合在所述第一接合垫与所述第二接合垫之间的第三电感。

32.在一个或多个实施例中,所述封装rf放大器装置另外包括:

33.在所述第一节点与所述接地参考节点之间与所述第二电感串联耦合的第一dc阻隔电容器。

34.在一个或多个实施例中,所述基本频率阻抗匹配电路包括:

35.耦合在所述输入引线与第二节点之间的第三电感;

36.耦合在所述第二节点与所述晶体管输入端之间的第四电感;

37.耦合在所述第二节点与接地参考端之间的第二电容;

38.耦合在所述晶体管输入端与所述接地参考节点之间的第五电感;以及

39.在所述晶体管输入端与所述接地参考节点之间与所述第五电感串联耦合的第三电容。

40.在一个或多个实施例中,所述封装rf放大器装置另外包括:

41.耦合到所述装置基板的第二集成无源装置,其中所述第二集成无源装置包括对应于所述第二节点的第二接合垫,且所述第二电容和所述第三电容一体地形成于所述第二集

成无源装置内。

42.根据本发明的第三方面,提供一种制造rf放大器装置的方法,所述方法包括以下步骤:

43.在输入引线与输出引线之间将晶体管管芯耦合到装置基板,其中所述晶体管管芯包括晶体管和晶体管输入端;

44.在所述输入引线与所述晶体管输入端之间耦合基本频率阻抗匹配电路;以及

45.在所述晶体管输入端与接地参考节点之间耦合谐波频率终端电路,其中所述谐波频率终端电路包括耦合在所述晶体管输入端与第一节点之间的第一电感和耦合在所述第一节点与所述接地参考节点之间的储能电路,其中所述储能电路包括耦合在所述第一节点与所述接地参考节点之间的第一电容和耦合在所述第一节点与所述接地参考节点之间的第二电感。

46.在一个或多个实施例中,在所述晶体管输入端与所述接地参考节点之间耦合所述谐波频率终端电路包括:

47.在所述输入引线与所述晶体管管芯之间将集成无源装置耦合到所述装置基板,其中所述集成无源装置包括对应于所述第一节点的第一接合垫,且所述第一电容和所述第二电感一体地形成于所述集成无源装置内且并联地电耦合在所述第一接合垫与所述接地参考节点之间。

48.在所述晶体管输入端与所述第一接合垫之间耦合对应于所述第一电感的接合线集合。

49.本发明的这些和其它方面将根据下文中所描述的实施例显而易见,且参考这些实施例予以阐明。

附图说明

50.结合以下图式考虑,同时通过参考具体实施方式和权利要求书可得到对主题的更完整理解,图式中类似附图标记遍及各图指代相似元件。

51.图1为根据示例实施例的功率放大器电路的示意性电路图;

52.图2包括示出谐波频率终端电路的实施例在一系列频率内的阻抗特征曲线的图表,以及谐波频率终端电路在明显高于基本工作频率的频率下的相关联等效电路;

53.图3为根据示例实施例的体现图1的功率放大器电路的封装rf功率放大器装置的俯视图;

54.图4为根据实施例的体现谐波频率终端电路的集成无源装置的俯视图;

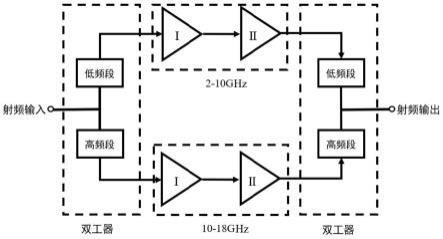

55.图5为根据示例实施例的多尔蒂功率放大器的简化示意图;并且

56.图6为根据示例实施例的用于制造包括谐波频率终端电路的实施例的封装rf功率放大器装置的方法的流程图。

具体实施方式

57.如上文所提及,在包括特征在于非线性输入电容的功率晶体管装置(例如,氮化镓(gan)晶体管)的放大器中,功率晶体管可在放大器的基本工作频率的谐波下,且具体地说在二次谐波频率下生成相当大的不合需要的信号能量。因此,此放大器的输入处可包括二

次谐波频率终端电路(“谐波终端电路”)。

58.典型的谐波终端电路包括连接在功率晶体管装置的输入(例如,栅极)与接地参考节点之间的串联耦合的电感器电容器(lc)电路(即,谐波终端电路以分流配置连接)。串联lc谐波终端电路基本上被配置成在二次谐波频率下或接近二次谐波频率时谐振,以便将二次谐波频率下的信号能量分流到接地。一些基本匹配电路包括分流电感,所述分流电感可使用接合线集合实施。lc谐波终端电路的电感也可使用接合线集合实施,且当在lc谐波终端电路中利用较高电容值时,基本匹配电路和谐波终端电路的接合线电感可能会不合需要地与放大器性能相互作用并降低放大器性能(如,通过改变基本匹配电路系统的网络谐振,因此不利地影响放大器增益)。

59.对于被配置成在相对较低的基本工作频率(例如,低于1吉兆赫(ghz))下工作的功率晶体管装置,相比于可用于在较高频率下工作的放大器的电容值,形成有效的二次谐波终端所需的谐波终端电路的电容值相当高。然而,用于低频放大器中的谐波终端电路的相对较高的电容值可能会产生谐波终端电路与基本匹配电路系统的电感之间的不合需要的相互作用。更具体地说,此谐波终端电路可能会形成较高的高通截止,这意味着用于高通谐振的有效电感可能会减小,继而可能会降低放大器增益。换句话说,对于被设计成在相对较低的基本工作频率下工作的放大器,典型的谐波终端电路可能对基本匹配电路系统不够透明,且可能会不合需要地负载基本匹配电路系统。

60.根据本发明主题的各种实施例,提供一种功率放大器电路,所述功率放大器电路包括不会呈现上文所描述的不合需要的效果的谐波终端电路系统。更具体地说,本文所论述的谐波终端电路的实施例被配置成避免干扰基本匹配电路系统,即使在以相对较低的基本频率工作的放大器中也是如此。如下文将详细描述的,本文所描述的谐波终端电路的实施例被配置成分流二次谐波频率下或约二次谐波频率下的信号能量,同时对基本频率下的信号能量呈现为开路。因此,在工作期间,谐波终端电路可基本上避免谐波终端电路与基本匹配电路系统之间的电感的上述不合需要的相互作用,因此可避免与此类相互作用相关联的不合需要的性能下降。

61.图1为rf功率放大器电路100的示意图。在实施例中,电路100包括输入102、输入基本频率阻抗匹配电路110(“基本匹配电路”)、二次谐波频率终端电路130(“谐波终端电路”)、晶体管140和输出引线104。输入102和输出104中的每一者可更笼统地被称作“rf输入/输出(i/o)”。另外,下文参考“接地参考节点”。在各种实施例中,“接地参考节点”为装置或模块的导电特征(例如,图3的法兰盘301、管芯垫或基于印刷电路板(pcb)的模块中的导电接地平面),电路100的各种部件的端耦合到所述导电特征,其中当装置或模块并入到更大的电气系统中时所述导电特征可耦合到系统接地(例如,耦合到零伏的接地参考或耦合到另一电压参考)。

62.输入102和输出104可各自包括导体(例如,封装引线),所述导体被配置成使得电路100能够与外部电路系统(未示出)电耦合。更具体地说,在实施例中,输入102和输出104物理地定位成跨在装置封装或模块的外部与内部之间。基本匹配电路110和谐波终端电路130电耦合在输入102与晶体管140的输入端142(还被称作“晶体管输入端”、“控制端”或“栅极端”)之间。晶体管140的第一载流端144(例如,漏极端)直接或间接(例如,通过输出阻抗匹配电路,未示出)耦合到输出104。晶体管140的第二载流端145(例如,源极端)耦合到接地

参考节点。

63.根据实施例,晶体管140为电路100的主要有源部件。晶体管140包括控制端142和两个载流端144、145,其中载流端144、145通过可变电导率通道在空间和电气上分离。例如,晶体管140可为包括栅极端(控制端142)、漏极端(第一载流端144)和源极端(第二载流端145)的场效应晶体管(fet)。根据实施例,并且使用通常以非限制性方式应用于fet的命名法,晶体管140的栅极端142耦合到基本匹配电路110和谐波终端电路130,晶体管140的漏极端144耦合到输出104,并且晶体管140的源极端145耦合到接地(或另一电压参考)。通过改变提供到晶体管140的栅极端的控制信号,可调制晶体管140的载流端之间的电流。

64.根据各种实施例,晶体管140为iii-v型场效应晶体管(例如,高电子迁移率晶体管(hemt)),其相比于基于硅的fet(例如,横向扩散的金属氧化物半导体(ldmos)fet)具有非线性输入电容和相对较低的漏极端源极端电容cds。根据实施例,晶体管140可具有小于约0.2pf/w的漏极端源极端电容。另外,在一些实施例中,晶体管140可为gan fet,但在其它实施例中,晶体管140可为另一种类型的iii-v型晶体管(例如,砷化镓(gaas)、磷化镓(gap)、磷化铟(inp)或锑化铟(insb)),或具有非线性输入电容和相对较低的漏极端源极端电容的另一种类型的晶体管。

65.如上文所提及,基本匹配电路110和谐波终端电路130电耦合在输入102与晶体管140的第一端142(例如,栅极端)之间。更具体地说,基本匹配电路110耦合在输入102与第二节点124之间,所述第二节点124又耦合到晶体管140的控制端142(例如,栅极端)。基本匹配电路110被配置成在节点102处将晶体管140的栅极阻抗变换(例如,升高)到更高的(例如,中间或更高的)阻抗电平(例如,介于约2欧姆至约10欧姆或更高欧姆之间的范围内)。

66.根据实施例,基本匹配电路110具有带通滤波器拓扑,所述带通滤波器拓扑包括单个t型匹配电路和(与dc阻隔电容器串联的)分流电感。更具体地说,且根据所示的实施例,基本匹配电路110包括t型匹配电路,所述t型匹配电路包括耦合在输入102与第一节点115(还被称作“连接节点”)之间的第一电感元件112(例如,图3的第一接合线集合312)、耦合在节点115与接地参考节点之间的分流电容114以及耦合在节点115与第二节点124之间的第二电感元件116(例如,图3的第二接合线集合316),所述第二节点124又耦合到晶体管140的控制端142。分流电感包括与电容122(例如,dc阻隔电容器)串联耦合的电感元件118(例如,图3的第三接合线集合318),其中串联电感和电容耦合在第二节点124(或晶体管140的控制端142)与接地参考节点之间。根据实施例,电感元件112、116和分流电容114形成类带通滤波器配置的低通滤波器部分,并且分流电感元件118形成类带通滤波器配置的高通滤波器部分。这种类带通配置允许在rf频率下进行宽带操作,而这在利用更简单的匹配网络的情况下是难以实现的。

67.根据实施例,电感元件112的电感值可介于约150微微亨(ph)至约400ph之间的范围内,电感元件116的电感值可介于约80ph至约600ph之间的范围内,分流电感118的电感值可介于约100ph至约350ph之间的范围内,并且分流电容114的电容值可介于约6皮法(pf)至约60pf之间的范围内。对于大功率应用,dc阻隔电容器122的电容值可介于约60pf至约240pf之间的范围内。在其它实施例中,上文所列的部件中的一些或全部可具有比上文给定的范围更小或更大的部件值。

68.根据实施例,谐波终端电路130耦合在第二节点124(或晶体管140的输入端142(例

如,栅极端))与接地参考节点之间。因此,第二节点124基本上对应于到谐波终端电路130的输入。谐波终端电路130基本上包括耦合在第二节点124(或晶体管140的输入端142)与第三节点132之间的电感131(例如,图3的第四接合线集合331),以及耦合在第三节点132与接地参考节点之间的储能电路138。储能电路138基本上包括与电容133并联的电感137,其中并联组合耦合在第三节点132与接地参考节点之间。根据实施例,dc阻隔电容器139可与电感137串联耦合。也就是说,谐波终端电路130包括与并联lc储能电路串联耦合的电感131(即,与电容133并联的电感137/dc阻隔电容器139)。

69.根据实施例,为储能电路138选择的电感和电容值将电路138配置成:针对基本工作频率下的信号能量用作到接地的高阻抗路径(例如,实际上为开路),并且针对二次谐波频率下或约二次谐波频率下(例如,二次谐波频率下或10%的二次谐波频率内)的信号能量用作到接地的低阻抗路径。更具体地说,且简单地参考图2,图表200示出了储能电路138在一系列频率内的阻抗特征曲线。在图表200中,频率202至少大约(例如,在5%的范围内)对应于放大器100的基本工作频率。在基本频率202下,储能电路138的阻抗达到峰值,因此基本上自身针对基本频率下的信号能量呈现为到节点124、132和晶体管140的输入端142的开路。在低于基本频率202的频率下,储能电路138的电感137起主导作用,并且在高于基本频率202的频率下,如图表200右侧的简化电路210中所指示,储能电路138的电容133起主导作用,并且串联lc电路由电感131和电容133形成。

70.根据实施例,为储能电路138的并联的电感137和电容133选择值以使得在基本工作频率下,电感137和电容133形成具有极高阻抗的并联谐振(例如,几乎为开路)。在较高频率下,电感137呈现极高阻抗,并且储能电路138的电容133的主导作用变得更明显,而电感137的主导作用变得不太明显。根据实施例,在二次谐波频率下或接近二次谐波频率时,谐波终端电路130的电气等效物基本上包括串联lc电路,所述串联lc电路包括电感131(串联lc电路的“l”)和储能电路138的电容133(串联lc电路的“c”)。为这种有效串联lc电路的电感131和电容133选择值以使得所述电路在二次谐波频率下或约二次谐波频率下谐振。可选择131的值以终止二次谐波频率下或约二次谐波频率下的最优位置处的信号能量。因此,对于二次谐波频率下或约二次谐波频率下的信号能量,谐波终端电路130将自身呈现为到接地的低阻抗路径。

71.根据实施例,电感131的电感值介于约200ph至约500ph之间的范围内,电感137的电感值介于约200ph至约1000ph之间的范围内,并且电容133的电容值介于约10pf至约50pf之间的范围内。对于大功率应用,dc阻隔电容器139的电容值可介于约60pf至约250pf之间的范围内。在其它实施例中,谐波终端电路130的各种部件的值可低于或高于上述给定范围中指定的那些值。

72.由于储能电路138基本上自身对于基本频率下的信号能量呈现为开路,因此在放大器100的工作期间,微小或可忽略的基本频率电流分量流过电感131和137。因此,当使用接合线实施谐波终端电路130的电感131、137中的任一者或两者时,那些接合线电感131、137不大可能与基本匹配电路110的电感118、116明显地(例如,通过互耦合)相互作用,所述电感118、116也可以接合线的形式实施。因此,利用谐波终端电路130中的储能电路138可避免明显改变基本匹配电路系统110的网络谐振,从而避免产生对放大器增益的不利影响。

73.尽管晶体管140以及基本匹配电路110和谐波终端电路130的各个元件示出为单个

部件,但描述仅出于易于说明的目的。本领域的技术人员基于本文中的描述应理解,晶体管140和/或基本匹配电路110和谐波终端电路130的某些元件可各自实施为(例如,彼此并联或串联连接的)多个部件。另外,实施例可包括单路径装置(例如,包括单个输入引线、输出引线、晶体管等)、双路径装置(例如,包括两个输入引线、输出引线、晶体管等),和/或多路径装置(例如,包括两个或更多个输入引线、输出引线、晶体管等)。另外,输入/输出引线的数目可不与晶体管的数目相同(例如,可存在用于输入/输出引线的给定集合的同时工作的多个晶体管)。因此,对晶体管140以及基本匹配电路110和谐波终端电路130的各种元件的特定描述并不意图将本发明主题的范围仅限制到所示的实施例。

74.再次参考图1且如稍后将结合图3和4更详细地描述的,rf放大器装置的各种实施例可包括至少一个输入侧集成无源装置(ipd)(例如,图3、4的ipd 310、330、430),所述至少一个输入侧ipd被配置成实施基本匹配电路110和谐波终端电路130的部分。更具体地说,每一ipd可包括具有一个或多个集成无源部件的半导体基板。在特定实施例中,输入侧ipd可包括分流电容114、122、133和139(图1)。

75.在其它实施例中,基本匹配电路110和/或谐波终端电路130的一些部分可实施为不同/离散的部件或实施为其它类型的组件(例如,低温共烧陶瓷(ltcc)装置、小型pcb组件等)的部分。在又其它实施例中,基本匹配电路110和/或谐波终端电路130的一些部分可耦合到包括晶体管140的半导体管芯和/或集成在所述半导体管芯内。对包括ipd的实施例的以下详细描述不应被理解为限制本发明主题,且术语“无源装置基板”或“ipd基板”意味着包括无源装置的任何类型的结构,包括ipd、ltcc装置、晶体管管芯、pcb组件等。

76.放大器100在一些实施例中可实施于离散、封装的功率放大器装置中,或在其它实施例中可实施于基于pcb的模块中。在此类装置中,输入和输出引线耦合到支撑基板,并且与放大器100相关联的部件也耦合到基板。功率放大器管芯外壳晶体管140以及基本匹配电路110和谐波终端电路130包括为封装装置或模块内的这些部件中的一些部件。

77.例如,图3为体现图1的放大器100的封装rf放大器装置300的实施例的俯视图。如下文将更详细地描述的,装置300包括功率晶体管管芯340和两个输入侧ipd 310、330,其中的每一者包括基本匹配电路(例如,图1的电路110)或谐波终端电路(例如,图1的电路130)的部分。

78.在实施例中,装置300包括法兰盘301(或“装置基板”),所述法兰盘301可包括刚性导电和导热基板,所述刚性导电和导热基板的厚度足以为装置300的各种电气部件和元件提供结构支撑。法兰盘301具有顶部表面和底部表面,其中图3中可见顶部表面。根据实施例,法兰盘301可用作晶体管管芯340的散热片。另外,法兰盘301可对应于装置300的接地参考节点(且更具体地说,晶体管管芯340和ipd 310、330的接地参考节点)。例如,各种部件和元件可具有电耦合到法兰盘301的端,且当装置300并入到更大的电气系统中时,法兰盘301可电耦合到系统接地。至少法兰盘301的顶部表面由导电材料层形成,且有可能所有的法兰盘301由块体导电材料形成。

79.尽管图3中未示出,但在实施例中,隔离结构可附接到法兰盘301的顶部表面。由刚性电绝缘材料形成的隔离结构在装置的导电特征之间(例如,在引线302、304与法兰盘301之间)提供电隔离。在实施例中,隔离结构可具有框架形状,所述框架形状包括具有中心开口的大体封闭的四边结构。可替换的是,隔离结构可具有另一形状(例如,环形圈、椭圆形

等)。

80.法兰盘301的顶部表面的通过隔离结构中的开口暴露的一部分在本文中被称作装置300的“有源区域”晶体管管芯340和ipd 310、330定位在装置300的有源装置区域内,并且物理耦合且电耦合到法兰盘301的顶部表面。例如,晶体管管芯340和ipd 310、330可使用导电环氧树脂、焊料、焊料凸点、烧结和/或共晶接合耦合到法兰盘301的顶部表面。

81.根据图3所示的实施例,装置300并入在空气腔封装中,其中功率晶体管管芯340和ipd 310、330定位在封闭的空气腔内。基本上,空气腔由法兰盘301、隔离结构(未示出)以及上覆于并接触隔离结构和引线302、304的盖(未示出)限界。在其它实施例中,装置300的部件可并入到包覆模制封装(即,其中有源装置区域内的电气部件用非导电模制化合物封装且其中引线302、304的部分也可由模制化合物包围的封装)中。在又其它实施例中,装置300的部件可并入到无引线封装(例如,双扁平无引线(dfn)或方形扁平无引线(qfn)封装)中,或并入到其它类型的封装中。

82.无关于所利用的封装的类型,装置300容纳表示放大器电路100(图1)的物理实施方案的单个放大路径。体现于装置300中的放大路径包括输入引线302(例如,图1的输入102)、输出引线304(例如,图1的输出104)、功率晶体管管芯340(例如,体现图1的晶体管140)、输入侧阻抗匹配电路(例如,图1的基本匹配电路110)和输入侧谐波终端电路(例如,图1的谐波终端电路130)。一些实施例还可具有输出侧阻抗匹配电路和/或输出侧谐波终端电路(未示出)。

83.输入引线302和输出引线304可安装在隔离结构的顶部表面上,位于中心开口的相对侧上,且因此输入引线302和输出引线304升高到法兰盘301的顶部表面之上,且与法兰盘301电隔离。通常,输入引线302和输出引线304定向成允许在输入引线302和输出引线304与隔离结构的中心开口内的部件和元件之间附接接合线。

84.晶体管管芯340包括集成功率晶体管341(例如,图1的晶体管140)。晶体管341具有输入端(例如,图1的输入端142)和两个载流端(例如,图1的输出/漏极端144和源极端145)。如先前结合图1所论述,晶体管341可为场效应晶体管(fet)。例如,且根据各种实施例,晶体管341可为hi-v型场效应晶体管(例如,hemt)或另一类型的晶体管。在一些实施例中,晶体管341可具有非线性输入电容。

85.晶体管341的输入端耦合到管芯340的输入接合垫342,晶体管341的第一载流端(例如,输出/漏极端)耦合到管芯340的输出接合垫344,并且晶体管341的第二载流端可(例如,使用穿基板通孔和管芯340的底部上的导电层)耦合到法兰盘301,且因此耦合到接地参考节点。输出接合垫344(且因此,晶体管341的第一载流端)通过接合线集合346电耦合到输出引线304。

86.应注意,在图3中,为说明方便起见,针对本文所论述的各种接合线集合(例如,接合线集合312、316、331、337-1、318-1、346)中的每一者,仅圈示/参考一个接合线。连接在相同的两个元件之间的所有接合线被视为在相同的接合线集合内。另外,尽管在图3中,每一接合线集合示出为包括特定数目的接合线,但每一接合线集合可包括比所示的接合线更少或更多的接合线。通常,对于任何特定的接合线集合,接合线的数目和接合线的特征曲线/长度确定与接合线集合相关联的所需电感值。

87.再次参考晶体管管芯340,输入接合垫342(且因此晶体管341的输入端)通过基本

匹配电路(例如,图1的电路110)和谐波终端电路(例如,图1的电路130)耦合到输入引线302(例如,图1的输入102)。换句话说,基本匹配电路(例如,图1的电路110)和谐波终端电路(例如,图1的电路130)电耦合在输入引线302(例如,图1的输入102)与晶体管管芯340的输入接合垫342之间(且因此耦合到晶体管341的输入端)。为了帮助理解图3,在图3的右下角中示出了基本匹配电路的电气等效物,并且在图3的右上角中示出了谐波终端电路的电气等效物。

88.根据所示的实施例,基本匹配电路(例如,图1的电路110)的部分体现于在输入引线302与晶体管管芯340之间耦合到法兰盘301的顶部表面的第一ipd 310中。更具体地说,基本匹配电路的体现于ipd 310内的部分包括第一分流电容314和分流lc网络,所述分流lc网络包括电感318-2和电容322的串联组合。使用接合线312、316、318-1实施基本匹配电路的其它部分,且具体地说其它电感部分。利用接合垫(例如,接合垫315、317)实施各种导电“节点”。

89.如先前结合图1所论述的,根据实施例,基本匹配电路包括具有第一电感的t型匹配电路,所述第一电感呈第一接合线集合312(例如,图1的第一电感元件112)的形式,所述第一接合线集合312的第一端耦合到输入引线(例如,图1的输入102)且第二端耦合到ipd 310的接合垫315(例如,对应于图1的节点115)。t型匹配电路另外包括分流电容器314(例如,图1的电容114),所述分流电容器314的第一端耦合到接合垫315且第二端耦合到接地参考节点(例如,法兰盘301)。另外,t型匹配电路另外包括第二电感,所述第二电感呈第二接合线集合316(例如,图1的第二电感元件116)的形式,所述第二接合线集合316的第一端耦合到接合垫315且第二端耦合到晶体管管芯340的输入接合垫342(且因此,晶体管341的输入/控制端)。

90.基本匹配电路还包括分流电感,所述分流电感包括第三接合线集合318-1(例如,图1的电感元件118的一部分)、ipd 310内的集成螺旋电感器318-2和ipd 310内的集成电容器322的串联布置,所述第三接合线集合318-1的第一端耦合到晶体管管芯340的输入接合垫342且第二端耦合到ipd 310的接合垫317。集成螺旋电感器318-2的第一端耦合到接合垫317,且集成螺旋电感器312-2的第二端耦合到集成电容器322的第一端。电容器322的第二端耦合到接地参考节点(例如,法兰盘301)。基本上,第三接合线集合318-1、接合垫317和集成螺旋电感器318-2对应于电感118(图1),且集成电容器322对应于电容122(图1)。

91.此时,可注意到,在图3的实施例中,对应于图1中的电感118和电容122的一部分的lc电路使用耦合在接合垫317与法兰盘301之间的多个(在此情况下四个)并联lc电路来实施。还在图3的右下角中所示的电气等效电路中描绘了并联lc电路配置。如带有省略号(“...”)的电气等效电路所示,更多或更少的并联lc电路可集成在ipd 310内,以提供对应于图1中的电感118和电容122的一部分的lc电路。

92.另外,可注意到,对应于电感118(图1)的接合线318-1、接合垫317和集成螺旋电感器318-2的组合可采取其它形式。例如,当单独的接合线318-1足以提供所需的电感118(图1)时,集成螺旋电感器318-2可从ipd 310中排除,且接合垫317可直接耦合到集成电容器322的第一端。

93.根据所示的实施例,谐波终端电路(例如,图1的电路130)的部分体现于在输入引线302与晶体管管芯340之间耦合到法兰盘301的顶部表面的第二ipd 330中。更具体地说,

体现于ipd 330内的谐波终端电路的部分包括储能电路338(例如,图1的储能电路138),所述储能电路338包括电容器333(例如,图1的电容133)和电感器337(例如,图1的电感137)的并联组合,其中电感器337与dc阻隔电容器339(例如,图1的电容139)串联耦合。使用接合线集合331实施谐波终端电路的其它部分,且具体地说其它电感部分。并且,利用接合垫(例如,接合垫332、335)实施各种导电“节点”。

94.如先前结合图1所论述的,根据实施例,谐波终端电路包括第一电感,所述第一电感呈第一接合线集合331(例如,图1的电感元件131)的形式,所述第一接合线集合331的第一端耦合到晶体管管芯340的输入接合垫342(且因此,晶体管341的输入/控制端)且第二端耦合到ipd330的接合垫332(例如,对应于图1的节点132)。谐波终端电路还包括耦合在接合垫332(对应于图1的节点132)与接地参考节点(例如,法兰盘301)之间的储能电路338(例如,图1的储能电路138)。更具体地说,储能电路338包括ipd 330的电容器333(例如,图1的电容133),所述电容器333的第一端耦合到接合垫332且第二端耦合到接地参考节点(例如,法兰盘301)。另外,储能电路338包括分流电感,所述分流电感包括第五接合线集合337-1(例如,图1的电感元件137的一部分)、ipd 330内的集成螺旋电感器337-2(例如,图1的电感元件137的另一部分)和dc阻隔电容器339(例如,图1的电容139)的串联布置。第五接合线集合337-1的接合线的第一端耦合到ipd 330的接合垫332且第二端耦合到ipd 330的接合垫335。集成螺旋电感器337-2的第一端耦合到接合垫335,且集成螺旋电感器337-2的第二端耦合到集成电容器339的第一端。电容器339的第二端耦合到接地参考节点(例如,法兰盘301)。

95.此时,可注意到,在图3的实施例中,对应于图1中的电感137和电容139的一部分的lc电路使用耦合在接合垫335与法兰盘301之间的多个(在此情况下四个)并联lc电路来实施。还在图3的右上角中所示的电气等效电路中描绘了并联lc电路配置。如带有省略号(“...”)的电气等效电路所示,更多或更少的并联lc电路可集成在ipd 330内,以提供对应于图1中的电感137和电容139的一部分的lc电路。

96.如上文所提及,在另一实施例中,ipd 330的用于提供与谐波终端电路(例如,图1的电路130)相关联的各种部件的替代实施例可在装置300中实施。更具体地说,图4为根据另一实施例的体现谐波频率终端电路的部分的ipd 430的俯视图。基本上,在图3中,ipd 330(包括接合线337-1)可用ipd 430替换。

97.更具体地说,根据替代实施例,谐波终端电路(例如,图1的电路130)的部分体现于可在输入引线302与晶体管管芯340之间耦合到法兰盘(例如,图3的法兰盘301)的顶部表面的ipd 430中。谐波终端电路的体现于ipd 430内的部分包括储能电路438(例如,图1的储能电路138),所述储能电路438包括分流电容器433(例如,图1的电容133)和与dc阻隔电容器439(例如,图1的电容139)串联耦合的电感器437(例如,图1的电感137)的并联组合。

98.ipd 330与ipd 430之间的基本差异在于,在ipd 430中,分流电容器433的第一端和电感器437的第一端直接电耦合到接合垫435,而非通过接合线集合(例如,图3的接合线337-1)耦合。

99.如上文所提及,装置300体现了输入引线302与输出引线304之间的单个放大路径。当并入多路径放大器(例如,下文结合图5所描述的多尔蒂放大器500)中时,体现于装置300中的放大路径可对应于主放大器路径(例如,图5的主放大器路径520),或放大路径可对应

于峰化放大器路径(例如,图5的峰化放大器路径521)。因此,装置300的两个实例可用以提供主放大器路径和峰化放大器路径两者,但部分个别部件可能存在差异(例如,峰化放大器路径中的功率晶体管可能大于主放大器路径中的功率晶体管)。在替代实施例中,装置300可被修改为包括在相同封装内并联实施的两个放大路径(例如,装置可包括两个输入引线、两个输出引线和图3所描绘的电路系统的两个实例),以便在多路径放大器中得到更高效的利用。

100.例如,图5为其中可实施rf功率放大器电路100的两个并联实例的多尔蒂功率放大器500的简化示意图。放大器500包括输入节点502、输出节点504、功率分配器506(或分离器)、主放大器路径520、峰化放大器路径521和组合节点580。负载590可(例如,通过阻抗变换器,未示出)耦合到组合节点580以从放大器500接收放大后rf信号。

101.功率分配器506被配置成将在输入节点502处接收到的输入rf信号的功率划分成输入信号的主要部分和峰化部分。向功率分配器输出508处的主放大器路径520提供主输入信号,且向功率分配器输出509处的峰化放大器路径521提供峰化输入信号。在满功率模式下的工作期间,当主放大器540和峰化放大器541均向负载590供应电流时,功率分配器506在放大器路径520、521之间分配输入信号功率。例如,功率分配器506可相等地分配功率,使得约一半的输入信号功率被提供到每一路径520、521(例如,针对对称多尔蒂放大器配置)。可替换的是,功率分配器506可不等地分配功率(例如,针对不对称多尔蒂放大器配置)。

102.基本上,功率分配器506分配在输入节点502处供应的输入rf信号,且分配后信号分别沿着主放大器路径520和峰化放大器路径521被放大。随后在组合节点580处同相地组合放大后信号。重要的是,在目标频带内维持主放大器路径520与峰化放大器路径521之间的相位相干性以确保放大后的主信号和峰化信号同相地到达组合节点580,且因此确保恰当的多尔蒂放大器操作。

103.主放大器540和峰化放大器541中的每一者包括一个或多个单级或多级功率晶体管管芯(例如,图3的管芯340),用于放大通过放大器540、541传导的rf信号。根据各种实施例,可例如使用iii-v型场效应晶体管(例如,hemt)来实施主放大器540和/或峰化放大器541中的任一者或两者的所有放大器级或最终放大器级,所述iii-v型场效应晶体管例如gan fet(或另一类型的iii-v型晶体管,包括gaas fet、gap fet、inp fet或insb fet)。在一些实施例中,在主放大器540或峰化放大器541中的仅一者实施为iii-v型fet的情况下,其它放大器可实施为基于硅的fet(例如,ldmos fet)。

104.尽管主功率晶体管管芯和峰化功率晶体管管芯可具有相同的大小(例如,呈对称多尔蒂配置),但主功率晶体管管芯和峰化功率晶体管管芯也可具有不同的大小(例如,呈各种不对称多尔蒂配置中)。呈不对称多尔蒂配置时,峰化功率晶体管管芯通常通过一些倍增器大于主功率晶体管管芯。例如,峰化功率晶体管管芯的大小可为主功率晶体管管芯的大小的两倍,以使峰化功率晶体管管芯的载流能力为主功率晶体管管芯的载流能力的两倍。还可实施除2∶1比率以外的峰化放大器管芯大小与主放大器管芯大小比率。

105.在多尔蒂放大器500的工作期间,主放大器540被偏置以在ab类模式下工作,且峰化放大器541被偏置以在c类模式下工作。在低功率电平下,其中节点502处的输入信号的功率比峰化放大器541的接通阈值电平低,放大器500在低功率(或回退(back-off))模式下工作,其中主放大器540为向负载590供应电流的唯一放大器。当输入信号的功率超过峰化放

大器541的阈值电平时,放大器500在高功率模式下工作,其中主放大器540和峰化放大器541均向负载590供应电流。此时,峰化放大器541在组合节点580处提供有源负载调制,从而允许主放大器540的电流持续线性地增大。

106.可在主放大器540的输入和/或输出处实施输入阻抗匹配网络510和输出阻抗匹配网络550(输入mnm、输出mnm)。类似地,可在峰化放大器541的输入和/或输出处实施输入阻抗匹配网络511和输出阻抗匹配网络551(输入mnp、输出mnp)。在每种情况下,匹配网络510、511、550、551可用于将主放大器540和峰化放大器541的栅极阻抗和漏极阻抗变换为更合乎需要的系统级阻抗,并且操控信号相位以确保恰当的多尔蒂放大器操作。输入阻抗匹配网络510、511和输出阻抗匹配网络550、551中的全部或部分可在包括主放大器540和/或峰化放大器541的功率晶体管封装内部实施,或输入阻抗匹配网络510、511和输出阻抗匹配网络550、551的一些部分可在安装功率晶体管封装的pcb或其它基板上实施。根据实施例,输入阻抗匹配网络510、511中的每一者可具有与上文所描述的基本匹配电路(例如,图1的电路110)相同或类似的配置。

107.另外,本发明主题的实施例包括耦合在放大器540、541的输入与接地参考节点之间的谐波频率终端电路530、531(例如,图1的谐波终端电路130的实例)。谐波终端电路530、531被配置成在相对较宽的分数带宽内控制谐波阻抗。例如,谐波终端电路530、531可针对放大器500的基本工作频率的二次谐波下的信号能量提供到接地的低阻抗路径。

108.如具有虚线框300-1、300-2的图5中所指示,主放大路径520的输入匹配电路510、放大器540和谐波终端电路530可使用装置300的第一实例实施,并且峰化放大路径521的输入匹配电路511、放大器541和谐波终端电路531可使用装置300的第二实例实施。在替代实施例中,且如先前所论述,主放大路径和峰化放大路径的上述部件可组合到单个封装主体中。

109.多尔蒂放大器500具有“非倒置”负载网络配置。在非倒置配置中,输入电路被配置成使得在放大器500的基本工作频率下供应到峰化放大器541的输入信号相对于供应到主放大器540的输入信号延迟90度。如对恰当的多尔蒂放大器操作来说基本的,为了确保主输入rf信号和峰化输入rf信号以约90度的相位差到达主放大器540和峰化放大器541,相位延迟元件582向峰化输入信号施加约90度的相位延迟。例如,相位延迟元件582可包括四分之一波长传输线,或具有约90度的电长度的另一合适类型的延迟元件。

110.为了补偿放大器540、541的输入处的主放大器路径520与峰化放大器路径521之间的所得90度相位延迟差(即,为了确保放大后信号同相地到达组合节点580),输出电路被配置成向主放大器540与组合节点580的输出之间的信号施加约90度的相位延迟。这通过额外的延迟元件584实现。多尔蒂放大器的替代实施例可具有“倒置”负载网络配置。在此配置中,输入电路被配置成使得在放大器500的中心工作频率下供应到主放大器540的输入信号相对于供应到峰化放大器541的输入信号延迟约90度,且输出电路被配置成向峰化放大器541与组合节点580的输出之间的信号施加约90度的相位延迟。

111.图6为根据各种示例实施例的用于制造封装rf功率放大器装置(例如,图3的装置300)的方法的流程图,所述封装rf功率放大器装置包括基本匹配电路和谐波终端电路(例如,图1的电路110、130)的实施例。在框602,所述方法可通过形成一个或多个ipd而开始。更具体地说,在框602,可形成一个或多个输入ipd(例如,图3、4的ipd 310、330、430)。根据实

施例,第一输入ipd(例如,图3的ipd 310)包括基本匹配电路的部件,且第二输入ipd(例如,图3、4的ipd 330、430)包括谐波终端电路的部件。例如,第一输入ipd(例如,图3的ipd 310)可包括一个或多个集成电容器(例如,图3的电容器314、322)和一个或多个电感元件(例如,图3的电感元件318-2)。第二输入ipd(例如,图3、4的ipd 330或430)可包括一个或多个集成电容器(例如,图3、4的电容器333、339、433、439)。除了形成每一ipd的无源部件之外,形成每一ipd还包括形成各种导电特征(例如,导电层和导通孔),所述导电特征促进每一电路的各种部件之间的电连接。例如,形成ipd还可包括在每一ipd基板的表面处形成各种可接入的连接节点。如先前所论述,连接节点可包括导电接合垫(例如,图3、4的接合垫315、317、332、335、435),所述导电接合垫可接受电感元件(例如,图3、4的接合线312、316、318-1、331、337-1)的附接。另外,在框602,当对应于各种电路元件(例如,图3的接合线337-1)的一些部件实施为非集成部件时,那些离散部件可耦合到在ipd的表面处暴露的导体以形成ipd组件。例如,再次参考图3,在一些实施例中,接合线337-1可耦合在ipd 310的接合垫332与335之间。

112.在框604,对于空气腔实施例,将隔离结构耦合到装置基板(例如,图3的法兰盘301)。另外,一个或多个有源装置(例如,图3的晶体管管芯340)和ipd组件(例如,ipd或图3、4的ipd组件310、330、430)耦合到基板的顶部表面的通过隔离结构中的开口暴露的一部分。引线(例如,图3的输入引线302和输出引线304)耦合到隔离结构的顶部表面。对于包覆模制(例如,包封)装置实施例,可不包括隔离结构,并且基板和引线可形成引线框架的部分。

113.在框606,将输入引线、晶体管、ipd组件和输出引线电耦合在一起。例如,可在各种装置部件和元件之间使用接合线形成电连接,如先前所论述。例如,一些接合线对应于输入匹配电路(例如,图3的接合线312、316、318-1)和谐波终端电路(例如,图3、4的接合线331、337-1)的电感部件。最后,在框608,(例如,对于空气腔封装)盖住或(例如,利用用于包覆模制封装的模制化合物)包封装置。装置可随后并入到较大的电气系统(例如,多尔蒂放大器或其它类型的电气系统)中。

114.一种rf放大器的实施例包括放大器输入,具有晶体管和晶体管输入端的晶体管管芯,耦合在所述放大器输入与所述晶体管输入端之间的基本频率阻抗匹配电路,以及耦合在所述晶体管输入端与接地参考节点之间的谐波频率终端电路。所述谐波频率终端电路包括耦合在所述晶体管输入端与第一节点之间的第一电感和耦合在所述第一节点与所述接地参考节点之间的储能电路。所述储能电路包括耦合在所述第一节点与所述接地参考节点之间的第一电容和耦合在所述第一节点与所述接地参考节点之间的第二电感。

115.根据另外的实施例,所述储能电路被配置成分流二次谐波频率下或约二次谐波频率下的信号能量,同时对所述rf放大器的基本工作频率下的信号能量呈现为开路。

116.根据又一另外的实施例,所述储能电路被配置成针对所述rf放大器的基本工作频率下的信号能量用作到接地的高阻抗路径,并且针对二次谐波频率下或约二次谐波频率下的信号能量用作到接地的低阻抗路径。

117.一种封装rf放大器装置的实施例包括装置基板,耦合到所述装置基板的输入引线,以及耦合到所述装置基板的晶体管管芯,所述晶体管管芯包括具有晶体管输入端的晶体管。所述装置另外包括耦合在所述输入引线与所述晶体管输入端之间的基本频率阻抗匹配电路,以及耦合在所述晶体管输入端与接地参考节点之间的谐波频率终端电路。所述谐

波频率终端电路包括耦合在所述晶体管输入端与第一节点之间的第一电感和耦合在所述第一节点与所述接地参考节点之间的储能电路。所述储能电路包括耦合在所述第一节点与所述接地参考节点之间的第一电容和耦合在所述第一节点与所述接地参考节点之间的第二电感。

118.一种制造rf放大器装置的方法的实施例包括在输入引线与输出引线之间将晶体管管芯耦合到装置基板,其中所述晶体管管芯包括晶体管和晶体管输入端。所述方法另外包括在所述输入引线与所述晶体管输入端之间耦合基本频率阻抗匹配电路,以及在所述晶体管输入端与接地参考节点之间耦合谐波频率终端电路。所述谐波频率终端电路包括耦合在所述晶体管输入端与第一节点之间的第一电感和耦合在所述第一节点与所述接地参考节点之间的储能电路。所述储能电路包括耦合在所述第一节点与所述接地参考节点之间的第一电容和耦合在所述第一节点与所述接地参考节点之间的第二电感。

119.先前详细描述本质上仅为说明性的,且并不意图限制主题的实施例或此类实施例的应用和使用。如本文中所使用,词语“示例性”意味着“充当例子、实例或说明”。本文中描述为“示例性”的任何实施方案未必解释为比其它实施方案优选或有利。另外,不希望受前述先前技术领域、背景技术或具体实施方式中所呈现的任何所表达或暗示的理论的约束。

120.本文包含的各图中所示的连接线意图表示各种元件之间的示例性功能关系和/或物理耦合。应注意,许多替代或另外的功能关系或物理连接可存在于主题的实施例中。另外,本文中还可仅出于参考的目的使用特定术语且因此所述特定术语并不意图进行限制,并且除非上下文清楚地指示,否则指代结构的术语“第一”、“第二”和其它此类数值术语并不暗示顺序或次序。

121.如本文中所使用,“节点”意味着任何内部或外部参考点、连接点、接合点、信号线、导电元件等,在“节点”处存在给定信号、逻辑电平、电压、数据模式、电流或量。此外,两个或更多个节点可通过一个物理元件实现(并且尽管在公共节点处接收或输出,但仍然可对两个或更多个信号进行多路复用、调制或以其它方式区分)。

122.以上描述是指元件或节点或特征“连接”或“耦合”在一起。如本文中所使用,除非以其它方式明确地陈述,否则“连接”意味着一个元件直接接合到另一元件(或直接与另一元件通信),且不一定以机械方式接合。同样,除非以其它方式明确地陈述,否则“耦合”意味着一个元件直接或间接接合到另一元件(或直接或间接以电气方式或以其它方式与另一元件通信),且不一定以机械方式接合。因此,尽管图中所示的示意图描绘元件的一个示例性布置,但所描绘的主题的实施例中可存在额外介入元件、装置、特征或部件。

123.尽管以上详细描述中已呈现至少一个示例性实施例,但应了解,存在大量变化。还应了解,本文中所描述的一个或多个示例性实施例并不希望以任何方式限制所主张的主题的范围、适用性或配置。实际上,以上详细描述将向本领域的技术人员提供用于实施所描述的一个或多个实施例的方便指南。应理解,可在不脱离由权利要求书所限定的范围的情况下对元件的功能和布置作出各种改变,权利要求书所限定的范围包括在提交本专利申请案之时的已知等效物和可预见的等效物。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。