基于ldpc码的编码方法、系统、介质及装置

技术领域

1.本发明涉及通信技术领域,特别是涉及一种基于ldpc码的编码方法、系统、介质及装置。

背景技术:

2.随着世界经济文化的快速发展,用户对无线信息业务的需求量快速增长。单独依靠传统无线广播网或传统无线双向通信网,已无法实现信息业务的最优化传输。与此同时,人们不再满足于仅仅收看传统的无线广播电视业务,而是对新型无线交互广播电视业务有着越来越强烈的需求。无线交互广播电视(aib)系统,可实现无线广播和无线双向交互通信的融合共存,是解决移动信息业务数据量快速增长和无线网络传输容量受限之间矛盾的有效途径,也是支撑有线、无线融合创新业务的必要途径。

3.在复杂多变的无线环境中,aib系统业务传输面临严重的干扰和噪声问题。纠错编码技术是保证信息传输的可靠性、克服噪声和干扰的最有效技术之一。由于ldpc码的误码平层较深、译码复杂度较低,所以其被众多通信标准所采纳。

4.在传统的通信系统中,例如dvb-t2(第二代欧洲数字地面电视广播传输),采用s-ira结构的ldpc码,这种ldpc码编码复杂度低,只需要根据校验矩阵即可实现线性复杂度的编码。但dvb-t2系统中所采用的ldpc码,存在以下三个问题:一、低码率(码率<1/2)码字的译码门限距离香农限较远,性能有待于进一步提升;二、某些码字错误平层高于ber=1e-7;三、其1/5码率的ldpc码是为了保护信令而设计,传输信道的最低码率为4/9,使得传输信道在深度衰落的场景下无法正常工作。

5.因此,希望能够解决ldpc码在低码率译码门限距离香农限较远,在深度衰落的场景下无法正常工作的问题。

技术实现要素:

6.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种基于ldpc码的编码方法、系统、介质及装置,用于解决现有技术中ldpc码在低码率译码门限距离香农限较远,在深度衰落的场景下无法正常工作的问题。

7.为实现上述目的及其他相关目的,本发明提供一种基于ldpc码的编码方法,包括以下步骤:长度为k

bch

比特的待传输数据构成bch码的信息比特其中m0为待传输数据最高有效位(msb),为最低有效位(lsb);对信息比特m进行bch码编码,将得到的bch码的校验比特将所述校验比特d附加在信息比特m之后,得到ldpc码的信息比特对长度为k

ldpc

的信息比特λ进行ldpc码编码,得到的ldpc码的校验比特将所述校验比特δ附加在信息比特λ之后,得到码长为n

ldpc

的ldpc码系统码字

所述系统码字u的长度为n

ldpc

;所述ldpc码的长度为k

ldpc

;码长为n

ldpc

;基本参数为:

8.ldpc码率k

ldpc

n

ldpc

z2/152560192003201/63200192003201/53840192003201/44800192003201/36400192003205/128000192003201/29600192003207/1211200192003202/312800192003203/414400192003204/51536019200320

9.所述ldpc码为系统码,所述ldpc码的校验矩阵h是一个定义在域gf(2)上维度为m

ldpc

×

n

ldpc

的分块矩阵;

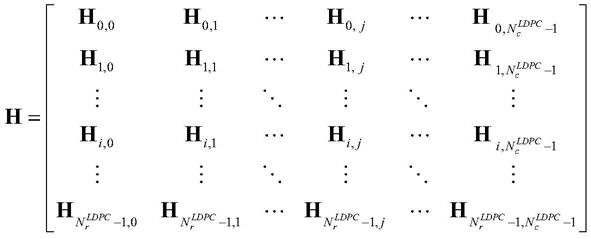

[0010][0011]

其中,m

ldpc

=n

ldpc-k

ldpc

,每一个子块h

i,j

是一个维度为z

×

z的循环矩阵,h

i,j

的第k行(1≤k≤z-1)由h

i,j

的第0行循环右移k个元素得到;校验矩阵h由其第kz行的所有元素唯一确定。

[0012]

于本发明的一实施例中,所述ldpc码的码率大于等于1/2时,所述校验矩阵h由为(n

ldpc-k

ldpc

)

×

k

ldpc

的稀疏分块结构矩阵和为(n

ldpc-k

ldpc

)

×

(n

ldpc-k

ldpc

)的101 双对角结构矩阵构成。

[0013]

于本发明的一实施例中,所述ldpc码的码率小于1/2时,所述校验矩阵h由为从左至右依次排布的横排数相同的高密度分块结构矩阵a,101 双对角结构矩阵b和零阵z;以及排布在所述矩阵a、b、z下方的从左至右依次排布的横排数相同的稀疏分块结构矩阵c和对角阵d构成。

[0014]

于本发明的一实施例中,所述bch码采用定义在域gf(2

14

)上的本原bch系统码作为外码,其生成多项式十六进制表示为:120bba549566ba23004bf345d7adc79eae3330c560d。

[0015]

于本发明的一实施例中,所述ldpc码的校验矩阵h在码率分别2/15、1/6、1/5、1/4、

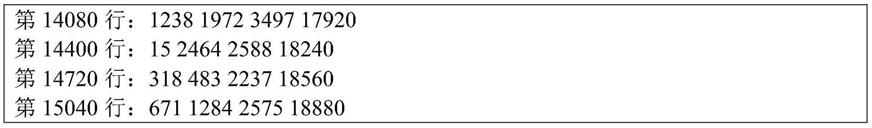

1/3、5/12、1/2、7/12、2/3、3/4、4/5时分别对应如下表a.1、a.2、a.3、a.4、a.5、a.6、a.7、a.8、a.9、a.10、a.11所定义:(具体表格详见说明书)。

[0016]

为实现上述目的,本发明还提供一种基于ldpc码的编码系统,包括:bch码构成模块、bch码编码模块和ldpc码编码模块;所述bch码构成模块用于长度为k

bch

比特的待传输数据构成bch码的信息比特其中m0为待传输数据最高有效位(msb),为最低有效位(lsb);所述bch码编码模块用于对信息比特m进行bch码编码,将得到的bch码的校验比特将所述校验比特d附加在m之后,得到ldpc码的信息比特所述ldpc码编码模块用于对长度为k

ldpc

的信息比特λ进行ldpc码编码,得到的ldpc码的校验比特将所述校验比特δ附加在信息比特λ之后,得到码长为n

ldpc

的ldpc码系统码字所述系统码字u的长度为n

ldpc

;所述ldpc码的长度为k

ldpc

;码长为n

ldpc

;基本参数为:

[0017][0018][0019]

所述ldpc码为系统码,所述ldpc码的校验矩阵h是一个定义在域gf(2)上维度为m

ldpc

×

n

ldpc

的分块矩阵;

[0020][0021]

其中,m

ldpc

=n

ldpc-k

ldpc

,每一个子块h

i,j

是一个维度为z

×

z的循环矩阵,h

i,j

的第k行(1≤k≤z-1)

由h

i,j

的第0行循环右移k个元素得到;校验矩阵h由其第kz行的所有元素唯一确定。

[0022]

于本发明的一实施例中,所述ldpc码的码率大于等于1/2时,所述校验矩阵h由为(n

ldpc-k

ldpc

)

×

k

ldpc

的稀疏分块结构矩阵和为(n

ldpc-k

ldpc

)

×

(n

ldpc-k

ldpc

)的101 双对角结构矩阵构成。

[0023]

于本发明的一实施例中,所述ldpc码的码率小于1/2时,所述校验矩阵h由为从左至右依次排布的横排数相同的高密度分块结构矩阵a,101 双对角结构矩阵b和零阵z;以及排布在所述矩阵a、b、z下方的从左至右依次排布的横排数相同的稀疏分块结构矩阵c和对角阵d构成。

[0024]

为实现上述目的,本发明还提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现任一上述基于ldpc码的编码方法。

[0025]

为实现上述目的,本发明还提供一种基于ldpc码的编码装置,包括:处理器和存储器;所述存储器用于存储计算机程序;所述处理器与所述存储器相连,用于执行所述存储器存储的计算机程序,以使所述基于ldpc码的编码装置执行任一上述的基于ldpc码的编码方法。

[0026]

如上所述,本发明的一种基于ldpc码的编码方法、系统、介质及装置,具有以下有益效果:对应的11种码率的ldpc码均具有逼近香农限的译码门限,涵盖了深度衰落下的深度覆盖场景和高速率数据传输场景。

附图说明

[0027]

图1a显示为本发明的基于ldpc码的编码方法于一实施例中的流程图;

[0028]

图1b显示为本发明的基于ldpc码的编码方法于一实施例中的校验矩阵h的结构图;

[0029]

图1c显示为本发明的基于ldpc码的编码方法于又一实施例中的校验矩阵的结构图;

[0030]

图1d显示为本发明的基于ldpc码的编码方法于一实施例中的码长为19200的ldpc码在awgn信道下的性能示意图;

[0031]

图1e显示为本发明的基于ldpc码的编码方法于又一实施例中的码长为19200的ldpc码在awgn信道下的性能示意图;

[0032]

图2显示为本发明的基于ldpc码的编码系统于一实施例中的结构示意图;

[0033]

图3显示为本发明的基于ldpc码的编码装置于一实施例中的结构示意图。

[0034]

元件标号说明

[0035]

21

ꢀꢀꢀꢀꢀꢀꢀ

bch码构成模块

[0036]

22

ꢀꢀꢀꢀꢀꢀꢀ

bch码编码模块

[0037]

23

ꢀꢀꢀꢀꢀꢀꢀ

ldpc码编码模块

[0038]

31

ꢀꢀꢀꢀꢀꢀꢀ

处理器

[0039]

32

ꢀꢀꢀꢀꢀꢀꢀ

存储器

具体实施方式

[0040]

以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

[0041]

需要说明的是,以下实施例中所提供的图示仅以示意方式说明本发明的基本构想,故图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

[0042]

本发明的基于ldpc码的编码方法、系统、介质及装置,基于ldpc码的编码方法、系统、介质及装置,对应的11种码率的码均具有逼近香农限的译码门限,涵盖了深度衰落下的深度覆盖场景和高速率数据传输场景。

[0043]

如图1所示,于一实施例中,本发明的基于ldpc码的编码方法,包括以下步骤:

[0044]

步骤s11、长度为k

bch

比特的待传输数据构成bch码的信息比特其中m0为待传输数据最高有效位(msb),为最低有效位(lsb)。

[0045]

具体地,所述为长度为k

bch

比特的待传输数据。所述为0、1比特序列的向量序列。信息比特m是bch码的信息比特。

[0046]

步骤s12、对信息比特m进行bch码编码,将得到的bch码的校验比特将所述校验比特d附加在信息比特m之后,得到ldpc码的信息比特

[0047]

具体地,所述bch码是一类能够纠正多个随机错误的循环码。所述信息比特λ的长度为k

ldpc

。信息比特λ是ldpc码的信息比特。

[0048]

步骤s13、对长度为k

ldpc

的信息比特λ进行ldpc码编码,得到的ldpc码的校验比特将所述校验比特δ附加在λ之后,得到码长为n

ldpc

的ldpc码系统码字所述系统码字u的长度为n

ldpc

。

[0049]

所述ldpc码的长度为k

ldpc

;码长为n

ldpc

;基本参数为:

[0050][0051][0052]

所述ldpc码为系统码,所述ldpc码的校验矩阵h是一个定义在域gf(2)上维度为m

ldpc

×

n

ldpc

的分块矩阵;

[0053][0054]

其中,m

ldpc

=n

ldpc-k

ldpc

,

[0055]

每一个子块h

i,j

是一个维度为z

×

z的循环矩阵,h

i,j

的第k行(1≤k≤z-1)由h

i,j

的第0行循环右移k个元素得到;校验矩阵h由其第kz行的所有元素唯一确定。

[0056]

具体地,所述第kz行是指第k乘以z行。gf是galois field的缩写,中文称其为galois域或有限域,域gf(2)是最简单的有限域,只有0,1二元运算、 (异或运算)、

×

(与运算)。

[0057]

具体地,所述ldpc码的码率大于等于1/2时,所述校验矩阵h由为(n

ldpc-k

ldpc

)

×

k

ldpc

的稀疏分块结构矩阵和为(n

ldpc-k

ldpc

)

×

(n

ldpc-k

ldpc

)的101 双对角结构矩阵构成。所述(n

ldpc-k

ldpc

)

×

k

ldpc

的稀疏分块结构矩阵如图1b的左半部分矩阵所示,稀疏矩阵是指矩阵中数值为0的元素数目远远多于非0元素的数目,并且非0元素分布没有规律时,则称该矩阵为稀疏矩阵;与之相反,若非0元素数目占大多数时,则称该矩阵为高密度矩阵。矩阵中非零元素的个数远远小于矩阵元素的总数,并且非零元素的分布没有规律,通常认为矩阵中非零元素的总数比上矩阵所有元素总数的值小于等于0.05时,则称该矩阵为稀疏矩阵(sparse matrix)。而稀疏分块结构矩阵是指分块结构的矩阵前提下的稀疏矩阵。分块矩阵是一个矩阵,它是把矩阵分别按照横竖分割成一些小的子矩阵。然后把每个小矩阵看成一个元素。如果分块矩阵的非零子矩阵都在对角线上,就称为对角分块矩阵。分块矩阵仍满足矩阵的乘法和加法。任何方阵都可以通过相似变换,变为约当标准型。约当标准型是最熟知的分块矩

阵。利用分块矩阵可以简化很多有关矩阵性质的证明。既满足稀疏矩阵又同时是分块矩阵即为稀疏分块结构矩阵。所述101 双对角结构矩阵是指如图1b的右半部分矩阵所示的矩阵,其中,图1b中方块内的0表示单位阵,1表示循环右移一位的单位阵。即校验矩阵h具有图1b所示的结构,其中校验部分为101 双对角结构矩阵,系统部分为稀疏分块结构矩阵,只利用校验矩阵而非生成矩阵,即可实现线性时间内编码。

[0058]

具体地,所述ldpc码的码率小于1/2时,所述校验矩阵h由为从左至右依次排布的横排数相同的高密度分块结构矩阵a,101 双对角结构矩阵b和零阵z;以及排布在所述矩阵a、b、z下方的从左至右依次排布的横排数相同的稀疏分块结构矩阵c和对角阵d构成。具体地,如图1c所示,所述高密度分块结构矩阵a是指既满足高密度矩阵又同时是分块矩阵即为高密度分块结构矩阵,101 双对角结构矩阵b如图1c的矩阵b所示的矩阵。所述零阵z是指所有元素皆为0的矩阵,所述稀疏分块结构矩阵c既满足稀疏矩阵又同时是分块矩阵即为稀疏分块结构矩阵,所述对角阵d是指对角分块矩阵,每个对角线上的子矩阵为单位阵,即方块内的零。

[0059]

具体地,所述bch码采用定义在域gf(2

14

)上的本原bch系统码作为外码,其生成多项式十六进制表示为:120bba549566ba23004bf345d7adc79eae3330c560d。

[0060]

具体地,本发明针对但不限于无线交互广播(aib)系统的业务需求和技术需求,进一步提升aib系统(包含并不仅限于aib系统)的性能,使其更加逼近香农限,本发明为aib系统的固定接收场景,设计了一套ldpc码编码方案。aib系统的fec(前向纠错)编码由bch编码(外编码)和ldpc编码(内编码)级联构成。本发明只设计内码ldpc码的设计方案。长度为k

ldpc

的ldpc码的信息比特进行ldpc编码,得到ldpc码校验比特并将其附加在信息比特之后,得到长度为n

ldpc

的ldpc码字。移动接收场景ldpc码的码长为n

ldpc

=19200,包含11个不同码率,分别为2/15、1/6、1/5、1/4、1/3、5/12、1/2、7/12、2/3、3/4和4/5。

[0061]

具体地,所述ldpc码的校验矩阵在码率分别2/15、1/6、1/5、1/4、1/3、5/12、1/2、7/12、2/3、3/4和4/5时分别对应如下表a.1、a.2、a.3、a.4、a.5、a.6、a.7、a.8、a.9、a.10、a.11所定义:ldpc码率为2/15的校验矩阵h具体如表a.1所示:其中除非零元素外,其他均为零元素。例如,表a.1第0行的第245列、第1181列、第2105列、第3015列、第3434列、第3769列、第4138列、第5088列、第7999列、第8206列、第9143列、第9385列、第10241列、第10560列的元素是非零元素。给出了校验矩阵h的第kz行的非零元素的位置,这些行中其他位置的元素取值为零,所述第kz行是指第k乘以z行。

[0062]

ldpc码率为1/6的校验矩阵h具体如表a.2所示。ldpc码率为1/5的校验矩阵h具体如表a.3所示。ldpc码率为1/4的校验矩阵h具体如表a.4所示。ldpc码率为1/3的校验矩阵h具体如表a.5所示。ldpc码率为5/12的校验矩阵h具体如表a.6所示。ldpc码率为1/2的校验矩阵h具体如表a.7所示。ldpc码率为7/12的校验矩阵h具体如表a.8所示。ldpc码率为2/3的校验矩阵h具体如表a.9所示。ldpc码率为3/4的校验矩阵h具体如表a.10所示。ldpc码率为4/5的校验矩阵h具体如表a.11所示。码长n

ldpc

为19200的ldpc码在awgn信道、qpsk信道,ber=10-7

下,其工作范围为-5.6db~4.65db(snr),涵盖了深度衰落下的深度覆盖场景和高速率数据传输场景;在本技术中,相邻码的译码门限间隔约为1db(snr),使网络部署具有极大的灵活性;所有11种码率的码均具有逼近香农限的译码门限;与dvb-t2系统的ldpc码相比,本技术的ldpc码具有更广的工作范围(dvb-t2的1/5码仅在信令信道中使用)、更均匀的工

作点分布、更大的瀑布区斜率、更低的译码门限。码长为19200的ldpc码在awgn信道下的性能如图1d和1e所示。

[0063]

具体地,码长为19200的ldpc码在awgn信道下译码门限:

[0064][0065]

表a.1:2/15码率ldpc码校验矩阵,n

ldpc

=19200

[0066]

[0067][0068]

表a.2:1/6码率ldpc码校验矩阵,n

ldpc

=19200

[0069]

[0070][0071]

表a.3:1/5码率ldpc码校验矩阵,n

ldpc

=19200

[0072]

[0073][0074]

表a.4:1/4码率ldpc码校验矩阵,n

ldpc

=19200

[0075]

[0076][0077]

表a.5:1/3码率ldpc码校验矩阵,n

ldpc

=19200

[0078]

[0079][0080]

表a.6:5/12码率ldpc码校验矩阵,n

ldpc

=19200

[0081]

[0082][0083]

表a.7:1/2码率ldpc码校验矩阵,n

ldpc

=19200

[0084][0085]

表a.8:7/12码率ldpc码校验矩阵,n

ldpc

=19200

[0086][0087]

表a.9:2/3码率ldpc码校验矩阵,n

ldpc

=19200

[0088]

[0089][0090]

表a.10:3/4码率ldpc码校验矩阵,n

ldpc

=19200

[0091][0092]

表a.11:4/5码率ldpc码校验矩阵,n

ldpc

=19200

[0093][0094]

如图2所示,于一实施例中,本发明的基于ldpc码的编码系统,bch码构成模块21、bch码编码模块22和ldpc码编码模块23.

[0095]

所述bch码构成模块21用于长度为k

bch

比特的待传输数据构成bch码的信息比特其中m0为待传输数据最高有效位(msb),为最低有效位(lsb)。

[0096]

所述bch码编码模块22用于对信息比特m进行bch码编码,将得到的bch码的校验比特将所述校验比特d附加在m之后,得到ldpc码的信息比特

[0097]

所述ldpc码编码模块23用于对长度为k

ldpc

的信息比特λ进行ldpc码编码,得到的ldpc码的校验比特将所述校验比特δ附加在λ之后,得到码长为n

ldpc

的ldpc码系统码字所述系统码字u的长度为n

ldpc

;所述ldpc码的长度为k

ldpc

;码长为n

ldpc

;基本参数为:

[0098]

ldpc码率k

ldpc

n

ldpc

z2/152560192003201/63200192003201/5384019200320

1/44800192003201/36400192003205/128000192003201/29600192003207/1211200192003202/312800192003203/414400192003204/51536019200320

[0099]

所述ldpc码为系统码,所述ldpc码的校验矩阵h是一个定义在域gf(2)上维度为m

ldpc

×

n

ldpc

的分块矩阵;

[0100][0101]

其中,m

ldpc

=n

ldpc-k

ldpc

,每一个子块h

i,j

是一个维度为z

×

z的循环矩阵,h

i,j

的第k行(1≤k≤z-1)由h

i,j

的第0行循环右移k个元素得到;校验矩阵h由其第kz行的所有元素唯一确定。

[0102]

具体地,所述ldpc码的码率大于等于1/2时,所述校验矩阵h由为(n

ldpc-k

ldpc

)

×

k

ldpc

的稀疏分块结构矩阵和为(n

ldpc-k

ldpc

)

×

(n

ldpc-k

ldpc

)的101 双对角结构矩阵构成。

[0103]

具体地,所述ldpc码的码率小于1/2时,所述校验矩阵h由为从左至右依次排布的横排数相同的高密度分块结构矩阵a,101 双对角结构矩阵b和零阵z;以及排布在所述矩阵a、b、z下方的从左至右依次排布的横排数相同的稀疏分块结构矩阵c和对角阵d构成。

[0104]

具体地,所述bch码采用定义在域gf(2

14

)上的本原bch系统码作为外码,其生成多项式十六进制表示为:120bba549566ba23004bf345d7adc79eae3330c560d。

[0105]

需要说明的是,bch码构成模块21、bch码编码模块22和ldpc码编码模块23的结构和原理与上述基于ldpc码的编码方法中的步骤一一对应,故在此不再赘述。

[0106]

需要说明的是,应理解以上系统的各个模块的划分仅仅是一种逻辑功能的划分,实际实现时可以全部或部分集成到一个物理实体上,也可以物理上分开。且这些模块可以全部以软件通过处理元件调用的形式实现;也可以全部以硬件的形式实现;还可以部分模块通过处理元件调用软件的形式实现,部分模块通过硬件的形式实现。例如,x模块可以为单独设立的处理元件,也可以集成在上述装置的某一个芯片中实现,此外,也可以以程序代码的形式存储于上述装置的存储器中,由上述装置的某一个处理元件调用并执行以上x模块的功能。其它模块的实现与之类似。此外这些模块全部或部分可以集成在一起,也可以独立实现。这里所述的处理元件可以是一种集成电路,具有信号的处理能力。在实现过程中,

上述方法的各步骤或以上各个模块可以通过处理器元件中的硬件的集成逻辑电路或者软件形式的指令完成。

[0107]

例如,以上这些模块可以是被配置成实施以上方法的一个或多个集成电路,例如:一个或多个特定集成电路(application specific integrated circuit,简称asic),或,一个或多个微处理器(micro processor uint,简称mpu),或,一个或者多个现场可编程门阵列(field programmable gate array,简称fpga)等。再如,当以上某个模块通过处理元件调度程序代码的形式实现时,该处理元件可以是通用处理器,例如中央处理器(central processing unit,简称cpu)或其它可以调用程序代码的处理器。再如,这些模块可以集成在一起,以片上系统(system-on-a-chip,简称soc)的形式实现。

[0108]

于本发明一实施例中,本发明还包括一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现上述任一所述基于ldpc码的编码方法。

[0109]

本领域普通技术人员可以理解:实现上述各方法实施例的全部或部分步骤可以通过计算机程序相关的硬件来完成。前述的计算机程序可以存储于一计算机可读存储介质中。该程序在执行时,执行包括上述各方法实施例的步骤;而前述的存储介质包括:rom、ram、磁碟或者光盘等各种可以存储程序代码的介质。

[0110]

如图3所示,于一实施例中,本发明的基于ldpc码的编码装置包括:处理器31和存储器32;所述存储器32用于存储计算机程序;所述处理器31与所述存储器32相连,用于执行所述存储器32存储的计算机程序,以使所述基于ldpc码的编码装置执行任一所述的基于ldpc码的编码方法。

[0111]

具体地,所述存储器32包括:rom、ram、磁碟、u盘、存储卡或者光盘等各种可以存储程序代码的介质。

[0112]

优选地,所述处理器31可以是通用处理器,包括中央处理器(central processing unit,简称cpu)、网络处理器(network processor,简称np)等;还可以是数字信号处理器(digital signal processor,简称dsp)、专用集成电路(application specific integrated circuit,简称asic)、现场可编程门阵列(field programmable gate array,简称fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件。

[0113]

综上所述,本发明基于ldpc码的编码方法、系统、介质及装置,对应的11种码率的ldpc码均具有逼近香农限的译码门限,涵盖了深度衰落下的深度覆盖场景和高速率数据传输场景。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

[0114]

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。