1.实施例的方面涉及差分信号驱动电路和光电转换设备。

背景技术:

2.近年来,诸如低电压差分信令(lvds)方案或可扩展低电压信令(slvs)方案的差分信号传输方案已被广泛用作高速数据通信方案。专利文献1公开了一种lvds驱动器,该lvds驱动器抑制由于电阻器的制造变化而导致的输出幅度的变化。

3.引文列表

4.专利文献

5.ptl 1:日本专利申请特开no.2018-085713

技术实现要素:

6.技术问题

7.专利文献1中公开的lvds驱动器由输出电路和多个控制电路形成,并且通过使用控制电路来确定从输出电路输出的差分信号的高电平和低电平。当不需要从lvds驱动器输出数据时,例如,可以断开lvds驱动器的输出电路的电流路径以减少电力。然而,在专利文献1中公开的lvds驱动器中,当从电流路径断开的状态恢复之后开始数据输出时,紧接在开始输出之后差分信号的高电平可能具有比lvds驱动器的操作状态下的电压高的电压。在启动电源等时可能发生相同的现象。

8.问题的解决方案

9.根据实施例的一个方面,提供了一种装置,所述装置包括多个差分发送器、以及向所述多个差分发送器中的每一个供给电源电压的电源电路。所述电源电路包括:公共的电路单元,所述公共的电路单元限定供给到所述多个差分发送器的电源电压;以及多个单独的电路单元,所述多个单独的电路单元与所述多个差分发送器相关联地提供并且各自连接到所述公共的电路单元。所述多个单独的电路单元中的每一个具有输出节点,所述输出节点将所述公共的电路单元限定的电源电压输出到所述多个差分发送器中的对应的差分发送器,并且所述多个单独的电路单元中的一个的输出节点和所述多个单独的电路单元中的另一个的输出节点彼此连接。

10.此外,根据实施例的另一方面,提供了一种电源电路,所述电源电路向与多个通道对应的多个差分发送器供给电源电压,并且所述电源电路包括:公共的电路单元,所述公共的电路单元限定供给到所述多个差分发送器的电源电压;以及多个单独的电路单元,所述多个单独的电路单元与所述多个差分发送器相关联地提供并且各自连接到所述公共的电路单元。所述多个单独的电路单元中的每一个具有输出节点,所述输出节点将所述公共的电路单元限定的电源电压输出到所述多个差分发送器中的对应的一个,并且所述多个单独的电路单元中的一个的输出节点和所述多个单独的电路单元中的另一个的输出节点彼此连接。

11.从以下参考附图对示例性实施例的描述,本公开的其它特征将变得清楚。

附图说明

12.图1是图示根据本公开的第一实施例的差分信号驱动电路的总体配置的电路图。

13.图2是图示根据本公开的第一实施例的差分信号驱动电路中的差分发送器的配置示例的电路图。

14.图3是图示根据本公开的第一实施例的差分信号驱动电路的操作的图。

15.图4是图示根据第一参考例的差分信号驱动电路的总体配置的电路图。

16.图5是图示根据第一参考例的差分信号驱动电路的操作的图。

17.图6是图示根据第一参考例的差分信号驱动电路的目标的图。

18.图7是图示根据第二参考例的差分信号驱动电路的总体配置的电路图。

19.图8是图示根据本公开的第一实施例的修改例的差分信号驱动电路的总体配置的电路图。

20.图9是图示根据本公开的第二实施例的光电转换设备的总体配置的框图。

21.图10是图示根据本公开的第三实施例的成像系统的总体配置的框图。

22.图11a是图示根据本公开的第四实施例的成像系统的配置示例的图。

23.图11b是图示根据本公开的第四实施例的可移动体的配置示例的图。

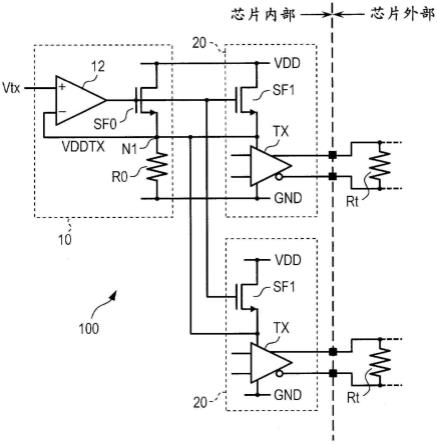

具体实施方式

24.现在将根据附图详细描述本公开的示例性实施例。

25.第一实施例

26.将参考图1至图3描述根据本公开的第一实施例的差分信号驱动电路。图1是图示根据本实施例的差分信号驱动电路的总体配置的电路图。图2是图示根据本实施例的差分信号驱动电路中的差分发送器的配置示例的电路图。图3是图示根据本实施例的差分信号驱动电路的操作的图。

27.如图1中所示,根据本实施例的差分信号驱动电路100包括公共的电路单元10和多个单独的电路单元20。多个单独的电路单元20中的每一个是与一个通道对应的电路块。尽管为了简化说明在图1中仅图示了两个单独的电路单元20,但是单独的电路单元20的数量不被特别限制,并且可以根据所需的通道的数量适当地增加或减少。

28.公共的电路单元10包括差分放大器电路12、n沟道mos晶体管sf0和负载电阻器r0。多个单独的电路单元20中的每一个包括n沟道mos晶体管sf1和差分发送器tx。公共的电路单元10限定要供给到多个差分发送器tx的电源电压。此外,单独的电路单元20的n沟道mos晶体管sf1将由公共的电路单元10限定的电源电压输出到对应的差分发送器tx。即,在形成差分信号驱动电路100的电路元件中,公共的电路单元10和单独的电路单元20的n沟道mos晶体管sf1形成向差分发送器tx的电源电压端子供给电源电压的电源电路。

29.公共的电路单元10的差分放大器电路12具有两个输入端子(非反转输入端子( )和反转输入端子(-))以及输出端子。差分放大器电路12的输出端子连接到n沟道mos晶体管sf0的栅极。n沟道mos晶体管sf0具有连接到电源电压节点(电压vdd)的漏极,并且形成源极跟随器电路。n沟道mos晶体管sf0的源极连接到负载电阻器r0的一个端子和差分放大器电

路12的反转输入端子。负载电阻器r0的另一个端子连接到基准电压节点(gnd节点)。在以下的描述中,出于说明的目的,n沟道mos晶体管sf0的源极、负载电阻器r0的一个端子、差分放大器电路12的反转输入端子的连接节点被称为节点n1。

30.注意的是,尽管在图1中负载电阻器r0被图示为连接到n沟道mos晶体管sf0的负载元件,但是可以连接不同的负载元件,例如电流源,而不是负载电阻器r0。

31.基准电压(电压vtx)被供给到差分放大器电路12的非反转输入端子。当差分放大器电路12的反转输入端子的电压被表示为vddtx时,由于差分放大器电路12被虚短路,因此电压vddtx等于电压vtx。即,n沟道mos晶体管sf0的源极的电压,即,节点n1的电压为电压vtx。

32.单独的电路单元20的差分发送器tx具有电源电压端子、基准电压端子、一对差分输入端子和一对差分输出端子。n沟道mos晶体管sf1具有连接到电源电压节点(电压vdd)的漏极,并且形成源极跟随器电路。n沟道mos晶体管sf1的栅极连接到n沟道mos晶体管sf0的栅极和差分放大器电路12的输出端子。n沟道mos晶体管sf1的源极连接到节点n1和差分发送器tx的电源电压端子。即,n沟道mos晶体管sf1的源极是向差分发送器tx输出电源电压的输出节点。

33.差分发送器tx的基准电压端子连接到基准电压节点(gnd节点)。差分发送器tx的差分输出端子连接到安装有差分信号驱动电路100的芯片外部的终端电阻器rt。

34.以这样的方式,在根据本实施例的差分信号驱动电路100中,公共的电路单元10的n沟道mos晶体管sf0和单独的电路单元20的n沟道mos晶体管sf1连接使得栅极被共同连接,漏极被共同连接,并且源极被共同连接。因此,n沟道mos晶体管sf1中的每一个的源极的电压,即,供给到单独的电路单元20中的每一个的差分发送器tx的电源电压端子的电压为电压vtx。

35.差分发送器tx例如如图2中所示可以由n沟道mos晶体管m1、m2、m3和m4以及电阻器r1和r2形成。n沟道mos晶体管m1和m2的漏极经由电阻器r1连接到电压vddtx_i所供给到的电源电压端子。n沟道mos晶体管m1的源极连接到n沟道mos晶体管m3的漏极。n沟道mos晶体管m2的源极连接到n沟道mos晶体管m4的漏极。n沟道mos晶体管m3和m4的源极经由电阻器r2连接到基准电压端子(gnd节点)。

36.在成对的差分输入端子中,数据d输入到的一个输入端子连接到n沟道mos晶体管m1的栅极和n沟道mos晶体管m4的栅极。在成对的差分输入端子中,作为数据d的反转数据的数据db输入到的另一个输入端子连接到n沟道mos晶体管m2的栅极和n沟道mos晶体管m3的栅极。

37.n沟道mos晶体管m1的源极和n沟道mos晶体管m3的漏极的连接节点是成对的差分输出端子中的一个输出端子。例如,从一个输出端子输出的信号是例如数据outp。此外,n沟道mos晶体管m2的源极和n沟道mos晶体管m4的漏极的连接节点是成对的差分输出端子中的另一个输出端子。从另一个输出端子输出的信号是例如数据outn。终端电阻器rt连接到安装有差分信号驱动电路100的芯片外部的差分输出端子。此外,差分输出端子中的一个输出端子连接到布置在接收器芯片上的接收器rx的非反转输入端子。差分输出端子的另一个输出端子连接到布置在接收器芯片上的接收器rx的反转输入端子。

38.接下来,将参考图2描述从差分发送器tx输出的信号的高电平的电压vsigh。本文

假定数据d处于高电平并且数据db处于低电平。

39.在图2中所示的差分发送器tx中,当高电平的数据d和低电平的数据db输入到差分输入端子时,n沟道mos晶体管m1和m4接通,并且n-沟道mos晶体管m2和m3关断。由此,电流从被供给电压vddtx_i的电源电压端子经由电阻器r1、n沟道mos晶体管m1、终端电阻器rt、n沟道mos晶体管m4和电阻器r2流到基准电压端子。如果本文假定n沟道mos晶体管m1和m4的沟道电阻可以忽略,那么电压vsigh可以被表达为下面的式子(1)。

40.vsigh=vddtx_i

×

(rt r2)/(r1 rt r2)...(1)

41.在本文中,考虑公共的电路单元10处于操作状态并且差分发送器tx处于非操作状态的情况。这样的情况可以是例如电源启动时的情况、不需要将数据输出到芯片的外部的情况等。

42.当差分发送器tx处于非操作状态时,从降低电力消耗的角度,从电源电压端子流动的电流的路径与基准电压端子断开。断开电流路径的方法可以是例如将数据d和数据db两者控制在低电平以关断所有n沟道mos晶体管m1至m4的方法。替代地,差分发送器tx可以被配置为具有当差分发送器tx处于非操作状态时将差分输出端子连接到固定电位的组件。

43.将参考图3描述当公共的电路单元10处于操作状态并且差分发送器tx处于非操作状态时的操作。注意的是,在图3中,差分发送器tx的电路符号由虚线表示,以便视觉地表达差分发送器tx处于非操作状态和从电源电压端子流到基准电压端子的电流的路径断开的开路状态。

44.如上所述,单独的电路单元20的n沟道mos晶体管sf1的源极被共同连接到节点n1。因此,n沟道mos晶体管sf1的源极的电压vddtx是电压vtx,并且供给到差分发送器tx的电源电压端子的电压vddtx_i也是电压vtx。

45.当差分发送器tx从这个状态转变到操作状态时,电压vtx继续被供给到差分发送器tx的电源电压端子。即,电源电压端子的电压即使紧接在差分发送器tx恢复到操作状态之后也是电压vtx,并且从差分发送器tx输出的信号在如式子(1)所表达的期望的电压范围内。

46.注意的是,当差分发送器tx恢复到操作状态时,电阻器r1和r2以及终端电阻器rt作为负载连接到n沟道mos晶体管sf1。因此,在恢复之后,电流被供给到在恢复之前没有电流流过的这些负载电阻器,并且这导致n沟道mos晶体管sf1的源极电压暂时下降。然而,因为差分放大器电路12的输出电压响应于这个电压变化而增加,所以n沟道mos晶体管sf1的源极的电压,即,差分发送器tx的电源电压端子的电压稳定在电压vtx。

47.接下来,将参考图4至图7、结合与根据参考例的差分信号驱动电路的比较描述根据本实施例的差分信号驱动电路获得的有利效果。

48.图4中所示的根据第一参考例的差分信号驱动电路与根据本实施例的差分信号驱动电路的不同在于单独的电路单元20的n沟道mos晶体管sf1的源极和差分发送器tx的电源电压端子的连接节点没有连接到节点n1。即,在根据第一参考例的差分信号驱动电路中,n沟道mos晶体管sf1的源极的电压vddtx1是供给到差分发送器tx的电源电压端子的电压。

49.在根据第一参考例的差分信号驱动电路中,电路被设计为使得n沟道mos晶体管sf0的源极的电压vddtx和n沟道mos晶体管sf1的源极的电压vddtx1在差分发送器tx正在操作时相同。

50.电压vddtx和电压vddtx1相同的条件由下面的式子(2)和式子(3)表达。

51.r0=k

×

(r1 rt r2)...(2)

52.w0/l0=w1/(k

×

l1)...(3)

53.式子(2)是表达差分发送器tx的电阻r1、电阻r2和终端电阻rt之和与负载电阻r0之间的关系的式子。式子(3)是表达n沟道mos晶体管sf0的栅极宽度w0和栅极长度l0之比(w0/l0)与n沟道mos晶体管sf1的栅极宽度w1和栅极长度l1之比(w1/l1)之间的关系的式子。在式子(2)和式子(3)中,k是常数。当式子(2)和式子(3)两者都满足时,n沟道mos晶体管sf0的源极的电压vddtx和n沟道mos晶体管sf1的源极的电压vddtx1相同。

54.在根据第一参考例的差分信号驱动电路中,将参考图5描述当差分发送器tx从非操作状态转变到操作状态时的操作。注意的是,在图5中,差分发送器tx的电路符号由虚线表示,以便视觉地表达差分发送器tx处于非操作状态和从电源电压端子流到基准电压端子的电流的路径断开的开路状态。

55.在根据第一参考例的差分信号驱动电路中,当差分发送器tx处于非操作状态时,如图5中所示,单独的电路单元20的n沟道mos晶体管sf1的源极处于开路状态。因此,在n沟道mos晶体管sf1中没有电流流动,并且n沟道mos晶体管sf1的源极的电压vddtx1高于差分发送器tx正在操作时的电压。即,各个点的电压满足下面的式子(4)中所示的关系。

56.vddtx1>vddtx=vtx...(4)

57.因此,当差分发送器tx从这个状态转变到操作状态时,紧接在转变之后供给到差分发送器tx的电源电压端子的电压变得高于电压vtx。作为结果,例如如图6中所示,从差分发送器tx输出的输出数据的高电平高于期望的电压。

58.当输出数据的信号电平高于期望的电压时,可能超过接收数据的接收器的额定电压,并且在最坏的情况下,接收器可能发生故障。例如,当连接到单独的电路单元20的n沟道mos晶体管sf1的漏极的电源的电压vdd和电压vddrec满足下面的式子(5)时,很可能超过接收器的最大额定值,其中电压vddrec表示接收器的电源电压。

59.vdd>vddrec...(5)

60.在这个方面,在根据本实施例的差分信号驱动电路中,供给到差分发送器tx的电压vddtx_i始终是电压vtx,并且从差分发送器tx输出的输出数据的信号电平可以始终控制在期望的电压范围内。因此,从差分发送器tx输出的输出数据的信号电平不会超过接收器的额定电压,并且可以防止由于从差分发送器tx输出的数据信号而导致的接收器故障。

61.图7中所示的根据第二参考例的差分信号驱动电路是在电源电压生成单元30中生成电压vddtx并且这个电压vddtx作为电源电压(电压vddtx_i)被供给到各个通道上的差分发送器tx1和tx2的示例。在图7中,假定靠近电源电压生成单元30的差分发送器tx1和远离电源电压生成单元30的差分发送器tx2。此外,这里假定连接在电源电压生成单元30和差分发送器tx1之间的电源互连的互连电阻是rp并且连接在电源电压生成单元30和差分发送器tx2之间的电源互连的互连电阻是2rp。

62.电源电压生成单元30包括差分放大器电路32、n沟道mos晶体管sf3和负载电阻器r3。差分放大器电路32具有两个输入端子(非反转输入端子( )和反转输入端子(-))以及输出端子。电压vtx被供给到差分放大器电路32的非反转输入端子。差分放大器电路32的输出端子连接到n沟道mos晶体管sf3的栅极。n沟道mos晶体管sf3具有连接到电源电压节点(电

压vdd)的漏极,并且形成源极跟随器电路。n沟道mos晶体管sf3的源极连接到负载电阻器r3的一个端子和差分放大器电路32的反转输入端子。负载电阻器r3的另一个端子连接到基准电压节点(gnd节点)。

63.在本文中,出于说明的目的,n沟道mos晶体管sf3的源极、负载电阻器r3的一个端子、以及差分放大器电路32的反转输入端子的连接节点被称为节点n3。此外,连接到gnd节点的负载电阻器r3的另一个端子被称为节点n4。节点n3的电压vddtx与公共的电路单元10的节点n1一样与电压vtx相同。电源电压和基准电压分别经由互连从节点n3和节点n4供给到各个通道上的差分发送器tx1和tx2。

64.当每个通道上的差分发送器tx1和tx2正在操作时,电流总是从电源电压端子流到基准电压端子。在图2中所示的差分发送器tx的电路示例中,从电源电压端子流到基准电压端子的电流itx被表达为下面的式子(6)。

65.itx=vddtx_i/(r1 rt r2)...(6)

66.此外,从电源电压生成单元30供给到差分发送器tx1和tx2的电源电压因电源电压生成单元30与差分发送器tx1和tx2之间的互连电阻而减小。即,从电源电压生成单元30供给到差分发送器tx1的电压vddtx_i被表达为下面的式子(7)。此外,从电源电压生成单元30供给到差分发送器tx2的电压vddtx_i被表达为下面的式子(8)。

67.vddtx_i=vddtx—rp

×

itx...(7)

68.vddtx_i=vddtx-2

×

rp

×

itx...(8)

69.如上所述,在根据第二参考例的差分信号驱动电路中,对于更远离电源电压生成单元30的差分发送器tx,供给到电源电压端子的电压将更低。此外,这同样适用于gnd节点侧的电压,并且对于更远离电源电压生成单元30的差分发送器tx,供给到基准电压端子的电压将更高。

70.因此,在根据第二参考例的差分信号驱动电路中,供给到差分发送器tx的电源电压根据通道而不同,因此从差分发送器tx输出的数据信号的幅度在通道之间将不同。

71.在这个方面,在根据本实施例的差分信号驱动电路中,如图1中所示,电压vddtx经由每个通道上的n沟道mos晶体管sf1从电源电压节点供给到差分发送器tx的电源电压端子。而且在这样的情况下,尽管由于电源电压互连的互连电阻而在供给到每个通道上的单独的电路单元20的电压vdd中发生电压降,但是电压降在形成源极跟随器电路的n沟道mos晶体管sf1的漏极处发生。当n沟道mos晶体管sf1正在饱和区域中操作时,由于漏极电压的变化对漏极电流的影响小,因此对供给到每个通道上的差分发送器tx的电压vddtx的影响小。因此,与根据第二参考例的差分信号驱动电路的情况相比,对从差分发送器tx输出的数据信号的幅度的影响可以减小得更小。根据本实施例的差分信号驱动电路中对gnd节点侧的电压的影响与根据第二参考例的差分信号驱动电路的情况相同。

72.注意的是,尽管在本实施例中公共的电路单元10的n沟道mos晶体管sf0的栅极和单独的电路单元20的n沟道mos晶体管sf1的栅极彼此直接连接,但是这些栅极不一定需要彼此直接连接。例如,如图8中所示,n沟道mos晶体管sf0的栅极和n沟道mos晶体管sf1的栅极可以经由栅极电阻器rg连接。此外,单独的电路单元20的一个n沟道mos晶体管sf1的栅极和单独的电路单元20的另一个n沟道mos晶体管sf1的栅极可以经由栅极电阻器rg连接。而且当以这样的方式配置差分信号驱动电路时,可以获得与本实施例中描述的相同的有利效

果。栅极电阻器rg可以通过布置电阻器元件来配置,或者可以通过局部减小互连的宽度以增加互连电阻来配置。

73.如上所述,根据本实施例,即使在差分信号驱动电路的操作状态被切换时也可以输出具有稳定幅度的信号。因此,可以提高从差分发送器输出的信号的质量。此外,可以防止接收来自差分发送器的信号的接收器的故障。

74.第二实施例

75.将参考图9描述根据本公开的第二实施例的光电转换设备。与根据第一实施例的差分信号驱动电路中的组件相同的组件被利用相同的符号标记,并且将省略或简化其描述。图9是图示根据本实施例的光电转换设备的总体配置的框图。

76.尽管没有特别限制,但是根据第一实施例的差分信号驱动电路100例如可以用作光电转换设备的输出电路单元。在本实施例中,将描述根据第一实施例的差分信号驱动电路应用到的光电转换设备的示例。

77.如图9中所示,根据本实施例的光电转换设备200包括像素区域110、垂直扫描电路120、ad转换电路单元130、存储器单元140、水平扫描电路150、计算单元160、信号处理电路170和差分信号驱动电路100。

78.在像素区域110中,提供以矩阵布置以便形成多个行和多个列的多个像素112。像素112中的每一个包括由诸如光电二极管的光电转换元件形成的光电转换单元并且具有输出根据入射光的光量的像素信号的功能。垂直扫描电路120是控制电路单元,当从像素区域110读出像素信号时,该控制电路单元经由提供在像素阵列的各行上的控制线向像素112供给用于驱动像素112的控制信号。

79.ad转换电路单元130包括与像素阵列的各列相关联地提供的多个列ad转换电路132。列ad转换电路132将从对应列上的像素112输出的模拟像素信号转换成数字数据。存储器单元140包括与像素阵列的各列相关联地提供的多个列存储器142。列存储器142存储由对应列上的列ad转换电路132转换的数字数据。水平扫描电路150顺次地选择各列上的列存储器142,并且将存储在选择的列存储器142中的数字数据输出到计算单元160。

80.计算单元160对从存储器单元140传送的数字数据执行预定的计算处理,例如放大处理、数字相关双采样(cds)处理等,并且将处理后的数字数据输出到信号处理电路170。信号处理电路170包括并串转换电路,将从计算单元160输出的并行数据转换成串行数据,并且将转换后的串行数据输出到差分信号驱动电路100。

81.差分信号驱动电路100是在第一实施例中描述的差分信号驱动电路100。差分信号驱动电路100将从信号处理电路170接收的串行数据转换成差分信号,并且将差分信号经由差分发送器tx输出到光电转换设备200的外部。注意的是,为了简化附图,在图9中仅图示了与形成差分信号驱动电路100的多个单独的电路单元20的一个通道对应的一个单独的电路单元20。电源电压通过单独的电路单元20供给到差分发送器tx。此外,供给到单独的电路单元20的n沟道mos晶体管的栅极和源极的电压由公共的电路单元10生成。

82.通过将第一实施例的差分信号驱动电路100应用到光电转换设备的信号输出单元,从差分发送器tx输出的信号可以被控制为始终在期望的范围内。因此,可以提高信号的质量,并且可以防止接收信号的接收器的破坏。此外,由于差分发送器tx的电源电压在芯片内部生成,因此在芯片外部不需要电源ic。因此,可以减少组件的数量,并且可以减少成本。

83.第三实施例

84.将参考图10描述根据本公开的第三实施例的成像系统。图10是图示根据本实施例的成像系统的总体配置的框图。

85.以上第二实施例中描述的光电转换设备200可以应用到各种成像系统。可应用的成像系统的示例可以包括数字静态相机、数字摄像机、监控相机、复印机、传真机、移动电话、车载相机、观测卫星等。此外,包括诸如透镜的光学系统和成像设备的相机模块也包括在成像系统中。图10图示了作为这些示例中的示例的数字静态相机的框图。

86.图10中作为示例图示的成像系统300包括成像设备301、将物体的光学图像捕获到成像设备301上的透镜302、用于改变通过透镜302的光量的光圈304、以及用于保护透镜302的屏障306。透镜302和光圈304形成将光会聚到成像设备301上的光学系统。成像设备301是在第二实施例中描述的光电转换设备200,并且将由透镜302捕获的光学图像转换成图像数据。

87.此外,成像系统300包括处理从成像设备301输出的输出信号的信号处理单元308。信号处理单元308从由成像设备301输出的数字信号生成图像数据。此外,根据需要,信号处理单元308执行执行各种校正或压缩以输出图像数据的操作。成像设备301可以具有生成在信号处理单元308中处理的数字信号的ad转换单元。ad转换单元可以在形成有成像设备301的光电转换单元的半导体层(半导体基板)中形成,或者可以在与形成有成像设备301的光电转换单元的半导体层不同的半导体基板上形成。此外,信号处理单元308可以在与成像设备301相同的半导体基板上形成。

88.此外,成像系统300包括用于在其中暂时存储图像数据的存储器单元310和用于与外部计算机等进行通信的外部接口单元(外部i/f单元)312。成像系统300还包括用于执行成像数据的存储或读出的诸如半导体存储器的存储介质314和用于对存储介质314执行存储或读出的存储介质控制接口单元(存储介质控制i/f单元)316。注意的是,存储介质314可以嵌入在成像系统300中或者可以是可移除的。

89.此外,成像系统300包括执行各种计算并且控制整个数字静态相机的总体控制/运算单元318以及向成像设备301和信号处理单元308输出各种定时信号的定时生成单元320。这里,定时信号等可以从外部输入,并且成像系统300可以至少具有成像设备301和处理从成像设备301输出的输出信号的信号处理单元308。

90.成像设备301将成像信号输出到信号处理单元308。信号处理单元308对从成像设备301输出的成像信号执行预定的信号处理并且输出图像数据。信号处理单元308使用成像信号以生成图像。

91.如上所述,根据本实施例,可以实现根据第二实施例的光电转换设备200应用到的成像系统。

92.第四实施例

93.将参考图11a和图11b描述根据本公开的第四实施例的成像系统和可移动体。图11a是图示根据本实施例的成像系统的配置的图。图11b是图示根据本实施例的可移动体的配置的图。

94.图11a图示了与车载相机相关的成像系统的示例。成像系统400包括成像设备410。成像设备410是以上第二实施例中描述的光电转换设备200。成像系统400包括对由成像设

备410获取的多个图像数据执行图像处理的图像处理单元412和从由成像系统400获取的多个图像数据计算视差(视差图像的相位差)的视差获取单元414。此外,成像系统400包括基于计算的视差计算与物体的距离的距离获取单元416和基于计算的距离确定是否存在碰撞可能性的碰撞确定单元418。这里,视差获取单元414和距离获取单元416是获取关于与物体的距离的距离信息的距离信息获取单元的示例。即,距离信息是关于视差、散焦量、与物体的距离等的信息。碰撞确定单元418可以使用任何距离信息以确定碰撞可能性。距离信息获取单元可以通过专门设计的硬件来实现,或者可以通过软件模块来实现。此外,距离信息获取单元可以通过现场可编程门阵列(fpga)、专用集成电路(asic)等来实现,或者可以通过其组合来实现。

95.成像系统400连接到车辆信息获取设备420,并且可以获取诸如车辆速度、偏航率、转向角等的车辆信息。此外,成像系统400连接到控制ecu 430,该控制ecu 430是基于碰撞确定单元418的确定结果输出用于使车辆生成制动力的控制信号的控制设备。此外,成像系统400还连接到警告设备440,该警告设备440基于碰撞确定单元418的确定结果向驾驶员发出警告。例如,当作为碰撞确定单元418的确定结果碰撞概率高时,控制ecu 430通过施加制动、推回加速器、抑制引擎功率等来执行车辆控制以避免碰撞或减少损坏。警告设备440通过发出诸如声音的警告、在汽车导航系统等的显示器上显示警告信息、向安全带或转向盘提供振动等来警告用户。

96.在本实施例中,通过使用成像系统400来捕获车辆周围的区域,例如前方区域或后方区域。图11b图示了捕获车辆的前方区域(捕获区域450)时的成像系统。车辆信息获取设备420向成像系统400或成像设备410发送指令。这样的配置可以进一步提高测距准确度。

97.尽管以上已描述了用于避免与另一个车辆的碰撞的控制的示例,但是该实施例可应用到跟随另一个车辆的自动驾驶控制、不驶出行车道的自动驾驶控制等。此外,成像系统不限于诸如本主题车辆的车辆,并且可以应用到例如诸如船、飞机或工业机器人的可移动体(移动装置)。此外,成像系统可以广泛地应用到利用物体识别的设备,诸如智能运输系统(its),而不限于可移动体。

98.修改的实施例

99.本公开不限于上述实施例,并且各种修改是可能的。例如,其中实施例中的任何一个的配置的一部分被添加到另一个实施例的示例、或者其中实施例中的任何一个的配置的一部分被利用另一个实施例的配置的一部分替换的示例也是本公开的实施例中的一个。

100.此外,供给到公共的电路单元10的差分放大器电路12的电源电压以及供给到公共的电路单元10的n沟道mos晶体管sf0和单独的电路单元20的n沟道mos晶体管sf1的电源电压可以相同或可以彼此不同。例如,供给到差分放大器电路12的电源电压可以被设置为比供给到n沟道mos晶体管sf0和sf1的电源电压高的电压。

101.此外,公共的电路单元10的差分放大器电路12的基准电压和差分发送器tx的基准电压可以相同或可以彼此不同。

102.此外,尽管在上述实施例中供给到公共的电路单元10的n沟道mos晶体管sf0的电源电压和供给到单独的电路单元20的n沟道mos晶体管sf1的电源电压两者是电压vdd,但是这些电源电压可以彼此不同。

103.此外,尽管在以上实施例中已图示了使用n沟道mos晶体管形成电源电路和差分发

送器的示例,但是可以使用p沟道mos晶体管形成电源电路或差分发送器。

104.此外,作为第一实施例的差分信号驱动电路可以应用到的光电转换设备的示例提供了以上第二实施例中所示的光电转换设备,并且这个差分信号驱动电路可以应用到的设备不限于图9中所示的配置。

105.此外,作为第二实施例的光电转换设备可以应用到的成像系统的示例提供了以上第三和第四实施例中所示的成像系统,并且光电转换设备可以应用到的成像系统不限于图10和图11a中所示的配置。

106.虽然已参考示例性实施例描述了本公开,但是要理解的是,本发明不限于所公开的示例性实施例。以下权利要求的范围要被赋予最广泛的解释,以便涵盖所有这样的修改以及等同的结构和功能。

107.本技术要求2019年10月30日提交的日本专利申请no.2019-197616的权益,该日本专利申请no.2019-197616特此通过引用整体并入本文。

108.[参考符号列表]

[0109]

10 公共的电路单元

[0110]

12 差分放大器电路

[0111]

20 单独的电路单元

[0112]

100 差分信号驱动电路

[0113]

r0 负载电阻器

[0114]

rt 终端电阻器

[0115]

rx 接收器

[0116]

sf0、sf1 n沟道mos晶体管

[0117]

tx、tx1、tx2 差分发送器。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。