1.本公开中呈现的实施例总体涉及光子器件,并且更具体地,涉及制造具有边缘耦合器的光子器件。

背景技术:

2.光子芯片可以包括光学接口以允许从光源(例如,激光器或光纤)接收光信号和/或将光信号发送到光纤或检测器。一些光子芯片包括设置在光子芯片顶部的光栅耦合器。然而,光栅耦合器对波长和偏振是敏感的并需要非常严格的工艺控制,这往往会增加光子芯片的成本和/或降低制造良率。其他光子芯片包括边缘耦合器,这些边缘耦合器可以设置在光子芯片的侧面并且更容易制造,并且相比于光栅耦合器可以提供不依赖波长的且改进的光学耦合。

附图说明

3.为了能够详细理解本公开的上述特征的方式,可以通过参考实施例来获得对上文简要概括的本公开的更具体的描述,其中的一些实施例在附图中示出。然而,应当注意,附图示出了典型的实施例并因此不应被视为限制性的;还涵盖其他等效的实施例。

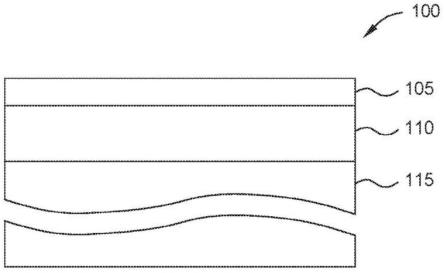

4.图1示出了根据一个或多个实施例的绝缘体上硅(soi)器件。

5.图2a和图2b示出了根据一个或多个实施例的包括与电子晶圆接合的光子晶圆的示例性晶圆组件。

6.图3a至图3i示出了根据一个或多个实施例的用于制造光学装置的示例性顺序。

7.图4是根据一个或多个实施例的用于制造光学装置的示例性方法。

8.图5示出了根据一个或多个实施例的包括边缘耦合器的光子芯片的侧视图。

9.图6a至图6e示出了根据一个或多个实施例的图5的边缘耦合器的截面图。

10.图7a和图7b示出了根据一个或多个实施例的锥形波导的视图。

11.为了便于理解,在可能的情况下,使用相同附图标记来表示附图共有的相同元件。可以设想,在一个实施例中公开的元件可有益地用在其他实施例中而无需具体阐述。

具体实施方式

12.概述

13.本公开中呈现的一个实施例是一种方法,所述方法包括:将光子晶圆与电子晶圆进行接合以形成晶圆组件;去除所述晶圆组件的衬底以暴露所述光子晶圆或所述电子晶圆的表面;在所述光子晶圆的金属层与所述电子晶圆的金属层之间形成电连接;以及通过在所暴露的表面处将中介层晶圆与所述晶圆组件进行接合,来将所述中介层晶圆添加至所述晶圆组件。所述中介层晶圆包括与所述光子晶圆和所述电子晶圆中的一者或两者的金属层电耦合的贯穿过孔。所述方法还包括切割所述晶圆组件以形成多个管芯,其中,每个管芯的相应边缘耦合器在通过所述切割形成的界面处被光学暴露。

14.另一实施例是一种方法,所述方法包括在光子晶圆中形成多个光学元件。所述多个光学元件包括多个边缘耦合器。所述方法还包括:在电子晶圆中形成多个电子元件;将所述光子晶圆与所述电子晶圆进行接合以形成晶圆组件;在所述多个光学元件与所述多个电子元件之间形成电连接;以及通过将中介层晶圆与所述晶圆组件的外表面进行接合,来将所述中介层晶圆添加至所述晶圆组件。所述中介层晶圆包括贯穿过孔,所述贯穿过孔与所述多个光学元件和所述多个电子元件中的一者或两者电耦合。所述方法还包括切割所述晶圆组件以形成多个管芯。每个管芯的相应边缘耦合器在通过所述切割形成的界面处被光学暴露。

15.另一实施例是一种用于形成多个管芯的晶圆组件。所述晶圆组件包括光子晶圆,所述光子晶圆包括多个光学元件。所述多个光学元件包括多个边缘耦合器,所述多个边缘耦合器被布置成使得所述多个管芯中的每个管芯的相应边缘耦合器将在切割界面处被光学暴露。所述晶圆组件还包括电子晶圆,所述电子晶圆具有与所述光子晶圆的第二表面接合的第一表面。所述电子晶圆包括多个电子元件,并且在所述多个光学元件与所述多个电子元件之间形成电连接。所述晶圆组件还包括与第三表面接合的中介层晶圆,所述第三表面是以下两者中的一者:所述电子晶圆的与所述第一表面相反的表面和所述光子晶圆的与所述第二表面相反的表面。所述晶圆组件还包括延伸穿过所述中介层晶圆的多个贯穿过孔。所述多个贯穿过孔与所述多个光学元件和所述多个电子元件中的一者或两者电耦合。

16.示例实施例

17.交换机和其他联网设备中包括的集成电路(ic)的处理能力和速度不断提高;因此,将大量数据移入和移出这些交换机和联网设备是一项重大挑战。非常需要光学输入/输出解决方案来克服这一挑战。硅光子是一种可用来解决这一问题的有发展前景的技术。通过使用硅光子平台来制造光学元件,可利用现有ic组装基础设施,这往往会降低制造成本并支持规模扩大。

18.在一些情况下,基于硅光子的光学元件的制造和/或封装与互补金属氧化物半导体(cmos)制造和/或封装技术保持兼容。一些非限制性示例包括表面安装技术,诸如受控塌陷芯片连接(也称为“c4”或“倒装芯片”)、球栅阵列(bga)等。此外,减少光学元件的整体封装面积可能是有益的,这可以支持高信号和功率完整性(例如,支持高速和高级调制技术,诸如112g pam4)并具有低功率要求和寄生效应。

19.本文描述的实施例包括制造光学装置的方法,所述方法允许以成本效益的方式实现用于高数据速率收发器模块和封装内光学应用的高速光学输入/输出。更具体地,制造方法包括光子晶圆与电子晶圆的晶圆级组装,从而降低下游制造工艺的成本、复杂性和周期时间,同时提高制造良率并支持高速/功率完整性操作。通过在晶圆级将光子晶圆与电子晶圆进行接合,消除了在下游制造工艺中单独封装电子ic和光子ic的需要。此外,在晶圆级将光子晶圆与电子晶圆进行接合有助于改善输入/输出耦合,减少寄生效应,并支持用于光学引擎与ic共同封装的小外形尺寸。

20.图1示出了根据一个或多个实施例的绝缘体上硅(soi)器件100。soi器件100包括表面层105、绝缘层110(也被称为掩埋氧化物(box)层)和半导体衬底115。尽管本文的实施例将表面层105和半导体衬底115称为硅,但本公开不限于此。例如,可以使用其他半导体或可选的透光材料来形成此处所示的结构。此外,表面层105与半导体衬底115可以由相同材

料制成,但在其他实施例中,表面层105与半导体衬底115由不同材料制成。

21.表面层105的厚度可以在小于100纳米至大于一微米的范围内。更具体地,表面层105的厚度可以在100纳米至300纳米之间。绝缘层110的厚度可取决于期望的应用而变化。在一个实施例中,绝缘层110的厚度可以在小于一微米至数十微米的范围内。半导体衬底115的厚度可以取决于soi器件100的具体应用而广泛变化。例如,半导体衬底115可以具有典型半导体晶圆的厚度(例如,100微米至700微米),或者可以被减薄并安装在另一衬底上。

22.对于光学应用,硅表面层105和绝缘层110(例如,二氧化硅、氮化硅、氮氧化硅等)可以提供将光信号限定在表面层105中的硅波导中的对比折射率。在后续处理步骤中,表面层105可以被蚀刻以形成一个或多个硅波导。由于与诸如二氧化硅之类的绝缘体相比,硅具有更高的折射率,因此光信号在其传播穿过表面层105时倾向于主要保留在硅波导中。此外,也可以在制造过程中沉积(一个或多个)其他层,诸如(一个或多个)氮化硅层,以用于形成附加光导波导层。

23.图2a和图2b示出了根据一个或多个实施例的包括与电子晶圆215接合的光子晶圆210的示例性晶圆组件200。更具体地,图2a是晶圆组件200的俯视图,并且图2b提供了晶圆组件200的透视图。光子晶圆210和电子晶圆215可以由任何(一种或多种)合适的半导体材料形成,这将在下面更详细地讨论。

24.如图所示,晶圆组件200包括多个矩形光子芯片205(例如,约10个至约200个光子芯片)。代替一次形成单个光子芯片205,晶圆组件200能够使用相同的制造步骤来并行地形成多个光子芯片205。晶圆组件200可以被切割以分离相邻的光子芯片205。在一些实施例中,用于切割晶圆组件200的切割工艺包括机械锯切、划线和劈开以及激光切割中的一种或多种。

25.在基于一个或多个soi器件的一些实施例中,每个光子芯片205包括图1所示的绝缘层110和半导体衬底115。然而,表面层105已被处理以包括各种光学元件(例如,波导、耦合器、调制器、检测器等)和/或电子元件。例如,可以通过对表面层105执行各种制造步骤(诸如蚀刻或掺杂表面层105的硅材料)以及沉积或生长附加材料来形成光学元件。在一些实施例中,光子晶圆210和电子晶圆215中的一者是使用soi器件来制造的。在其他实施例中,光子晶圆210和电子晶圆215两者都是使用soi器件来制造的。

26.在一些实施例中,相邻的光子芯片205各自包括在通过切割工艺形成的侧表面处光学暴露的相应边缘耦合器(未示出)。边缘耦合器可以被设计为高效地耦合至外部光承载介质。在一些实施例中,使用边缘耦合器可以减轻与穿过侧表面来发射光信号相关联的光损耗。

27.图3a至图3i示出了根据一个或多个实施例的用于制造光学装置的示例性顺序。更具体地,示意图300、326、330、334、344、360、366、374、384描绘了针对光学装置的不同制造阶段。尽管光学装置被描绘为单个光子芯片(例如,单个管芯),但应当理解,可以在晶圆级制造中并行地制造其他光子芯片。

28.在示意图300中,光子晶圆302(图2b的光子晶圆210的一个示例)与电子晶圆306(图2b的电子晶圆215的一个示例)彼此分离。在一些实施例中,光子晶圆302和电子晶圆306中的每一者均使用soi器件(例如,至少包括表面层105、绝缘层110和半导体衬底115)来形成。光子晶圆302包括一个或多个光学元件,而电子晶圆306包括一个或多个电子元件。光学

元件和/或电学元件可以部分地形成在表面层105和/或形成在表面层105上方的一个或多个层(例如,附加光波导层)中。

29.如图所示,光子晶圆302包括多个光学元件:边缘耦合器314-1、314-2、光学检测器316和光学调制器318。多个光学元件可以彼此光学耦合。例如,在操作期间,边缘耦合器314-1可以从外部光承载介质接收光信号,光检测器316检测光信号,光调制器318调制光信号,并且边缘耦合器314-2在外部耦合调制后的光信号(例如,通过光子芯片的边缘耦合到另一外部光承载介质)。在一些配置中,边缘耦合器314-1接收调制后的光信号,并且光检测器316检测调制后的光信号并将其转换成电信号。

30.光子晶圆302还包括顶表面310、多个金属层312-1、312-2、在金属层312-1、312-2之间延伸的过孔、以及在金属层312-2与表面层105或其他(一个或多个)半导体层之间延伸的过孔。光子晶圆302设置在衬底304(例如,半导体衬底115的一部分)上。

31.如图所示,电子晶圆306包括电子元件324。在一些实施例中,电子元件324包括晶体管或包括晶体管的其他电子电路。电子晶圆306还包括顶表面320、多个金属层322-1、322-2、322-3、322-4、在金属层322-1、322-2、322-3、322-4之间延伸的过孔、以及在金属层322-4与表面层105或其他(一个或多个)半导体层之间延伸的过孔。电子晶圆306设置在衬底308(例如,半导体衬底115的一部分)上。

32.在示意图326中,光子晶圆302被倒置(或翻转),并且光子晶圆302的顶表面310与电子晶圆306的顶表面320接触。可以执行接合工艺以在接合线328处将光子晶圆302与电子晶圆306进行接合,从而形成晶圆组件。在一些实施例中,将光子晶圆与电子晶圆接合通过晶圆级氧化物-氧化物接合来进行。可以设想其他合适类型的直接接合。在一些实施例中,接合工艺包括晶圆级混合接合,其中,氧化物-氧化物接合和金属互连在单个接合步骤中实现。例如,在顶表面310、320包括导电接合点阵列的情况下,可以使用直接接合互连(dbi)或面对面接合。

33.在图330中,从晶圆组件去除衬底以暴露光子晶圆302或电子晶圆306的表面。如图所示,去除衬底304以暴露光子晶圆302的表面332。在其他实施例中,可以去除衬底308以暴露电子晶圆306的表面。衬底304或308可以使用任何合适的技术(例如,使用光刻和化学蚀刻工艺)来去除。

34.在图334中,在表面332上方、向光子晶圆302添加附加氧化物或其他合适的电介质材料,并且在光子晶圆302中添加过孔,使得晶圆厚度增加了厚度336以延伸至表示晶圆组件的外表面的表面338。多个过孔340-1、340-2、

…

、340-6从表面338形成并部分或完全延伸穿过光子晶圆302和/或部分或完全穿过电子晶圆306。在一些实施例中,多个过孔340-1、340-2、

…

、340-6形成为贯穿氧化物过孔。多个导电接触件342-1、342-2、

…

、342-7形成在表面338处,并与过孔340-1、340-2、

…

、340-6中的相应一个或多个耦合。

35.过孔340-1、340-2、340-3、340-5从表面338延伸穿过光子晶圆302,并部分地延伸穿过电子晶圆306到达金属层322-1。过孔340-4、340-6部分地延伸穿过光子晶圆302到达金属层312-1。以这种方式,导电接触件342-1、342-2、342-3、342-6与电子晶圆306的电子元件电耦合,并且导电接触件342-3、342-7与光子晶圆302的光学元件电耦合。

36.在图344中,晶圆组件被倒置,并且光子晶圆302的表面338与中介层晶圆346的表面348接触。中介层晶圆346可以由任何合适的材料(诸如硅或玻璃)形成。可以执行接合工

艺以在接合线358处将晶圆组件与中介层晶圆346接合。在一些实施例中,通过晶圆级氧化物-氧化物接合来将晶圆组件与中介层晶圆346进行接合。还可以设想其他合适类型的直接接合(例如,晶圆级混合接合)。

37.中介层晶圆346包括多个贯穿过孔350-1、350-2、

…

、350-7,它们在表面348处形成的多个表面接触件352-1、352-2、

…

、352-7与在表面356处形成的多个表面接触件354-1、354-2、

…

、354-7之间延伸,其中表面356与表面348相反。

38.在图360中,焊球362-1、362-2、

…

、362-7附接至表面接触件354-1、354-2、

…

、354-7以形成与贯穿过孔350-1、350-2、

…

、350-7电耦合的表面安装连接器。表面安装连接器可以具有任何合适的形式,无论是标准化的还是专有的。例如,焊球362-1、362-2、

…

、362-7可以布置为球栅阵列(例如,具有0.4mm至0.65mm的间距)或倒装芯片凸块(例如,具有50微米至150微米的间距)。

39.在形成表面安装连接器之后,然后可以沿着线364-1、364-2切割晶圆组件以形成多个管芯。在一些实施例中,线364-1、364-2被选择为使得边缘耦合器314-1、314-2在通过切割形成的界面处被光学暴露。如本文所用,“光学暴露”是指边缘耦合器314-1、314-2在侧表面处被物理暴露或从侧表面略微凹陷(例如,1微米至5微米),但仍可以与外部光承载介质光学耦合。如图366所示,通过切割形成的界面是侧表面368-1、368-2。可以对界面执行进一步处理,例如蚀刻或抛光侧表面368-1、368-2,以实现边缘耦合器314-1、314-2与外部光承载介质的高光学耦合效率。

40.在图366中,多个电接触件380-1、380-2、

…

、380-7形成在集成电路(ic)衬底378或中介层的表面382上。第一管芯的表面安装连接器(例如,焊球362-1、362-2、

…

、362-7)与电接触件380-1、380-2、

…

、380-7电耦合。

41.在图374中,外部光承载介质372附接至第一管芯。在一些实施例中,外部光承载介质372包括以下各项中的一项:外部光子芯片的光波导、外部光子芯片的边缘耦合器、激光器、发光二极管、单根光纤以及对多根光纤进行布置的光纤阵列单元。在一些实施例中,如图所示,在将外部光承载介质372附接至第一管芯之前,将第一管芯与ic衬底378进行电耦合。这种排序可能适合于用于附接焊球362-1、362-2、

…

、362-7的回流温度高于用于附接外部光承载介质372的环氧树脂固化温度的情况。然而,在其他实施例中,外部光承载介质372附接至第一管芯在第一管芯与ic衬底378电耦合之前,这在对焊球362-1、362-2、

…

、362-7使用低温焊料或使用可承受更高温度的环氧树脂时可能是合适的。

42.外部光承载介质372与边缘耦合器314-1光学耦合。可以通过无源和/或有源对准技术来实现外部光承载介质372与边缘耦合器314-1的光学耦合。在一些实施例中,外部光承载介质372和/或第一管芯包括有助于对准的一个或多个对准特征。例如,一个或多个对准特征的尺寸可以被设计为使得当与第一管芯的参考表面或另一对准特征耦合时,外部光承载介质372与边缘耦合器314-1光学耦合。尽管示出两个边缘耦合器314-1、314-2,但其他实现方式可以包括不同数量的边缘耦合器。例如,光子晶圆302可以包括三个插脚耦合器(prong coupler):用于接收未调制的光的第一插脚耦合器、用于发送调制后的光(例如,在收发器的发送侧)的第二插脚耦合器以及用于接收调制后的光(用于检测)的第三插脚耦合器。此外,在一些实施例中,可以在光子晶圆302中形成输入和输出阵列(例如,使得边缘耦合器可以是光纤阵列单元(fau))。

43.在一些实施例中,在外部光承载介质372与边缘耦合器314-1光学耦合之后,在第一管芯的界面(此处为侧表面368-1)与外部光承载介质372之间施加折射率匹配材料370(例如,环氧树脂)。以这种方式,光信号可以穿过折射率匹配材料370传播。折射率匹配材料370可以被固化(例如,使用uv光或热)以将外部光承载介质372附接至第一管芯。在其他实施例中,外部光承载介质372可以在不使用用于光学耦合的折射率匹配材料370的情况下而附接至第一管芯(例如,使用插头或连接器可去除地附接)。

44.在图384中,将热界面材料386施加至衬底308的表面376(例如,第二衬底的包括在第一管芯中的部分)。热界面材料386的一些非限制性示例包括导热油脂、间隙填充剂(例如,弹性体片材)、绝缘硬件(例如,诸如氧化铝、氮化铝、氧化铍之类的陶瓷)、导热垫或薄膜(例如,硅胶或石墨)、导热胶带、相变材料、导热环氧树脂等。热盖388通过热界面材料386附接至第一管芯。如图所示,热盖388的表面390与热界面材料386接触。热盖388可以用作散热片或散热器。热盖388可以由任何(一种或多种)合适的材料(例如,铝、铜、碳基或石墨基复合材料等)形成。

45.图4是根据一个或多个实施例的用于制造光学装置的示例性方法400。方法400可以与其他实施例结合使用,例如,以执行图3a至图3i中描绘的序列。

46.方法400开始于框405,其中,在光子晶圆中形成多个光学元件。在一些实施例中,光子晶圆用于制造多个管芯,并且每个管芯包括相应的一个或多个光学元件。在一些实施例中,多个光学元件部分地形成在soi衬底的表面层中。

47.在框410处,在电子晶圆中形成多个电子元件。在一些实施例中,电子晶圆用于制造多个管芯,并且每个管芯包括相应的一个或多个电子元件。在一些实施例中,多个电子元件部分地形成在soi衬底的表面层中。

48.在框415处,将光子晶圆与电子晶圆进行接合。将光子晶圆与电子晶圆接合形成晶圆组件。在一些实施例中,将光子晶圆与电子晶圆接合包括晶圆级氧化物-氧化物接合。在框420处,去除晶圆组件的衬底以暴露光子晶圆或电子晶圆的表面。在一些实施例中,晶圆组件的衬底包括soi衬底的半导体衬底。在一些实施例中,去除衬底包括执行光刻和化学蚀刻工艺。

49.在框425处,从晶圆组件的外表面形成过孔。在一些实施例中,过孔延伸至光子晶圆的金属层和电子晶圆的金属层。在一些实施例中,光子晶圆或电子晶圆从所暴露的表面生长,并增加一定厚度以限定外表面。

50.在框430处,中介层晶圆在表面处与晶圆组件接合。以这种方式,将中介层晶圆添加至晶圆组件中。在一些实施例中,将中介层晶圆与晶圆组件接合包括晶圆级氧化物-氧化物接合。在一些实施例中,中介层晶圆包括与过孔电耦合的贯穿过孔。在框435处,在晶圆组件上形成表面安装连接器。在一些实施例中,焊球可以附接至中介层晶圆的表面接触件。

51.在框440处,切割晶圆组件以形成多个管芯。在一些实施例中,切割晶圆组件包括机械锯切、划线和劈开以及激光切割中的一种或多种。还可以设想其他合适的切割技术。在一些实施例中,每个管芯的相应边缘耦合器在通过切割晶圆组件形成的界面处被光学暴露。

52.在框445处,将第一管芯的表面安装连接器与集成电路衬底的电接触件进行电耦合。在框450处,将外部光承载介质附接至第一管芯。在一些实施例中,以相反次序来执行框

445、450。在一些实施例中,外部光承载介质包括以下各项中的一项:外部光子芯片的光波导、外部光子芯片的边缘耦合器、激光器、发光二极管、单根光纤以及对多根光纤进行布置的光纤阵列单元。

53.在一些实施例中,附接外部光承载介质包括将外部光承载介质与第一管芯的边缘耦合器进行光学耦合。可以通过无源和/或有源对准技术来实现将外部光承载介质与边缘耦合器光学耦合。在一些实施例中,附接外部光承载介质包括在第一管芯的界面与外部光承载介质之间施加折射率匹配材料(例如,环氧树脂)。折射率匹配材料可以被固化(例如,使用uv光或热)以将外部光承载介质附接至第一管芯。

54.在框455处,将热界面材料施加至衬底的表面。在框460处,将热盖(例如,散热片或散热器)附接至第一管芯,使得热盖的表面与热界面材料接触。方法400在完成框460之后结束。

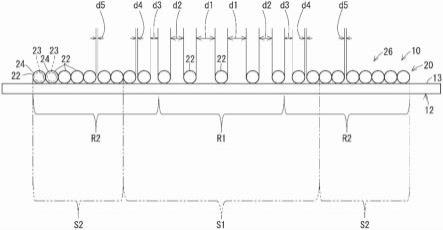

55.图5示出了光子芯片的侧视图500,所述光子芯片包括使用多插脚嵌入式结构形成的边缘耦合器520。侧视图500所示的特征可以与其他实施例结合使用。例如,边缘耦合器520表示图3a至图3i的边缘耦合器314-1、314-2的一种可能实现方式。

56.在侧视图500中,光波导505(例如,硅波导)形成在边缘耦合器520上方(例如,边缘耦合器520可以嵌入在光子芯片的绝缘层中,诸如氧化物层中)。光波导505在光子芯片的一个或多个光学元件(未示出)与边缘耦合器520之间耦合光信号。在另一实施例中,多插脚结构可以相对于光波导505被翻转,使得边缘耦合器520的插脚被形成在光波导505上方的层中(即,光波导505位于边缘耦合器520的插脚与绝缘层之间)。

57.如侧视图500所示,边缘耦合器520的一个界面耦合至光波导505,而另一界面在光子芯片的侧表面525处被光学暴露。在一些实施例中,通过对图3f中描绘的晶圆组件执行切割工艺来形成侧表面525。在一些情况下,侧表面525可以进行进一步处理(例如,抛光)以提高与外部光承载介质的光学耦合效率。

58.边缘耦合器520包括波导适配器515,该波导适配器515可以与外部光承载介质(例如,fau的光纤)光学耦合。边缘耦合器520由可以包括嵌入在绝缘材料(例如,二氧化硅或氮氧化硅)中的相同材料(例如,氮化硅或氮氧化硅)的单独插脚510a、510b、510c制成。以这种方式,单独插脚510a、510b、510c设置在不同层上,并且不同层中的每一层被电介质材料(例如,氧化物层)分离。在一个实施例中,插脚510a、510b、510c和边缘耦合器520的材料可能不同于光子芯片的绝缘层的材料。通常,边缘耦合器520可以由具有比围绕插脚510a、510b、510c的绝缘材料的材料更高的折射率的任何(一种或多种)材料来制成。

59.图6a至图6e示出了根据一个或多个实施例的图5的边缘耦合器520的截面图。具体地,图6a示出了波导适配器515的最靠近侧表面525(或耦合界面)的部分的截面a-a。本文中,波导适配器515包括四个单独插脚510a、510b、510c、510d,它们可以具有相同或相似的宽度(w)和高度(h)(或厚度)尺寸。这些尺寸以及插脚510a、510b、510c、510d之间的间距可以取决于具体应用而变化。在所示示例中,波导适配器515可以被配置为与具有10微米模场直径的单模光纤接口连接。如本领域普通技术人员将理解的,这些尺寸可取决于具体应用而变化。具体地,尺寸可以选择为使得耦合界面处的插脚的模与光要耦合至或从其耦合的外部器件的模基本上匹配。如本文所述,“基本上匹配”包括模大小相等的情况,以及模大小在彼此的约25%以内的情况。本文中,插脚510a、510b、510c、510d的宽度可以在约200纳米

至300纳米的范围内,高度在约100纳米至250纳米之间。更具体地,宽度可以是约200纳米,而高度是约200纳米。插脚510a与插脚510c之间的距离以及插脚510d与插脚510b之间的距离可以是约两微米。如上所述,插脚510a、510b、510c、510d的尺寸以及间距可以根据耦合至光子芯片的外部光源的模或设计而变化。

60.图6b示出了波导适配器515的截面b-b。此图示出,随着多插脚适配器远离侧表面525凹陷时,插脚510b、510c、510d的宽度减小,而插脚510a的宽度增加。如图所示,以绝热方式使插脚510a、510b、510c、510d的宽度逐渐变细。逐渐变细导致光能从由位于波导适配器515右侧的插脚510a、510b、510c、510d限定的光学模逐渐转变,其中,插脚510a、510b、510c、510d的宽度和高度与在波导适配器515中更靠左的位置处逐渐越来越多地限定在上插脚510a中的模相同或相似。这种逐渐变细将由插脚510a、510b、510c、510d限定的光能单独传递至插脚510a。然而,反之亦然。也就是说,随着光信号从左向右传播,使宽度逐渐变细还使得在上插脚510a中引入的信号能够传递至由插脚510a、510b、510c、510d限定的模。插脚510a、510b、510c、510d的宽度可连续变化(例如,以线性或非线性方式,诸如指数地或以更高阶多项式型线),或在替代实施例中,如波导适配器515从右向左延伸那样以离散增量变化。如图5所示,最终,插脚510b、510c、510d终止(其终止波导适配器515),而插脚510a继续传输光信号。在一个实施例中,波导适配器515可以具有约100微米至500微米的长度。此外,波导适配器515可针对所有此长度或仅针对其一部分逐渐变细。例如,在插脚510a、510b、510c、510d的宽度开始改变之前,插脚510a、510b、510c、510d的宽度对于前5微米至50微米可以保持基本上相等。

61.图6c示出了边缘耦合器520的截面c-c。在此,波导适配器515已终止,留下插脚510a来承载光信号。尽管示出为线性的,但插脚510a可弯曲、变弯、扭曲等以将光信号承载至光子芯片或测试结构的不同区域。因此,插脚510a的长度可以远大于插脚510b、510c、510d的长度以使插脚510a能够将光信号承载至不同区域。

62.图6d示出了边缘耦合器520和光波导505的截面d-d。如图所示,插脚510a的宽度大于光波导505的宽度。此外,取决于用于制造晶圆的技术,插脚510a与光波导505之间的距离可以在数百纳米到仅几纳米之间的范围内。取决于用于制造半导体晶圆的技术,插脚510a的一部分可直接接触光波导505。

63.图6e示出了边缘耦合器520和光波导505的截面e-e。本文中,插脚510a的宽度已缩小,而光波导505的宽度已增大。再次以绝热方式示出的这种逐渐变细导致插脚510a中的光信号以最小的损耗传递至光波导505,并且反之亦然。最终,插脚510a终止并且光波导505可以将光信号承载至不同光学元件,例如光子芯片中。

64.尽管上述实施例讨论了通过改变宽度而使得插脚510a、510b、510c、510d逐渐变细,但如果高度变细或两者的某种组合,则可能发生光功率的类似传递。然而,使插脚510a、510b、510c、510d的高度逐渐变细可能需要与如图6a至图6e所示的使宽度逐渐变细不同的光刻和制造技术或材料。也不必使所有插脚的宽度都逐渐变细。例如,在一些设计中,期望的光能传递可以通过仅使插脚510a的宽度逐渐变细而不必使插脚510b、510c、510d的宽度逐渐变细来获得。

65.图7a和图7b示出了根据一个或多个实施例的锥形波导的视图。更具体地,图7a和图7b示出了用于在波导之间传递光信号的部分重叠的倒锥形波导结构。如图所示,图7示出

了与第二锥形波导710部分重叠的第一锥形波导705的平面图。具体地,图7a可以是图5中光子芯片的一部分的布置,其中,光波导505与插脚510a重叠。波导的逐渐变细是以绝热方式完成的,以最小化光损耗。尽管图7a和图7b示出了锥形的宽度线性变化,但只要满足绝热标准,波导也可以以非线性方式逐渐变细,例如以指数或某一高阶多项式型线。在一个实施例中,第一锥形波导705与第二锥形波导710之间的距离小于一微米。例如,第一锥形波导705与第二锥形波导710可以分离100纳米或更小。分离距离会影响光信号在第一锥形波导705与第二锥形波导710之间传递的效率,因此,结构可以设计为使得第一锥形波导705与第二锥形波导710在制造技术允许的情况下尽可能接近。

66.图7b示出了第一锥形波导705和第二锥形波导710的俯视图。通过使第一锥形波导705与第二锥形波导710至少部分地重叠,可以在半导体晶圆的不同层中的波导之间传送光信号。在一个实施例中,第一锥形波导705和第二锥形波导710在它们的相应端开始逐渐变细的地方部分重叠。锥形的斜率或变化可取决于用于形成第一锥形波导705和第二锥形波导710的材料。在一个实施例中,在最宽点处,第一锥形波导705和第二锥形波导710可以具有范围介于200纳米至2微米之间的宽度。在最窄点处,第一锥形波导705和第二锥形波导710可以具有从100纳米至200纳米的宽度。锥形部分的长度可以在10微米至50微米之间的范围内,例如,为约20微米。

67.在上文中,参考了本公开中呈现的实施例。然而,本公开的范围不限于具体描述的实施例。相反,无论是否涉及不同的实施例,都涵盖所描述的特征与元件的任何组合以实现和实践所涵盖的实施例。此外,尽管本文公开的实施例可以实现优于其他可能的解决方案或现有技术的优势,但给定实施例是否实现特定优势并不会限制本公开的范围。因此,除非在(一个或多个)权利要求中明确记载,否则前述各个方面、特征、实施例和优点仅仅是说明性的并且不被认为是所附权利要求的要素或限制。

68.参考根据本公开中呈现的实施例的方法、装置(系统)和计算机程序产品的流程图和/或框图来描述本公开的各方面。应当理解,可以由计算机程序指令来实施流程图图示和/或框图的每个框以及流程图图示和/或框图中的各个框的组合。这些计算机程序指令可以提供给通用计算机、专用计算机或其他可编程数据处理装置的处理器以产生机器,使得经由计算机或其他可编程数据处理装置的处理器执行的指令创建用于实现流程图和/或框图的一个或多个框中指定的功能/动作的方式。

69.这些计算机程序指令也可以存储在计算机可读介质中,所述计算机可读介质可以指示计算机、其他可编程数据处理装置或其他设备以特定方式起作用,使得存储在计算机可读介质中的指令产生制品,所述制品包括实现流程图和/或框图的一个或多个框中指定的功能/动作的指令。

70.计算机程序指令还可以被加载到计算机、其他可编程数据处理装置或其他设备上,以使得在计算机、其他可编程装置或其他设备上执行一系列操作步骤,以产生计算机实现的过程,使得在计算机或其他可编程装置上执行的指令提供用于实现在流程图和/或框图的一个或多个框中指定的功能/动作的过程。

71.图中的流程图和框图示出了根据各种实施例的系统、方法和计算机程序产品的可能实现方式的架构、功能性和操作。在这方面,流程图或框图中的每个框可以表示代码的模块、段或部分,包括用于实现指定的(一个或多个)逻辑功能的一个或多个可执行指令。还应

注意,在一些替代实现方式中,框中提及的功能可以不按图中指出的次序出现。例如,连续示出的两个框实际上可以基本上同时执行,或者这些框有时可以以相反次序执行,这取决于所涉及的功能性。还将注意,框图和/或流程图图示中的每个框以及框图和/或流程图图示中的框的组合可以由执行指定功能或动作的基于专用硬件的系统或通过专用硬件和计算机指令的组合来实现。

72.鉴于前述内容,本公开的范围由所附权利要求决定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。