制造半导体结构

背景技术:

1.在某些光子集成电路(pic)中,使半导体材料的膜由介电材料(诸如空气或聚合物材料)界限存在益处。通常,此类结构通过以下步骤制造:在基材的整个表面区域之上沉积第一半导体材料层,在第一材料层的整个表面区域之上沉积第二半导体材料层,向第二材料层的一个或多个部分施加光罩材料及蚀刻该层以暴露该第一材料层的一个或多个部分。然后,施加蚀刻制程,其中使蚀刻剂材料穿过到达第一半导体材料层的暴露部分以对其进行蚀刻。此种过程是有问题的,因为它需要仔细控制将蚀刻剂材料施加到第一材料层以便提供所需尺寸的时间。此外,在一些情况下,可能无法非对称地蚀刻材料。

2.期望提供制造半导体结构的更可靠方法。

附图说明

3.图1是示出根据实施方式的制造半导体结构的方法的流程图;且

4.图2a至图2g是根据实施方式的在制造的各个阶段期间半导体结构的一系列剖面图。

具体实施方式

5.本文描述的实施方式涉及制造半导体结构的方法。具体地,但非排他地,涉及制造半导体材料的膜以供在光子集成电路(pic)中使用。

6.如下文(例如)将参考块110详细说明,可通过蚀刻产生形状和尺寸更精确的空腔。这使得用于pic的半导体结构具有更多的设计自由度和复杂性。

7.图1是以一般方式示出根据实施方式的制造半导体结构的方法100的流程图。

8.在块102处,沉积第一层,使其与基材的第一表面区域接触。基材具有第一半导体材料,且第一层具有第二半导体材料。

9.在块104处,沉积第二层,使其与基材的第二表面区域接触。第二表面区域基本上与第一表面区域共面且在第一表面区域之外。第二层具有第一半导体材料或与第一半导体材料不同的第三半导体材料。第一表面区域可另外称为内表面区域,且第二表面区域可另外称为外表面区域。

10.通过认为基本上共面,例如沉积第二表面层,使其与基材的第一层沉积在其上的区域连续的区域接触。因此,第一表面区域和第二表面区域可在可接受的制造公差内彼此处于同一平面中,该制造公差可通过单独地沉积第一层及第二层而发生。

11.在一些实施方式中,第一层基本上跨基材的整个表面区域(例如,除基材的被在其中制造半导体的反应器的晶圆夹具夹紧的区域之外)沉积。在此类实施方式中,然后在沉积第二层之前,通过移除第一层的在第一表面区域之外的外部分来暴露第二表面区域。例如,通过蚀刻制程移除该外部分,该蚀刻制程可以是干式蚀刻制程或湿式蚀刻制程或湿式蚀刻制程与干式蚀刻制程的组合。在其他实施方式中,第一层沉积在第一表面区域上,而不是也沉积在第二表面区域上(例如使用光罩)。

12.沉积第一层使其具有第一厚度,且沉积第二层使其具有基本上等于第一厚度的第二厚度。以此方式,预期第二层的上表面与第一层的上表面连续(在可接受的制造公差内)。这提供连续的(例如,平坦或平面的)或接近连续的表面,在该表面上沉积另外的层,诸如下文参考块106描述的第三层。可设想每个沉积制程受到制造公差的影响,且所产生的上表面可能不是完全连续的(例如,不能一起形成恰好平坦的表面或彼此位于同一平面内)。

13.在块106处,沉积第三层,使其与第一层及第二层接触。第三层具有第一半导体材料或者作为替代可具有不同于第一半导体材料的第三半导体材料或第四半导体材料。例如,第三材料及第四材料中的每一者具有砷化镓(gaas)、氮化镓(gan)或锑化镓(gasb),且例如基材202具有砷化镓(gaas)、氮化镓(gan)或锑化镓(gasb)。

14.如上所述,可设想第一层及第二层的上表面在制造公差内基本上连续。通过在基本上连续的表面上沉积第三层,第三层的上表面也基本上是连续的(在同一公差内),以便例如提供合适地平坦或平面表面。

15.在块108处,移除第三层的一部分以暴露第一层的一部分。

16.在一些实施方式中,移除第三层的一部分包括使用光罩选择性地蚀刻第三层的一部分。此类选择性蚀刻可包含干式蚀刻制程,该干式蚀刻制程借助于蚀刻制程的物理方式而具有选择性(例如,借助于对第三层的电压感应的物理影响而具有选择性),或者可以是湿式蚀刻制程,该湿式蚀刻制程借助于相对于另一种材料而与一种材料组合的化学偏好而具有选择性(且因此选择性地蚀刻该种材料)。

17.在块110处,移除第一层的至少一部分以在基材、第二层与第三层之间产生空腔。

18.在实施方式中,移除第一层的至少一部分包含施加蚀刻剂,该蚀刻剂相对于第一半导体材料优先地蚀刻第二半导体材料。因为第一层由被蚀刻剂蚀刻(如果发生的话)的材料包围(由基材、第二层及第三层包围),其蚀刻速率比第一层被蚀刻剂蚀刻的速率低得多,所以周围的层提供所谓的「终止蚀刻」,该终止蚀刻使得蚀刻制程能够在无需严格控制蚀刻制程进行的时间的情况下进行。作为替代,包围第一层的材料的材料性质提供防止对周围材料的任何或任何显著的过度蚀刻的物理边界。也就是说,不意图被蚀刻的材料不会被蚀刻剂蚀刻到妨碍所产生结构的性能的程度。因此,通过移除第一层的至少一部分产生的空腔的侧面可对应于第二层的侧面(例如由第二层的侧面界限)。由于部分蚀刻到第二层中,空腔的这一侧可具有基本上平面表面,而不是弯曲形状。因此,可产生形状和尺寸更精确的空腔。对已知技术的此类额外控制使半导体结构具有更多的设计自由度和复杂性。

19.在一些实施方式中,空腔是在第一方向(垂直于基材平面的方向)上位于第三层与基材之间及在第二方向(垂直于第一方向且平行于基材平面的方向)上位于第二层的外部分之间的例如填充有空气的间隙或空间。因此,空腔的侧面与基材的表面(例如,第一表面区域)、第二层的至少一个内表面及第三层的表面对应(例如,由此等表面界限)。在实施方式中,空腔随后至少部分地填充有除空气之外的材料,例如介电材料。对于上下文,上文参考图1描述的方法是参考pic描述的。pic是将两个或更多个光子设备(例如,使用光执行功能的设备)集成在一起的光电路。pic可包括执行功能的部件,这些功能包括例如:发射光;检测光;放大光;引导光;反射光;衍射光;混合不同波长的光;分离不同波长的光;极化转换;光学滤波;功率分裂;调幅;及调相。pic可被视为电子电路的光学模拟。

20.在一些实施方式中,第三层用作膜。此种膜可以是「主动的」,因为它包含可对穿过

膜的光提供放大的增益材料(例如,膜激光器),或者是被动的,因为它是光学透明的或吸收穿过膜的光。

21.用于pic的商业上常用的材料平台系磷化铟(inp),其允许在同一芯片上集成光学主动及被动功能;然而,其他材料平台(诸如硅(si)、砷化镓(gaas)或铌酸锂(linbo3))可用作用于pic的平台。

22.pic的示例包含集成在单一芯片中的数百个部件。

23.现在使用图2a至图2g来详细解释上文笼统描述的实施方式,图2a至图2g是以剖面图展示在制造制程(诸如上文参考图1描述的方法100)期间半导体结构200的形成的一系列图。

24.图2a展示包含基材202的第一半导体结构200a,该基材202通常是另外的磊晶层生长或另外沉积在其上的半导体晶圆。在本文描述的实施方式中,基材202是基本上纯磷化铟(inp)基材。也就是说基材202主要包含inp。基材202可以是纯inp(在可接受的纯度公差内),或者可包含其他材料(诸如掺杂剂或杂质),其中该材料包含至少99%的inp。例如,基材202掺杂有掺杂剂材料使得基材可被视为n型掺杂的,或者基材202掺杂有掺杂剂材料使得基材202可被视为p型掺杂的,或者基材202掺杂有掺杂剂材料使得基材202可被视为半绝缘的。

25.在其他实施方式中,基材202具有另一种半导体材料。例如,基材202具有砷化镓(gaas)、氮化镓(gan)或锑化镓(gasb)。

26.在基材202的第一表面(在下文称为基材202的上表面)上,沉积半导体材料的第一层204。第一层204具有与基材202的材料不同的材料。例如,在基材202包含inp的情况下,第一层204是不包含inp的半导体材料。例如,第一层204是包含inp及其他二元半导体材料(诸如砷化镓(gaas)、砷化铟(inas)、砷化铝(alas)及磷化镓(gap))的三元或四元合金。

27.在图2a所示的状态中,将第一光罩206施加到第一层204的上表面。光罩206是被布置成抵抗蚀刻的蚀刻光罩。第一光罩206被图案化以暴露第一层204的部分。当将蚀刻剂施加到第一层204时,相对于第一光罩206,蚀刻剂优先地移除第一层204;也就是说蚀刻剂在它与之进行化学或物理相互作用以移除材料的材料方面具有选择性,使得第一层204被蚀刻剂移除的速率超过第一光罩206被蚀刻剂移除的速率。对于给定的蚀刻剂,第一层204的蚀刻速率与第一光罩206的蚀刻速率的比称为选择性。

28.图2b展示在施加蚀刻制程以移除第一层204的在基材202的第一表面区域202b之上的部分之后的第二半导体结构200b。

29.用于移除第一层204的蚀刻制程可以是湿式蚀刻(例如,通过将第一半导体结构200a浸入液体化学蚀刻剂中)或干式蚀刻(例如,通过将第一半导体结构200a的上表面暴露于电浆或溅镀制程)或湿式蚀刻与干式蚀刻的组合。

30.在移除第一层204的在基材202的第二表面区域202b之上的部分之后,执行另外的沉积制程(有时称为再生长制程)以沉积半导体材料的第二层208,使其与基材202的第二表面区域202b接触,如图2c所示。第二层208沉积在与基材202的第一表面区域202a共面且在该第一表面区域202a之外的第二表面区域202b上。也就是说,第一层204及第二层208的厚度基本上相等,使得该等层的上表面大致齐平。类似于上文参考图1给出的解释,即第一层204及第二层208的厚度基本上相等,使得这些层的上表面大致齐平意思是例如在上文指定

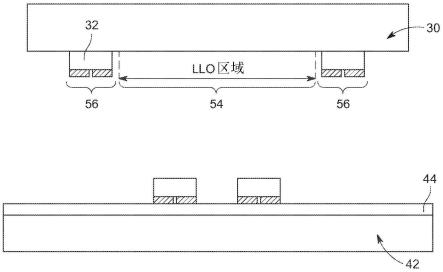

的制造公差内,第一层及第二层的各别厚度相等,且因此在那些相同制造公差内,上表面彼此齐平或成一直线。

31.如图2c所示,第二层208形成在第一层204与第二层208之间包括所谓的「对接接头」,使得第二层208邻接第一层204的第三半导体结构200c。

32.在此实施方式中,第二层208包含与基材202相同的材料。在一些实施方式中,第二层208是基本上纯磷化铟(inp)基材。也就是说基材202主要包含inp。基材202可以是纯inp的,或者可包含其他材料诸如掺杂剂或杂质。例如,基材202掺杂有掺杂剂材料使得基材可被视为n型掺杂的,或者基材202掺杂有掺杂剂材料使得基材202可被视为p型掺杂的。

33.在形成第二层208之后,移除第一光罩206。然后沉积第三层210使其与第一层204及第二层208接触,如图2d所示,图2d展示第四半导体结构200d。第三层210具有第一半导体材料。例如,第三层可包含inp且可包含与基材202及第二层208相同的材料。

34.在形成第三层210之后,在第三层210上限定第二光罩212以形成如图2e所示的第五半导体结构200e。第二光罩212包含一个或多个开口214。开口214为蚀刻剂材料通过提供路径。

35.在第一蚀刻制程(其可以是湿式蚀刻制程或干式蚀刻制程)中,将蚀刻剂施加到第三层210的通过第二光罩212中的开口214暴露的部分。所产生的第六半导体结构200f如图2f所示。

36.在第二蚀刻制程中,将蚀刻剂施加到第一层204。蚀刻剂经由开口214及通过第一蚀刻制程在第三层210中形成的对应的开口214进入第一层204。

37.第二蚀刻剂制程施加蚀刻剂,该蚀刻剂相对于基材202及第二层208优先地蚀刻第一层204以产生如图2g所示的空腔216。空腔216可以是在第一方向(垂直于基材202平面的方向)上位于第三层218与基材202之间且在第二方向(垂直于第一方向且平行于基材202平面的方向)上位于第二层208的材料之间的气隙。在其他实施方式中,空腔216随后填充有除空气之外的材料。例如,空腔216至少部分地填充有以下中之一或多者:苯环丁烯(bcb)、聚甲基丙烯酸甲酯(pmma)或su-8。在一些实施方式中,空腔216(无论是被空气填充还是至少部分地被介电材料填充)可被视为限定膜(对应于第三层)的与基材202分离的一侧。

38.根据上文参考图1描述的制造方法100制造且在图2g中展示的半导体结构200可以是pic的部件。例如,半导体结构200是膜激光器或被动膜波导。

39.如本领域技术人员将理解,根据本文描述的实施方式,可使用各种技术来沉积半导体材料层。此种技术可称为再生技术,例如可使用金属有机气相磊晶(movpe)制程或分子束磊晶(mbe)制程。

40.以上实施方式被理解为本发明的说明性实施方式。应当理解,关于任何一个实施方式描述的任何特征可单独使用,或者与所描述的其他特征组合使用,且还可与任何其他实施方式或任何其他实施方式的任何组合的一或多个特征组合使用。此外,在不脱离所附权利要求范围的情况下,也可采用上文未描述的等同物及修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。