一种pipelined-sar adc的级间增益非线性校准方法

技术领域

1.本发明属于模拟集成电路技术领域,具体涉及一种pipelined-sar adc的级间增益非线性校准方法。

背景技术:

2.目前,pipelined-sar adc既能在保持较低功耗和较小面积的同时,也能达到较高的精度和速度,并且结合多通道、时间交织、每步多比特、多比较器等技术,使该架构在模数转换器的研究领域备受关注。pipelined-sar adc由采样保持电路、子adc和级间放大器组成,其中子adc采用逐次逼近型模数转换器(sar adc)取代传统的闪型adc(flash adc),这样做的好处是每一级的分辨率可以有效增高,因此不再需要很多级来实现更高的分辨率。由于pipelined-sar adc存在采样开关管的时钟馈通效应、电荷注入效应、采样电容的电容失配、级间放大器的有限增益和非线性效应、比较器失调等非理想因素的影响,这些因素限制了pipelined-sar adc能够达到的精度。所以需要对adc校准来减小这些非理想因素对于adc精度的影响。

3.adc校准主要分为数字域校准和模拟域校准。模拟域校准是通过增添额外的模拟电路来对adc进行校准,会打断adc的正常量化过程并且增加模拟电路的设计复杂度。数字域校准是在数字域对输出码字进行补偿,数字域校准可以突破工艺极限对adc性能的限制,所以数字校准早已成为adc中不可或缺的一部分。数字域校准一般包括电容失配校准和运放非线性校准,传统的增益非线性数字校准算法通常使用伪随机噪声序列或最小均方算法(lms)。但是通过伪随机序列注入的方法会降低adc动态输入范围,而且提取误差的收敛时间很长。而lms算法需要在模拟域添加一个参考adc,增加了模拟电路的资源浪费。使用基于亚稳态的pipelined-sar adc的级间增益非线性误差的校准算法,只需要模拟端的数字输出,解决以上缺陷,以提高pipelined-sar adc的精度。

技术实现要素:

4.本发明所要解决的技术问题是由pipelined-sar adc的级间运算放大器非线性(主要是三阶非线性)引起adc整体性能下降的缺陷,以及传统增益校准技术存在的模拟电路复杂的问题。

5.本发明采用的技术方案是:

6.基于亚稳态检测pipelined-sar adc的级间增益非线性校准方法,假设pipelined-sar adc由n个sar adc作为子级级联,每一子级为ki(1≤i≤n,i为正整数,n为大于1的整数)比特,相邻子级之间通过一个级间运算放大器连接,按照量化方向依次记为第一级子sar adc至第n级子sar adc,以及第一级的级间增益g1至第n-1级的级间增益g

n-1

,该n级pipelined-sar adc能实现比特精度的数字输出。

7.所述级间增益非线性校准的方法包括如下步骤:

8.步骤1,获得由输入信号经过pipelined-sar adc量化产生的位输出码字,其中每一级每一位的数字码字为di[ki:1],同时,还应获得亚稳态标志码字fi[ki:1]。其中di[ki:1]代表第i级子sar adc的所有数字码字,di[ki]代表第i级最高权重位,di[1]代表第i级最低权重位;若第i级子sar adc在量化第m位码字di[m]时比较器出现亚稳态,则di[m]对应的亚稳态标志位fi[m]=0,否则fi[m]=1,m为正整数且1≤m≤ki;

[0009]

步骤2,通过得到的数字码字对第一级至第n-1级的级间增益非线性进行校准,校准顺序为从低权重的后级向高权重的前级校准;

[0010]

步骤2.1,通过步骤1得到的第i级数字输出码字di和亚稳态码字fi对第二级至第n-1级的级间增益g2,

…

,g

n-1

进行线性校准,i∈[2,n-1];

[0011]

步骤2.2,通过步骤1得到的第一级数字输出码字d1[k1:1]、亚稳态码字f1[k1:1]和后级校准后合成码字对第一级的级间增益g1进行非线性校准;

[0012]

步骤3,得到非线性校准后的级间增益之后对adc输出的数字码字进行合成补偿,得到进行级间增益非线性校准后的实际量化输出码字。

[0013]

进一步的,步骤2的具体实现方式如下:

[0014]

级间增益的非线性校准主要是校准三阶非线性误差,因为pipelined-sar adc的模拟电路采用差分输入,偶数阶非线性可以被抵消。又由于adc的第一级权重占比最大,所以只校准第一级级间增益g1非线性误差,而第二级至第n-1级校准级间增益的线性误差即可。

[0015]

具体的,第二级至第n-1级的线性误差校准方法如下:

[0016]

因为级间增益的校准是从后级向前级校准,所以先通过第n-2级和第n-1级的数字码字对第n-1级的级间增益g

n-1

进行校准。其中通过提取第n-1级的发生亚稳态的数据得出第n-2级的理想残差电压v

res_ideal

,通过第n级的数字码字合成得到第n-2级的理想残差经过运算放大器放大后得到的实际残差电压v

res_real

。

[0017]

理想残差电压v

res_ideal

的获取过程为:第i级第m位发生亚稳态且当前位置1时,di[m]=1,fi[m]=1,ci[m]代表第i级第m位的电容大小,v

res_m_1

[i]代表第i级第m位发生亚稳态且当前位置1时的残差电压,v

ref

代表adc的参考电压;第i级第m位发生亚稳态且当前位置0时,di[m]=1,fi[m]=0,v

res_m_0

[i]代表第i级第m位发生亚稳态且当前位置0时的残差电压。将第i级一定数量发生亚稳态且置1的数据提取出来得到同理,将第i级相同数量发生亚稳态且置0的数据提取出来得到u代表发生亚稳态且分别置位为0或1的数量,即第i级理想残差电压

[0018]

放大后的实际残差电压v

res_real

的合成:求第i级级间增益的实际残差电压由第i 1级的数字码字直接合成,w

i 1

代表第i 1级的每一位的权重

值。

[0019]

联合第i级的理想残差电压和第i 1级的实际残差电压可得到第i级的线性级间增益为第二级至第n-1级的增益都按照此方法校准。

[0020]

具体的,第一级级间增益非线性校准方法如下:

[0021]

如上所述,pipelined-sar adc级间增益的校准步骤是从后级向前级校准,所以当校准第一级级间增益的时候,后级的级间增益已经校准完成,因此,可以将后端(第二级至第n级)当做一个理想adc来分析。第一级余量电压v

x

经过第一级级间运算放大器f(x)进行放大,假设f(x)=α1x α2x2 α3x3

…

αnxn,放大后的残差电压v

res

作为后端pipelined-sar adc的输入,后端的数字输出经过校准函数g(x)进行校准,将校准后的输出值和第一级的数字输出结合即得到

[0022]

pipelined-sar adc经过级间增益非线性数字校准后的输出d

out

,d

out

的数学表达式为:d

out

=d1 g(f(v

x

))。

[0023]

进一步的,步骤3的具体实现方式如下:

[0024]

通过步骤2对级间增益进行非线性校准时不能完全还原成线性,所以在合成码字时对输出进行补偿。补偿的方法为:选取第一级第i位发生亚稳态且将此位置为0或置为1的输入电压;将这个输入电压值经过g1放大后的残差电压送入校准系统,得出非线性校准后的v

x

';补偿的电压值为或c1[n]代表第一级的每一位的电容值大小,v

cp

代表补偿的电压值;得出第一级每一位发生亚稳态且分别置位为0或1的补偿电压值v

cp

,最后合成的输出为d

out

=d1 g(f(v

x

)) v

cp

。

[0025]

本发明的有益效果为,本发明提出了一种基于亚稳态的pipelined-sar adc的级间增益非线性误差的校准算法,在没有额外增加模拟电路的情况下,对级间增益的非线性进行校准,从而提高级间增益的校准精度,有效地提升了adc的性能。

附图说明

[0026]

图1为传统pipelined-sar adc的结构示意图;

[0027]

图2为pipelined-sar adc带比较器亚稳态检测的子sar adc结构示意图;

[0028]

图3为pipelined-sar adc级间增益非线性数字校准顺序的结构示意图;

[0029]

图4为pipelined-sar adc的余量放大传输函数曲线示意图;

[0030]

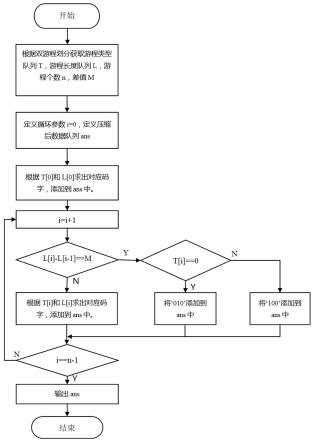

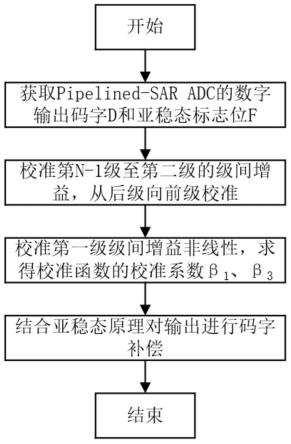

图5为本发明中pipelined-sar adc数字校准技术的流程图;

[0031]

图6为对比图,其中(a)为未校准第一级级间增益非线性、(b)校准第一级级间增益非线性不补偿码字、(c)为校准第一级级间增益非线性并补偿码字的fft分析对比图;。

具体实施方式

[0032]

下面结合附图对本发明的技术方案进行详细的描述;

[0033]

图1为传统pipelined-sar adc的结构示意图。假设该pipelined-sar adc一共含有n级电路,其中每级由ki比特sar adc组成,级间通过n-1个运算放大器连接。sar adc由电

容阵列,开关阵列和比较器组成,电容阵列负责对输入信号进行采样保持,开关阵列对输入信号进行翻转,翻转后的输入信号被送入比较器,由比较器得出对应位的数字码字,通过sar逻辑控制下一位的比较,每一级比较ki次,得到ki位数字码字,然后将子sar adc的余量电压作为运算放大器的输入信号,经过运算放大器的放大,所得结果输入到下一级作为下一级的输入信号,最终得到位数字码字。

[0034]

如图1所示,在未考虑级间增益非线性的情况下,对于整体的流水线adc,数字输出的理想值可以表示为:

[0035][0036][0037]di

表示第i级adc对应的数字输出,wi表示第i级数字输出对应的权重,gj为第j级运算放大器的级间增益,n表示整体adc的总级数。

[0038]

如图2是含有亚稳态检测电路的pipelined-sar adc的结构示意图。当比较器两端的输入差值v

p-vn小于一个临界值时,判断比较器进入了亚稳态比较区,此时比较结果可能为“1”也可能为“0”,此位的亚稳态标志位f置为1,代表发生了亚稳态,并将此位的数字码字置为“1”或“0”,发生亚稳态的数字码字置位为“1”或“0”的概率要满足伪随机序列的要求。一个输入电压在某一级量化出现亚稳态的情况只有一次,例如,在第一级的第i位发生了亚稳态且将此位置为“1”时,那么第一级剩余位的码字为“0”,即d1=x

…

x_1_0

…

0,x

…

x代表第ki位至第i 1位正常量化的数字码字,0

…

0代表第i-1位至第1位的数字码字“0”。如此置位的理由如下:当第i位发生了亚稳态,代表此时送入比较器的电压值约等于0,可以看作这一级高位量化得到的数字码字对应的模拟值约等于这一级的输入电压,即

[0039][0040]

但是由于还未完成剩余位的量化,此时将第i位置位为“1”,剩余位置“0”,第i级量化电压vdac为:

[0041][0042][0043]

其中,w1代表第一级每一位数字码字对应权重值,c

1[i]

表示第一级第i位的电容值,c

1total

代表第一子级的总电容值,v

ref

代表adc的参考电压,第二个等式和第三个等式相等是因为子sar adc的电容是二进制阵列。上式说明上述的置位方法使量化电压值和实际输入电压值只相差1lsb相当于发生亚稳态时确定了第一级的余量电压v

x

为即已知值。

[0044]

图3描述了pipelined-sar adc的级间增益校准顺序,假设除第一级外的级间增益

采用线性校准,先校准后级增益g

n-1

,再使用校准后的级间增益对g

n-2

,g

n-3

,

……

,g2进行校准,因此在校准第一级级间增益非线性的时候可以将后端看成一个整体,整体数字码字输出为d

be

。

[0045]

图4是子sar adc经过级间运算放大器的输入输出信号。当使用开环放大电路作为级间余量放大器的时候,放大函数应该当作非线性函数看待,导致余量电压曲线呈非线性。我们的校准目标就是使非线性输出经过一个校准系统还原成线性输出。

[0046]

下面详述本发明第一级级间增益非线性校准过程。

[0047]

步骤1,获得由输入信号经过pipelined-sar adc量化产生的输出码字di[ki:1]和亚稳态标志码字fi[ki:1]。其中di[ki:1]代表第i级子sar adc的所有数字码字,di[ki]代表第i级最高权重位,di[1]代表第i级最低权重位;若第i级子sar adc在量化第m位码字di[m]时比较器出现亚稳态,则di[m]对应的亚稳态标志位fi[m]=0,否则fi[m]=1,m为正整数且1≤m≤ki;

[0048]

步骤2,对后端(第二级至第n级)adc的级间增益进行线性校准,本发明不再赘述线性校准相关内容。因为adc的第一级精度对整体adc的精度影响最大,所以本发明考虑只对第一级的级间增益进行非线性校准。对后端的级间增益进行校准的计算公式为:

[0049][0050]

其中,以上每一子级累加的数据di是发生了亚稳态所提取出来的数据,di[u]代表第i级第u位的数字码字,wi[u]代表第i级第u位数字码字对应的权重,gi代表第i级的级间增益。

[0051]

步骤3,对第一级的级间增益非线性进行校准,主要是校准线性误差和三次非线性误差。定义第一子sar adc级的数字输出码字为d1,余量输出电压为v

x

,余量电压经第一级级间运算放大器放大后为残差电压v

res

,第一级级间运算放大器的输入输出表达式如下:

[0052][0053]

残差电压v

res

经过后端adc得到后端数字输出码字d

be

,d

be

经过校准函数g(x)进行还原,为了将三次非线性还原为线性,校准函数也需要是一个三次多项式函数,g(x)=β1·

x β3·

x3将非线性系统还原为线性系统:

[0054][0055]

上式q

be

代表后端adc的量化误差,β1和β3代表校准函数的一次和三次系数。

[0056]

不考虑后端量化误差的情况下,通过上述表达式可知d

out

的表达式为:

[0057][0058]

所以校准非线性系统的目标就转换成了校准β1和β3的值。

[0059]

余量传输函数曲线如图4所示,可以利用v

res

的边界值和一个固定值来估算非线性

误差。在a处,级间运算放大器的输入电压很小,此时非线性不明显,可以假设在每个量化区间的固定值a处函数呈线性,则v

xa

=v

resa

;v

res

的边界值是每个量化区间内的最大或者最小值,可以通过d1来确定量化区间,通过对应量化区间内d

be

的最值得到v

res

的边界值。但是需要通过对每一个d

be

作比较才能找到最值,会增加代码复杂度并且耗费资源,通过结合亚稳态的方法获取v

res

的边界值以解决上述问题。

[0060]

由表达式(3)和(4)知,当发生亚稳态时级间运算放大器的输入电压为:

[0061][0062]

此时的输入电压v

x

为已知值且为最大值,经过级间运算放大器得到的v

res

虽然有非线性偏差,但根据级间运算放大器输入输出的单调性可知此时的残差电压v

res

也为最大值,所以可以通过结合亚稳态的方法对级间增益非线性进行校准。结合表达式(7),可知具体计算式如下:

[0063]vxa

=β1·vresa

β3·vresa3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(10)

[0064]vxmax

=β1·vresmax

β3·vresmax3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(11)

[0065]

联立表达式(10)、(11)可得β1和β3的值,其中v

xa

代表在固定值a处的余量电压,v

resa

代表在固定值a处经过级间运算放大器放大后的残差电压,v

xmax

代表对应v

res

边界值的电压输入,v

resmax

代表v

res

边界值。在校准级间增益非线性需要足够多发生亚稳态的数据样本,将样本数据的后端数字码字合成v

resmax

求平均来减小残差电压边界值误差。

[0066]

步骤4,得到非线性校准后的级间增益之后对adc输出的数字码字进行合成补偿,得到进行级间增益非线性校准后的实际输出。

[0067]

在进行非线性校准的时候,将校正函数g(x)设为三次项函数不能完全的还原级间增益的非线性。首先,因为g(x)不是级间增益表达式的反函数,其次在计算的时候省略了5次及高次阶数,本身就做了近似处理,这样限制了能校准的非线性误差的范围,特别是开环运算放大器的增益较大时,此时α3值较大,运算放大器具有很强的非线性,会导致级间增益非线性校准效果很差。所以提出合成码字补偿的方法来减小非线性校准的误差,合成码字补偿方法如下:

[0068]

当第一级的最低位发生亚稳态时,通过第一级的数字码字合成余量电压v

x

为通过其后端数字码字d

be

和β1、β3合成校准后的余量电压v

cali

,v

cali

表达式如下:

[0069]vcali

=β1·dbe

β3·dbe3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(12)

[0070]

将校准后的余量电压和数字码字合成的余量电压作差就得到了补偿电压v

cp

:

[0071]vcp

=v

x-v

cali

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(13)

[0072]

根据第一级的最低位发生亚稳态时置位为“1”或“0”,得到不同的补偿电压v

cp_1_1

和v

cp_1_0

。第一级的第二位发生亚稳态时,v

cp_2

的计算方法和上述相同,只是最低位无论是“1”还是“0”都会进行补偿,所以第二位发生亚稳态的时候只需要补偿v

cp_2

和v

cp_1

的差值,补偿电压计算式如下:

[0073]vcp_2_1

=v

cp_2_cal_1-v

cp_1_1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(14)

[0074]vcp_2_0

=v

cp_2_cal_0-v

cp_1_0

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(15)

[0075]

其中,v

cp_2_cal_1

(v

cp_2_cal_0

)代表第二位发生亚稳态且置位为“1”(或“0”)时计算出

来的补偿电压,v

cp_2_1

(v

cp_2_0

)代表第二位发生亚稳态且置位为“1”(或“0”)时的实际补偿电压。第三位至第k1位的补偿电压都如上所示。

[0076]

最终合成输出d

out

的表达式如下所示:

[0077]dout

=d1 d

be

d1[1]

·vcp_1_1

(1-d1[1])

·vcp_1_0

…

d1[k1]

·vcp_k1_1

(1-d1[k1])

·vcp_1_0

[0078]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(16)

[0079]

因为只对第一级级间增益非线性进行校准,所以补偿的电压v

cp

通过利用在第一子级发生了亚稳态的数据进行计算即可。

[0080]

图5是pipelined-sar adc级间增益非线性数字校准的流程图。如图所示,先从第n-1级开始校准第n-1级的级间增益g

n-1

,然后校准第n-2级的级间增益直到第二级的级间增益g2,从后级向前级校准,然后对第一级级间增益的非线性进行校准,最后对输出进行码字补偿。

[0081]

对14bit的pipelined-sar adc进行建模和校准,该adc采用三级流水线结构,每一子级的数字量化位数分别为5bit、6bit和5bit,其中第二级和第三级分别含有一位冗余位。使用python对pipelined-sar adc进行整体工作电路以及校准电路的行为级建模,其中本发明只涉及对级间增益非线性的校准,所以第一级级间增益按照线性项和非线性项给,第二级的级间增益按照其满足的正态分布的平均值和方差随机赋值。首先校准第二级级间增益,统计第二级最低量化位出现亚稳态的量化数据,按照线性增益校准的方法进行实际增益的求解,然后校准第一级级间增益非线性,通过发生了亚稳态的数据合成残差电压的边界值(第一级最低位发生亚稳态的数据设定值为2048,次低位为1024,直到最高位为128),求得校正函数的系数,然后根据第一级每一位数字量化位的亚稳态标志位统计其相应的量化数据,再将其误差码字分配到相对应的量化数字码字上进行码字补偿,合成最终的输出。如图6所示是在同一条件(α1=8,α2=-400)设置下未校准第一级级间增益非线性(如图6中的(a))、校准第一级级间增益非线性不补偿码字(如图6中的(b))、校准第一级级间增益非线性并补偿码字(如图6中的(c))的fft分析对比图,可以看出失真信噪比sndr从61.08db上升到77.16db再到83.84db,无杂散动态范围sfdr从70.94db上升到83.42db再上升到101.87db,有效位数从9.85db上升到12.53db再上升到13.63db。

[0082]

综上所述,本发明将比较器亚稳态检测原理与pipelined-sar adc的级间增益非线性校准技术相结合,校准原理简单,在没有增加模拟电路设计复杂度的基础上,增加了校准系数的精度,提升了adc的性能。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。