高功率密度3d半导体模块封装

技术领域

1.本技术涉及半导体模块封装,尤其但不排他地涉及高功率密度、三维模块封装。

背景技术:

2.为了满足汽车、航空航天、可再生能源和其他应用的高标准要求,高功率半导体封装面临着各种挑战。人们希望半导体模块应该紧凑且具有高功率密度,并且能够在恶劣环境中运行相对较长的使用寿命(超过15年)。已经提供了各种器件,旨在提高在高温、高湿度水平、高机械冲击和振动、高辐射水平和其他恶劣环境下的操作能力和稳定性。然而,现有的封装结构、材料和技术无法在单一设计中解决所有这些问题。

3.图1示出了一种这样的现有技术的器件,它示出了一个封装中的两个半导体芯片,处于平面配置中。每个芯片都连接到两个衬底层,在衬底之一和半导体芯片之间具有间隔件。在许多器件中,衬底是陶瓷。该封装只有一层半导体芯片,因此功率密度有限。

4.us 2014/0118956还涉及一种功率半导体模块,其具有用于使用导线附接半导体器件的两层衬底。us 2012/0162931涉及附接到不同衬底上的功率器件和控制器件的组件。us 7,808,101涉及使用pcb在pcb的任一侧附接功率器件和ic器件并将功率器件的另一侧连接到常规衬底的功率模块。us 7,492,043涉及一种功率模块倒装芯片封装,在其中单层器件经由导电凸点连接到载体上。

技术实现要素:

5.在所附权利要求中概述了各方面和优选特征。

6.根据本公开的第一方面,提供了一种半导体器件子组件,包括:至少两个功率半导体器件;以及第一类型的触点,其中,第一功率半导体器件位于第一类型的触点的第一侧上,并且其中,第二功率半导体器件位于第一类型的触点的第二侧上,其中,第二侧与第一侧相反。

7.第一类型的触点的第一侧可以是第一类型的触点的顶侧或顶表面,并且第一类型的触点的第二侧可以是第一类型的触点的底侧或底表面。第一类型的触点可以是发射极触点或端子,或者可以是集电极触点或端子。

8.通过将半导体器件连接到触点或端子的相反侧或表面,可以将半导体器件布置成器件的3d堆叠,而无需使用基板或陶瓷衬底。与现有技术的器件相比,在给定体积中功率半导体器件的密度可以增加,这允许子组件具有更高的功率密度。

9.该子组件提供了紧凑且高可靠性的功率igbt模块产品。3d半导体芯片堆叠具有无基板和衬底结构。此外,倒装芯片、平面互连技术和耐高温高湿环氧化合物都可以用于子组件或具有根据本公开的子组件的封装中。子组件的特性大大提高了其电气、热学和机械性能,从而增强了子组件的可靠性。

10.由于层叠平面端子的布局、集电极和发射极端子的重叠结构、端子的大表面积以及使用无键合线技术的平面互连,子组件具有低寄生电感。

11.与现有技术相比,该子组件具有以下优点:

12.(i)该子组件为高标准的汽车、航空航天、可再生能源转换系统产品提供高功率密度、低寄生、高效率、高工作温度和高可靠性的功率半导体模块;

13.(ii)通过使用半导体器件的3d堆叠实现高功率密度,无需基板和衬底;

14.(iii)由于电源端子结构和布局以及平面互连,寄生电感和电阻较低;

15.(iv)可以使用位于子组件外表面上的散热器来提供双侧模块冷却;

16.(v)采用传递模塑封装,具有耐高工作温度、耐高湿性、机械稳定性好;

17.(vi)在分离器件封装系统中的高功率密度子组件。

18.第一功率半导体器件和第二功率半导体器件均可以直接连接到第一类型的触点。

19.第一功率半导体器件和第二功率半导体器件可以以倒装芯片堆叠组件的方式连接到的第一类型的触点。

20.子组件还可以包括至少两个第二类型的触点,其中,第二类型的触点中的一个连接到第一功率半导体器件的顶侧并且第二类型的触点中的另一个连接到第二功率半导体器件的底侧。第二类型的触点可以是集电极触点或端子,或者可以是发射极触点或端子。

21.半导体器件子组件还可以包括间隔件,并且可以使用间隔件将第二类型的触点彼此电连接。间隔层可以仅存在于触点之间,而不存在于功率半导体器件和触点之间。这意味着间隔层不会阻止功率器件和触点之间的连接,因此可以在触点顶部形成额外的半导体器件层。

22.子组件可以包括布置成至少两层半导体器件的至少四个半导体器件。每层半导体器件内的半导体器件可以在第一维度上彼此间隔开,并且半导体器件层可以在第二维度上彼此间隔开,其中第一维度垂直于第二维度。

23.第一类型的触点可以连接到所有的所述至少四个半导体器件。

24.所述至少四个功率半导体器件可以并联和/或反并联连接以形成单个开关。

25.子组件可以包括在第一维度上彼此侧向间隔开的至少两个第一类型的触点,其中,来自每层半导体器件的半导体器件可以连接到每个第一类型的触点。

26.子组件可以包括至少四个第二类型的触点,并且半导体器件可以连接到每个第二类型的触点。至少两个第二类型的触点可以连接到两层半导体器件中的第一层中的半导体器件的顶侧,并且至少两个其他的第二类型的触点可以连接到两层半导体器件中的第二层中的半导体器件的底侧。

27.半导体器件的第一侧可以是顶侧并且半导体器件的第二侧可以是底侧,其中第一侧和第二侧可以是相反侧。

28.第一类型的触点可以连接到第二类型的触点。

29.所述至少四个功率半导体器件可以以半桥配置布置。半桥配置非常有用,因为它对于功率系统配置来说既简单又灵活。

30.子组件可以包括至少四层半导体器件。

31.第一层半导体器件中的半导体器件可以位于第一类型的第一触点的第一侧上,第二层半导体器件中的半导体器件可以位于第一类型的第一触点的第二侧上。第二层半导体器件中的半导体器件可以位于第二类型的第一触点的第一侧上,第三层半导体器件中的半导体器件可以位于第二类型的第一触点的第二侧上。第三层半导体器件中的半导体器件可

以位于第一类型的第二触点的第一侧上,且第四层半导体器件中的半导体器件可以位于第一类型的第二触点的第二侧上。每个触点的第一侧可以是顶侧并且每个触点的第二侧可以是底侧,其中,第一侧和底侧是相反侧。

32.第一类型的第一触点和第二触点可以彼此连接。

33.功率半导体器件可以是绝缘栅双极晶体管(igbt)和/或快速恢复二极管(frd)。半导体器件可以由sic或gan形成。

34.半导体器件子组件还可以包括位于第二类型的触点的外表面上的散热器。散热器可以形成在子组件的顶表面和底表面上。这些散热器冷却半导体器件芯片,提高子组件的可靠性并允许子组件模块以更高的输出功率水平运行。

35.子组件可以包括至少一个衬底结构,其中,衬底结构位于功率半导体器件和触点之间。衬底结构可以是直接键合铜(dbc)衬底。衬底结构可以直接连接到半导体器件并且触点(金属端子)可以从dbc的金属延伸。这仍然允许半导体器件的3d堆叠,同时提供隔离。

36.根据本公开的另一方面,提供了一种半导体器件封装,包括如上所述的半导体器件子组件,其中,子组件被封装在模塑料中。

37.根据本公开的另一方面,提供了一种半导体器件封装的制造方法,其中,该方法包括:

38.形成至少两个第二类型的触点;

39.形成至少两个功率半导体器件,每个第二类型的触点上至少有一个半导体器件;

40.形成第一类型的触点;以及

41.通过将功率半导体器件中的第一半导体器件连接到第一类型的触点的第一(顶)侧,并将功率半导体器件中的第二功率半导体器件连接到第一类型的触点的第二(底)侧,以形成半导体器件的堆叠,其中,第二侧与第一侧相反,并且使得第二类型的触点中的一个连接到第一功率半导体器件的顶侧并且第二类型的触点中的另一个连接到第二功率半导体器件的底侧。

42.所述方法还包括:将半导体器件的堆叠放置在框架中;用模塑料填充框架;以及固化模塑料。这种传递模塑封装的方法提高了半导体器件封装的耐高温和高湿性能以及机械稳定性。

附图说明

43.现在将仅通过示例并参考附图来描述本发明的一些优选实施例,其中:

44.图1示出了根据现有技术的半导体器件子组件;

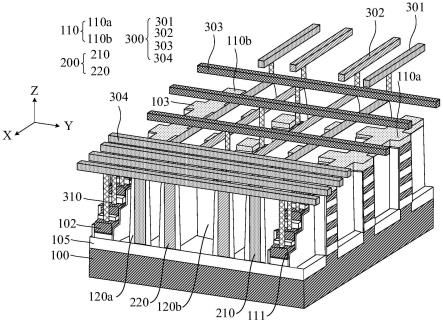

45.图2示出了根据本公开实施例的半导体器件子组件;

46.图3示出了根据本公开实施例的替代半导体器件子组件,其中子组件具有两个集电极触点;

47.图4示出了根据本公开的实施例的替代半导体器件子组件,其中子组件具有半桥配置;

48.图5示出了根据本公开的另一实施例的替代半导体器件子组件,其中子组件具有替代半桥配置;

49.图6示出了根据本公开实施例的替代半导体器件子组件,其中子组件具有四层芯

片;

50.图7示出了根据本公开的实施例的替代半导体器件子组件,其中子组件具有四层芯片并且其中子组件被封装在模塑料封装中;

51.图8示出了根据本公开的另一实施例的替代半导体器件子组件,其中子组件具有四层芯片并且其中子组件被封装在模塑料封装中;

52.图9示出了根据本公开实施例的替代半导体器件子组件,其中子组件具有双侧模块液体冷却;

53.图10示出了在半导体器件子组件的制造过程期间根据本公开的实施例的半导体器件子组件的展开图。

具体实施方式

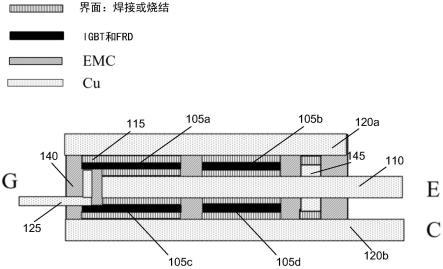

54.图2图示了根据实施例的半导体器件子组件100的示意性截面图。在本实施例中,子组件具有四个功率半导体器件芯片105a、105b、105c和105d。功率器件可以是绝缘栅双极晶体管(igbt)或快速恢复二极管(frd)。所有四个功率器件芯片105都使用焊接或烧结界面115直接连接到发射极触点110。

55.功率器件芯片105以3d结构布置,因此有两层功率半导体器件芯片。第一层包括芯片105a和105b,第二层包括芯片105c、105d。每层内的芯片在第一维度上彼此侧向间隔开,并且层本身在垂直于第一维度的第二维度上间隔开。第一层芯片105a、105b中的两个半导体器件都位于发射极触点110的顶侧,并且第二层芯片105c、105d中的两个半导体器件都位于相同发射极触点110的相反底侧。功率半导体器件105a、105b、105c、105d以倒装芯片堆叠组件的方式连接到触点110、120。

56.该子组件具有形成在第一层半导体器件中的功率器件105a、105b二者的顶表面上并连接到它们的集电极触点120a。该子组件具有形成在第二层半导体器件中的功率器件105c、105d二者的底表面上并连接到它们的另一个集电极触点120b。在该实施例中,集电极触点120a、120b通过金属间隔件145彼此电连接。通过将集电极触点120a、120b与间隔件145连接,子组件模块具有一个集电极端子,因此应用功率系统中的连接将更简单。与现有技术的器件相比,这仅使用仅一个间隔件来形成电路,这意味着子组件的组装更容易。

57.栅极触点125连接到每层功率器件中的第一功率器件105a、105c。子组件被封装在环氧树脂模塑料(emc)封装140中。emc复合封装140允许发射极和集电极触点120、110伸出emc,但也允许铜集电极触点120的顶表面和底表面暴露在外进行冷却,如果需要,使得它们可以连接到散热器。

58.图3示出了根据本公开实施例的替代半导体器件子组件,在其中子组件具有两个未连接的集电极触点。该实施例中的许多特征与图2中所示的特征相同,因此具有相同的附图标记。在该实施例中,集电极触点220a、220b彼此不存在电连接。由于没有间隔件,组装过程更简单,并且可以减小子组件的尺寸/体积,从而提供更高的功率密度。

59.在该实施例中,以及在图2的实施例中,芯片105a和105c都彼此并联连接,并且芯片105b和105d彼此并联连接。在该示例中,芯片105a和105c是igbt芯片,芯片105b和105d是frd芯片,但是它们可以反之亦然地被布置。igbt芯片105a、105c在功率半导体模块中以反并联配置(极性相反的并联连接)的方式连接到frd芯片105b、105d。

60.图4(a)示出了根据本公开的实施例的替代半导体器件子组件,在其中子组件具有半桥配置。图4(b)示出了图4(a)的半导体子组件的电路图。该实施例中的许多特征类似于图2中所示的特征,因此具有相同的附图标记。在本实施例中,功率器件芯片105也以3d结构布置,因此功率半导体器件芯片有两层。第一层包括芯片105a和105b,第二层包括芯片105c、105d。

61.半导体子组件具有两个发射极触点310a、310b。第一层的第一芯片105a和第二层的第一芯片105c连接到第一发射极触点310a。第一层的第二芯片105b和第二层的第二芯片105d连接到第二发射极触点310b。

62.该器件具有四个集电极触点320a、320b、320c、320d,每个都直接连接到单独的功率半导体器件。第一层中的第一功率器件105a的集电极触点320a连接到第二层中的第一功率器件302c的集电极触点302c,第一层中的第二功率器件105c的集电极触点320b连接到第二层中的第二功率器件302d的集电极触点302d。在该实施例中,功率器件以串联配置连接。连接到每层中的第一功率器件105a、105c的发射极触点310a连接到下层105d中的第二功率器件的集电极触点320d。栅极触点325a连接到每层功率器件中的第一功率器件105a、105c,并且栅极触点325b连接到每层功率器件中的第二功率器件。

63.半导体子组件具有两个单独的开关(图4(b)中所示的顶部和底部开关),形成半桥拓扑。单独的开关彼此串联连接。该子组件具有三个端子dc 、dc-和ac,从中间具有ac输出。

64.在图4(a)中,设备的左侧(芯片105a和105c)是顶部开关,右侧(芯片105b和105d)是底部开关。触点320c(c1)是dc 端子,触点310b(e2)是dc-端子,并且触点320d(e1/c2)是ac端子。半桥配置非常有用,因为它对于功率系统配置来说既简单又灵活。

65.图5示出了根据本公开的另一实施例的替代半导体器件子组件,其中子组件具有替代半桥配置。该实施例中的许多特征类似于图4中所示的特征,因此具有相同的附图标记。在该实施例中,集电极触点320a、320c和320b、320d彼此不具有电连接。

66.图6示出了根据本公开实施例的替代半导体器件子组件,在其中子组件具有四层芯片。在该实施例中,与图2类似的两个子组件堆叠在一起,中央集电极触点连接到两层半导体芯片。通过增加半导体芯片的层数,可以提高单个模块的功率密度和功率水平。

67.在该实施例中,集电极触点420a、420b、420c彼此电连接。通过连接集电极触点420a、420b、420c,子组件模块具有一个集电极端子,因此应用功率系统中的连接将更加简单。发射极触点410a、410b也彼此电连接。栅极触点425连接到每层功率器件中的第一功率器件405a、405c、405e、405g。

68.图7示出了根据本公开的实施例的替代半导体器件子组件,在其中子组件具有四层芯片并且在其中子组件被封装在环氧树脂模塑料封装440中。许多特征与图6中所示的相似,因此具有相同的附图标记。在该实施例中,集电极触点420a、420b、420c彼此不电连接,并且发射极触点410a、410b彼此不聚集。由于没有连接触点的间隔件,组装过程更简单,并且可以减小子组件的尺寸/体积,从而提供更高的功率密度。

69.图8示出了根据本公开的另一实施例的替代半导体器件子组件,在其中子组件具有四层芯片并且在其中子组件被封装在模塑料封装440中。该实施例与图6的实施例相同,但是子组件被封装在环氧树脂模塑料封装440中。

70.图9示出了根据本公开的实施例的替代半导体器件子组件,在其中子组件具有双

侧模块液体冷却。在该实施例中,散热器530形成在子组件的顶表面和底表面上。散热器530可以是具有冷却片的铝散热器。硝酸铝隔离膜535位于散热器530和子组件的集电极触点120之间。双侧冷却提高了冷却效率,并降低了结合到冷却剂的热阻。芯片会更冷,因此可靠性会提高。此外,子组件模块将能够在高输出功率水平下运行。

71.图10示出了在半导体器件子组件的制造过程期间根据本公开的实施例的半导体器件子组件的展开图。

72.该制造方法包括以下步骤:

73.1)每个具有功率半导体器件905芯片的管芯的第一层附接到第一(顶部)集电极电源引线或端子920a的底表面,并且每个具有功率半导体器件905芯片的管芯的第二层附接到第二(底部)集电极电源线或端子920b的顶表面。可以使用无铅焊接或ag/cu低温烧结来附接管芯;

74.2)第一和第二集电极电源端子920a、920b堆叠在一起,发射极触点910位于它们之间,并且焊接在发射极触点的顶表面和底表面上。栅极引脚925附接到顶部和底部集电极端子,顶部和底部集电极端子通过金属间隔件945连接。堆叠可以使用无铅焊接或ag/cu低温烧结;

75.3)将子组件堆叠放置在夹具中,并在高压和高温下(例如,在大约50mpa和250℃下)将环氧树脂模塑料注入夹具中。然后在高温下固化组件(例如,在大约125℃下)。夹具可以是附接在电源端子(触点)上的塑料框架。框架可以被填充有环氧树脂模塑料或硅凝胶。

76.本领域技术人员将理解,在前面的描述和所附权利要求中,诸如“上方”、“重叠”、“下方”、“侧向”等位置术语可以理解为参考装置的概念图,例如标准横截面透视图和附图中所示的那些。使用这些术语是为了便于参考,但不具有限制性。因此,这些术语应被理解为指的是处于如附图所示取向的设备。

77.虽然本公开已经根据上述优选实施例进行了描述,但是应当理解这些实施例仅是说明性的并且权利要求不限于这些实施例。鉴于所附权利要求,本领域技术人员将能够进行修改和替代。本说明书中公开或图示的每个特征可以单独或与本文公开或图示的任何其他特征的任何适当组合并入本公开。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。