1.描述概括而言涉及三维(3d)电路处理,更具体的描述涉及3d电路的阶梯区域中的虚设(dummy)字线触点。

背景技术:

2.三维(3d)nand(与非)技术通常用于创建非易失性(nv)存储设备,例如固态驱动器(solid state drive,ssd)。对3d nand的提及可以更具体地指nand闪存。在3d nand工艺中,存储阵列经常是按阶梯结构用字线来创建的,其中垂直连接器支柱将顶部连接层与字线相连接。更高的3d nand密度是通过更小的工艺几何尺寸和特征间距实现的。因此,一些器件将是密集封装的,而一些垂直支柱将是半隔离的。

3.半隔离的垂直支柱或半隔离的字线连接器相对于非隔离的触点有更加锥形的轮廓。锥度的增大可导致蚀刻不足,即触点未能与目标字线层接触,或者蚀刻过度/穿通,即触点穿过字线蚀刻到其他层中。

4.与在上部接触层和目标字线之间形成适当连接的具有正确轮廓的字线触点相比,半隔离触点在蚀刻期间往往具有不那么均匀的聚合物淀积。形成适当接触的非隔离触点可被称为正常字线触点。半隔离字线触点的非均匀聚合物淀积可能是由于随着连接器支柱更密集封装而发生的高纵横比蚀刻的微米负载效应,导致相对于半隔离的支柱,材料/工艺差异增大。半隔离支柱最终会有不同的蚀刻特性。从而,与正常字线触点相比,半隔离字线触点具有更差的锥度和更小的工艺裕量,导致垂直支柱未进行期望接触的工艺差异。

5.传统工艺使用干式蚀刻工艺调节,这在蚀刻期间由于聚合物淀积较少而牺牲了聚合选择性。这大大降低了蚀刻不足和蚀刻过度之间的蚀刻工艺裕量。使得该工艺很难持续。

6.传统工艺尝试调节中心工艺的临界尺寸(critical dimension,cd)大小,以使得非隔离和半隔离的触点都具有充分的特性,从而获得良好的器件产量。器件产量对于成功的大批量制造(high volume manufacturing,hvm)是必要的。然而,随着规模的扩大,继续调节中心工艺来为半隔离和密集字线触点两者提供充足的蚀刻特性是更困难了。由于随着纵横比容差因更小的临界尺寸而下降,蚀刻深度随层数增大而增大,所以该工艺对聚合物淀积和蚀刻之间的平衡变得更加敏感。

附图说明

7.下面的描述包括对具有借由实现方式的示例给出的图示的附图的论述。应当以示例方式而不是限制方式来理解附图。就本文使用的而言,提及一个或多个示例应被理解为描述本发明的至少一个实现方式中包括的特定特征、结构或特性。本文出现的诸如“在一个示例中”或“在替换示例中”之类的短语提供了本发明的实现方式的示例,而并不一定全都是指同一实现方式。然而,它们也不一定相互排斥。

8.图1是电路的截面的示例的表示,该电路的阶梯区域具有虚设的连接器支柱。

9.图2是在半隔离触点附近具有虚设连接器的电路的示例的截面成像表示。

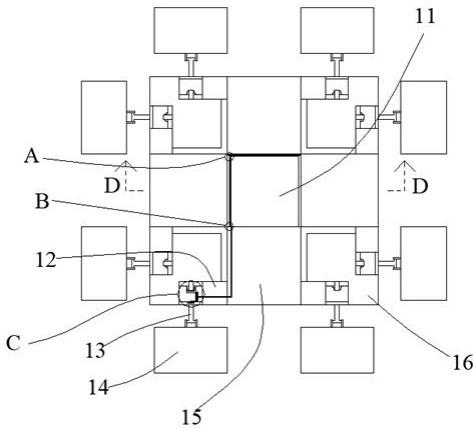

10.图3是具有虚设连接器的电路的顶视图的示例的表示。

11.图4a是在半隔离连接器的隔离侧具有虚设连接器的电路的截面的示例的表示。

12.图4b是在半隔离连接器的任一侧具有虚设连接器的电路的截面的示例的表示。

13.图4c是在半隔离连接器的隔离侧具有多个虚设连接器的电路的截面的示例的表示。

14.图4d是在半隔离连接器的任一侧具有多个虚设连接器的电路的截面的示例的表示。

15.图5是在阶梯区域的不同区域中的半隔离连接器附近具有虚设连接器的电路的截面的示例的表示。

16.图6是与不使用虚设连接器时相比,当使用虚设连接器时的块故障的示例的图解表示。

17.图7a是具有固态驱动器(ssd)的硬件视图的系统的示例的框图,该固态驱动器具有非易失性阵列,该非易失性阵列具有虚设连接器。

18.图7b是具有固态驱动器(ssd)的系统的逻辑视图的示例的框图,该固态驱动器具有非易失性阵列,该非易失性阵列具有虚设连接器。

19.图8是用于创建具有虚设连接器支柱的阶梯区域的过程的示例的流程图。

20.图9是计算系统的示例的框图,在该计算系统中可以实现在半隔离区域中具有虚设连接器的非易失性介质。

21.图10是移动设备的示例的框图,在该移动设备中可以实现在半隔离区域中具有虚设连接器的非易失性介质。

22.接下来对某些细节和实现方式进行描述,包括对附图的非限制性描述,这些附图可以描绘一些或所有示例,以及其他潜在的实现方式。

具体实施方式

23.如本文所述,具有三维(3d)阶梯存储器堆叠的存储器设备包括接近半隔离连接器的虚设连接器。半隔离连接器在3d阶梯的边缘处,或者在相对于将利用相同的半导体处理来蚀刻的更高密度的支柱区域,连接器支柱的密度较低的地方,连接到字线。由于相邻连接器的密度更低,半隔离连接器与非隔离连接器具有不同的蚀刻特性。或者,任何倾向于具有与中心工艺显著不同的蚀刻处理特性(导致连接器支柱的蚀刻过度或蚀刻不足)的连接器,都可以被视为半隔离连接器。在一个示例中,半隔离连接器是指在一侧有但在另一侧没有相邻连接器的连接器。

24.垂直连接器穿过3d阶梯堆叠上的隔离层来将字线与访问层中的导电线连接起来。存储器设备在半隔离连接器的一侧包括至少一个虚设垂直连接器。存储器设备在半隔离连接器周围可包括多个虚设连接器。虚设垂直连接器伸入隔离层中,但可以将或不将3d阶梯堆叠的字线与访问层的导电线电连接。在一个示例中,虚设垂直连接器连接到字线,但不连接到顶部连接器或导电线。在一个示例中,虚设垂直连接器连接到顶部连接器或导电线,但不连接到字线。一般而言,虚设垂直连接器延伸进入或穿过至少一些隔离层,但不在字线与顶部连接器或导电线之间提供电连接。

25.虚设连接器改变了如果没有虚设连接器则将会半隔离的连接器的蚀刻特性。即使

虚设连接器不提供字线与访问层中的导电线之间的连接,它也会使得半隔离连接器具有更接近中心工艺的特性。从而,它可以改善锥度和工艺裕量。因此,半隔离触点将不容易出现蚀刻不足或蚀刻过度/穿通。传统上,半隔离字线触点的临界尺寸与正常字线触点相比更小。有了一个或多个虚设触点,触点的尺寸将更接近正常字线触点。

26.图1是电路的截面的示例的表示,该电路的阶梯区域具有虚设的连接器支柱。电路100表示具有非易失性(nv)存储器的阶梯区域的存储器设备的一部分。在一个示例中,电路100表示3d nand存储器的一部分,例如3d nand闪存设备。在一个示例中,电路100中的虚设连接器可以被应用到3dxp(3d交叉点)存储器或者其他堆叠式存储器。将会理解,电路100中的某些特征不一定是按比例绘制的。更确切地说,某些特征被强调,而其他特征则被弱化。

27.电路100包括衬底110,它表示一半导体表面,3d存储器结构被构建在该表面上。在一个示例中,对于3d结构,电路100包括选择门源极层sgs 112,或者等同物。此外,电路100可包括选择门漏极层sgd 114作为存储器层的漏极。

28.存储器结构形成在字线(wl)120的层中的sgs 112和sgd 114之间的层中。对于不同的存储器设备,wl 120的层数可以是不同的。wl 120的层形成比特单元或存储单元的3d堆叠。一般而言,字线响应于存储器访问操作(例如,读取或写入)的行地址而被激活。电路100包括位线(bl)130,这些位线响应于存储器访问操作的列地址而被充电。wl 120连接到多行比特单元,并且bl 130选择所选的一行或多行的个体比特或比特单元。wl 120的堆叠的方向可以基于视角而变化。例如,在堆叠的顶部或堆叠的顶层的字线可被认为是靠近阶梯区域150的边缘的第一字线。在一个示例中,在堆叠的底部或堆叠的底层的字线可以被认为是第一字线。

29.如图所示,bl 130在电路100中进入页面,并且wl 120在页面上从左到右。bl 130和wl 120是相互正交的。在一个示例中,比特单元在bl和wl的交点处。在一个示例中,bl 130具有穿过wl 120的层的垂直列或通道。在一个示例中,nv介质包括在位线和字线的重叠处的比特单元。如果这样的器件具有所描述的半隔离字线触点,那么在这样的结构中可以使用虚设触点。

30.区域150图示了电路100的阶梯结构。该阶梯结构可以被识别为阶梯堆叠,并且指的是这样一个事实,即从截面来看,使用衬底110作为参考“地板”,另一个字线层上方的字线层将不会延伸到它下方的字线层那么远。从而,边缘处的字线层看起来有从最接近衬底110的字线向上到最远离衬底110的字线的阶梯。

31.阶梯区域150暴露了各种字线,以与连接器层140进行垂直连接。连接器140表示层中的导电线,它对于其中将包括电路100的设备而言允许从外部i/o(输入/输出)对电路100进行电气访问。在一个示例中,连接器140表示多条平行的导电线,它们在图1的方向上从左到右延伸。连接器线可以与wl 120平行,并且与bl 130正交。

32.连接器层140也可以被称为访问层或触点,并且位于电路100的顶层或者顶层附近。连接器140为外部i/o提供连接点。活跃支柱142表示将wl 120之一与连接器140电连接的连接器或字线连接器或支柱。虽然在电路100中没有具体图示,但活跃支柱142(和支柱144)具有非常高的纵横比。高纵横比的支柱是指相对于其直径而言,具有非常深的深度的支柱。

33.半隔离支柱144表示活跃支柱142,但在阶梯的一端。更具体而言,支柱144被图示

在阶梯的顶部边缘,以连接到最顶部的wl 120。在一个示例中,半隔离支柱可以位于阶梯的下部边缘,以连接到最底部的wl 120。将会观察到,支柱144的一侧有相邻触点,这是一个活跃支柱142,在阶梯中的下一级。在阶梯底部的半隔离支柱将会有在阶梯的上一级的相邻活跃支柱。支柱144在另一侧、远离阶梯区域150的地方没有相邻的活跃支柱。

34.具有虚设支柱的半隔离支柱可以被说成具有相邻支柱。然而,将会理解,虚设支柱不是活跃支柱;从而,可以参考在一侧有相邻的活跃支柱而在另一侧没有或缺少相邻的活跃支柱来描述半隔离支柱。在一个示例中,可以参考连接到阶梯堆叠的如下字线来描述半隔离支柱:该字线具有向上一阶或向下一阶的相邻字线,但在阶梯结构的另一个方向上没有相邻字线。从而,在一个示例中,半隔离支柱连接到在阶梯堆叠中只有单个邻居的字线。

35.在一个示例中,电路100包括与支柱144相邻或接近的一个或多个虚设支柱。虚设支柱不连接到连接器,并且可以连接或不连接到字线。从而,虚设支柱可以被称为浮动支柱或浮动触点。在一个示例中,电路100包括虚设支柱146,它表示相对于支柱144而言远离阶梯区域的支柱。在一个示例中,电路100对于支柱144只包括虚设支柱146。虚设支柱146可以被认为是第一虚设支柱,并且虚设支柱148可以被认为是第二虚设支柱。或者,虚设支柱148可以被认为是第一虚设支柱,并且虚设支柱146可以被认为是第二虚设支柱。电路100可包括第三虚设支柱、第四虚设支柱、或者其他虚设支柱(未示出)。虚设支柱146与虚设支柱148在活跃支柱144的相反侧;可以说,虚设支柱是在彼此的相反侧。

36.在一个示例中,电路100包括虚设支柱148,它表示相对于支柱144而言朝向阶梯区域的支柱。在一个示例中,电路100不包括支柱148,除非它也包括支柱146。在一个示例中,电路100可包括虚设支柱148,而不包括虚设支柱146。在一个示例中,电路100包括至少一个虚设支柱146和至少一个虚设支柱148。

37.在一个示例中,虚设支柱或虚设触点146和148需要被蚀刻不足。在一个示例中,通过保持虚设触点支柱的直径小于活跃触点支柱的直径,可以保证虚设触点相对于活跃支柱而言是蚀刻不足的。已发现,当虚设支柱146和148的直径约为支柱144的80%时,虚设支柱保持蚀刻不足,并且为支柱144提供更好的蚀刻特性。当使用更多的虚设支柱时,虚设支柱的大小可以变化。

38.将会理解,随着电路100的结构的变化,虚设支柱146或虚设支柱148,或者虚设支柱146和148两者,可以防止支柱144被半隔离。从而,该工艺可能不需要额外的调节来为支柱144提供正确的蚀刻特性。

39.图2是在半隔离触点附近具有虚设连接器的电路的示例的截面成像表示。电路200表示与电路100一致的电路,如用显微镜成像技术所见。

40.电路200包括连接器(未具体示出),来与阶梯210的字线连接。阶梯210表示电路200的包括存储单元的区域。在阶梯区域和连接器之间是隔离层,例如氧化物或氮化物层。隔离层在存储单元和电路顶部的导电线之间提供电气隔离,这些导电线提供对外部设备i/o的访问。

41.相对于支柱的宽度,字线是非常细的。在一个示例中,触点222表示半隔离支柱或半隔离触点。触点222将阶梯210顶部的字线连接到连接器。在一个示例中,触点228也可以是半隔离触点。一些处理生成的器件在阶梯顶部和阶梯底部都有触点,它们可能无法正常蚀刻。顶部和底部wl触点都可能表现出强烈的间距依赖性。

42.在一个示例中,电路200包括接近触点222的虚设触点224和226。没有示出接近触点228的虚设触点,但将会理解,可以使用这种虚设触点。靠近触点222的虚设触点224和226可以消除字线触点蚀刻特性的系统性薄弱部位。在一个示例中,虚设触点可以提高字线触点蚀刻的工艺裕量,这提高了产量并且降低了工艺复杂性。

43.虚设触点224和226可以被称为浮动触点,因为它们没有完全通过隔离层延伸到阶梯。在电路200的具体实现方式中,触点222的隔离侧的虚设触点224并不像非隔离侧的虚设触点226延伸得那么远。在一个示例中,它们可以是相同或大致相同的深度。

44.将会观察到,虚设触点224和226的直径比活跃支柱更窄或更小,这可以从连接器处的支柱大小看出。还将观察到,虚设触点的锥度比活跃触点明显更大。

45.图3是具有虚设连接器的电路的顶视图的示例的表示。图300图示了与图1的电路100一致的电路的示例的俯视图。图300可以被认为是存储器设备的阶梯区域的电路特征的布局。

46.顶视图图示了电路的不同部分的方向。在图300中,位线310在图的方向上下延伸。触点330从右向左延伸,与位线310正交。字线没有被具体示出,但将会与触点330平行,并且可在其下方延伸。触点330可以表示连接到活跃字线的连接器。

47.图300没有具体示出字线,而是用不同的阴影图示了阶梯320,以表示阶梯区域的不同级别。在图300中,垂直触点支柱被表示为触点导电线上的圆圈。并非所有的连接器都一定在所表示的所有圆圈处连接到所有字线。连接取决于底层字线布局的体系结构,以及连接器导电线的体系结构。然而,这些圆圈图示了可以进行连接的地方。在一个示例中,单个触点连接到阶梯中的多个地方。在一个示例中,触点连接到阶梯上的单个地方。

48.图300图示了半隔离的活跃触点342,它可以是沿着阶梯320的同一阶的任何触点。还图示了其他活跃触点的可能位置。图300包括虚设触点344的表示。虽然不一定是按比例的,但将会理解,虚设触点的直径比半隔离活跃触点342更小。虚设触点344连接到上层连接器,但不连接到3d阶梯堆叠中的字线。

49.图4a是在半隔离连接器的隔离侧具有虚设连接器的电路的截面的示例的表示。电路402表示与图1的电路100一致的电路的示例。电路402包括在其上构建电路的衬底410。层412表示字线层,并且为电路402提供3d阶梯堆叠。

50.活跃触点426将(一个或多个)连接器420连接到层412的字线。触点422表示半隔离触点。虚设触点424表示虚设触点。虚设触点424是触点422的隔离侧的虚设触点。从而,虚设触点424在触点422的没有其他活跃触点的一侧。

51.将会理解,触点和层412的数目是用于说明的,而不一定代表实际系统;更确切地说,在电路402中可以有更多或更少的层和关联的触点。在电路402的示例中,触点422在阶梯的顶部。在另一个实现方式中,阶梯底部的触点可以是半隔离触点。

52.图4b是在半隔离连接器的任一侧具有虚设连接器的电路的截面的示例的表示。电路404表示与图1的电路100一致的电路的示例。电路404包括在其上构建电路的衬底430。层432表示字线层,并且为电路404提供3d阶梯堆叠。

53.活跃触点446将(一个或多个)连接器440连接到层432的字线。触点442表示半隔离触点。虚设触点444-1和444-2表示虚设触点。虚设触点444-1是在触点442的隔离侧的虚设触点,而虚设触点444-2是在触点442的非隔离侧的虚设触点。从而,虚设触点444-1在触点

442的没有其他活跃触点的一侧,而虚设触点444-2在触点442的有其他活跃触点的一侧。

54.将会理解,触点和层432的数目是用于说明的,而不一定代表实际系统;更确切地说,在电路404中可以有更多或更少的层和关联的触点。在电路404的示例中,触点442在阶梯的顶部。在另一个实现方式中,阶梯底部的触点可以是半隔离触点。

55.图4c是在半隔离连接器的隔离侧具有多个虚设连接器的电路的截面的示例的表示。电路406表示与图1的电路100一致的电路的示例。电路406包括在其上构建电路的衬底450。层452表示字线层,并且为电路406提供3d阶梯堆叠。

56.活跃触点466将(一个或多个)连接器460连接到层452的字线。触点462表示半隔离触点。虚设触点464-1、464-2和464-3表示虚设触点。虚设触点464-1和虚设触点464-2是在触点462的隔离侧的虚设触点,那里没有其他活跃触点。虚设触点464-3是在触点462的非隔离侧的虚设触点,那里有其他活跃触点。从而,电路406包括隔离侧的两个虚设触点和非隔离侧的一个虚设触点。可以使用隔离侧的多于两个浮动触点。

57.将会理解,触点和层452的数目是用于说明的,而不一定代表实际系统;更确切地说,在电路406中可以有更多或更少的层和关联的触点。在电路406的示例中,触点462在阶梯的顶部。在另一个实现方式中,阶梯底部的触点可以是半隔离触点。

58.图4d是在半隔离连接器的任一侧具有多个虚设连接器的电路的截面的示例的表示。电路408表示与图1的电路100一致的电路的示例。电路408包括在其上构建电路的衬底470。层472表示字线层,并且为电路408提供3d阶梯堆叠。

59.活跃触点486将(一个或多个)连接器480连接到层472的字线。触点482表示半隔离触点。虚设触点484-1、484-2、484-3和484-4表示虚设触点。虚设触点484-1和虚设触点484-2是在触点482的隔离侧的虚设触点,那里没有其他活跃触点。虚设触点484-3和虚设触点484-4是在触点482的非隔离侧的虚设触点,那里有其他活跃触点。从而,电路408包括隔离侧的两个虚设触点和非隔离侧的两个虚设触点。可以使用任一侧的多于两个浮动触点。

60.将会理解,触点和层472的数目是用于说明的,而不一定代表实际系统;更确切地说,在电路408中可以有更多或更少的层和关联的触点。在电路408的示例中,触点482在阶梯的顶部。在另一个实现方式中,阶梯底部的触点可以是半隔离触点。

61.图5是在阶梯区域的不同区域中的半隔离连接器附近具有虚设连接器的电路的截面的示例的表示。电路500表示与图1的电路100一致的电路的示例。电路500包括在其上构建电路的衬底510。层512表示字线层,并且为电路500提供3d阶梯堆叠。电路500说明了一个示例,在阶梯的顶部有触点522,它可以是半隔离触点,并且在阶梯的底部有触点532,它可以是半隔离触点。

62.活跃触点526将(一个或多个)连接器520连接到层512的字线。虚设触点524-1和524-2表示触点522的虚设触点。虚设触点524-1是在触点522的隔离侧的虚设触点。虚设触点524-2是在触点522的非隔离侧的虚设触点。虚设触点534-1和534-2表示触点532的虚设触点。虚设触点534-1是在触点532的隔离侧的虚设触点。虚设触点534-2是在触点532的非隔离侧的虚设触点。对于上部和下部半隔离触点都可以使用至少一个浮动触点。按照图4a-4d所示,任一者或者两者可以使用多于一个浮动触点。

63.将会理解,触点和层512的数目是用于说明的,而不一定代表实际系统;更确切地说,在电路500中可以有更多或更少的层和关联的触点。

64.图6是与不使用虚设连接器时相比,当使用虚设连接器时的块故障的示例的图解表示。图600图示了具有阶梯区域的电路的测试的映射。图上的每个加号“ ”和每个圆圈“o”表示被测试的单独电路。

65.这些电路在处理之后被测试故障。圆圈表示用传统电路处理方法来处理的电路。加号表示使用布局变化来消除工艺薄弱部位的电路;更具体而言,工艺变化是包括了虚设触点或浮动触点。更具体而言,由加号标记的电路表示具有两个浮动触点的电路:一个在半隔离触点的隔离侧,一个在非隔离侧。

66.轴612(x轴)标识了用于创建存储器设备的晶圆的尺寸,并且被指定为场半径,从10mm到140mm。轴614(y轴)标识了具有归因于蚀刻不足或穿通蚀刻的故障的设备的百分比。

67.曲线620表示对具有虚设触点的电路的图点的统计分析。曲线630表示对没有虚设触点的电路的图点的统计分析。将会观察到,曲线630在半径为70-130mm的情况下,故障率大约为40%。曲线620显示了显著的改善,在相同的范围上故障率接近零。曲线620在大约110mm处确实开始微升,在130mm处故障率上升到大约10%。然而,故障率显著低于没有虚设触点的相同工艺。从而,可以得出结论,使用虚设触点显著降低了故障率。

68.图7a是具有固态驱动器(ssd)的硬件视图的系统的示例的框图,该固态驱动器具有非易失性阵列,该非易失性阵列具有虚设连接器。系统702表示非易失性存储系统的组件,该系统可以按照图1的电路100实现具有阶梯结构和浮动触点的非易失性介质。

69.系统702包括与主机710耦合的ssd 720。主机710表示连接到ssd 720的主机硬件平台。主机710包括cpu(中央处理单元)712或者其他处理器作为主机处理器或主机处理器设备。cpu 712表示生成访问存储在ssd 720上的数据的请求的任何主机处理器,无论是读取数据还是将数据写入到存储装置。这样的处理器可包括单核或多核处理器,计算设备的主处理器,图形处理器,外围处理器,或者补充或辅助处理器,或者其组合。cpu 712可以执行主机os和其他应用以引起系统702的操作。

70.主机710包括芯片组714,它表示在连接cpu 712和ssd 720之间时可包括的硬件组件。例如,芯片组714可包括互连电路和逻辑,以实现对ssd 720的访问。从而,主机平台710可包括硬件平台驱动器互连,以将ssd 720耦合到主机710。主机710包括硬件来与ssd互连。同样地,ssd720包括相应的硬件来与主机710互连。

71.主机710包括控制器716,它表示主机侧的存储控制器或存储器控制器,以控制对ssd 720的访问。在一个示例中,控制器716被包括在芯片组714中。在一个示例中,控制器716被包括在cpu 712中。控制器716可以被称为nv存储器控制器,以使得主机710能够调度和组织对ssd 720的命令,以读取和写入数据。

72.ssd 720表示固态驱动器或其他存储系统或模块,其包括非易失性(nv)介质730来存储数据。ssd 720包括hw(硬件)接口722,它表示与主机710对接的硬件组件。例如,hw接口722可以与一个或多个总线相对接,以实现高速接口标准,例如nvme或pcie。

73.在一个示例中,ssd 720包括nv(非易失性)介质730作为ssd 720的主要存储装置。在一个示例中,nv介质730是或者包括可块寻址的存储器技术,例如nand(与非)或nor(或非)。在一个示例中,nv介质730可包括非易失性的、可字节寻址的介质,其基于存储器单元的电阻状态,或者存储器单元的相位,来存储数据。例如,nv介质730可以是或者可以包括三维交叉点(3dxp)存储器或者基于硫属化合物相变材料(例如,硫属化合物玻璃)的存储阵

列。在一个示例中,nv介质可以是或者可以包括多阈值级别nand闪存、nor闪存、单级或多级相变存储器(phase change memory,pcm)或者带开关的相变存储器(phase change memory with a switch,pcms)、电阻式存储器、纳米线存储器、铁电晶体管随机访问存储器(ferroelectric transistor random access memory,fetram)、包含了记忆体技术的磁阻随机访问存储器(magnetoresistive random access memory,mram)存储器、或者自旋转移矩(spin transfer torque,stt)-mram,或者上述任何存储器的组合,或者其他存储器。

74.在一个示例中,nv介质730被实现为多个管芯,图示为n个管芯,die[0:{n-1)]。n可以是任何器件数目,并且经常是二进制数字。ssd 720包括控制器740来控制对nv介质730的访问。控制器740表示ssd 720内的硬件和控制逻辑,以执行对介质的控制。控制器740在非易失性存储设备或模块的内部,并且与主机710的控制器716分开。

[0075]

nv介质730的nv管芯包括nv阵列732,它是基于nv介质的存储单元的阵列。nv阵列732包括按照本文的任何示例的阶梯结构。在一个示例中,nv阵列732包括按照对虚设触点或浮动触点的任何描述的虚设连接器734。虚设连接器734连接到连接层,但并不完全通过隔离层延伸到阶梯结构的字线。

[0076]

图7b是具有固态驱动器(ssd)的系统的逻辑视图的示例的框图,该固态驱动器具有非易失性阵列,该非易失性阵列具有虚设连接器。系统704提供了与图7a的系统702一致的系统的一个示例。系统704图示了按照系统702的硬件平台的主机和ssd的逻辑层。系统704可以表示系统702的示例的软件和固件组件,以及物理组件。在一个示例中,主机750提供主机710的一个示例。在一个示例中,ssd 760提供ssd 720的一个示例。

[0077]

在一个示例中,主机750包括主机os 752,它表示主机操作系统或主机的软件平台。主机os 752可包括应用、服务、代理和/或其他软件在其上执行的平台,并且由处理器执行。文件系统754表示用于控制对nv介质的访问的控制逻辑。文件系统754可以管理什么地址或存储器位置被用来存储什么数据。有许多已知的文件系统,并且文件系统754可以实现已知的文件系统或其他专属系统。在一个示例中,文件系统754是主机os752的一部分。

[0078]

存储驱动器756表示控制主机750的硬件的一个或多个系统级模块。在一个示例中,驱动器756包括软件应用来控制到ssd 760的接口,从而控制ssd 760的硬件。存储驱动器756可以提供主机和ssd之间的通信接口。

[0079]

ssd 760的控制器770包括固件774,它表示控制器的控制软件/固件。在一个示例中,控制器770包括主机接口772,它表示到主机750的接口。在一个示例中,控制器770包括介质接口776,它表示到nand管芯762的接口。nand管芯762表示nv介质的具体示例,并且包括关联的nand阵列764。虚设连接器766表示按照本文的任何示例的虚设连接器或虚设触点。虚设连接器将被理解为分布在整个nand阵列764中它们被用来减小半隔离字线触点的隔离度的任何地方。

[0080]

介质接口776表示在控制器770的硬件上执行的控制。将会理解,控制器770包括与主机750对接的硬件,这可以被认为是由主机接口软件/固件774控制。同样地,将会理解,控制器770包括与nand管芯762对接的硬件。在一个示例中,用于主机接口772的代码可以是固件774的一部分。在一个示例中,用于介质接口776的代码可以是固件774的一部分。

[0081]

在一个示例中,控制器770包括差错控制780,以处理访问的数据中的数据差错,以及在符合信令和通信接口方面的极端情况。差错控制780可以包括硬件或固件的实现方式,

或者硬件和软件的组合。

[0082]

图8是用于创建具有虚设连接器支柱的阶梯区域的过程的示例的流程图。过程800使得能够创建一个或多个虚设连接器。假设有单独的过程来确定在电路中是否需要虚设连接器。

[0083]

在一个示例中,在802,处理硬件在衬底上创建nv层。在典型过程中,这些层最初可以是平面层。材料层可以被覆盖层覆盖,并且处理硬件在804处蚀刻覆盖层和底层nv层,以形成或创建阶梯结构。将会理解,该阶梯结构具有在阶梯的顶部的区域和在阶梯的底部的区域。

[0084]

在一个示例中,在806,处理硬件在阶梯结构上创建掩模层。然后,在808,处理硬件可以创建从顶部层到阶梯结构的垂直触点通道。在一个示例中,在810,处理硬件创建一个或多个接近半隔离垂直连接器的虚设垂直触点通道。可以用用于创建实际字线触点的相同处理方法来执行虚设触点的创建。在812,处理硬件可以将垂直连接器连接到上层或访问层中的触点。

[0085]

图9是计算系统的示例的框图,在该计算系统中可以实现在半隔离区域中具有虚设连接器的非易失性介质。系统900表示按照本文的任何示例的计算设备,并且可以是膝上型计算机、桌面型计算机、平板计算机、服务器、游戏或娱乐控制系统、嵌入式计算设备、或者其他电子设备。系统900提供了系统的示例,该系统可以包含与图1的电路100一致的存储电路。

[0086]

在一个示例中,系统900包括带有nv阵列988的存储装置984。nv阵列988可以是例如nand阵列。nv阵列988包括接近否则将是半隔离的字线垂直连接器的一个或多个虚设连接器990。nv阵列988可以按照本文的任何示例实现虚设连接器990。虽然是在存储装置984中示出的,但将会理解,对于可字节寻址的nv存储器,具有虚设连接器的nv阵列可被包括在存储器930中。

[0087]

系统900包括处理器910,该处理器可包括任何类型的微处理器、中央处理单元(central processing unit,cpu)、图形处理单元(graphics processing unit,gpu)、处理核心、或者其他处理硬件、或者这些的组合,以为系统900提供指令的处理或执行。处理器910控制系统900的整体操作,并且可以是或者可以包括一个或多个可编程通用或专用微处理器、数字信号处理器(digital signal processor,dsp)、可编程控制器、专用集成电路(application specific integrated circuit,asic)、可编程逻辑器件(programmable logic device,pld)、或者这种设备的组合。

[0088]

在一个示例中,系统900包括与处理器910耦合的接口912,它可以代表更高速度的接口或者高吞吐量接口,用于需要更高带宽连接的系统组件,例如存储器子系统920或图形接口组件940。接口912代表接口电路,它可以是独立的组件,或者可被集成到处理器管芯上。接口912可以作为电路被集成到处理器管芯上,或者作为组件被集成在片上系统上。如果存在,则图形接口940与图形组件相对接,用于向系统900的用户提供视觉显示。图形接口940可以是独立的组件,或者被集成到处理器管芯或片上系统上。在一个示例中,图形接口940可以驱动向用户提供输出的高清晰度(high definition,hd)显示器或超高清(ultra high definition,uhd)显示器。在一个示例中,显示器可包括触摸屏显示器。在一个示例中,图形接口940基于存储在存储器930中的数据或基于由处理器910执行的操作或这两者

而生成显示。

[0089]

存储器子系统920代表系统900的主存储器,并且为将由处理器910执行的代码或者在执行例程时将要使用的数据值提供存储。存储器子系统920可包括一个或多个存储器设备930,例如只读存储器(read-only memory,rom)、闪存、一个或多个品种的随机访问存储器(random access memory,ram)(比如dram)、3dxp(三维交叉点)、或者其他存储器设备、或者这种设备的组合。存储器930存储和容宿——除其他外——操作系统(os)932,以为系统900中的指令的执行提供软件平台。此外,应用934可以从存储器930在os 932的软件平台上执行。应用934代表具有其自己的操作逻辑的程序,以执行一个或多个功能的执行。进程936代表向os 932或一个或多个应用934或者其组合提供辅助功能的代理或例程。os 932、应用934和进程936提供软件逻辑以为系统900提供功能。在一个示例中,存储器子系统920包括存储器控制器922,它是用于生成和发出命令给存储器930的存储器控制器。将会理解,存储器控制器922可以是处理器910的物理部分或者接口912的物理部分。例如,存储器控制器922可以是集成的存储器控制器,与处理器910一起被集成到电路上,例如被集成到处理器管芯或片上系统上。

[0090]

虽然没有具体图示,但将会理解,系统900可包括设备之间的一个或多个总线或总线系统,例如存储器总线、图形总线、接口总线或者其他。总线或其他信号线可以将组件通信地或电气地耦合在一起,或者同时将组件通信地且电气地耦合。总线可包括物理通信线路、点到点连接、桥接器、适配器、控制器、或者其他电路或者这些的组合。总线可包括例如以下各项中的一个或多个:系统总线、外围组件互连(peripheral component interconnect,pci)总线、hypertransport或工业标准体系结构(industry standard architecture,isa)总线、小型计算机系统接口(small computer system interface,scsi)总线、通用串行总线(universal serial bus,usb)、或者其他总线、或者这些的组合。

[0091]

在一个示例中,系统900包括接口914,它可以耦合到接口912。接口914可以是比接口912更低速度的接口。在一个示例中,接口914代表接口电路,它可包括独立的组件和集成电路。在一个示例中,多个用户接口组件或外围组件或者这两者耦合到接口914。网络接口950向系统900提供通过一个或多个网络与远程设备(例如,服务器或其他计算设备)通信的能力。网络接口950可包括以太网适配器、无线互连组件、蜂窝网络互连组件、usb(通用串行总线)、或者其他基于有线或无线标准的或专有的接口。网络接口950可以与远程设备交换数据,这可包括发送存储在存储器中的数据或者接收要存储在存储器中的数据。

[0092]

在一个示例中,系统900包括一个或多个输入/输出(i/o)接口960。i/o接口960可包括一个或多个接口组件,用户通过这些接口组件与系统900进行交互(例如,音频、字母数字、触觉/触摸或者其他接口)。外围接口970可包括上文没有具体提到的任何硬件接口。外设一般是指依赖性地连接到系统900的设备。依赖性连接是指这样的连接:系统900提供软件平台或硬件平台或者这两者,操作在该平台上执行,并且用户与该平台进行交互。

[0093]

在一个示例中,系统900包括存储子系统980,来以非易失方式存储数据。在一个示例中,在某些系统实现方式中,存储装置980的至少某些组件可以与存储器子系统920的组件重叠。存储子系统980包括(一个或多个)存储设备984,其可以是或者可以包括用于以非易失性方式存储大量数据的任何常规介质,例如一个或多个磁性的、固态的、3dxp或者基于光学的盘,或者这些的组合。存储装置984以持久的状态保存代码或指令和数据986(即,尽

管到系统900的电力中断,该值仍被保留)。存储装置984可以被笼统地认为是“存储器”,虽然存储器930通常是执行或操作存储器,以提供指令给处理器910。存储装置984是非易失性的,而存储器930可包括易失性存储器(即,如果到系统900的电力被中断,数据的值或状态是不确定的)。在一个示例中,存储子系统980包括控制器982来与存储装置984相对接。在一个示例中,控制器982是接口914或处理器910的物理部分,或者可包括处理器910和接口914两者中的电路或逻辑。

[0094]

电源902向系统900的组件提供电力。更具体而言,电源902通常与系统900中的一个或多个电力供应源904相对接,以向系统900的组件提供电力。在一个示例中,电力供应源904包括ac到dc(交流电到直流电)适配器,以插入到壁式插座中。这种ac电力可以是可再生能量(例如,太阳能)电源902。在一个示例中,电源902包括dc电源,例如外部ac到dc转换器。在一个示例中,电源902或电力供应源904包括无线充电硬件,以经由接近充电场来充电。在一个示例中,电源902可包括内部电池或燃料电池源。

[0095]

图10是移动设备的示例的框图,在该移动设备中可以实现在半隔离区域中具有虚设连接器的非易失性介质。系统1000表示移动计算设备,例如计算平板设备、移动电话或智能电话、可穿戴计算设备、或者其他移动设备、或者嵌入式计算设备。将会理解,某些组件被概括示出,并且在系统1000中没有示出这种设备的所有组件。系统1000提供了系统的示例,该系统可以包含与图1的电路100一致的存储电路。

[0096]

在一个示例中,系统1000包括带有nv阵列1066的存储器1062。nv阵列1066可以是例如nand阵列。nv阵列1066包括接近否则将是半隔离的字线垂直连接器的一个或多个虚设连接器1090。nv阵列1066可以按照本文的任何示例实现虚设连接器1090。

[0097]

系统1000包括处理器1010,它执行系统1000的主要处理操作。处理器1010可包括一个或多个物理设备,例如微处理器、应用处理器、微控制器、可编程逻辑器件、或者其他处理装置。处理器1010执行的处理操作包括对其上执行应用和设备功能的操作平台或操作系统的执行。处理操作包括关于与人类用户或与其他设备的i/o(输入/输出)的操作、关于功率管理的操作、关于将系统1000连接到另一设备的操作,或者这些的组合。处理操作还可包括与音频i/o、显示i/o或其他接口有关的操作,或者这些的组合。处理器1010可以执行存储在存储器中的数据。处理器1010可以写入或编辑存储在存储器中的数据。

[0098]

在一个示例中,系统1000包括一个或多个传感器1012。传感器1012代表嵌入式传感器或与外部传感器的接口,或者这些的组合。传感器1012使得系统1000能够监视或检测其中实现系统1000的环境或设备的一个或多个条件。传感器1012可包括环境传感器(例如温度传感器、运动检测器、光检测器、相机、化学传感器(例如,一氧化碳、二氧化碳或其他化学传感器))、压力传感器、加速度计、陀螺仪、医疗或生理学传感器(例如,生物传感器、心率监视器、或者其他检测生理属性的传感器)、或者其他传感器、或者这些的组合。传感器1012还可包括用于生物识别系统的传感器,例如指纹识别系统、面部检测或识别系统、或者检测或识别用户特征的其他系统。传感器1012应当被广泛地理解,而不是对可以结合系统1000实现的许多不同类型的传感器进行限制。在一个示例中,一个或多个传感器1012经由与处理器1010集成的前端电路耦合到处理器1010。在一个示例中,一个或多个传感器1012经由系统1000的另一组件耦合到处理器1010。

[0099]

在一个示例中,系统1000包括音频子系统1020,该音频子系统代表与向计算设备

提供音频功能相关联的硬件(例如,音频硬件和音频电路)和软件(例如,驱动器、编解码器)组件。音频功能可包括扬声器或耳机输出,以及麦克风输入。用于这种功能的设备可被集成到系统1000中,或者连接到系统1000。在一个示例中,用户通过提供被处理器1010接收和处理的音频命令来与系统1000交互。

[0100]

显示子系统1030代表提供视觉显示来呈现给用户的硬件(例如,显示设备)和软件组件(例如,驱动器)。在一个示例中,显示器包括触觉组件或触摸屏元件,以便用户与计算设备进行交互。显示子系统1030包括显示接口1032,该显示接口包括用于向用户提供显示器的特定屏幕或硬件设备。在一个示例中,显示接口1032包括与处理器1010(例如图形处理器)分离的执行与显示器有关的至少一些处理的逻辑。在一个示例中,显示子系统1030包括向用户提供输出和输入两者的触摸屏设备。在一个示例中,图形子系统1030包括向用户提供输出的高清晰度(hd)或超高清(uhd)显示器。在一个示例中,显示子系统包括或驱动触摸屏显示器。在一个示例中,显示子系统1030基于存储在存储器中的数据或者基于由处理器1010执行的操作或者这两者而生成显示信息。

[0101]

i/o控制器1040代表关于与用户的交互的硬件设备和软件组件。i/o控制器1040可进行操作来管理作为音频子系统1020和/或显示子系统1030或者这两者的一部分的硬件。此外,i/o控制器1040例示了用于连接到系统1000的附加设备的连接点,通过这些附加设备用户可以与系统进行交互。例如,可被附接到系统1000的设备可包括麦克风设备、扬声器或立体声系统、视频系统或其他显示设备、键盘或小键盘设备、按钮/开关、或者用于特定应用的其他i/o设备,例如读卡器或其他设备。

[0102]

如上所述,i/o控制器1040可与音频子系统1020和/或显示子系统1030或者这两者进行交互。例如,通过麦克风或其他音频设备的输入可以为系统1000的一个或多个应用或功能提供输入或命令。此外,取代显示输出,或者除了显示输出以外,可提供音频输出。在另一示例中,如果显示子系统包括触摸屏,则显示设备也充当输入设备,这可至少部分由i/o控制器1040来管理。在系统1000上也可以有额外的按钮或开关来提供由i/o控制器1040管理的i/o功能。

[0103]

在一个示例中,i/o控制器1040管理诸如加速度计、相机、光传感器或其他环境传感器、陀螺仪、全球定位系统(global positioning system,gps)之类的设备,或者可被包括在系统1000或传感器1012中的其他硬件。输入可以是直接用户交互的一部分,以及向系统提供环境输入以影响其操作(例如对噪声进行过滤,调整显示器以进行亮度检测,对相机应用闪光灯,或者其他特征)。

[0104]

在一个示例中,系统1000包括电力管理1050,其管理电池电力使用、电池的充电、以及与节电操作有关的特征。电力管理1050管理来自电源1052的电力,该电源向系统1000的组件提供电力。在一个示例中,电源1052包括ac到dc(交流电到直流电)适配器,以插入到壁式插座中。这种ac电力可以是可再生能量(例如,太阳能、基于运动的电力)。在一个示例中,电源1052包括仅dc电力,这可由dc电源提供,例如外部ac到dc转换器。在一个示例中,电源1052包括无线充电硬件,以经由接近充电场来充电。在一个示例中,电源1052可包括内部电池或燃料电池源。

[0105]

存储器子系统1060包括用于存储系统1000中的信息的(一个或多个)存储器设备1062。存储器子系统1060可包括非易失性存储器设备(如果到存储器设备的电力被中断,状

态不会变化)或者易失性存储器设备(如果到存储器设备的电力被中断,则状态不确定),或者这些的组合。存储器1060可存储应用数据、用户数据、音乐、照片、文档或其他数据,以及与系统1000的应用和功能的执行有关的系统数据(无论是长期的还是暂时的)。在一个示例中,存储器子系统1060包括存储器控制器1064(它也可以被认为是系统1000的控制的一部分,并且有可能被认为是处理器1010的一部分)。存储器控制器1064包括调度器,用于生成和发出命令,以控制对存储器设备1062的访问。

[0106]

连通性1070包括硬件设备(例如,无线或有线连接器和通信硬件,或者有线和无线硬件的组合)和软件组件(例如,驱动器、协议栈)来使得系统1000能够与外部设备进行通信。外部设备可以是分开的设备,例如其他计算设备、无线接入点或基站,以及诸如耳麦、打印机或其他设备之类的外设。在一个示例中,系统1000与外部设备交换数据以存储在存储器中或显示在显示设备上。交换的数据可包括要存储在存储器中的数据,或者已经存储在存储器中的数据,以读取、写入或编辑数据。

[0107]

连通性1070可包括多种不同类型的连通性。概括而言,系统1000被图示为具有蜂窝连通性1072和无线连通性1074。蜂窝连通性1072一般指的是由无线运营商提供的蜂窝网络连通性,例如经由gsm(global system for mobile communications,全球移动通信系统)或变体或衍生、cdma(code division multiple access,码分多址接入)或变体或衍生、tdm(time division multiplexing,时分复用)或变体或衍生、lte(长期演进—也称为“4g”)、5g或者其他蜂窝服务标准提供。无线连通性1074指的是非蜂窝的无线连通性,并且可包括个人区域网(例如蓝牙)、局域网(例如wi-fi)或者广域网(例如wimax),或者其他无线通信,或者这些的组合。无线通信是指通过使用经调制的电磁辐射通过非固体介质进行数据传送。有线通信是通过固体通信介质发生的。

[0108]

外围连接1080包括硬件接口和连接器,以及软件组件(例如,驱动器、协议栈)来进行外围连接。将会理解,系统1000既可以是其他计算设备的外围设备(“去往”1082),也可以有外围设备连接到它(“来自”1084)。系统1000通常具有“坞接”连接器来连接到其他计算设备,以便例如管理系统1000上的内容(例如,下载、上传、改变、同步)。此外,坞接连接器可允许系统1000连接到某些外设,这些外设允许系统1000控制例如到视听或其他系统的内容输出。

[0109]

除了专属坞接连接器或其他专属连接硬件以外,系统1000还可经由常见的或者基于标准的连接器来进行外围连接1080。常见类型可包括通用串行总线(usb)连接器(其可包括若干种不同硬件接口中的任何一种)、包括minidisplayport(mdp)的displayport,高清晰度多媒体接口(high definition multimedia interface,hdmi)、或者其他类型。

[0110]

一般而言,关于本文的描述,在一个示例中,一种存储器设备包括:堆叠在三维(3d)阶梯堆叠中的多条字线,包括在所述阶梯堆叠的边缘处的第一字线,该第一字线在一侧有相邻字线,而在相反侧没有相邻字线;以及垂直连接器,其穿过所述3d阶梯堆叠上的隔离层来将所述3d阶梯堆叠的字线与访问层中的导电线相连接,所述垂直连接器包括在所述第一字线的所述相反侧的至少一个虚设垂直连接器,其中所述虚设垂直连接器不将所述3d阶梯堆叠的字线电连接到所述访问层中的导电线。

[0111]

在一个示例中,所述虚设垂直连接器没有完全穿过所述隔离层延伸到所述字线。在一个示例中,所述虚设垂直连接器连接到所述3d阶梯堆叠中的字线,而不连接到所述访

问层中的导电线。在一个示例中,所述虚设垂直连接器包括第一虚设垂直连接器,并且还包括第二虚设垂直连接器,其中所述第二虚设垂直连接器不将所述3d阶梯堆叠的字线电连接到所述访问层中的导电线。在一个示例中,所述第一虚设垂直连接器位于所述第一字线的所述相反侧并且所述第二虚设垂直连接器位于所述第一字线的所述一侧。在一个示例中,所述第一虚设垂直连接器位于所述第一字线的所述相反侧并且所述第二虚设垂直连接器位于所述第一字线的所述相反侧。在一个示例中,所述存储器设备还包括第三虚设垂直连接器,其中所述第三虚设垂直连接器不将所述3d阶梯堆叠的字线电连接到所述访问层中的导电线,所述第三虚设垂直连接器位于所述第一字线的所述一侧。在一个示例中,所述第一字线是所述3d阶梯堆叠的一区域中的顶层。在一个示例中,所述第一字线是所述3d阶梯堆叠的一区域中的底层。在一个示例中,所述虚设垂直连接器的直径小于将所述3d阶梯堆叠的字线与访问层中的导电线相连接的垂直连接器的直径。在一个示例中,所述3d阶梯堆叠包括nand闪存存储器设备的字线的3d堆叠。

[0112]

一般而言,关于本文的描述,在一个示例中,一种系统包括:非易失性(nv)存储器控制器;以及与所述nv存储器控制器相耦合的nv存储器的多个管芯,所述nv存储器管芯包括堆叠在三维(3d)阶梯堆叠中的多条字线,包括在所述阶梯堆叠的边缘处的第一字线,该第一字线在一侧有相邻字线,而在相反侧没有相邻字线;以及垂直连接器,其穿过所述3d阶梯堆叠上的隔离层来将所述3d阶梯堆叠的字线与访问层中的导电线相连接,所述垂直连接器包括在所述第一字线的所述相反侧的至少一个虚设垂直连接器,其中所述虚设垂直连接器不将所述3d阶梯堆叠的字线电连接到所述访问层中的导电线。

[0113]

在一个示例中,所述虚设垂直连接器没有完全穿过所述隔离层延伸到所述字线。在一个示例中,所述虚设垂直连接器包括第一虚设垂直连接器,并且还包括第二虚设垂直连接器,其中所述第二虚设垂直连接器不将所述3d阶梯堆叠的字线电连接到所述访问层中的导电线。在一个示例中,所述第一虚设垂直连接器位于所述第一字线的所述相反侧并且所述第二虚设垂直连接器位于所述第一字线的所述一侧。在一个示例中,所述第一虚设垂直连接器位于所述第一字线的所述相反侧并且所述第二虚设垂直连接器位于所述第一字线的所述相反侧。

[0114]

在一个示例中,所述nv存储器管芯还包括第三虚设垂直连接器,其中所述第三虚设垂直连接器不将所述3d阶梯堆叠的字线电连接到所述访问层中的导电线,所述第三虚设垂直连接器位于所述第一字线的所述一侧。在一个示例中,所述第一字线是所述3d阶梯堆叠的一区域中的顶层。在一个示例中,所述第一字线是所述3d阶梯堆叠的一区域中的底层。在一个示例中,所述虚设垂直连接器的直径小于将所述3d阶梯堆叠的字线与访问层中的导电线相连接的垂直连接器的直径。在一个示例中,所述3d阶梯堆叠包括nand(与非)存储器设备的字线的3d堆叠。在一个示例中,所述系统还包括以下各项中的一个或多个:与所述多个管芯相耦合的主机处理器设备;与主机处理器通信地耦合的显示器;与主机处理器通信地耦合的网络接口;或者为所述系统供电的电池。

[0115]

本文图示的流程图提供了各种过程动作的序列的示例。流程图可指示出要被软件或固件例程执行的操作,以及物理操作。流程图可图示出有限状态机(finite state machine,fsm)的状态的实现方式的示例,该有限状态机可以用硬件和/或软件来实现。虽然是按特定的序列或顺序示出的,但除非另有指明,否则可以修改动作的顺序。从而,图示的

附图应当只被理解为示例,而过程可按不同的顺序被执行,并且一些动作可被并行执行。此外,可省略一个或多个动作;从而,并非所有实现方式都将执行所有动作。

[0116]

在本文描述的各种操作或功能的范围内,它们可被描述或定义为软件代码、指令、配置、和/或数据。这些内容可以是直接可执行的(“对象”或“可执行”形式)、源代码、或者差异代码(“delta”或“补丁”代码)。本文描述的内容的软件内容可经由其上存储有该内容的制造品来提供,或者经由操作通信接口以经由该通信接口发送数据的方法来提供。机器可读存储介质可以使得机器执行描述的功能或操作,并且包括以机器(例如,计算设备、电子系统,等等)可访问的形式存储信息的任何机制,例如可记录/不可记录介质(例如,只读存储器(rom)、随机访问存储器(ram)、磁盘存储介质、光学存储介质、闪存设备,等等)。通信接口包括与硬连线、无线、光学等等任何一种介质相接口的任何机制,以便与另一设备进行通信,例如存储器总线接口、处理器总线接口、互联网连接、盘控制器,等等。可通过提供配置参数和/或发送信号来配置通信接口,以使得通信接口准备好提供描述软件内容的数据信号。可经由向通信接口发送的一个或多个命令或信号来访问通信接口。

[0117]

本文描述的各种组件可以是用于执行所描述的操作或功能的手段。本文描述的每个组件包括软件、硬件、或者这些的组合。这些组件可被实现为软件模块、硬件模块、专用硬件(例如,特定应用硬件、专用集成电路(asic)、数字信号处理器(dsp),等等)、嵌入式控制器、硬接线电路,等等。

[0118]

除了本文描述的内容以外,还可对所公开的内容和本发明的实现方式做出各种修改,而不脱离其范围。因此,应当从说明意义而不是限制意义上来解释本文的说明和示例。应当仅通过参考所附权利要求来衡量本发明的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。