1.本发明涉及一种半导体器件。本发明还涉及一种制造半导体器件的方法。

背景技术:

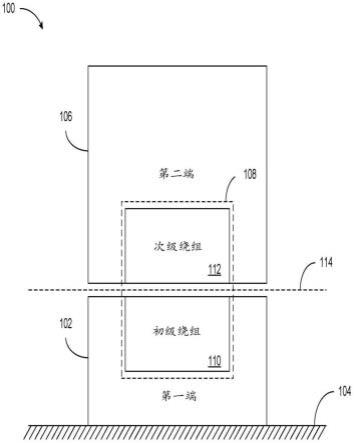

2.图1示出了一种已知的半导体器件。在这种芯片级封装(csp)产品中,已知漏极-源极导通电阻(rdson)由技术rspec10、双向电阻12、漏极侧衬底扩展电阻14和漏极侧外延(epi)扩展电阻16贡献。已知的是可以分别通过背面金属化和深的注入物或深的金属来减小双向电阻12和漏极侧epi扩展电阻16。然而,管理漏极侧衬底扩展电阻14是有困难的。该漏极侧衬底扩展电阻14对于任何电压等级都是固定的。对于低击穿(bv)电压等级,技术rdson是低的,但是总rdson将是高的,因为漏极侧衬底扩展电阻14直接加到技术rdson上。

3.在专利us9159786b2中描述了一种已知的半导体器件。该器件示于图2中。它示出了双栅极横向mosfet 100的简化横截面图。双栅极横向mosfet 100包括具有第一导电性的衬底103和从衬底103生长的具有第二导电性的外延区域102。第一漏极/源极区域112和第二漏极/源极区域114形成在衬底103上方的外延区域102中。在第一漏极/源极区域112和第二漏极/源极区域114之间形成有隔离区域104。双栅极横向mosfet进一步包括具有第一导电性的主体区域122,该主体区域122形成在衬底103上方的外延区域102中。如图2所示,主体区域形成在第二漏极/源极区域114的下方。

4.双栅极横向mosfet 100包括堆叠在一起的两个栅极。第一栅极142在第二栅极144的上方。第一栅极142和第二栅极144由介电层146隔开。第一栅极142联接至控制信号。当控制信号大于双栅极横向mosfet 100的阈值电压时,双栅极横向mosfet 100被接通。当控制信号小于阈值电压时,双栅极横向mosfet 100被关断。第二栅极144是浮置栅极。

5.侧壁介电层128和底部介电层126提供双栅极142、144与其周围的半导体区域之间的隔离。间隔物132提供第一栅极142与第二漏极/源极区域114之间的隔离。隔离区域104用于隔离有源区域,以便防止漏电流在相邻的有源区域之间流动。

技术实现要素:

6.各种示例性实施例针对如上所述的缺点和/或从以下公开内容可以变得明显的其他缺点。

7.根据本发明的实施例,一种半导体器件包括:

[0008]-衬底,

[0009]-沟道,该沟道定位在衬底的上方,

[0010]-漂移区,该漂移区定位在沟道的上方,

[0011]-第一多晶硅,该第一多晶硅定位在沟道和漂移区内,

[0012]-第二多晶硅,该第二多晶硅定位在第一多晶硅的上方并且定位在漂移区内,

[0013]-其中,第一多晶硅和第二多晶硅分别通过栅极氧化物和resurf氧化物与沟道和漂移区隔离。

[0014]

这种半导体器件确保了半导体器件的源极与漏极之间的击穿电压的显著提高。

[0015]

与第一多晶硅相比,第二多晶硅显著地更厚或为至少两倍厚。

[0016]

第二多晶硅连接至半导体器件的栅极或源极,或者它可以是浮置的。

[0017]

半导体器件可以是双向mosfet器件,或者任何其他合适的半导体器件。

[0018]

本发明还涉及一种制造半导体器件的方法。根据本发明的实施例,该方法包括以下步骤:

[0019]-形成主体;

[0020]-形成用于n沟道的n阱和用于p沟道的p阱,其中n阱和p阱形成漂移区,并且漂移区定位在主体的上方;

[0021]-蚀刻出第一沟槽;

[0022]-在第一沟槽内生长出自对准接触(sac)氧化物和栅极氧化物(gox);

[0023]-在第一沟槽中沉积第一多晶硅;

[0024]-去除第一多晶硅的顶部部分;

[0025]-在第一多晶硅的上方沉积resurf氧化物;

[0026]-在resurf氧化物的上方沉积或生长出第二多晶硅;以及

[0027]-插入高浓度注入物,以形成源极、漏极和接触开口以便拾取源极和漏极。

附图说明

[0028]

为了能够详细理解本发明公开的特征,参考实施例进行更具体的描述,其中一些实施例在附图中示出。然而,应当注意,附图仅示出了典型的实施例,因此不应被认为是对其范围的限制。附图是为了便于理解本发明公开,因此不一定按比例绘制。在结合附图阅读本描述之后,所要求保护的主题的优点对于本领域技术人员将变得显而易见,在附图中,相同的附图标记用于表示相同的元件,并且其中:

[0029]

图1示出了已知的半导体器件;

[0030]

图2示出了已知的半导体器件;

[0031]

图3示出了制造根据本发明的实施例的半导体器件的方法;

[0032]

图4示出了根据本发明的实施例的半导体器件。

具体实施方式

[0033]

图3示出了用于形成本发明实施例的半导体器件的方法。该方法包括以下步骤:

[0034]-附图标记200表示的步骤:

[0035]

o形成主体220;

[0036]

o形成用于n沟道的n阱和用于p沟道的p阱;n阱和p阱形成漂移区222;漂移区222定位在主体220的上方;

[0037]-附图标记202表示的步骤:

[0038]

o蚀刻出第一沟槽230;

[0039]

o在第一沟槽230中生长出自对准接触(sac)氧化物和栅极氧化物(gox)232;

[0040]

o在第一沟槽230中沉积第一多晶硅234;

[0041]-附图标记204表示的步骤:

[0042]

o去除第一多晶硅234的顶部部分240;

[0043]-附图标记206表示的步骤:

[0044]

o在顶部沉积或生长出resurf氧化物250;resurf氧化物确保半导体器件的击穿电压的增加;

[0045]-附图标记208表示的步骤:

[0046]

o在resurf氧化物250的上方沉积第二多晶硅260;

[0047]-附图标记210表示的步骤:

[0048]

o插入高浓度注入物270,以形成源极272、漏极274和接触开口以便拾取(pick up)源极和漏极;

[0049]

根据该方法制造的半导体器件与本领域已知的半导体器件相比具有更好的性能。第一多晶硅234是栅极多晶硅,并且其使用沟槽底部作为沟道来操作半导体器件。第二多晶硅260可以连接至栅极或源极,或者是浮置的。具有作为厚的热氧化物或沉积氧化物的resurf氧化物的第二多晶硅260显著地增加了半导体器件的击穿电压。

[0050]

图4示出了根据本发明的实施例的半导体器件300。该半导体器件300包括:

[0051]-衬底302,

[0052]-沟道304,该沟道304定位在衬底302的上方,

[0053]-漂移区306,该漂移区定位在沟道304的上方,

[0054]-第一多晶硅308,其定位在沟道304和漂移区306内,

[0055]-第二多晶硅310,其定位在第一多晶硅308的上方并且定位在漂移区306内,

[0056]-其中,第一多晶硅308和第二多晶硅310分别通过栅极氧化物312和resurf氧化物314与沟道304和漂移区306隔离。

[0057]

与第一多晶硅相比,第二多晶硅可以显著地更厚。

[0058]

半导体器件进一步包括源极316和漏极318。

[0059]

此外,第二多晶硅310可以连接至栅极或源极或者是浮置的,从而以厚的热氧化物或沉积氧化物作为resurf,以增加漏极与源极之间的击穿电压。

[0060]

半导体器件可以是双向mosfet器件或任何其他合适的半导体器件。

[0061]

本发明的特定和优选方面在所附独立权利要求中阐述。来自从属和/或独立权利要求的特征的组合可以适当地组合,而不仅仅是如权利要求中所阐述的。

[0062]

本发明的公开的范围包括明确地或隐含地公开的任何新的特征或特征的组合或其任何概括,而不管其是否涉及所要求保护的发明或减轻本发明解决的任何或所有问题。本发明的申请人特此提请注意,在本技术或从其导出的任何这种进一步申请的审查期间,可以针对这些特征提出新的权利要求。特别地,参考所附权利要求,来自从属权利要求的特征可以与独立权利要求的特征进行组合,并且来自各个独立权利要求的特征可以以任何适当的方式进行组合,而不仅仅是在权利要求中列举的特定组合。

[0063]

在单独实施例的上下文中描述的特征也可以在单个实施例中组合提供。相反,为了简洁起见,在单个实施例的上下文中描述的各种特征也可以单独地或以任何合适的子组合提供。

[0064]

术语“包括”不排除其他元件或步骤,术语“一”或“一个”不排除多个。权利要求中的附图标记不应被解释为限制权利要求的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。