一种基于多个led负载同步启动的led驱动装置

技术领域

1.本实用新型涉及led电源控制技术领域,尤其涉及一种基于多个led 负载同步启动的led驱动装置。

背景技术:

2.在led固定装置内,单个led驱动器为特定数量的led负载供电,如第一led灯组,以填充固定装置的空白空间。在实践中,灯具安装时,最大数量的led负载可适当安装在灯具内,以避免因缺少led板的空白空间而产生的灯光死区。这些负载串联连接,其中,第一个led负载的负极引线向下一个led负载的正极引线馈电。

3.单个led驱动器可以运行的负载数量限制在驱动器可以产生的最大电压范围内。串联时,每个led负载上的电压将堆叠在彼此的顶部。因此,负载电压将与连接到其上的负载数量成比例。

4.此驱动器限制规定了驱动器一次可以为其供电的串联led负载的数量。因此,可以从单个驱动器运行的led负载量可能不足以正确填充夹具,通过第二led灯组安装在现有led负载附近,以填充夹具内的可用空间,如第二led驱动器和第二led灯组的led负载,其中,第二led 灯组的led负载的数量少于第一led灯组的led负载。

5.由于夹具不平衡,驱动器将在不一致的时间向led负载供电。这可以从视觉上观察到爆米花效应,其中一个驱动器将在另一个驱动器之前供电,导致led的启动时间不一致且明显不同。

6.当在这种不平衡配置下工作时,第一驱动器的负载电压将高于第二驱动器的负载电压,并且第一驱动器将在第二驱动器通电后通电。为较低负载供电的驱动程序将比为较高负载供电的驱动程序启动更快。

7.因此,针对现有技术中led驱动电路级联应用控制信号数量较多且串行输出数据延迟的问题,目前尚未提出有效的解决方案。

技术实现要素:

8.本实用新型的主要目的是提供一种基于多个led负载同步启动的 led驱动装置,该装置可以解决现有技术中led驱动电路级联应用控制信号数量较多且串行输出数据延迟的问题,可以改善电源系统动态响应性。

9.为了实现上述主要目的,本实用新型提供的一种基于多个led负载同步启动的led驱动装置,包括led夹具、位于所述led夹具内的多路led驱动电路以及调光器,所述调光器与多路所述led驱动电路并联设置,每一路所述led驱动电路相接一led灯组,所述led驱动电路与所述led灯组的第一个led负载的正极引线连接,所述led灯组的第一个led负载的负极引线向下一个led负载的正极引线馈电,所述 led灯组的最后一个led负载的负极引线与所述led驱动电路连接,每路所述led驱动电路包括一个控制开关,该控制开关控制一路led灯组连通或阻断;所述led驱动电路还包括驱动控制电路和恒流输出电路,所述驱动控制电

路包括逻辑控制电路和时钟延迟电路,所述逻辑控制电路与所述恒流输出电路连接,用于使用逻辑控制信号控制所述恒流输出电路的有序导通或截止;所述时钟延迟电路与所述逻辑控制电路连接,用于获取与所述逻辑控制信号同步的时序控制信号,并输出所述时序控制信号至所述控制开关;其中,所述逻辑控制电路包括一误差放大器、微处理器、负载电流检测电路、误差放大器、基准电压产生电路,所述基准电压产生电路分别与所述微处理器、误差放大器连接,用于产生基准电压,向所述微处理器、误差放大器的一输入端提供基准电压,所述负载电流检测电路用于检测负载电流,并输出负载检测电压至所述误差放大器的另一输入端,所述误差放大器的输出端输出调整电压,所述微处理器基于所述基准电压向所述时钟延迟电路发送所述逻辑控制信号。

10.进一步的方案中,所述时钟延迟电路包括:计数器,用于当逻辑控制信号到达所述时钟延迟电路时,根据延迟时间进行计时;pwm信号延迟模块,用于接收逻辑控制信号,并当所述计数器的延迟时间计时完成时,输出所述时序控制信号至所述控制开关。

11.更进一步的方案中,所述pwm信号延迟模块包括移位延时输入端口、时钟延迟子电路、以及延时输出端口,其中,所述移位延时输入端口,与移位脉冲输入端口连接,用于接收所述时序控制信号;所述时钟延迟子电路,连接于所述移位延时输入端口与所述逻辑控制电路之间,用于获取与所述逻辑控制信号同步的时序控制信号;所述延时输出端口,连接于所述时钟延迟子电路与移位脉冲输出端口之间,用于输出所述时序控制信号。

12.更进一步的方案中,所述恒流输出电路包括交流输入电路、桥式全波整流器以及dc-dc输出电路,所述交流输入电路的输入端接交流电源,所述交流输入电路的输出端与所述桥式全波整流器的输入端连接,所述桥式全波整流器的输出端与所述dc-dc输出电路连接。

13.更进一步的方案中,所述交流输入电路包括交流输入端,所述交流输入端的l、n端依次连接有温度保险管f1、压敏电阻mv2、电容c1、电感l1,所述电感l1的2、4端连接至所述桥式全波整流器的输入端。

14.更进一步的方案中,所述桥式全波整流器的输出端依次连接有压敏电阻mv1、电容c4、电阻r2、电阻r204。

15.更进一步的方案中,所述dc-dc输出电路包括变压器t1、场效应管 q2以及输出整流管,所述场效应管q2连接在所述变压器t1的输入侧,所述输出整流管连接在所述变压器t1的输出侧。

16.更进一步的方案中,所述微处理器为stm32系列微处理器。

17.由此可见,本实用新型利用不同的延迟时间控制pwm信号输出,以实现对控制开关通断时刻的调控,将导出的接通延迟应用于驱动器,以便在延迟时间完成后保持驱动器关闭并尝试启动,当应用于为不平衡负载供电的驱动器时,为多个led负载供电的驱动器将比为较少led负载供电的驱动器经历更短的接通延迟,为led负载较少的驱动器提供延迟有助于更好地同步负载的开始时间。

18.此外,该控制电路通过检测负载电流的大小,以动态调节原边变压器的峰值电流,改善了系统的动态响应特性。

附图说明

19.图1是本实用新型一种基于多个led负载同步启动的led驱动装置实施例的原理图。

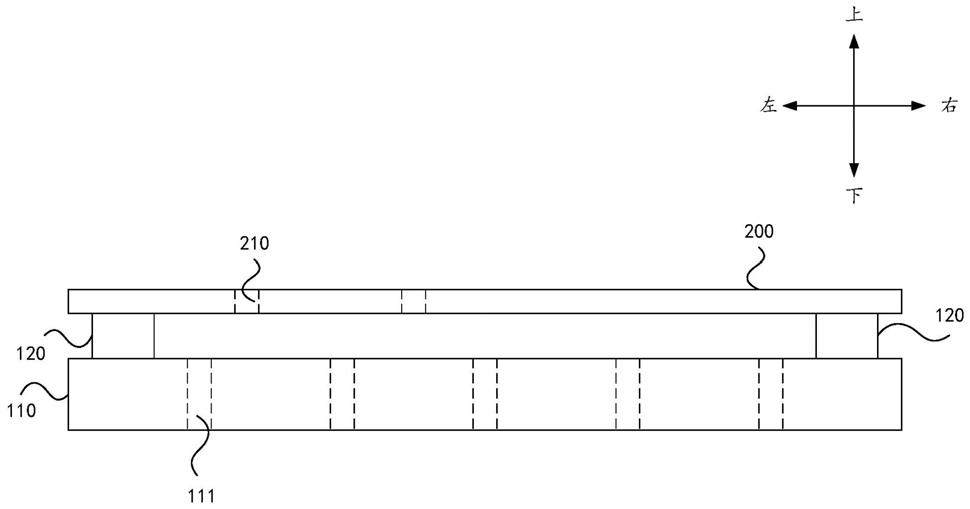

20.图2是本实用新型一种基于多个led负载同步启动的led驱动装置实施例中第一路led驱动电路、第二路led驱动电路、第一led灯组和第二led灯组的原理图。

21.图3是本实用新型一种基于多个led负载同步启动的led驱动装置实施例中led驱动电路的原理图。

22.图4是本实用新型一种基于多个led负载同步启动的led驱动装置实施例中时钟延迟电路的原理图。

23.图5是本实用新型一种基于多个led负载同步启动的led驱动装置实施例中逻辑控制电路的电路原理图。

24.图6是本实用新型一种基于多个led负载同步启动的led驱动装置实施例中交流输入电路、桥式全波整流器的电路原理图。

25.图7是本实用新型一种基于多个led负载同步启动的led驱动装置实施例中dc-dc输出电路的电路原理图。

26.以下结合附图及实施例对本实用新型作进一步说明。

具体实施方式

27.为使本实用新型实施例的目的、技术方案和优点更加清楚,下面将结合本实用新型实施例的附图,对本实用新型实施例的技术方案进行清楚、完整地描述。显然,所描述的实施例是本实用新型的一部分实施例,而不是全部的实施例。基于所描述的本实用新型的实施例,本领域普通技术人员在无需创造性劳动的前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

28.参见图1至图3,本实用新型的一种基于多个led负载同步启动的 led驱动装置,包括led夹具、位于led夹具内的多路led驱动电路 100以及调光器1,如第一路led驱动电路101和第二路led驱动电路201,调光器1与多路led驱动电路100并联设置,每一路led驱动电路100相接一led灯组2,如第一led灯组102和第二led灯组202, led驱动电路100与led灯组2的第一个led负载的正极引线连接,led 灯组2的第一个led负载的负极引线向下一个led负载的正极引线馈电, led灯组2的最后一个led负载的负极引线与led驱动电路100连接,每路led驱动电路100包括一个控制开关30,该控制开关30控制一路 led灯组2连通或阻断。

29.其中,第一led灯组102的led负载数量大于第二led灯组202 的led负载数量,第二led灯组202的led负载数量为一个,第一路 led驱动电路101与第一led灯组102的第一个led负载的正极引线连接,第一led灯组102的第一个led负载的负极引线向下一个led负载的正极引线馈电,第一led灯组102的最后一个led负载的负极引线与第一路led驱动电路101连接,第二路led驱动电路201与第二led 灯组202的led负载的正极引线、负极引线连接。

30.在本实施例中,led驱动电路100还包括驱动控制电路10和恒流输出电路20,驱动控制电路10包括逻辑控制电路11和时钟延迟电路12,逻辑控制电路11与恒流输出电路20连接,用于使用逻辑控制信号控制恒流输出电路20的有序导通或截止;时钟延迟电路12与逻

辑控制电路11 连接,用于获取与逻辑控制信号同步的时序控制信号,并输出时序控制信号至控制开关30。

31.其中,逻辑控制电路11包括一误差放大器v5、微处理器111、负载电流检测电路112、基准电压产生电路113,基准电压产生电路113分别与微处理器111、误差放大器v5连接,用于产生基准电压,向微处理器 111、误差放大器v5的一输入端提供基准电压,负载电流检测电路112用于检测负载电流,并输出负载检测电压至误差放大器v5的另一输入端,误差放大器v5的输出端输出调整电压,微处理器111基于基准电压向时钟延迟电路12发送逻辑控制信号。

32.如图4所示,时钟延迟电路12包括:计数器121,用于当逻辑控制信号到达时钟延迟电路12时,根据延迟时间进行计时;pwm信号延迟模块 122,用于接收逻辑控制信号,并当计数器121的延迟时间计时完成时,输出时序控制信号至控制开关30。

33.pwm信号延迟模块122包括移位延时输入端口1221、时钟延迟子电路1222、以及延时输出端口1223,其中,移位延时输入端口1221,与移位脉冲输入端口连接,用于接收时序控制信号;时钟延迟子电路1222,连接于移位延时输入端口1221与逻辑控制电路11之间,用于获取与逻辑控制信号同步的时序控制信号;延时输出端口1223,连接于时钟延迟子电路 1222与移位脉冲输出端口之间,用于输出时序控制信号。

34.在本实施例中,恒流输出电路20包括交流输入电路21、桥式全波整流器22以及dc-dc输出电路23,交流输入电路21的输入端接交流电源,交流输入电路21的输出端与桥式全波整流器22的输入端连接,桥式全波整流器22的输出端与dc-dc输出电路23连接。

35.如图6所示,交流输入电路21包括交流输入端j1,交流输入端j1的 l、n端依次连接有温度保险管f1、压敏电阻mv2、电容c1、电感l1,电感l1的2、4端连接至桥式全波整流器22的输入端。

36.其中,桥式全波整流器22的输出端依次连接有压敏电阻mv1、电容 c4、电阻r2、电阻r204。

37.如图7所示,dc-dc输出电路23包括变压器t1、场效应管q2以及输出整流管,场效应管q2连接在变压器t1的输入侧,输出整流管连接在变压器t1的输出侧。

38.作为优选,微处理器111为stm32系列微处理器111。

39.如图5所示,负载电流检测电路112具体可包括开关k1、开关k2、反相器以及滤波电阻rf和滤波电容cf。其中,本实用新型的开关k1、开关k2均为mos管;在误差放大器v5的输出侧连接有mos管m1、电阻r1、电阻r2、电阻r3以及电阻r4;基准电压产生电路113具体可包括:接收电路、电阻r5以及电阻r6,其中,接收电路为缓冲器。

40.其中,led驱动电路100通过观察led负载上的负载电压,并在驱动器关闭时存储该值,一旦用户再次通电,用户将使用存储的负载电压发出与存储的负载电压成比例的接通延迟。

41.每次驱动器通电时都会发生此启动延迟过程,其中,存储的负载电压用于确定驱动器的开启延迟和应用于误差放大器v5的参考电压。实时监控驱动器输出电压的微处理器111将存储负载电压,当向驱动器供电时,读取=先前存储的负载电压=并用于确定驱动器的接通延迟,将导出的接通延迟应用于驱动器,以便在延迟时间完成=后保持驱动器关闭=并尝试启动。

42.接通延迟与存储的负载电压成比例,低负载电压将导致更长的延迟,而高负载电压将导致更短的延迟,可用接通延迟时间的范围不是固定的,可以根据类型进行修改,延迟时间可以从预先编程的查找表或公式中导出。

43.在启动尝试之后,如果驱动器启动时间小于启动时间阈值,则导出参考电压并将其提供给误差放大器v5,再次存储负载电压,并继续正常操作驱动器。

44.每次驱动器通电时都会发生此过程,用于同步同一夹具内不平衡驱动器的启动时间。当应用于为平衡负载供电的驱动器时,驱动器的启动时间将彼此一致,并且驱动器将大致同时为各自的负载供电。当应用于为不平衡负载供电的驱动器时,如图2所示,为多个led负载供电的驱动器将比为较少led负载供电的驱动器经历更短的接通延迟。为led负载较少的驱动器提供延迟有助于更好地同步负载的开始时间。

45.由此可见,本实用新型利用不同的延迟时间控制pwm信号输出,以实现对控制开关30通断时刻的调控,将导出的接通延迟应用于驱动器,以便在延迟时间完成后保持驱动器关闭并尝试启动,当应用于为不平衡负载供电的驱动器时,为多个led负载供电的驱动器将比为较少led负载供电的驱动器经历更短的接通延迟,为led负载较少的驱动器提供延迟有助于更好地同步负载的开始时间。

46.此外,该控制电路通过检测负载电流的大小,以动态调节原边变压器的峰值电流,改善了系统的动态响应特性。

47.需要说明的是,以上仅为本实用新型的优选实施例,但实用新型的设计构思并不局限于此,凡利用此构思对本实用新型做出的非实质性修改,也均落入本实用新型的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。