一种基于tdc的两步式逐次逼近型模数转换器

技术领域

1.本发明属于模拟数字转换技术领域,具体涉及一种基于tdc的两步式逐次逼近型模数转换器。

背景技术:

2.逐次逼近型(sar)模数转换器(adc)凭借着其较低的功耗以及较小的芯片面积,成为中等分辨率以及中等带宽adc研究中的热门。然而,由于量化过程需要逐次进行,因此速度难以提升,同时随着分辨率的提高,比较器的功耗呈指数级增长。

3.时间数字转换器(tdc)能够不依赖比较器实现对时间的量化,将tdc和sar adc通过电压时间转换器(vtc)结合起来的的两步式数模转换器能够放松对比较器性能的要求并实现流水线量化。

4.然而传统基于tdc的两步式sar adc在sar adc完成量化后,vtc需要占用一定时间先将残差信号转换成时域信号,才能用tdc进行量化,限制了该结构的速度提升。另外,由于vtc和tdc之间存在的增益失配,将导致非线性,限制adc的动态性能。

技术实现要素:

5.针对上述存在问题或不足,为解决现有两步式sar adc存在量化速率和动态性能相对较差的问题,本发明提供了一种基于tdc的两步式逐次逼近型模数转换器。

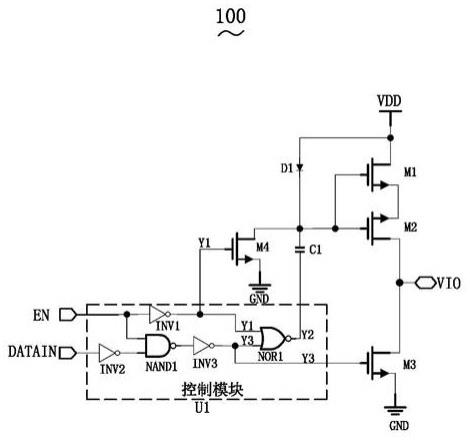

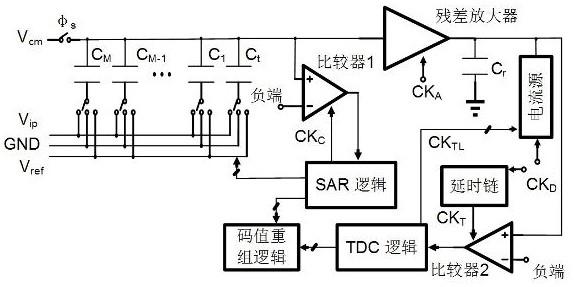

6.一种基于tdc的两步式逐次逼近型模数转换器,如图1所示(只画出正端,负端与正端结构相同),包括:dac电容阵列、比较器1、sar逻辑、残差放大器、tdc模块和码值重组逻辑。

7.所述dac电容阵列包括两组m位二进制开关电容和dummy电容c

t

,m表示sar量化位数与电容位数相同,按权重由低到高依次给m个电容编号为c1、c2、

……

、cm;dac电容阵列中的各电容上极板均连接共模电压vcm,各电容的下极板通过开关阵列分别连接输入信号vi、参考高电压vref和参考低电压gnd;共模电压vcm的电压值为参考高电压vref的电压值的一半。

8.所述比较器1由时钟ckc控制,用以产生m位sar量化码;其正负输入端分别接正负dac电容阵列,输出端接sar逻辑。

9.所述sar逻辑,根据比较器1输出结果切换dac电容阵列下极板开关,实现sar量化。同时储存m位sar量化码用于码值重组。

10.所述残差放大器由时钟cka控制,提供稳定的增益,其输入端连接dac电容阵列,输出端连接残差电容cr,将dac量化残差电压放大后保存在电容cr上。

11.所述tdc模块包含电流源、延时链、tdc逻辑和比较器2,实现n 1位的tdc量化输出,n表示tdc的初步量化位数。其中,电流源由时钟ckd控制,连接残差电容实现电压域到时域的转换;延时链也由时钟ckd控制,由2n 3个延时单元串联组成,产生方波信号控制比较器2输出2n 3个tdc量化码,tdc量化码是温度计码,后续需要转换成n 1位二进制码。tdc逻辑则

储存tdc量化码用于码值重组,同时根据码值变化产生信号ck

tl

控制电流源切换。

12.所述码值重组逻辑,在tdc模块量化完成后,将m位sar量化码值和2n 3位tdc量化码值重新组合成m n 1位二进制码。

13.进一步的,所述电流源和延时链选用相同尺寸的绝缘栅型场效应晶体管(mosfet),以减小pvt对tdc中电流源和延时链失配造成的负面影响。

14.进一步的,所述dac电容阵列采用较小的单位电容以提高sar量化速度。

15.上述基于tdc的两步式逐次逼近型模数转换器,其控制逻辑:步骤1:sar adc采样、量化操作。在dac电容阵列采样开关

ϕ

s导通期间,dac电容阵列将输入信号vip采样到dac电容阵列的下极板。采样完成后

ϕ

s关闭,时钟ckc控制比较器1和sar逻辑对输入信号进行正常量化,在sar 量化结束之后,dac电容阵列的上极板产生残差电压vr。

16.步骤2:残差电压的放大。残差电压vr产生后,时钟ckc控制比较器1关闭,时钟cka控制残差放大器开始工作,放大残差电压vr并保存在电容cr上。

17.步骤3:时间的初步量化。残差电压vr完成放大后,时钟cka控制残差放大器停止工作;时钟ckd控制电流源开始对残差电容cr进行放电,同时控制延时链开始工作,产生时钟ck

t

,控制比较器2开始工作。

18.若正端电压高于负端电压,只对正端残差电容cr放电,比较器2通过时钟ck

t

不断对正负端残差电容上的电压进行比较并由tdc逻辑保存比较结果,直至结果跳变,初步量化完成。

19.若正端电压低于负端电压,只对负端残差电容cr放电,比较器2通过时钟ck

t

不断对正负端残差电容上的电压进行比较并由tdc逻辑保存比较结果,直至结果跳变,初步量化完成。

20.步骤4:时间残差的量化。比较器2比较结果跳变后,tdc逻辑产生信号ck

tl

控制电流源切换,正端残差电容停止放电,负端残差电容由电流源0.5id进行放电,比较器2仍以相同的频率不断对正负残差电容上的电压进行比较并输出时间残差的量化码值,其包括1位时间残差量化码和1位量化完成标识码,并由tdc逻辑保存。

21.图2显示了tdc量化实现0.5lsb精度的示意图。需要量化的时间为tq,tdc初步量化完成后,时间残差为1-tr,随后对负端电压vn以0.5id的电流进行放电,则放电至vp=vn的时间为2tr。因为lsbt《2tr《2lsbt,根据放电时间的不同输出码值01或11,第一位为0表示tr》0.5lsbt,第一位为1表示tr《0.5lsbt,第二位是量化结束标识码恒为1,由此量化时间残差,实现了0.5lsbt的精度。

22.步骤5:码值重组。两步式adc量化码由m位sar量化码和2n 3位tdc量化码组合,其中tdc量化码包括1位跳变码,1位结束标识码和1位0.5lsb二进制码,跳变码和结束标识码不参与码值重组。将tdc量化码转换成n 1位2进制码,和m位sar量化码拼接重组成m n 1位adc二进制量化码。

23.时间残差放大的原理是,以电流源id对电容cr进行放电,理想情况下,电容上的残差电压vr是线性变化的。如果id变化,vr的时间特性曲线会有不同的斜率。图3显示了不同电流id下,残差电压vr随时间的变化。如果id=i0,vr从v0到vref的时间是t0。如果id=i0/n,vr从v0到vref的时间是n*t0,由此实现时间上的n倍放大。

24.传统结构在时序上是先通过vtc把sar adc级量化残差转换为时域信号后再进行tdc量化,即vtc和tdc量化在时域上是串行的,本发明采用时序重叠的vtc和tdc,提高了量化速率。同时,传统结构想要实现更高的精度,需要进一步缩减tdc延时单元的延时或者减小vtc放电电流id;前者需要更大的功耗开销,后者需要分配更多的时间给vtc。本发明对tdc量化后的时间残差进行放大并再次量化,在几乎不增牺牲其他性能的前提下提高了一位精度。

25.综上所述,本发明对比传统的基于tdc的两步式逐次逼近型模数转换器,以增加两个延时单元的方式实现了0.5lsb的精度,增加了adc精度,同时并合并了vtc和tdc的时序,在不提高硬件要求的条件下,有效提高了adc的速度。

附图说明

26.图1为本发明的正端电路结构图;图2为本发明的tdc量化示意图;图3为本发明的vtc功能图;图4为实施例的正端电路结构图;图5为实施例的tdc量化示意图。

具体实施方式

27.下面结合具体实施例和附图,对本发明做进一步的详细说明。需要说明的是:实施案例中的参数并不影响本发明的一般性。

28.如图1所示,一种基于tdc的两步式逐次逼近型模数转换器,实现7位的adc,具体为3位sar量化加4位tdc量化。即本实施例中sar量化m位,m=3,tdc量化n 1位,n=3,如图4所示,包括dac电容阵列、比较器1、sar逻辑、残差放大器、tdc模块和码值重组逻辑。本实施例用如图2所示的tdc实现对4.2lsbt的量化,具体量化时序如图5。

29.步骤1:传统sar adc采样、量化操作。在dac电容阵列采样开关

ϕ

s导通期间,dac电容阵列将输入信号vip采样到dac电容阵列的下极板。采样完成后

ϕ

s关闭,时钟ckc控制比较器1和sar逻辑对输入信号进行正常量化,在sar 量化结束之后,dac电容阵列的上极板产生残差电压vr,同时sar逻辑储存了高3位量化结果。

30.步骤2:残差电压的放大。残差电压vr产生后,时钟ckc控制比较器1关闭,时钟cka控制残差放大器开始工作,放大残差电压vr并保存在电容cr上。

31.步骤3:时间的初步量化。

32.首先初步量化4个lsbt,以正端电压高于负端电压为例,时钟ckd控制正端电压vp放电时间为5个lsbt,连续时间过零比较器2不断对正端电压vp和负端电压vn进行比较,tdc逻辑保存结果,最终输出5个温度计码11110,其中包括1个跳变码0,初步量化完成。选用连续时间过零比较器以降低功耗和面积。

33.步骤4:时间残差的量化。这一步开始量化剩余0.2个lsbt的时间残差。跳变码值0产生时,码值跳变产生信号ck

tl

控制正端电容停止放电,负端电容由电流源0.5id进行放电,如图3所示,0.5id放电时间将是id放电时间的两倍,由此将0.8lsbt放大为1.6lsbt,实现时间残差的放大。tdc逻辑继续保存过零比较器的输出码。这些码值分别为表示0.5lsb精度的

码值0,和量化结束标识码1。最终tdc量化码为1111001。

34.步骤5:码值重组。adc量化码由3位sar量化码和7位tdc量化码组合,其中tdc量化码包括1位跳变码0,1位0.5lsb精度二进制码0,1位结束标识码1和4位温度计码1111,跳变码和结束标识码不参与码值重组。将温度计码1111转换成3位2进制码100后,和3位sar输出的二进制码m2m1m0,0.5lsb精度二进制码0拼接重组成7位adc量化二进制码m2m1m01000。

35.通过以上实施例可见:本发明在保证传统基于tdc的两步式逐次逼近型模数转换器的功能基础上,将vtc和tdc在时序上重叠,提升了速度;同时借助tdc额外增加的延时单元实现了0.5lsbt的精度,在几乎不增加硬件成本的前提下将两步式adc的精度提高了一位。

36.以上实例仅为本发明的所选例子,本发明的使用并不局限于该实例,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。