一种多通道adc测试方法

技术领域

1.本发明属于半导体集成电路测试领域,特别涉及一种多通道adc测试方法。

背景技术:

2.多通道adc工作时多为各个通道并行同时工作,但测试时多为依次测试每个通道。因为每个通道都需要一台信号源来为其提供输入信号保证其信号质量,故多通道很难同时进行测量。通常测试时有两种方法,一是不改变芯片依次测试通道,二是不改变通道依次测试芯片。面对不同测试目的与芯片情况时,应采取不同的测试方法。

3.两种测试方法各有其优势。不改变芯片依次测试通道可以保证同一芯片的不同通道在同一环境下进行测试,所有通道的测试过程均在该芯片加电情况下进行,尽量排除了因芯片总体原因对通道功能带来的影响,如夹具接触、寄存器配置等。不改变通道依次测试芯片可以保证测试的通道在同一环境下,尽量地排除了输入信号、测试程序等问题对通道功能带来的影响。

4.传统的测试方法无论采用哪种都需要测量每个芯片的每个通道,测试过程都重复冗长且数据量较大。不仅测试过程中环境可能会产生变化,测试人员的操作也是造成测试误差的原因之一。在总合格率较低的研发测试阶段,同一批次电路的不同通道因为设计、工艺等原因合格率往往有很大的差异,即有的通道合格率高而有的通道合格率较低。因此可以先对样品进行摸底测试来判断该批次中哪个或哪几个通道合格率低后,统计不同通道的合格率。

技术实现要素:

5.本发明目的是:基于上述问题与现象提出一种新的多通道adc测试方法,采用摸底-统计-循环测试方法分段操作及时总结,不仅仅可以提升测试效率、降低测试误差,还可以及时发现设计、工艺中的问题,及时进行排查。

6.本发明的技术方案是:

7.一种多通道adc测试方法,包括以下步骤:

8.s1、进行若干样品摸底测试:

9.先选取同一批次多通道adc的若干样品,对每个样品的每个通道的功能进行摸底测试;

10.s2、统计单个通道合格率:

11.根据步骤s1的若干样品摸底测试结果,分别统计各单个通道合格率;

12.s3、测量同批次剩余芯片:

13.利用摸底测试结果,按照优先测量通道合格率低的通道原则,顺序测试同批次剩余的多通道adc芯片,遇到某一通道不合格时,该芯片不再进行下一通道的测试。

14.s4、不同批次芯片循环测试:

15.记录步骤s2-s3测试结果后,根据测试情况对芯片进行改进提升,下一次流片后重

复步骤s1-s3,记录新批次芯片情况,直至产品整体合格率满足批量生产条件。

16.优选的,步骤s1的摸底测试,采取不更换芯片、更换通道依次测试的方法,在芯片工作状态下不断电地更换通道进行采样。

17.优选的,步骤s1的摸底测试中,若某一芯片a的某一通道a(a)无法正常工作,在保证输入信号、采样程序不变的情况下,更换为芯片b进行对比,若芯片b的对应通道b(a)可以正常工作,则再复测芯片a,若a仍无法正常工作,则判定通道a(a)异常;若b(a)也无法正常工作,则排查夹具松弛、接触错位的问题后,重复上述测试实验进行排查直至判定通道a(a)异常或合格。

18.优选的,步骤s1的摸底测试中,记录每个样品的每个通道的功能情况,观察样品的芯片整体合格率:

19.若整体合格率低于设定值,则进入步骤s2统计单个通道合格率阶段;

20.若整体合格率高于设定值,则根据测试目的直接进行筛查测试阶段:

21.若以筛选、完成验收、出售为目的,则不需要测试全部通道,而是利用摸底测试结果优先测试合格率较低的通道,遇到不合格通道则整个芯片判定不合格,不需要再测试其他通道;若此次测试需要与其他批次芯片进行比较,仍需要进入步骤s2、s3。

22.本发明的优点是:

23.本发明通过摸底-统计-循环测试方法,可以更科学高效地对多通道adc进行测量,减少测试中的重复工作、提高测试效率、节约测试成本,增加了测试的准确性可靠性稳定性,及时总结排查问题,提高研发生产效率。摸底-统计-循环测试方法的测试结果可以在芯片研发生产的每个阶段发挥其意义。原理相似的芯片之间也可以通过摸底-统计-循环测试结果进行比较,排查问题改良设计,提高效率。

附图说明

24.下面结合附图及实施例对本发明作进一步描述:

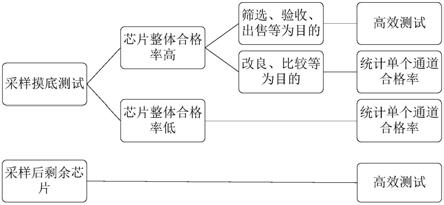

25.图1为本发明多通道adc测试方法的流程图。

具体实施方式

26.如图1所示,本发明的一种多通道adc测试方法,包括以下步骤:

27.s1、进行若干样品摸底测试:

28.先选取同一批次多通道adc的若干样品,对每个样品的每个通道的功能进行摸底测试;在摸底阶段采取不更换芯片、更换通道依次测试的方法,在芯片工作状态下不断电地更换通道进行采样。可以保证测试出的数据为同一芯片在同一环境下的不同通道情况,可以尽可能地排除接触问题与其他不稳定因素因测试环境不同而造成差异。

29.若某一芯片a的某一通道a(a)无法正常工作,在保证输入信号、采样程序不变的情况下,更换为芯片b进行对比,若芯片b的对应通道b(a)可以正常工作,则再复测芯片a,若a仍无法正常工作,则判定通道a(a)异常;若b(a)也无法正常工作,则排查夹具松弛、接触错位的问题后,重复上述测试实验进行排查直至判定通道a(a)异常或合格。

30.步骤s1的摸底测试中,记录每个样品的每个通道的功能情况,观察样品的芯片整体合格率:

31.若整体合格率低于设定值,则进入步骤s2统计单个通道合格率阶段;

32.若整体合格率高于设定值,则根据测试目的直接进行筛查测试阶段:

33.若以筛选、完成验收、出售为目的,则不需要测试全部通道,而是利用摸底测试结果优先测试合格率较低的通道,遇到不合格通道则整个芯片判定不合格,不需要再测试其他通道;若此次测试需要与其他批次芯片进行比较,仍需要进入步骤s2、s3。

34.s2、统计单个通道合格率:

35.根据步骤s1的若干样品摸底测试结果,分别统计各单个通道合格率;记录并计算各个通道情况,将芯片测试数据整理成为通道测试数据记录保存。通过分析该批次芯片每个通道的合格率,可以指导测试设计与工艺加工,排查造成通道不能正常工作的原因,提高产品合格率,降低成本。不同批次的芯片之间可以通过比较同一通道的合格率来判断产品研发过程中设计、工艺中的改良是否有效,是否引发了新的问题。

36.s3、测量同批次剩余芯片:

37.利用摸底测试结果,按照优先测量通道合格率低的通道原则,顺序测试同批次剩余的多通道adc芯片,遇到某一通道不合格时,该芯片不再进行下一通道的测试。

38.s4、不同批次芯片循环测试:

39.记录步骤s2-s3测试结果后,根据测试情况对芯片进行改进提升,下一次流片后重复步骤s1-s3,记录新批次芯片情况,直至产品整体合格率满足批量生产条件。

40.实施例1

41.假设想要测试通道数为m的共i批次adc。第i批次的芯片总体数为ni,抽样的样本数为ri。第i批次样品总合格率为αi,i批次的j通道合格率为β

ij

。

42.则:

43.传统测试方法全部按次序测量的测试量t

all

次如下:

[0044][0045]

采用摸底-统计-循环测试方法测试量ts次如下:

[0046][0047]

测试量减少率如下:

[0048][0049]

i批次样品总合格率如下:

[0050][0051]

i批次的j通道通道合格率如下:

[0052][0053]

为了证明摸底-统计-循环测试方法的可行性,假设存在某一型号待测试的8通道adc如下,共三批次:

[0054]

批次一,50只8通道adc,假设1通道合格率70%,2通道合格率80%,其余通道全部合格。通过随机采样方法采样10只。

[0055]

批次二,50只8通道adc,假设1通道合格率80%,2通道合格率90%,其余通道全部

合格。通过随机采样方法采样10只。

[0056]

批次三,100只8通道adc,假设1通道合格率90%,2通道合格率90%,其余通道全部合格。通过随机采样方法采样20只,即:

[0057]

m=8,i=3,n1=50,r1=10,n2=50,r2=10,n3=100,r3=20

[0058]

采用传统测试方法:

[0059]

全部按次序全部测量t

all

=1600。

[0060]

采用摸底-统计-循环测试方法:

[0061]

1.批次一:

[0062]

1.1抽样摸底测试:

[0063]

设测试结果如下:1通道7只合格3只不合格,2通道8只合格2只不合格,其余通道均合格,其中1、2通道均不合格的有1只。测试量t

11

=10

×

8=80,总体合格率为α1=60%。芯片均处于研发阶段且总体合格率较低,故进入第二阶段。

[0064]

1.2统计单个通道合格率:

[0065]

β

11

=70%,β

12

=80%,β

13

=β

14

=β

15

=β

16

=β

17

=β

18

=100%。

[0066]

1.3利用摸底测试结果测量剩下芯片:

[0067]

按照优先测量通道合格率低的通道原则,顺序测试采样后余下芯片,设测试结果如下:测试全部芯片1通道,需测试40次,筛除不合格芯片12只,28只1通道合格芯片进入下一步。测试28只1通道合格芯片的2通道,需测试28次,共测量出4只不合格,剩余24只进入下一步。测试其余通道,需测试24

×

6=144次。测试量t

12

=212。

[0068]

2.批次二:

[0069]

2.1抽样摸底测试:

[0070]

设测试结果如下:1通道8只合格2只不合格,2通道9只合格1只不合格,其余通道均合格,其中1、2通道均不合格的有0只。测试量t

21

=10

×

8=80,总体合格率为α2=70%。芯片均处于研发阶段且总体合格率较低,故进入第二阶段。

[0071]

2.2统计单个通道合格率:

[0072]

β

21

=80%,β

22

=90%,β

13

=β

14

=β

15

=β

16

=β

17

=β

18

=100%。

[0073]

2.3利用摸底测试结果测量剩下芯片:

[0074]

按照优先测量通道合格率低的通道原则,顺序测试采样后余下芯片,设测试结果如下:测试全部芯片1通道,需测试40次,筛除不合格芯片8只,32只1通道合格芯片进入下一步。测试32只1通道合格芯片的2通道,需测试32次,共测量出4只不合格,剩余28只进入下一步。测试其余通道,需测试28

×

6=168次。测试量t

22

=240。

[0075]

3.批次三:

[0076]

3.1抽样摸底测试:

[0077]

设测试结果如下:1通道18只合格2只不合格,2通道18只合格2只不合格,其余通道均合格,其中1、2通道均不合格的有0只。测试量t

31

=20

×

8=160,总体合格率为α3=80%。芯片均处于研发阶段且总体合格率较低,故进入第二阶段。

[0078]

3.2统计单个通道合格率:

[0079]

β

31

=90%,β

32

=90%,β

13

=β

14

=β

15

=β

16

=β

17

=β

18

=100%。

[0080]

3.3利用摸底测试结果测量剩下芯片:

[0081]

按照优先测量通道合格率低的通道原则,顺序测试采样后余下芯片,设测试结果如下:测试全部芯片1通道,需测试80次,筛除不合格芯片8只,72只1通道合格芯片进入下一步。测试72只1通道合格芯片的2通道,需测试72次,共测量出8只不合格,剩余64只进入下一步。测试其余通道,需测试64

×

6=384次。测试量t

32

=536。

[0082]

通过采用摸底-统计-循环测试方法,全部测试量ts=t

11

t

12

t

21

t

22

t

31

t

32

=1308。

[0083][0084]

故摸底-统计-循环测试方法的测试量相比传统测试方法减少了18.25%,大大减少了测试量,提高了测试效率。

[0085]

上述实施例只为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明主要技术方案的精神实质所做的修饰,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。