基于tsv的三维集成低噪声放大器

技术领域

1.本发明属于三维集成电路技术领域,涉及基于tsv的三维集成低噪声放大器。

背景技术:

2.低噪声放大器(lna)是射频芯片的重要组成部分,低噪声放大器作为射频接收机系统的第一个模块,其功能是将接收到的微弱信号放大的同时,不引入过高的噪声,从而提高输出的信噪比。因此低噪声放大器性能的好坏直接影响整个射频系统的优劣。

3.如今接收机系统正不断朝着功能更强、带宽更大,处理器速度更快的方向发展,设备的集成度越来越高的同时也使得功耗越来越大。而传统的平面工艺很难进一步满足高集成度的要求,功耗和延迟问题也日益突出。而通过硅通孔实现层间垂直互联的tsv技术,不仅自身高频特性出色而且减小了互联线长度从而使芯片封装尺寸更小、集成度更高。

4.将lna中的电容、电感、mos管加以tsv技术实现,不仅可以保证放大器的性能,而且利用tsv互联线短的技术优势减小了互联线长度从而降低了lna的延迟以及功耗。

技术实现要素:

5.本发明的目的是提供一种基于tsv的三维集成低噪声放大器,该装置提高了lna的集成度,降低lna的延迟以及功耗。

6.本发明所采用的技术方案是,基于tsv的三维集成低噪声放大器,包括tsv电感l2,tsv电感输入端为所示低噪声放大器的输入端vin,tsv电感l2的输出端lout与tsv电容c2输入端cin相连,tsv电容c2的输出端cout接入tsv mos管mos2的栅极g2;tsv mos管mos2的漏极d2连接tsv mos管mos1的源极s1,tsv mos管mos1的漏极d1连接tsv电容c1输出端cout,tsv电容c1输入端与电源vdd连接,电源vdd还分别连接电阻r1和tsv电感l1输入端lin,tsv电感l1输出端lout与tsv mos管mos1的漏极d1连接,tsv mos管mos2的栅极g2连接tsv电容c3输入端cin,tsv电容c3输出端cout连接tsv mos管mos1的源极s2;tsv电感l3输入端lin与tsv mos管mos2的源极s2相连,tsv电感l3的输出端lout与地信号gnd相连。

7.本发明的特点还在于:

8.tsv mos管mos1和tsv mos管mos2结构相同,均包括p型硅衬底,p型硅衬底的中心处贯穿设有tcv铜柱,tcv铜柱的外壁与硅衬底之间设有一层绝缘介质层,硅衬底上下两端靠近绝缘介质层处设有四个n 掺杂区。硅衬底的上下两端端面上分别设有二氧化硅绝缘层,从四个n 掺杂区分别引出四个金属端口。

9.绝缘介质层的材料为sio2。

10.tsv电感l1、tsv电感l2、tsv电感l3均通过若干个tsv呈螺旋状绕制形成,各tsv收尾之间依次采用rdl连接。

11.tsv电容c1、tsv电容c2、tsv电容c3均通过n

×

n的tsv阵列连接形成。

12.本发明的有益效果如下:

13.1.使用tsv mos管级联形成cascode结构,保证了放大器的增益的同时实现了更小

的尺寸。

14.2.本发明中使用的电感l1、l2、l3,电容c1、c2、c3均为基于tsv的三维结构,tsv无源器件与传统的无源器件相比损耗更低,占用面积更小,从而更利于提高芯片集成度。

15.3.本发明实现了tsv有源器件和无源器件的互联。相比于传统低噪声放大器(lna)具有面积小、噪声系数低、功耗低等优点。

附图说明

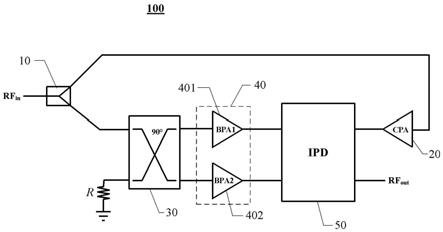

16.图1是本发明基于tsv的三维集成低噪声放大器的整体电路图;

17.图2是本发明基于tsv的三维集成低噪声放大器的整体结构顶视图;

18.图3是本发明基于tsv的三维集成低噪声放大器中tsv mos管的结构示意图;

19.图4是本发明基于tsv的三维集成低噪声放大器中tsv电感的结构示意图;

20.图5是本发明基于tsv的三维集成低噪声放大器中tsv电容的一种结构示意图;

21.图6是本发明基于tsv的三维集成低噪声放大器中tsv电容的另一种结构示意图。

22.图中,1.tsv铜柱,2.金属端口,3.二氧化硅氧化层,4.绝缘介质层,5.硅衬底,6.n 掺杂区。

具体实施方式

23.下面结合附图和具体实施方式对本发明进行详细说明。

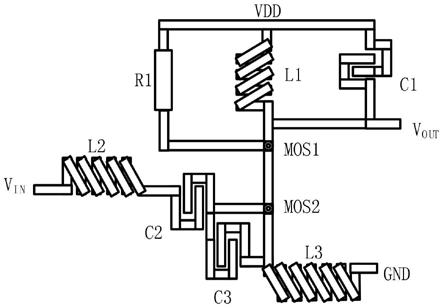

24.本发明基于tsv的三维集成低噪声放大器,如图1、2所示,包括两个tsv nmos管mos1、mos2,三个tsv电感l1、tsv电感l2、tsv电感l3,三个tsv电容c1、tsv电容c2、tsv电容c3、一个电阻r1、电源vdd、地信号gnd。

25.其中tsv mos1拥有四个端口,分别为源极s1、漏极d1、栅极g1、衬底b1,tsv mos2拥有四个端口,分别为源极s2、漏极d2、栅极g2、衬底b2。tsv电容c1、tsv电容c2、tsv电容c3均有两个端口,分别为输入端cin和输出端cout。tsv电感l1、tsv电感l2、tsv电感l3均有两个端口,分别为lin和lout。基于tsv的三维集成低噪声放大器拥有两个端口分别为输入端vin,输出端vout。

26.连接方式如下:

27.电源vdd与电阻r1、tsv电感l1输入端lin、tsv电容c1输入端cin相连,电阻r1与tsv mos管mos1的栅极g1相连,tsv电感l1输出端lout、tsv电容c1输出端cout与tsv mos管mos1的漏极d1相连;tsv mos管mos1的源极s1与tsv mos管mos2的漏极d2相连;

28.tsv电感l2输入端为芯片的输入端vin,输出端lout与tsv电容c2输入端cin相连,tsv电容c2的输出端cout接入tsv mos管mos2的栅极g2;

29.tsv电容c3输入端cin连接tsv mos管mos2的栅极g2,tsv电容c3输出端cout连接tsv mos管mos1的源极s2;tsv电感l3输入端lin与tsv mos管mos2的源极s2相连,tsv电感l3的输出端lout与地信号gnd相连。

30.该放大器中的tsvmos管mos1、tsvmos管mos2结构相同,均为nmos并且使用了tsv结构。如图3所示,在p型硅衬底5中加工完成通孔后贯穿一tsv铜柱1,并在tsv铜柱1外侧与硅衬底5中间形成一层sio2绝缘介质层4。硅衬底5上下两端靠近绝缘介质层4处设有四个n 掺杂区6。硅衬底5的上下两端端面上分别设有二氧化硅绝缘层3,从四个n 掺杂区6分别引出

四个金属端口2,四个金属端口2分别为tsvmos管mos1和tsvmos管mos2中对应的四个端口。

31.tsv电感l1、tsv电感l2、tsv电感l3的形式相同,仅仅是tsv的数量不同。如图4所示,以tsv电感l1为例,tsv电感l1由八根圆柱形tsv呈螺旋状依次连接形成,相邻两个tsv的顶部和底部之间分别采用rdl连接。

32.八根tsv铜柱分别为tsv1、tsv2、tsv3、tsv4、tsv5、tsv6、tsv7、tsv8;

33.其中tsv1、tsv3、tsv5、tsv7在一侧tsv2、tsv4、tsv6、tsv8在另一侧。将tsv1、tsv2、tsv3、tsv4、tsv5、tsv6、tsv7、tsv8依次使用rdl线连接,从而形成一个螺旋状的tsv电感。

34.tsv电感l2使用10根tsv铜柱,tsv电感l3使用12根tsv铜柱,原理同tsv电感l1。

35.该放大器使用了两种不同的tsv阵列电容,tsv阵列电容的选择依据容值的大小,容值越大则使用tsv电容的阵列越大。

36.一种tsv电容结构如图5所示,由九根圆柱形tsv、顶部和底部的rdl组成。九根tsv铜柱形成3

×

3(此处n=3)的阵列,依次为tsv9、tsv10、tsv11、tsv12、tsv13、tsv14、tsv15、tsv16、tsv17。其中tsv9、tsv10、tsv11、tsv15、tsv16、tsv17通过rdl线连接起来形成电容的一个极板;tsv12、tsv13、tsv14通过rdl连接起来形成电容的另一个极板,从而形成一个tsv电容。

37.另一种tsv电容结构如图6所示,由十六根圆柱形tsv、顶部和底部的rdl组成。十六跟tsv铜柱形成4

×

4(此处n=4)的阵列,依次为tsv18、tsv19、tsv20、tsv21、tsv22、tsv23、tsv24、tsv25、tsv26、tsv27、tsv28、tsv29、tsv30、tsv31、tsv32、tsv33。其中tsv18、tsv19、tsv20、tsv21、tsv26、tsv27、tsv28、tsv29通过rdl线连接起来形成电容的一个极板;tsv22、tsv23、tsv24、tsv25、tsv30、tsv31、tsv32、tsv33通过rdl线连接起来形成电容的另一个极板,从而形成一个tsv电容。

38.本发明中,tsv电容c1、tsv电容c2、tsv电容c3具体采用上述两种电容的哪一种结构,与电容的容值有关,容值越大则使用tsv电容的阵列越大。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。