1.本发明涉及一种神经形态器件。

2.本技术基于2020年10月23日申请的pct/jp2020/039957主张优先权,并在此引用其内容。

背景技术:

3.已知一种利用基于两个铁磁性层的磁化的相对角变化的电阻值变化(磁阻变化)的磁阻效应元件。在磁阻效应元件中,写入数据时的电流路径和读出数据时的电流路径有时不同。这样的磁阻效应元件为了分别控制不同的电流路径的电流,连接三个开关元件。由三个开关元件控制的磁阻效应元件被称为三端子型磁阻效应元件。

4.例如,专利文献1所记载的磁畴壁移动型的磁阻效应元件为三端子型磁阻效应元件的一例。

5.近年来,正在推进人工模仿人脑中的神经元和突触的关系的神经形态器件的研究。

6.例如,专利文献2所记载的磁神经元件为利用磁畴壁移动型磁阻效应元件的神经形态器件的一例。

7.现有技术文献

8.专利文献

9.专利文献1:专利第5441005号公报

10.专利文献2:专利第6617829号公报

技术实现要素:

11.发明所要解决的问题

12.磁阻效应元件等电阻变化元件多被集成使用。从提高存储容量的观点来看,集成了电阻变化元件的器件需要提高度集成性。作为提高电阻变化元件的集成性的方法,探讨减小电阻变化元件的方法。

13.然而,如果仅是减小电阻变化元件,则神经形态器件的识别率降低。

14.本发明鉴于上述问题而提出,其目的在于提供一种电阻变化元件的集成性高且识别率提高的神经形态器件。

15.用于解决问题的技术方案

16.(1)第一方案提供一种神经形态器件,其具备第一元件组和第二元件组,所述第一元件组和所述第二元件组分别包含多个磁畴壁移动元件,所述多个磁畴壁移动元件分别具备磁畴壁移动层、铁磁性层、以及夹持于所述磁畴壁移动层和所述铁磁性层之间的非磁性层,属于所述第一元件组的各个所述磁畴壁移动元件的所述磁畴壁移动层的长边方向上的长度比属于所述第二元件组的各个所述磁畴壁移动元件的所述磁畴壁移动层的长边方向上的长度短,就输入了规定的大小的脉冲时的电阻变化率而言,属于所述第一元件组的各

个所述磁畴壁移动元件一方比属于所述第二元件组的各个所述磁畴壁移动元件大。

17.(2)在上述方案的神经形态器件中,也可以是,所述第一元件组和所述第二元件组处于层叠结构体内,所述层叠结构体层叠于基板上。

18.(3)在上述方案的神经形态器件所具有的所述层叠结构体中,也可以是,所述第二元件组处于比所述第一元件组远离所述基板的位置。

19.(4)在上述方案的神经形态器件中,也可以是,属于所述第一元件组的磁畴壁移动元件的数量比属于所述第二元件组的磁畴壁移动元件的数量多。

20.(5)在上述方案的神经形态器件中,也可以是,就使所述磁畴壁移动元件的磁畴壁移动所需的临界电流密度而言,属于所述第二元件组的各个所述磁畴壁移动元件一方比属于所述第一元件组的各个所述磁畴壁移动元件小。

21.(6)从上述方案的神经形态器件所具有的所述磁畴壁移动元件的层叠方向俯视时,所述第一元件组的任一个所述磁畴壁移动元件和所述第二元件组的任一个所述磁畴壁移动元件至少一部分重叠。

22.(7)在属于上述方案的神经形态器件的所述第二元件组的任一个所述磁畴壁移动元件的长边方向上,也可以是,所述第一元件组中的任一个所述磁畴壁移动元件的两端处于所述第二元件组中的任一个所述磁畴壁移动元件的两端的内侧。

23.(8)从上述方案的神经形态器件的所述磁畴壁移动元件的层叠方向俯视时,也可以是,所述第一元件组的所述磁畴壁移动元件和所述第二元件组的所述磁畴壁移动元件未重叠。

24.(9)就上述方案的神经形态器件而言,也可以是,属于所述第二元件组的所述磁畴壁移动元件的下表面的表面粗糙度比属于所述第一元件组的所述磁畴壁移动元件的下表面的表面粗糙度大。

25.(10)就上述方案的神经形态器件而言,也可以是,还具备将所述第一元件组的任一个所述磁畴壁移动元件和所述第二元件组的任一个所述磁畴壁移动元件相连的连接配线。

26.(11)在上述方案的神经形态器件中,也可以是,所述第一元件组进行第一积和运算,所述第二元件组进行第二积和运算,将来自属于所述第一元件组的多个磁畴壁移动元件的输出的合计向属于所述第二元件组的所述磁畴壁移动元件输入。

27.(12)在上述方案的神经形态器件中,也可以是,向属于所述第二元件组的所述磁畴壁移动元件输入的写入脉冲的脉冲长度与向属于所述第一元件组的所述磁畴壁移动元件输入的写入脉冲的脉冲长度不同。

28.(13)在上述方案的神经形态器件中,也可以是,向属于所述第二元件组的所述磁畴壁移动元件输入的写入脉冲的脉冲振幅与向属于所述第一元件组的所述磁畴壁移动元件输入的写入脉冲的脉冲振幅不同。

29.(14)在上述方案的神经形态器件中,也可以是,所述第一元件组及所述第二元件组分别负责神经网络中的不同层之间的运算。

30.(15)在上述方案的神经形态器件中,也可以是,所述第一元件组与所述第二元件组相比,负责神经网络的输入层侧的运算。

31.发明效果

32.就上述方案的神经形态器件而言,电阻变化元件的集成性高,且识别率优异。

附图说明

33.图1是第一实施方式的集成装置的映像图。

34.图2是神经网络的示意图。

35.图3是用于第一实施方式的神经形态器件的集成装置的电路图。

36.图4是用于第一实施方式的神经形态器件的集成装置的特征部分的剖视图。

37.图5是用于第一实施方式的神经形态器件的集成装置的特征部分的俯视图。

38.图6是将用于第一实施方式的神经形态器件的集成装置的两个磁畴壁移动元件的附近放大的俯视图。

39.图7是用于第一实施方式的神经形态器件的集成装置的特征部分的立体图。

40.图8是用于第一实施方式的神经形态器件的集成装置的、属于第一元件组的磁畴壁移动元件及属于第二元件组的磁畴壁移动元件的剖视图。

41.图9是表示电阻值相对于施加到磁畴壁移动元件的脉冲数的变化的情况的映像图。

42.图10是用于第二实施方式的神经形态器件的集成装置的特征部分的俯视图。

43.图11是将用于第二实施方式的神经形态器件的集成装置的两个磁畴壁移动元件的附近放大的俯视图。

44.图12是用于第二实施方式的神经形态器件的集成装置的、属于第一元件组的磁畴壁移动元件及属于第二元件组的磁畴壁移动元件的剖视图。

45.图13是用于第三实施方式的神经形态器件的集成装置的特征部分的俯视图。

46.图14是将用于第三实施方式的神经形态器件的集成装置的两个磁畴壁移动元件的附近放大的俯视图。

47.图15是用于第四实施方式的神经形态器件的集成装置的特征部分的剖视图。

48.图16是用于第五实施方式的神经形态器件的集成装置的特征部分的剖视图。

49.图17是用于第五实施方式的神经形态器件的集成装置的另一例的集成装置的特征部分的剖视图。

50.图18是表示电阻值相对于施加到配置于用于第五实施方式的神经形态器件的集成装置的电阻变化元件的脉冲数的变化的情况的映像图。

51.图19是用于变形例1的神经形态器件的集成装置的、属于第一元件组的磁畴壁移动元件及属于第二元件组的磁畴壁移动元件的剖视图。

52.图20是用于变形例2的神经形态器件的集成装置的、属于第一元件组的磁畴壁移动元件及属于第二元件组的磁畴壁移动元件的剖视图。

53.图21是用于变形例3的神经形态器件的集成装置的、属于第一元件组的磁畴壁移动元件及属于第二元件组的磁畴壁移动元件的剖视图。

54.图22是用于变形例4的神经形态器件的集成装置的、属于第一元件组的磁畴壁移动元件及属于第二元件组的磁畴壁移动元件的剖视图。

55.图23是用于变形例5的神经形态器件的集成装置的、属于第一元件组的磁畴壁移动元件及属于第二元件组的磁畴壁移动元件的剖视图。

具体实施方式

56.以下,适当参照图对本实施方式详细地进行说明。为了容易理解本发明的特征,为了方便,以下的说明中使用的附图有时将成为特征的部分放大表示,各构成要素的尺寸比率等有时与实际不同。以下的说明中例示的材料、尺寸等为一例,本发明不受这些限制,可以在实现本发明的效果的范围内适当地变更并实施。

57.首先,对方向进行定义。将基板sb(参照图4)的一面的一方向设为x方向,将与x方向正交的方向设为y方向。x方向例如是磁畴壁移动元件的磁畴壁移动层延伸的方向。x方向是长边方向的一例。z方向是与x方向及y方向正交的方向。z方向是层叠方向的一例。以下,有时将 z方向表达为“上”,将-z方向表达为“下”。 z方向是远离基板sb的方向。上下未必与施加重力的方向一致。

58.另外,在本说明书中,“沿x方向延伸”是指x方向的长度比其它方向的长度长。另外,在本说明书中,“连接”不限于直接连接,包括在中间经由层的连接。

59.第一实施方式

60.图1是第一实施方式的集成装置id的电路图。集成装置id例如具备第一电路c1和第二电路c2。第一电路c1和第二电路c2分别是进行不同的积和运算的积和运算电路。第一电路c1和第二电路c2相互连接。例如,将由第一电路c1积和运算出的输出向第二电路c2输入。第二电路c2例如将由第一电路c1积和运算出的结果作为输入,进行进一步的积和运算。

61.第一实施方式的集成装置id例如作为神经形态器件发挥作用。神经形态器件是进行神经网络的运算的装置。神经形态器件人工模仿人脑中的神经元和突触的关系。

62.图2是神经网络nn的示意图。神经网络nn具有输入层lin、中间层lm以及输出层lout。在图2中,提示了中间层lm为三层的例子,但中间层lm的数量无关紧要。输入层lin、中间层lm以及输出层lout分别具有多个芯片c,各个芯片c与脑中的神经元对应。输入层lin、中间层lm以及输出层lout分别通过传递单元连接。传递单元与脑中的突触对应。神经网络nn通过传递单元(突触)进行学习而提高问题的正确回答率。学习为从信息中发现将来可以使用知识的行为。神经网络nn通过一边改变向传递单元施加的权重一边动作来学习。传递单元进行对输入的信号加权的乘积运算和将乘积运算的结果相加的求和运算。即,传递单元进行积和运算。

63.就神经网络nn而言,有时每一层级的分辨率不同。例如也可以是,越接近输出层lout的层级,越精细地改变向传递单元施加的权重。通过该结构,神经网络nn的识别率提高。即,在神经网络nn中,越接近输出层lout的层级,需要越高的分辨率。

64.图1所示的第一电路c1例如负责从第一中间层l

m1

向第二中间层l

m2

的积和运算,第二电路c2例如负责从第二中间层l

m2

向第三中间层l

m3

的积和运算。

65.图3是第一实施方式的集成装置id的一部分电路图。图3(a)是第一电路c1的电路图,图3(b)是第二电路c2的电路图。第一电路c1和第二电路c2例如具有相同的电路结构。

66.第一电路c1及第二电路c2分别具有多个电阻变化元件。第一电路c1所具有的电阻变化元件例如是磁畴壁移动元件100。另外,第二电路c2所具有的电阻变化元件例如是磁畴壁移动元件110。磁畴壁移动元件100、110是磁畴壁移动型磁阻效应元件。即,磁畴壁移动元件100、110是三端子型元件。第一电路c1的磁畴壁移动元件100的数量例如与第二电路c2的磁畴壁移动元件110的数量相同或比第二电路c2的磁畴壁移动元件110的数量多。向一个磁

畴壁移动元件110输入例如来自与连接到该磁畴壁移动元件110的读出线rl相连的多个磁畴壁移动元件100的输出的合计。

67.第一电路c1、第二电路c2分别具有多个第一开关元件sw1、多个第二开关元件sw2、多个第三开关元件sw3、多个写入线wl、多个读出线rl、多个共通线cl。

68.在第一电路c1中,磁畴壁移动元件100例如排列成矩阵状。在第二电路c2中,磁畴壁移动元件110例如排列成矩阵状。一个磁畴壁移动元件100、110分别与一个第一开关元件sw1、一个第二开关元件sw2、一个第三开关元件sw3连接。第一开关元件sw1、第二开关元件sw2、第三开关元件sw3中的任一个也可以与多个磁畴壁移动元件100、110连接。

69.如果将与特定的磁畴壁移动元件100、110连接的第一开关元件sw1及第二开关元件sw2设为on,则向特定的磁畴壁移动元件100、110写入数据。数据作为磁畴壁移动元件100、110的层叠方向的电阻值被记录。另外,如果将与特定的磁畴壁移动元件100、110连接的第二开关元件sw2和第三开关元件sw3设为on,则读出写入到特定的磁畴壁移动元件100、110的数据。

70.在从磁畴壁移动元件100、110读出数据的情况下,使电流从读出线rl朝向共通线cl流通。从共通线cl输出的电流(输出值)根据磁畴壁移动元件100、110的电阻值或者电阻值的倒数即电导(权重)而不同。即,从读出线rl朝向共通线cl施加电流与神经网络nn中的乘积运算对应。另外共通线cl与属于相同列的多个磁畴壁移动元件100、110连接,在共通线cl的端部检测的电流成为对由各个磁畴壁移动元件100、110进行乘积运算的结果进行求和运算的值。因此,集成装置id作为神经网络nn的积和运算器发挥作用。

71.向集成装置id的读出线rl施加的电流分别为向积和运算器的输入,从集成装置id的共通线cl中的每一个输出的电流为来自积和运算器的输出。向积和运算器的输入信号可以由脉冲长度控制,可以由脉冲振幅控制,也可以由脉冲频率控制。

72.第一开关元件sw1、第二开关元件sw2及第三开关元件sw3例如是场效应晶体管。第一开关元件sw1、第二开关元件sw2及第三开关元件sw3也可以是例如像双向阈值开关(ots:ovonic threshold switch)这样利用结晶层的换相的元件、像金属绝缘体转变(mit)开关这样利用能带结构的变化的元件、像齐纳二极管及雪崩二极管这样利用击穿电压的元件、随着原子位置的变化而传导性变化的元件。

73.第一开关元件sw1与写入线wl连接。第二开关元件sw2与共通线cl连接。第三开关元件sw3与读出线rl连接。读出线rl是读出数据时供电流流通的配线。写入线wl是写入数据时供电流流通的配线。共通线cl是在数据写入时及数据读出时的任一种情况下供电流流通的配线。

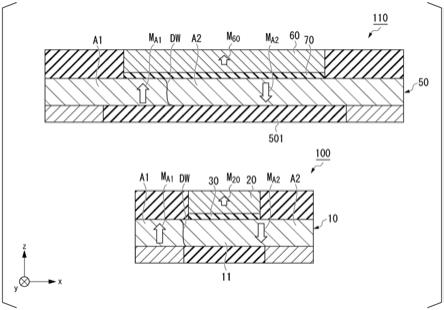

74.图4是第一实施方式的集成装置id的特征部分的剖视图。图5是第一实施方式的集成装置id的特征部分的俯视图。图5去除读出线rl、写入线wl、共通线cl进行图示。图6是将第一实施方式的集成装置id的两个磁畴壁移动元件100、110的附近放大的俯视图。图4是沿着图5及图6中的a-a线切断的xz截面。图7是集成装置id的特征部分的立体图。图7去除绝缘体in进行图示。

75.集成装置id具备基板sb和层叠结构体ls。层叠结构体ls处于基板sb上。

76.基板sb例如是半导体基板。基板sb具有多个开关元件。多个开关元件之间用元件间绝缘体ei进行绝缘。多个开关元件控制磁畴壁移动元件100、110中的每一个。

77.多个开关元件例如是第一开关元件sw1及第二开关元件sw2。第三开关元件sw3例如处于y方向的不同的位置。第三开关元件sw3例如处于磁畴壁移动元件100、110集成的集成区域的外侧的周边区域。以下,以第一开关元件sw1及第二开关元件sw2在集成区域内排列成矩阵状的情况为例。

78.第一开关元件sw1及第二开关元件sw2例如分别是场效应晶体管tr。以下,有时不区别第一开关元件sw1及第二开关元件sw2,简称为晶体管tr。

79.晶体管tr例如排列成矩阵状。晶体管tr例如具有栅极g、栅极绝缘膜gi、源极s、漏极d。从z方向观察,栅极g处于源极s和漏极d之间。栅极g控制源极s和漏极d之间的电荷的流动。源极s和漏极d是根据电流的流通方向而规定的名称,根据电流的流通方向而位置变化。图所示的源极s和漏极d的位置关系为一例,各个晶体管tr的源极s和漏极d的位置关系也可以相反。

80.层叠结构体ls具备第一元件组、第二元件组、配线、绝缘体in。第一元件组具有多个磁畴壁移动元件100。第二元件组具有多个磁畴壁移动元件110。第一元件组和第二元件组处于不同的层级。第二元件组处于比第一元件组远离基板sb的位置。第一元件组例如形成第一电路c1,进行第一积和运算。第二元件组例如形成第二电路c2,进行第二积和运算。即,第一元件组和第二元件组例如负责图2所示的神经网络nn的连续的不同的层级之间的运算。第一元件组例如负责比第二元件组接近输入层lin的层级的运算。

81.层级是按功能划分的层。层叠结构体ls通过层叠工序和加工工序的重复而制作,在各个层叠工序中层叠的单位通常成为层级。就层叠结构体ls而言,例如,包括面内配线的配线层和包括磁畴壁移动元件的元件层交替层叠。元件层是二层以上的任意的层数。

82.多个磁畴壁移动元件100、110及配线处于绝缘体in内。绝缘体in形成于每一层级。绝缘体in例如按层级区分为绝缘体in1、in2、in3、in4。绝缘体in将多层配线的配线之间或元件之间绝缘。绝缘体in为例如氧化硅(sio

x

)、氮化硅(sin

x

)、碳化硅(sic)、氮化铬、氮碳化硅(sicn)、氮氧化硅(sion)、氧化铝(al2o3)、氧化锆(zro

x

)等。

83.配线具有导电性。配线包括例如选自由ag、cu、co、al、au、ru构成的组中的任一个。配线有面内配线和通孔配线vl。面内配线是xy面内的沿任一方向延伸的配线。通孔配线vl是沿z方向延伸的配线。通孔配线vl例如将处于不同层级的元件之间相连。通孔配线vl也可以是贯通相邻的层级并到达夹着相邻的层级的层级或基板的贯通配线。贯通配线例如将磁畴壁移动元件100、110中的每一个和基板sb的晶体管tr相连,沿z方向贯通绝缘体in的一部分。贯通配线例如沿z方向连续。

84.例如,读出线rl、写入线wl、共通线cl、将它们和通孔配线vl连接的配线、将通孔配线vl之间连接的配线是面内配线。面内配线例如处于基板sb和第一元件组之间的层级、及第一元件组和第二元件组之间的层级。读出线rl例如沿x方向延伸。读出线rl例如有与磁畴壁移动元件100连接的读出线rl1和与磁畴壁移动元件110连接的读出线rl2。读出线rl1、rl2例如经由电极e与磁畴壁移动元件100、110的铁磁性层20、60连接。写入线wl例如沿x方向延伸。写入线wl例如经由沿y方向延伸的配线与到达晶体管tr的通孔配线vl连接。共通线cl例如沿y方向延伸。

85.磁畴壁移动元件100和磁畴壁移动元件110处于层叠结构体ls的不同的层级。磁畴壁移动元件100处于第一层级,磁畴壁移动元件110处于第二层级。磁畴壁移动元件100、110

分别与例如基板sb的晶体管tr中的任一个连接。例如,在x方向上相邻的晶体管tr与不同层级的磁畴壁移动元件100、110连接。例如,在x方向上相邻的晶体管tr与不同层级的磁畴壁移动元件100、110连接。例如,沿x方向排列的第二列和第三列晶体管tr控制磁畴壁移动元件100,第一列和第四列晶体管tr控制磁畴壁移动元件110。

86.图8是第一实施方式的集成装置id所具备的磁畴壁移动元件100、110的剖视图。图8是以穿过磁畴壁移动层10、50的y方向的宽度的中心的xz平面分别切断磁畴壁移动元件100、110的截面。

87.磁畴壁移动元件100、110例如如图4~7所示集成于集成装置id。磁畴壁移动元件100在x方向上的长度比磁畴壁移动元件110短。因此,磁畴壁移动元件100的x方向上的两端例如配置为成为磁畴壁移动元件110的x方向上的两端的内侧。从z方向观察,磁畴壁移动元件110与磁畴壁移动元件100至少一部分重叠。

88.磁畴壁移动元件100具有磁畴壁移动层10、非磁性层30以及铁磁性层20。磁畴壁移动层10例如处于比铁磁性层20靠基板sb侧。磁畴壁移动元件110具有磁畴壁移动层50、非磁性层70以及铁磁性层60。磁畴壁移动层50例如处于比铁磁性层60靠基板sb侧。磁畴壁移动元件100、110是三端子型磁阻效应元件,x方向的长度比y方向的长度长。磁畴壁移动元件100和磁畴壁移动元件110在x方向上的长度不同。磁畴壁移动元件110在x方向上的长度比磁畴壁移动元件100长。磁畴壁移动元件100和磁畴壁移动元件110的其它结构及形状大致相同。

89.磁畴壁移动层10、50沿x方向延伸。从z方向俯视时,磁畴壁移动层10、50例如为x方向是长轴、y方向是短轴的矩形。磁畴壁移动层10、50夹着非磁性层30、70与铁磁性层20、60对置。就磁畴壁移动层10、50而言,第一端与第一开关元件sw1连接,第二端与第二开关元件sw2连接。

90.磁畴壁移动层10、50包含铁磁性体。磁畴壁移动层10、50是能够根据内部的磁性状态的变化而对信息进行磁记录的层。磁畴壁移动层10、50可以具有磁性状态不同的第一磁区a1和第二磁区a2。第一磁区a1的磁化m

a1

和第二磁区a2的磁化m

a2

例如向相反方向取向。例如第一磁区a1的磁化m

a1

向 z方向取向,第二磁区a2的磁化m

a2

向-z方向取向。第一磁区a1和第二磁区a2的边界是磁畴壁dw。磁畴壁移动层10、50能够在内部具有磁畴壁dw。如果在磁畴壁移动层10、50的长边方向上流通磁畴壁移动层10、50的临界电流密度以上的电流,则磁畴壁dw移动。

91.如果磁畴壁dw移动,则磁畴壁移动层10、50中的第一磁区a1和第二磁区a2的比率变化。磁畴壁dw通过使写入电流沿磁畴壁移动层10、50的x方向流通而移动。如果磁畴壁移动层10、50中的第一磁区a1和第二磁区a2的比率变化,则磁畴壁移动元件100、110的电阻值变化。磁畴壁移动元件100、110的电阻值根据夹着非磁性层30、70的铁磁性层的磁化的相对角而变化。磁畴壁移动元件100、110的电阻值根据磁畴壁移动层10、50的磁化m

a1

、m

a2

和铁磁性层20、60的磁化m

20

、m

60

的相对角而变化。

92.即磁畴壁移动元件100、110的电阻值取决于磁畴壁移动层10、50中的第一磁区a1和第二磁区a2的比率、及磁畴壁移动层10、50的磁化m

a1

、m

a2

和铁磁性层20、60的磁化m

20

、m

60

的相对角。

93.如果第一磁区a1的比率变高,则磁畴壁移动元件100、110的电阻值减小。在第一磁

区a1的比率最大时,磁畴壁移动层10、50的磁化和铁磁性层20、60的磁化m

20

、m

60

处于平行的关系,磁畴壁移动元件100、110的电阻值成为最小电阻值。如果第二磁区a2的比率变高,则磁畴壁移动元件100、110的电阻值变大。在第二磁区a2的比率最大时,磁畴壁移动层10、50的磁化和铁磁性层20、60的磁化m

20

、m

60

成为反平行的关系,磁畴壁移动元件100、110的电阻值成为最大电阻值。

94.磁畴壁移动元件100、110例如通过改变磁畴壁dw的位置,将电阻值变为模拟。磁畴壁移动元件100、110的电阻值或者电阻值的倒数即电导与神经网络nn中的传递单元的权重对应。

95.将规定的脉冲施加到磁畴壁移动元件100、110时的磁畴壁移动元件100的电阻变化率比磁畴壁移动元件110的电阻变化率大。在对电阻值r的磁畴壁移动元件施加了规定的脉冲时的电阻值为r

′

的情况下,电阻变化率p由下式(1)表示。在此,将磁畴壁移动元件的最大电阻值及最小电阻值分别设为r

max

、r

min

。

96.p=|r

′

-r|/(r

max

-r

min

)

···

(1)

97.图9是表示磁畴壁移动元件100、110的电阻值和对磁畴壁移动元件100、110施加的脉冲数的关系的映像图。在图9中,作为一例,示出由于脉冲输入而电阻值增加的映像图,但在本实施方式中,也可以使用由于脉冲输入而电阻值减少的磁畴壁移动元件。图9(a)是关于磁畴壁移动元件100的图表,图9(b)是关于磁畴壁移动元件110的图表。就磁畴壁移动元件100、110而言,电导相对于施加的脉冲数进行线性变化,但因为动态范围狭窄,所以如图9所示,电阻值进行线性变化。这样,作为磁畴壁移动元件,可以使用电阻值相对于施加的脉冲数进行非线性变化的磁畴壁移动元件,也可以使用电阻值相对于施加的脉冲数进行线性变化的磁畴壁移动元件。在图9中,例示出磁畴壁移动元件100的最大电阻值rmax及最小电阻值rmin和磁畴壁移动元件110的最大电阻值rmax及最小电阻值rmin相同的情况,但也可以不同。

98.在长边方向上,磁畴壁移动元件110的磁畴壁移动层50比磁畴壁移动元件100的磁畴壁移动层10长。如果对磁畴壁移动元件100、110施加规定的脉冲,则磁畴壁dw移动,第一磁区a1和第二磁区a2的比率变化。因为磁畴壁移动层10、50的长度不同,所以即使在磁畴壁dw的移动量相同的情况下,施加规定的脉冲引起的第一磁区a1和第二磁区a2的比率变化的比例在磁畴壁移动元件100和磁畴壁移动元件110中也不同。即施加规定的脉冲后的磁畴壁移动元件100的电阻变化率比磁畴壁移动元件110的电阻变化率大。在此,规定的脉冲是磁畴壁移动层10、50的临界电流密度以上的任意的脉冲。临界电流密度是使磁畴壁dw移动所需的电流密度。

99.这样,因为磁畴壁移动元件110的电阻变化率比磁畴壁移动元件100的电阻变化率小,所以磁畴壁移动元件110能够细分电阻值。即,磁畴壁移动元件110与磁畴壁移动元件100比较,分辨率高。通过将磁畴壁移动元件110配置于神经网络nn中的输出层lout侧,能够对传递的信息赋予各种权重。

100.分辨率也能够通过钉扎点进行调节。在钉扎点上,磁畴壁dw不易移动,第一磁区的磁化m

a1

及第二磁区的磁化m

a2

被强力固定。钉扎点例如是磁畴壁移动层10、50的凹凸。磁畴壁移动层10、50也可以具备多个钉扎点。从提高分辨率的观点来看,磁畴壁移动层50也可以具备比磁畴壁移动层10多的钉扎点。例如,磁畴壁移动层50的下表面501的表面粗糙度也可

以比磁畴壁移动层10的下表面11的表面粗糙度粗糙。

101.磁畴壁移动层10、50由磁性体构成。磁畴壁移动层10、50也可以是铁磁性体、亚铁磁性体、或它们和能够通过电流改变磁性状态的反铁磁性体的组合。磁畴壁移动层10、50优选具有选自由co、ni、fe、pt、pd、gd、tb、mn、ge、ga构成的组中的至少一个元素。作为用于磁畴壁移动层10、50的材料,可举出例如co和ni的层叠膜、co和pt的层叠膜、co和pd的层叠膜、mnga系材料、gdco系材料、tbco系材料。mnga系材料、gdco系材料、tbco系材料等亚铁磁性体的饱和磁化小,使磁畴壁dw移动所需的阈值电流变小。另外,co和ni的层叠膜、co和pt的层叠膜、co和pd的层叠膜的矫顽力大,磁畴壁dw的移动速度变慢。反铁磁性体例如是mn3x(x为sn、ge、ga、pt、ir等)、cumnas、mn2au等。磁畴壁移动层10、50也可以包含与后述的铁磁性层20、60相同的材料。另外,磁畴壁移动层10、50也可以包含与后述的铁磁性层20、60相同的材料,且为层叠结构。例如,磁畴壁移动层10、50也可以是co、pd、cofeb的层叠膜。

102.非磁性层30例如层叠于磁畴壁移动层10。非磁性层70例如层叠于磁畴壁移动层50。非磁性层30、70处于磁畴壁移动层10、50和铁磁性层20、60之间。

103.非磁性层30、70例如由非磁性绝缘体、半导体或金属构成。非磁性绝缘体是例如al2o3、sio2、mgo、mgal2o4、及它们的al、si、mg中的一部分被zn、be等取代的材料。这些材料的带隙大,绝缘性优异。在非磁性层30、70由非磁性绝缘体构成的情况下,非磁性层30、70是隧道势垒层。非磁性金属是例如cu、au、ag等。非磁性半导体是例如si、ge、cuinse2、cugase2、cu(in,ga)se2等。

104.非磁性层30、70的厚度优选为以上,更优选为以上。如果非磁性层30、70的厚度厚,则磁畴壁移动元件100、110的电阻面积积(ra)变大。磁畴壁移动元件100、110的电阻面积积(ra)优选为1

×

104ωμm2以上,更优选为1

×

105ωμm2以上。磁畴壁移动元件100、110的电阻面积积(ra)由一个磁畴壁移动元件100、110的元件电阻和磁畴壁移动元件100、110的元件截面积(由xy平面切断非磁性层30、70的切截面的面积)的积表示。

105.铁磁性层20处于非磁性层30上。铁磁性层60处于非磁性层70上。铁磁性层20具有向一方向取向的磁化m

20

。铁磁性层60具有向一方向取向的磁化m

60

。铁磁性层20、60的磁化m

20

、m

60

在被施加规定的外力时与第一磁区a1及第二磁区a2的磁化m

a1

、m

a2

相比,不易磁化反转。规定的外力是例如通过外部磁场施加于磁化的外力或通过自旋极化电流施加于磁化的外力。铁磁性层20、60有时被称为磁化固定层、磁化参照层。

106.铁磁性层20、60包含铁磁性体。铁磁性层20、60例如在磁畴壁移动层10、50之间包含容易获得相干隧道效应的材料。铁磁性层20、60包含例如选自由cr、mn、co、fe及ni构成的组的金属、包含一种以上这些金属的合金、包含这些金属和b、c及n中的至少一种以上的元素的合金等。铁磁性层20、60例如是co-fe、co-fe-b、ni-fe。

107.铁磁性层20、60例如也可以是惠斯勒合金。惠斯勒合金是半金属,具有高的自旋极化率。惠斯勒合金是具有xyz或x2yz的化学成分的金属间化合物,x在周期表上是co、fe、ni或者cu族的过渡金属元素或贵金属元素,y是mn、v、cr或者ti族的过渡金属或x的元素种类,z是iii族~v族的典型元素。作为惠斯勒合金,可举出例如co2fesi、co2fege、co2fega、co2mnsi、co2mn

1-a

feaalbsi

1-b

、co2fege

1-c

gac等。

108.也可以在铁磁性层20、60的与非磁性层30、70相反侧的面上隔着隔离层设置磁性层。铁磁性层20、60、隔离层、磁性层成为合成反铁磁性结构(saf结构)。合成反铁磁性结构

由夹着非磁性层的两个磁性层构成。通过铁磁性层20、60和磁性层进行反铁磁性耦合,与没有磁性层的情况相比,铁磁性层20、60的矫顽力变大。磁性层可以包含例如铁磁性体,也可以包含irmn、ptmn等反铁磁性体。隔离层包含例如选自由ru、ir、rh构成的组中的至少一种。

109.磁畴壁移动元件100、110的各层的磁化的方向能够通过例如测定磁化曲线来确认。磁化曲线例如能够使用moke(magneto optical kerr effect)测定。基于moke的测定为如下测定方法:使直线偏光入射至测定对象物,通过利用发生该偏光方向的旋转等的磁光效应(克尔磁效应)而进行。

110.接下来,对集成装置id的制造方法进行说明。集成装置id通过各层的层叠工序和将各层的一部分加工成规定的形状的加工工序而形成。各层的层叠能够使用溅射法、化学气相沉积(cvd)法、电子束蒸发法(eb蒸发法)、原子激光沉积法等。各层的加工能够使用光刻等进行。

111.首先,在基板sb的规定的位置掺杂杂质,形成源极s和漏极d。接下来,在源极s和漏极d之间形成栅极绝缘膜gi和栅极g。源极s、漏极d、栅极绝缘膜gi及栅极g成为晶体管tr。基板sb也可以使用晶体管tr周期性排列的市售的半导体基板。

112.接下来,形成直至第一层级的配线层。配线层能够使用光刻制作。

113.接下来,制作第一层级的第一元件组。首先,依次层叠铁磁性层、非磁性层、铁磁性层,并将它们加工成规定的形状。铁磁性层、非磁性层、铁磁性层分别成为磁畴壁移动层10、非磁性层30、铁磁性层20。第一元件组也能够使用光刻制作。

114.接下来,通过以相同的步骤制作第一层级和第二层级之间的配线层及第二层级的第二元件组,获得集成装置id。第二元件组能够以与第一元件组相同步骤制作。通过依次层叠铁磁性层、非磁性层、铁磁性层,并将它们加工成规定的形状,铁磁性层、非磁性层、铁磁性层分别成为磁畴壁移动层50、非磁性层70、铁磁性层60。

115.具备如上的结构的神经形态器件将属于第一元件组的磁畴壁移动元件100高度集成,同时提高属于第二元件组的磁畴壁移动元件110的分辨率。即,在本实施方式的神经形态器件中,集成性高,能够提高识别率。此外,本实施方式的神经形态器件这样的、在属于第一元件组的磁畴壁移动元件100和属于第二元件组的磁畴壁移动元件110上改变x方向上的长度,对每一层级的结构带来偏差的构想与通过在阵列内使用相同的元件等来减少每一层级的偏差的以往的技术常识背道而驰。

116.另外,本实施方式的神经形态器件也能够通过改变磁畴壁移动元件100和磁畴壁移动元件110的长度而将磁畴壁移动元件100的x方向上两端配置于磁畴壁移动元件110的x方向上的两端的内侧。通过这样的结构,能够简易地形成使神经形态器件动作所需的配线。另外,能够容纳于规定的区域内的磁畴壁移动元件100、110的数量变多。即,提高了集成装置id的电阻变化元件的集成性。

117.此外,上述的磁畴壁移动元件100和磁畴壁移动元件110的关系可以满足磁畴壁移动元件100、110中所有磁畴壁移动元件100、110,也可以满足任意的磁畴壁移动元件100、110。例如,在属于第二元件组的任一个磁畴壁移动元件110的长边方向上,属于第一元件组的任一个磁畴壁移动元件100的两端处于属于第二元件组的任一个磁畴壁移动元件110的两端的内侧即可。另外,属于第一元件组的任一个磁畴壁移动元件100和属于第二元件组的任一个磁畴壁移动元件110至少一部分重叠即可。另外,在上述的例子中,在图中示出了属

于第一元件组及第二元件组的所有磁畴壁移动元件100、110的长边方向为x方向的结构,但属于第一元件组及第二元件组的任一个磁畴壁移动元件的长边方向也可以是x方向以外的方向。

118.另外,在上述的实施方式中,在图中示出了属于第一元件组的磁畴壁移动元件100和属于第二元件组的磁畴壁移动元件110在数量上不同的情况,但属于第一元件组的磁畴壁移动元件100和属于第二元件组的磁畴壁移动元件110的数量也可以相同。

119.另外,在集成装置id动作时,也可以设为向属于第二元件组的磁畴壁移动元件110输入的写入脉冲的脉冲长度和向属于第一元件组的磁畴壁移动元件100输入的写入脉冲的脉冲长度不同的结构。例如,也可以使向磁畴壁移动元件110输入的写入脉冲的脉冲长度比向属于第一元件组的磁畴壁移动元件100输入的写入脉冲的脉冲长度长。

120.另外,也可以设为向属于第二元件组的磁畴壁移动元件110输入的写入脉冲的脉冲振幅和向属于第一元件组的磁畴壁移动元件100输入的写入脉冲的脉冲振幅不同的结构。例如,也可以使向磁畴壁移动元件110输入的写入脉冲的脉冲振幅比向磁畴壁移动元件100输入的写入脉冲的脉冲振幅大。

121.通过向磁畴壁移动层50施加的写入脉冲的大小(脉冲长度、脉冲振幅)与向磁畴壁移动层10施加的写入脉冲的大小不同,能够精密地调整神经形态器件中的各层级中的分辨率。

122.例如,通过增大向磁畴壁移动层50施加的写入脉冲的大小,能够抑制磁畴壁dw被捕捉到阱位。即,能够提高磁畴壁移动元件110的动作的可靠性。脉冲的大小例如由与集成装置id连接的写入电路控制。

123.(第二实施方式)

124.图10是用于第二实施方式的神经形态器件的集成装置id1的俯视图。图10去除读出线rl、写入线wl、共通线cl进行图示。图11是将第二实施方式中的集成装置id1的属于第一元件组的磁畴壁移动元件100及属于第二元件组的磁畴壁移动元件111的附近放大的剖视图。图12是以穿过磁畴壁移动层10、51的x方向的中心的yz平面分别切断磁畴壁移动元件100、111的截面。第二实施方式的神经形态器件在磁畴壁移动元件111的宽度w111比磁畴壁移动元件100的宽度w100宽的点上与第一实施方式不同。在第二实施方式中,对与第一实施方式相同的结构标注相同的符号,并省略说明。

125.磁畴壁移动元件111具有磁畴壁移动层51、非磁性层71以及铁磁性层61。磁畴壁移动元件111与磁畴壁移动元件110在y方向上的长度不同。属于第二元件组的磁畴壁移动元件111的磁畴壁移动层51、非磁性层71及铁磁性层61的y方向上的长度比属于第一元件组的磁畴壁移动元件100的磁畴壁移动层10、非磁性层30及铁磁性层20的y方向上的长度长。即,磁畴壁移动元件111的宽度w111比磁畴壁移动元件100的宽度w100大。在此,磁畴壁移动元件的宽度是指磁畴壁移动层的上表面和铁磁性层的下表面的各个宽度的平均。

126.从z方向观察集成装置id1,磁畴壁移动元件100被磁畴壁移动元件111覆盖。

127.第二元件组配置于比第一元件组靠神经网络nn的输出层lout侧。如上所述,属于第二元件组的磁畴壁移动元件111的数量也可以比属于第一元件组的磁畴壁移动元件100的数量少。在属于第二元件组的磁畴壁移动元件111的数量比属于第一元件组的磁畴壁移动元件100的数量少的情况下,与一个读出电流rl相连的磁畴壁移动元件111的数量比与一

个读出配线rl相连的磁畴壁移动元件100的数量少。因此,就一个读出配线rl的输出合计而言,第二元件组一方比第一元件组小。在一个读出配线rl的输出合计小到无法判别的情况下,成为神经形态器件的学习错误的原因。

128.在第二实施方式的神经形态器件中,因为磁畴壁移动元件111的磁畴壁移动层51、非磁性层71及铁磁性层61的y方向上的长度长,所以能够减小层叠方向上的电阻值。即,能够增大读出时在磁畴壁移动元件111中流通的电流。因此,能够增大读出时的来自磁畴壁移动元件111的输出。因此,能够抑制神经形态器件中的学习错误。另外,即使是第二实施方式的神经形态器件,也能够实现与第一实施方式的神经形态器件相同的效果。

129.此外,在图10~12中,示出从z方向观察,磁畴壁移动元件100被磁畴壁移动元件111覆盖的状态。通过设为这样的配置,集成装置id1中的磁畴壁移动元件100、111的集成性得以提高。然而,本实施方式的磁畴壁移动元件100和磁畴壁移动元件111的配置不限于该例,也可以如第一实施方式那样是磁畴壁移动元件100与磁畴壁移动元件111一部分重叠的结构。另外,在图12中,示出了磁畴壁移动元件100、111的yx截面形状倾斜的例子,但也可以是未倾斜的结构。

130.(第三实施方式)

131.图13是用于第三实施方式的神经形态器件的集成装置id2的俯视图。图13去除读出线rl、写入线wl、共通线cl进行图示。图14是将第三实施方式的神经形态器件的两个磁畴壁移动元件100、110的附近放大的俯视图。第三实施方式的神经形态器件的磁畴壁移动元件100及磁畴壁移动元件110的配置与第一实施方式的神经形态器件不同。在第三实施方式中,对与第一实施方式相同的结构标注相同的符号,并省略说明。

132.在本实施方式中,从z方向观察,属于第二元件组的磁畴壁移动元件110不与属于第一元件组的磁畴壁移动元件100重叠。

133.越是在比磁畴壁移动元件110靠下层存在各种结构体,制作磁畴壁移动元件110时的层叠面地平坦性越降低。其原因在于,直至层叠面为止的加工的次数增加。从z方向观察,在不与磁畴壁移动元件100重叠的位置配置磁畴壁移动元件110,由此,能够提高制作磁畴壁移动元件110时的层叠面地平坦性。

134.如果制作磁畴壁移动元件110时的层叠面的平坦性高,则磁畴壁移动层50的下表面的平坦性提高。

135.第三实施方式的神经形态器件实现与第一实施方式的神经形态器件相同的效果。另外,第三实施方式的神经形态器件通过减小磁畴壁移动层10和磁畴壁移动层50的粗糙度的差而写入动作的可靠性优异。

136.(第四实施方式)

137.图15是用于第四实施方式的神经形态器件的集成装置id3的剖视图。图15中,磁畴壁移动元件100和磁畴壁移动元件110中的一部分经由连接配线cw连接。在第四实施方式中,对与第一实施方式相同的结构标注相同的符号,并省略说明。

138.磁畴壁移动元件100例如与最接近的磁畴壁移动元件110不经由基板sb电连接、而经由连接配线cw连接。磁畴壁移动元件100无需全部与磁畴壁移动元件110连接,也可以是任一个。例如,磁畴壁移动元件100的铁磁性层20与磁畴壁移动元件110的磁畴壁移动层50连接。

139.连接配线cw也可以具有垂直开关元件vsw。垂直开关元件vsw是由沿z方向层叠的层叠膜构成的开关元件。例如,如双向阈值开关(ots:ovonic threshold switch)这样利用结晶层的换相的元件、如金属绝缘体转变(mit)开关这样利用能带结构的变化的元件、如齐纳二极管及雪崩二极管这样利用击穿电压的元件、随着原子位置的变化而传导性变化的元件是垂直开关元件vsw。

140.如果将磁畴壁移动元件100和磁畴壁移动元件110用连接配线cw连接,则形成从读出线rl2经由磁畴壁移动元件100、110到达共通线cl的电流路径。即,能够读出将磁畴壁移动元件100的电阻值和磁畴壁移动元件110的电阻值组合的合成电阻。在神经形态器件中,磁畴壁移动元件100、110的电阻值或者电阻值的倒数即电导与权重对应。上述的电流路径能够表达将两个磁畴壁移动元件100、110的权重合成的新的权重。因此,使用第四实施方式的集成装置id2的神经形态器件能够由两个磁畴壁移动元件100、110表达三个权重,能够进行更复杂的运算,表达力提高。

141.(第五实施方式)

142.在上述实施方式中,例示出第一元件组及第二元件组包括磁畴壁移动元件的情况,但本发明不限于该例。第一元件组及第二元件组也可以包括其它电阻变化元件。第五实施方式的神经形态器件在使用磁畴壁移动元件100、110以外的电阻变化元件作为电阻变化元件的点上与第一实施方式的神经形态器件不同。另外,第五实施方式的神经形态器件在属于第一元件组的电阻变化元件的长边方向上的长度也可以比属于第二元件组的电阻变化元件的长边方向上的长度长的点上与第一实施方式的神经形态器件不同。另外,在第五实施方式的神经形态器件中,就有助于电阻变化元件的电阻变化的部分的体积而言,优选的是,属于第二元件组的电阻变化元件一方比属于第一元件组的电阻变化元件大。其它结构与第一实施方式的神经形态器件相同,省略详细的说明。

143.第五实施方式的神经形态器件具备包括多个电阻变化元件的第一元件组及第二元件组。在第五实施方式的神经形态器件中,就输入了规定的脉冲时的电阻变化率而言,属于第一元件组的各个电阻变化元件一方大于属于第二元件组的各个电阻变化元件。以下,为了便于说明,将属于第一元件组的电阻变化元件称为第一电阻变化元件,将属于第二元件组的电阻变化元件称为第二电阻变化元件。

144.使用在施加的脉冲数和电阻值之间存在相关关系的任意元件作为第一电阻变化元件及第二电阻变化元件。作为第一电阻变化元件及第二电阻变化元件,使用例如使用相变存储器(pcm:phase change memory)的元件、电阻变化型存储器(reram:resistive random access memory)、碳纳米管存储器(nram:nanotube random access memory)、使用利用强关联电子电子系统的ceram(correlated electron random access memory)的元件等。pcm逐步控制结晶和非晶质的换相。reram在tao2等介质中形成基于金属析出的导电丝,利用电阻变化。用作第一电阻变化元件和第二电阻变化元件的电阻变化元件的种类可以相同,也可以不同。

145.图16是用于第五实施方式的神经形态器件的集成装置id4的剖视图的一例。第五实施方式的神经形态器件在具备由相变存储器构成的电阻变化元件120、130的点上与第一实施方式的神经形态器件不同。电阻变化元件120是例如处于第一层级的第一电阻变化元件,电阻变化元件130是例如处于第二层级的第二电阻变化元件。

146.电阻变化元件120、130与第一实施方式的磁畴壁移动元件100、110不同,是二端子型元件。电阻变化元件120、130分别具备例如沿层叠方向重叠的下部电极e1、e3、功能层15、75、及上部电极e2、e4。下部电极e1、e3与通孔配线vl连接。电阻变化元件120、130的上部电极e2、e4与配线l连接。下部电极e1、e3和通孔配线vl也可以是一体,上部电极e2、e4和配线l也可以是一体。

147.电阻变化元件130设置于比例如电阻变化元件120远离基板sb的位置。就电阻变化元件120而言,例如至少一部分与电阻变化元件130重叠。从z方向俯视时,电阻变化元件120所有的端部也可以处于电阻变化元件130的全部的内侧。在这样的结构中,电阻变化元件120的长边方向上的两端处于电阻变化元件130的长边方向上的两端的内侧。电阻变化元件120也可以设为例如比电阻变化元件130多。

148.功能层15、75包含ge-sb-te等硫族化物,例如由硫族化物构成。如果对功能层15、75施加高电压而使大电流流通,则功能层15、75进行焦耳加热,如果超过熔点,则超过熔点的区域熔解。之后,如果使电压紧急下降,则功能层15、75骤冷,通过焦耳加热而熔解的区域从结晶状态向非晶态变化,电阻值增大(重置动作)。在此,从结晶状态向非晶态变化的区域取决于向功能层15、75施加的电压和下部电极e1、e3的与层叠方向垂直的面积。向功能层15、75施加的电压越大,从结晶状态向非晶态变化的区域越大。另外,在功能层15、75中,功能层15、75的与层叠方向垂直的面积越大,能够从结晶状态向非晶态变化的区域越大。从结晶状态变为非晶态的功能层15、75如果施加比进行重置动作的电压低且足够高的电压,则从非晶态向结晶状态变化,电阻值减小(设置动作)。这样,功能层15、75由通过焦耳加热而电阻值变化的材料构成。将增大电阻值的动作称为重置动作,将减小电阻值的动作称为设置动作。

149.从z方向俯视时的功能层15的面积也可以比功能层75的面积小,为功能层75的面积的2/3倍以下或1/2倍以下。在此,功能层15的x方向上的长度及y方向上的长度也可以均比功能层75的x方向上的长度及y方向上的长度短。通过将电阻变化元件120、130的功能层15、75的面积设为如上所述的结构,能够在电阻变化元件130中扩大能够通过焦耳加热而结晶状态变化的区域,能够使电阻值更多值地变化。另外,由于电阻变化元件120的集成性高,能够设置成比电阻变化元件130的数量多。

150.功能层75的厚度t75例如也可以比功能层15的厚度t15厚,为厚度t15的3/2倍以上或2倍以上。通过将电阻变化元件120、130的功能层15、75的厚度设为如上所述的结构,能够使电阻变化元件130中通过焦耳加热而结晶状态能够变化的区域增大,能够使电阻值更多值地变化。

151.下部电极e1的与层叠方向垂直的面积例如也可以比下部电极e3的与层叠方向垂直的面积小,为下部电极e3的与层叠方向垂直的面积的2/3倍或1/2倍。在下部电极e1、e3中,如果减小与层叠方向垂直的面积,则能够减小重置动作所需的重置电流。在电阻变化元件120、130中,通过将下部电极e1、e3的与层叠方向垂直的面积的关系设为如上所述的结构,能够减小数量比电阻变化元件130多的电阻变化元件120的重置电流,能够减小所需的电力。

152.功能层15、75的主面中,就基板sb侧的面的表面粗糙度而言,功能层75一方也可以比功能层15粗糙。

153.集成装置id4例如通过各层的层叠工序和将各层的一部分加工成规定的形状的加工工序而形成。各层能够活用与集成装置id相同的方法进行层叠。即,与集成装置id同样,在基板sb上设置晶体管tr后,形成直至第一层级的配线层。形成直至第一层级的配线层。

154.在层叠至第一层级后,配线层能够使用光刻制作。接下来,制作第一层级的第一元件组。首先,依次层叠下部电极、功能层及上部电极,并将它们加工成规定的形状。下部电极、功能层及上部电极分别成为下部电极e1、功能层15及上部电极e2。第一元件组也能够使用光刻形成。接下来,通过以与上述的工序相同的步骤形成第一层级和第二层级之间的配线层及第二层级的第二元件组,获得集成装置id4。

155.此外,在图16所示的例子中图示出从z方向俯视时电阻变化元件120及电阻变化元件130重叠的结构,但从z方向俯视时,电阻变化元件120及电阻变化元件130也可以不重叠。

156.进行了重置动作时的电阻值变化取决于从结晶状态变为非晶态的区域相对于功能层15、75整体的大小的比率(变化比率)。从结晶状态向非晶态变化的区域的大小相对于向功能层15、75施加的脉冲的大小具有正相关。在比功能层15大的功能层75中,通过使脉冲的大小变细,与功能层15相比,能够使变化比率细微地变化。

157.图17是用于第五实施方式的神经形态器件的集成装置id5的剖视图的一例。集成装置id5的电阻变化元件121、131的功能层16、76的材料与集成装置id4的电阻变化元件120、130的功能层15、75不同。另外,集成装置id5的下部电极e1、e3的大小与集成装置id4不同。在集成装置id5中,对与集成装置id4相同的结构标注相同的符号,并省略说明。

158.电阻变化元件121、131与电阻变化元件120、130同样,是二端子型元件。电阻变化元件121、131例如是reram。作为reram,也能够应用单极型及双极型、以及导电丝型及界面型中的任一种。电阻变化元件121是例如处于第一层级的第一电阻变化元件,电阻变化元件131是例如处于第二层级的第二电阻变化元件。

159.电阻变化元件121、131分别具备例如沿层叠方向重叠的下部电极e1、e3、功能层16、76、及上部电极e2、e4。下部电极插头e1、e3与通孔配线vl连接。电阻变化元件121、131的上部电极e2、e4与配线l连接。

160.电阻变化元件131设置于例如比电阻变化元件121远离基板sb的位置。就电阻变化元件121而言,例如至少一部分与电阻变化元件131重叠。从z方向俯视时,电阻变化元件121所有的端部也可以处于电阻变化元件131的全部的内侧。在这样的结构中,电阻变化元件121的长边方向上的两端处于电阻变化元件131的长边方向上的两端的内侧。电阻变化元件121也可以设为例如比电阻变化元件131多。

161.功能层16、76包含钙钛矿型金属氧化物等包含多个金属元素的多元系金属氧化物、或由一种金属元素和氧构成的二元系金属氧化物,例如由多元系金属氧化物或二元系金属氧化物构成。具体而言,作为构成功能层16、76的材料,使用tio

x

、tao

x

、hfo

x

、srruo3、氧化石墨烯等。

162.在使用绝缘性高的金属氧化物作为功能层16、76的情况下,电阻变化元件121、131例如示出导电丝型动作机构。

163.在导电丝型动作机构中,在金属氧化物内形成作为导电性路径的导电丝,之后,通过利用电压施加而焦耳热或电化学效应引起的金属氧化物的氧化还原反应来开闭导电丝的一部分,由此,改变电阻变化元件121、131的电阻值。

164.以下,对具体的动作原理进行说明。

165.如果对功能层16、76施加足够高的电压,则形成从上部电极e2、e4连接到下部电极e1、e3的导电路径(成型)。以下,在本实施方式中,将该导电路径称为导电丝。

166.接下来,如果向上部电极e2、e4及下部电极e1、e3之间施加电压并向导电丝施加电流,则导电丝的一部分变化而形成的导电丝断开。即,能够清除电阻变化元件121、131的信息(重置动作)。在进行重置动作时,电阻变化元件121、131的功能层16、76的电阻值变大。

167.之后,如果使电流在上部电极e2、e4及下部电极e1、e3之间流通,则再次形成从上部电极e2、e4连接到下部电极e1、e3的导电丝。即,能够向电阻变化元件121、131写入信息(设置动作)。在进行设置动作时,电阻变化元件121、131的功能层16、76的电阻值减小。

168.表示导电丝型动作原理的、形成于电阻变化元件121、131的功能层16、76的导电丝的数量不限于一个,有时是多个。功能层76的与z方向垂直的面积比功能层16的与z方向垂直的面积大。因此,电阻变化元件131形成有一个导电丝时的电阻值变化比电阻变化元件121小。因此,电阻变化元件131的分辨率比电阻变化元件121高。另外,电阻变化元件121比电阻变化元件131小,能够进行高度集成化。

169.在使用半导体性金属氧化物作为功能层16、76的情况下,电阻变化元件121、131例如示出界面型动作机构。

170.在界面型动作机构中,如果向下部电极e2、e4及上部电极e1、e3之间施加电压,则由于两电极之间的电场而在接合界面附近发生缺氧,功能层16、76的电阻值变化。

171.电阻变化元件121、131的元件面积越大,界面型动作机构中的电阻值越难以变化。因此,在元件面积大的电阻变化元件131中,耗电量大。从减小耗电量的观点来看,电阻变化元件131的数量也可以比电阻变化元件121的数量少。

172.从z方向俯视时的功能层16的面积也可以比功能层76的面积小,是功能层76的面积的2/3倍以下或1/2倍以下。在此,功能层16的x方向上的长度及y方向上的长度也可以均比功能层76的x方向上的长度及y方向上的长度短。通过将电阻变化元件121、131的功能层16、76的面积设为如上所述的结构,能够在电阻变化元件131中扩大能够通过导电丝形成或界面的氧化还原等而电阻变化的区域,能够使电阻值更多值地变化。另外,电阻变化元件121的集成性高,能够设置成比电阻变化元件131的数量多。

173.从提高电阻变化元件131的分辨率的观点来看,功能层76的厚度t76例如也可以比功能层16的厚度t16厚,为厚度t16的3/2倍以上或2倍以上。另一方面,在电阻变化元件131的数量比电阻变化元件121的数量少的情况下,从抑制由电阻变化元件131构成的元件组的电流的合计小至无法检测的观点来看,电阻变化元件131的功能层76的厚度t76例如也可以比电阻变化元件121的功能层16的厚度t16薄。

174.下部电极e1的与层叠方向垂直的面积例如也可以比下部电极e3的与层叠方向垂直的面积小,为下部电极e3的与层叠方向垂直的面积的2/3倍或1/2倍。

175.功能层16、76的主面中,就基板sb侧的面的表面粗糙度而言,功能层76一方也可以比功能层16粗糙。

176.集成装置id5由与集成装置id4相同的方法制造。即使是具备集成装置id5的神经形态器件,也实现与第一实施方式的神经形态器件相同的效果。

177.图18是表示第一电阻变化元件及第二电阻变化元件的电阻值和向第一电阻变化

元件及第二电阻变化元件施加的脉冲数的关系的映像图。图18(a)是关于第一电阻变化元件的图表,图18(b)是关于第二电阻变化元件的图表。如果向第一电阻变化元件及第二电阻变化元件施加的脉冲数增加,则第一电阻变化元件及第二磁阻效应元件的电阻值增加。在图18中,作为一例,示出了由于脉冲输入而电阻值增加的映像图,但在本实施方式中也可以使用由于脉冲输入而电阻值减小的电阻变化元件。此外,第一电阻变化元件及第二电阻变化元件的电阻值有时相对于施加的脉冲数进行非线性变化。即使在这样的情况下,就输入了规定的脉冲时的电阻变化率而言,第一电阻变化元件一方比第二电阻变化元件大。在此,即使在使用电阻值相对于施加的脉冲数进行非线性变化的第一电阻变化元件及第二电阻变化元件的情况下,电阻变化率p也是由与第一实施方式相同的式(1)所示的电阻变化率。

178.p=|r

′

-r|/(r

max

-r

min

)

···

(1)

179.在图18中,r

max

是第一电阻变化元件及第二电阻变化元件的电阻值的最大值,r

min

是第一电阻变化元件及第二电阻变化元件的电阻值的最小值。另外,在式(1)中,|r

′

-r|是向第一电阻变化元件及第二电阻变化元件施加了一次脉冲时的第一电阻变化元件及第二电阻变化元件电阻值的各个变化量的最大值。在第一电阻变化元件中,|r

′

-r|=r2-r1,在第二电阻变化元件中,|r

′

-r|=r2-r1。此外,在第一电阻变化元件和第二电阻变化元件中,电阻值的最大值及最小值可以相同,也可以不同。

180.即使是本实施方式的神经形态器件,也获得与第一实施方式的神经形态器件相同的效果。

181.(变形例)

182.在上述的实施方式中,用于使磁畴壁移动元件110的磁畴壁dw移动的临界电流密度的大小jc2也可以比用于使磁畴壁移动元件100的磁畴壁dw移动的临界电流密度的大小jc1小。即,磁畴壁移动元件100、110也可以满足jc2<jc1的关系。通过磁畴壁移动元件100、110满足jc2<jc1,能够抑制使磁畴壁移动元件110的磁畴壁dw移动所需的耗电量。磁畴壁移动元件110有时要求比磁畴壁移动元件100高的分辨率,获得适当的电阻值所需的脉冲数多。磁畴壁移动元件100、110的临界电流密度jc1、jc2能够根据例如磁畴壁移动层10、50的结构、形状、材料等改变。例如,通过以下的方法,磁畴壁移动元件100、110能够满足jc2<jc1的关系。

183.(变形例1)

184.图19是以穿过磁畴壁移动层10、53的y方向中心的xz平面分别切断磁畴壁移动元件100、112的截面。是用于变形例1的神经形态器件的磁畴壁移动元件的剖视图。图19表示属于第一元件组的磁畴壁移动元件100和属于第二元件组的磁畴壁移动元件112。磁畴壁移动元件112具有磁畴壁移动层52。磁畴壁移动元件112在磁畴壁移动层52的z方向上的厚度h52薄的点上与磁畴壁移动元件110不同。其它结构与磁畴壁移动元件110相同,标注相同的符号并省略说明。磁畴壁移动层52的厚度h52比磁畴壁移动层10的厚度h10薄。由于磁畴壁移动层52的厚度h52比磁畴壁移动层10的厚度h10薄,从而磁畴壁移动元件100的临界电流密度jc1和磁畴壁移动元件112的临界电流密度jc2满足jc2<jc1的关系。

185.(变形例2)

186.图20是以穿过磁畴壁移动层10、53的x方向的中心的yz平面分别切断磁畴壁移动元件100、113的截面。磁畴壁移动元件113属于第二元件组。磁畴壁移动元件113具有磁畴壁

移动层53、铁磁性层63以及非磁性层73。就磁畴壁移动元件113而言,y方向上的长度短,在磁畴壁移动层53的宽度w

53

及磁畴壁移动层10的宽度w

10

之间满足的关系与磁畴壁移动元件110不同。对与磁畴壁移动元件110相同的结构标注相同的符号,并省略说明。

187.存在磁畴壁移动层的临界电流密度在线宽为70nm附近变为极小这一报告(例如,t.koyama,et al.,nat.mater.10,194(2011))。因此,在磁畴壁移动层的线宽为70nm以上的情况下,磁畴壁移动层53的宽度w

53

优选比磁畴壁移动层10的宽度w

10

窄,在磁畴壁移动层的线宽为70nm以下的情况下,磁畴壁移动层53的宽度w

53

优选比磁畴壁移动层10的宽度w

10

宽。通过满足上述关系,能够使磁畴壁移动层53的临界电流密度比磁畴壁移动层10的临界电流密度低。在此,磁畴壁移动层的y方向的宽度是指上表面和下表面的各自的y方向的宽度的平均。

188.另外,磁畴壁移动层53的倾斜角θ2也可以比磁畴壁移动层10的倾斜角θ1大。通过满足这样的关系,磁畴壁移动元件100的临界电流密度jc1和磁畴壁移动元件113的临界电流密度jc2满足jc2<jc1的关系。

189.(变形例3)

190.图21是以穿过磁畴壁移动层10、54的y方向中心的xz平面分别切断磁畴壁移动元件100、114的截面。磁畴壁移动元件114属于第二元件组。变形例3中,磁畴壁移动元件114的结构与第一实施方式不同。在变形例3中,对与第一实施方式相同的结构标注相同的符号,并省略说明。

191.磁畴壁移动元件114具有磁畴壁移动层54、非磁性层70以及铁磁性层60。磁畴壁移动层54具有铁磁性层541、隔离层543以及铁磁性层542。隔离层543在z方向上被铁磁性层541和铁磁性层542夹持。铁磁性层541、542能够使用与磁畴壁移动层10及铁磁性层20相同的材料。隔离层543能够包含选自由ru、ir、rh构成的组的至少一种。

192.铁磁性层541和铁磁性层542进行磁耦合。铁磁性层541和铁磁性层542例如进行反铁磁耦合。铁磁性层541、隔离层543以及铁磁性层542是合成反铁磁性结构(saf结构)。通过满足这样的关系,磁畴壁移动元件100的临界电流密度jc1和磁畴壁移动元件114的临界电流密度jc2满足jc2<jc1的关系。

193.(变形例4)

194.图22是以穿过磁畴壁移动层10、50的y方向中心的xz平面分别切断磁畴壁移动元件105、115的截面。磁畴壁移动元件115属于第二元件组。变形例4在磁畴壁移动元件105、115分别具备配线层40或配线层80的点上与第一实施方式不同。在第五实施方式中,对与第一实施方式相同的结构标注相同的符号,并省略说明。

195.配线层40、80与磁畴壁移动层10、50相接。配线层40、80处于沿z方向与非磁性层30、70夹着磁畴壁移动层10、50的位置。配线层40、80例如处于沿z方向与铁磁性层20、60重叠的位置。配线层40也可以是处于磁畴壁移动层10、50和通孔配线vl之间。

196.配线层40、80包含具有通过电流流通时的自旋霍尔效应产生自旋电流的功能的金属、合金、金属间化合物、金属硼化物、金属碳化物、金属硅化物、金属磷化物中的任一种。

197.配线层40、80例如包含非磁性重金属作为主元素。主元素是构成配线层40、80的元素中比例最高的元素。配线层40、80例如包含具有钇(y)以上的比重的重金属。就非磁性重金属而言,原子序数39以上的原子序数大,且在最外层壳上具有d电子或f电子,因此,产生

强的自旋轨道相互作用。自旋霍尔效应通过自旋轨道相互作用而产生,在配线层40、80内,自旋容易分布不均,容易产生自旋电流js。配线层40、80包含选自例如由au、hf、mo、pt、w、ta构成的组中的任一种。

198.构成配线层80的材料的自旋霍尔角比构成配线层40的材料的自旋霍尔角大。“自旋霍尔角”是自旋霍尔效应的强度的指标之一,表示产生的自旋电流相对于沿着配线层40、80流通的电流的转换效率。即,自旋霍尔角的绝对值越大,向磁畴壁移动层10、50注入的自旋量越增加,赋予磁化越大的自旋轨道扭矩(sot)。通过满足这样的关系,磁畴壁移动元件100的临界电流密度jc1和磁畴壁移动元件115的临界电流密度jc2满足jc2<jc1的关系。

199.在上述的实施方式及变形例中,示出属于第二元件组的所有磁畴壁移动元件的长边方向上的长度比属于第一元件组的所有磁畴壁移动元件的长边方向上的长度长的例子,但本发明不限于该例。例如,第一元件组及第二元件组也可以都是具有磁畴壁移动元件100及磁畴壁移动元件110,且第一元件组中的磁畴壁移动元件110的比率比属于第二元件组的磁畴壁移动元件110的比率一方高的结构。这样的结构也提高第二元件组中的分辨率,提高第一元件组中的神经形态器件的识别率及磁畴壁移动元件的集成性。

200.另外,在上述的实施方式及变形例中,以将越接近输出层lout的层级,越精细地改变向传递单元施加的权重的神经网络nn再现记载为前提。即,将越接近输出层lout的层级,要求越高的分辨率记载为前提。然而,本发明不限于该例。就神经网络而言,也有时越接近输入层的层级,要求越高的分辨率。为了再现这样的神经网络,本实施方式的神经形态器件也可以是第一元件组位于比第二元件组靠输入层侧的结构。

201.至此,提示了几个实施方式,并提示了集成装置及神经形态器件的一例。然而,本发明不限于该实施方式,在不变更发明的主旨的范围内能够进行各种变更。

202.例如,图23是变形例5的神经形态器件的第一元件组的磁畴壁移动元件106及第二元件组的磁畴壁移动元件116的剖视图。如图23所示,磁畴壁移动层10、50也可以处于比铁磁性层20、60远离基板sb的位置。图23被称为磁化的稳定性较高的铁磁性层20、60处于基板sb侧的底销结构。图23所示的底销结构与图8所示的顶部引脚结构相比,磁化的稳定性高。

203.除此之外,也可以将上述的实施方式及变形例的特征性结构分别组合。

204.符号说明

205.10、50、51、52、53、54

…

磁畴壁移动层

206.20、60、61、63

…

铁磁性层

207.30、70、71、73

…

非磁性层

208.15、16、75、76

…

功能层

209.40、80

…

配线层

210.100、104、105、110、111、112、113、114、115

…

磁畴壁移动元件

211.120、121、130、131

…

电阻变化元件

212.543

…

隔离层

213.a1

…

第一磁区

214.a2

…

第二磁区

215.c

…

芯片

216.c1

…

第一电路

217.c2

…

第二电路

218.c3

…

第三电路

219.cl

…

共通线

220.cw

…

连接配线

221.dw

…

磁畴壁

222.e

…

电极

223.id、id1、id2、id3

…

集成装置

224.in、in1、in2、in3、in4

…

绝缘体

225.lin

…

输入层,lm…

中间层

226.lout

…

输出层

227.ls

…

层叠结构体

228.nn

…

神经网络

229.rl、rl1、rl2

…

读出线

230.vl

…

通孔配线

231.vsw

…

垂直开关元件

232.θ1、θ2

…

倾斜角。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。