1.本发明涉及半导体制造技术领域,尤其涉及一种半导体结构的形成方法。

背景技术:

2.随着集成电路制造技术的快速发展,促使集成电路中的半导体器件的尺寸不断地缩小,使整个集成电路的运作速度将因此而能有效地提升。随着元件的尺寸要求越来越小,相应形成的导电结构的尺寸越来越小。

3.所述导电结构的形成方法为:提供半导体衬底;在半导体衬底上形成第一介质层,所述第一介质层内具有第一开口;在所述第一开口内形成第一插塞;形成所述第一插塞之后,在所述第一插塞表面和第一介质层表面形成第二介质层;在所述第二介质层内形成第二开口;形成所述第二开口之后,在所述第二开口内形成第二插塞。所述第一插塞和第二插塞构成导电结构。为了降低尺寸日益减小的导电结构的电阻,采用电阻率较小的材料形成所述导电结构。

4.然而,现有技术形成的半导体器件的性能有待提高。

技术实现要素:

5.本发明解决的技术问题是提供一种半导体结构的形成方法,以提高形成的半导体结构的性能。

6.为解决上述技术问题,本发明技术方案提供一种半导体结构的形成方法,包括:提供基底,所述基底内具有相互分立的第一导电层和第二导电层;在所述基底上形成第一介质层,所述第一介质层内具有第一开口和第二开口,且所述第一开口暴露出所述第一导电层,所述第二开口暴露出所述第二导电层;采用第一选择性化学气相沉积工艺,在所述第一开口内形成第一插塞材料层,在所述第二开口内形成第二插塞材料层,且所述第一插塞材料层的顶部表面高于所述第二插塞材料层的顶部表面;对所述第一插塞材料层和第二插塞材料层进行钝化处理;所述钝化处理之后,采用第二选择性化学气相沉积工艺,在所述第一开口内第一插塞材料层表面形成第三插塞材料层,使所述第三插塞材料层填充满所述第一开口,在所述第二开口内第二插塞材料层表面形成第四插塞材料层,使所述第四插塞材料层填充满所述第二开口,且形成所述第三插塞材料层的速率小于形成所述第四插塞材料层的速率。

7.可选的,还包括:形成所述第一插塞材料层和第二插塞材料层之后,所述钝化处理之前,对所述第一开口和第二开口暴露出的第一介质层进行第一离子注入,使高于所述第一插塞材料层表面的第一开口的宽度减小,使高于所述第二插塞材料层的第二开口的宽度减小。

8.可选的,所述钝化处理的方法包括:采用远程等离子体工艺,通入钝化气体;所述远程等离子体工艺的参数包括:所述钝化气体的入射方向与基底表面法线之间具有夹角,且所述夹角大于0度。

9.可选的,所述钝化气体包括:含氮气体,所述含氮气体包括氮气、氨气、一氧化氮或者一氧化二氮。

10.可选的,所述第一离子注入工艺的参数包括:注入第一离子,且所述第一离子的相对原子质量大于所述第一介质层中的一种元素的相对原子质量,注入能量范围为1千电子伏至100千电子伏,剂量范围为1e10原子每平方厘米至1e100原子每平方厘米,循环次数为1至1000。

11.可选的,所述第一介质层的材料含有硅元素和氧元素,所述第一离子的相对原子质量大于硅元素的相对原子质量。

12.可选的,所述第一离子包括:锗离子或者锡离子。

13.可选的,所述第一插塞材料层和第二插塞材料层的材料相同;所述第一插塞材料层和第二插塞材料层的材料包括:金属,所述金属包括铜、钨、铝、钛、氮化钛或者钽。

14.可选的,所述第一选择性化学气相沉积工艺的参数包括:通入的气体包括wf6和h2,所述wf6的流量范围为0毫升/分钟至1000毫升/分钟,所述h2的流量范围为0毫升/分钟至10000毫升/分钟,压强为0托至100托。

15.可选的,还包括:所述钝化处理之后,所述第二选择性化学气相沉积工艺之前,进行清洁处理。

16.可选的,所述清洁处理的方法包括:通入还原性气体,使所述还原性气体与第一插塞材料层和第二插塞材料层表面的杂质反应。

17.可选的,所述第三插塞材料层和第四插塞材料层的材料相同;所述第三插塞材料层和第四插塞材料层的材料包括:金属,所述金属包括铜、钨、铝、钛、氮化钛或者钽。

18.可选的,所述第二选择性化学气相沉积工艺参数包括:通入的气体包括wf6和h2,所述wf6的流量范围为0毫升/分钟至1000毫升/分钟,所述h2的流量范围为0毫升/分钟至10000毫升/分钟,压强为0托至100托。

19.可选的,还包括:在所述第一介质层、第三插塞材料层以及第四插塞材料层表面形成粘附层;在所述粘附层表面形成第五插塞材料层;平坦化所述第五插塞材料层、粘附层、第三插塞材料层以及第四插塞材料层,直至齐平于或者低于第二插塞材料层表面,在所述第一开口内形成第一插塞,在所述第二开口内形成第二插塞。

20.可选的,还包括:形成第三插塞材料层和第四插塞材料层之后,形成所述粘附层之前,对所述第一介质层进行第二离子注入,减小第一插塞材料层、第二插塞材料层、第三插塞材料层以及第四插塞材料层与第一介质层之间的缝隙。

21.可选的,所述第二离子注入的工艺参数包括:注入第二离子,且所述第二离子的相对原子质量大于所述第一介质层材料中的一种元素的相对原子质量,注入能量范围为1千电子伏至100千电子伏,剂量范围为1e10原子每平方厘米至1e100原子每平方厘米,循环次数为1至1000。

22.可选的,所述第一介质层的材料含有硅元素和氧元素,所述第二离子的相对原子质量大于硅元素的相对原子质量。

23.可选的,所述第二离子包括:锗离子或者锡离子。

24.可选的,所述基底包括:衬底和位于衬底表面的第二介质层,所述第一导电层和第二导电层位于所述第二介质层内,且所述第二介质层暴露出所述第一导电层和第二导电

层。

25.与现有技术相比,本发明的技术方案具有以下有益效果:

26.本发明技术方案提供的半导体结构的形成方法中,通过在形成第一插塞材料层和第二插塞材料层之后,对所述第一插塞材料层和第二插塞材料层进行钝化处理,所述钝化处理能够降低后续采用第二选择性化学气相沉积工艺形成膜层的速率。由于位于第一开口内的第一插塞材料层的顶部表面高于位于第二开口内的第二插塞材料层的顶部表面,所述钝化处理对第一插塞材料层造成钝化作用的程度大于对第二插塞材料层造成钝化作用的程度,使得形成第三插塞材料层的速率小于第四插塞材料层的速率,进而缩小了采用第一选择性化学气相沉积工艺,在第一开口内和第二开口内形成膜层速率的差异,使得在第一开口内形成的第一插塞材料层和第三插塞材料层的整体厚度,与第二开口内形成第二插塞材料层和第四插塞材料层的整体厚度接近,从而提高在第一开口内形成的膜层和第二开口内形成的膜层形貌均一性,有利于提高形成的半导体结构的性能。

27.进一步,在进行所述钝化处理之前,还包括:对所述第一开口和第二开口暴露出的第一介质层进行第一离子注入,注入的第一离子能够取代第一介质层材料的晶格中原子位置,且第一离子的相对原子质量大于第一介质层中的一种元素的相对原子质量,使得第一离子注入处理后的膜层膨胀,从而能够减小高于所述第一插塞材料层表面的第一开口的宽度和高于第二插塞材料层表面的第二开口的宽度。并且,所述第一插塞材料层的顶部表面高于所述第二插塞材料层的顶部表面,所述第一插塞材料层暴露出的第一开口的高度小于第二插塞材料层暴露出的第二开口的高度,所述第一离子注入使所述第一开口宽度减小的高度小于所述第二开口宽度减小的高度,从而有利于增强钝化处理对第一插塞材料层和第二插塞材料层的钝化作用,加大后续在第一开口内和第二开口内形成膜层速率的差异,从而有利于提高在第一开口内形成的膜层和第二开口内形成的膜层形貌均一性,有利于提高形成的半导体结构的性能。

28.进一步,形成第三插塞材料层和第二插塞层之后,还包括:对所述第一介质层进行第二离子注入。由于注入的第二离子能够取代第一介质层材料的晶格中原子位置,且第二离子的相对原子质量大于第一介质层中的一种元素的相对原子质量,使得第二离子注入处理后的膜层膨胀,从而能够减小第一插塞材料层、第二插塞材料层、第三插塞材料层以及第四插塞材料层与第一介质层之间的缝隙,有利于减小后续平坦化工艺中采用的研磨溶液对第一导电层和第二导电层造成的损耗,从而提高形成的半导体结构的性能。

29.进一步,通过清洁处理,通入的还原性气体与第一插塞材料层和第二插塞材料层表面的杂质反应,从而能够清除表面杂质,提高第一插塞材料层和第二插塞材料层表面光滑度,从而提高后续采用第二选择性化学气相沉积工艺形成的膜层的质量。

附图说明

30.图1至图4是一种半导体结构的形成方法各步骤的结构示意图;

31.图5至图14是本发明一实施例中的半导体结构的形成方法各步骤的结构示意图。

具体实施方式

32.需要注意的是,本说明书中的“表面”、“上”,用于描述空间的相对位置关系,并不

限定于是否直接接触。

33.首先,对现有半导体结构的性能较差的原因结合附图进行详细说明,图1至图4是一种现有半导体结构的形成方法各步骤的结构示意图。

34.请参考图1,提供基底100,所述基底100内具有相互分立的第一导电层111和第二导电层112,所述基底100上具有介质层120,所述介质层120内具有第一开口121和第二开口122,且所述第一开口121暴露出所述第一导电层111,所述第二开口122暴露出所述第二导电层112。

35.请参考图2,采用第一选择性化学气相沉积工艺,在所述第一开口121内形成第一插塞材料层131,在所述第二开口122内形成第二插塞材料层132,且所述第一插塞材料层131填充满所述第一开口121。

36.请参考图3,采用第二选择性化学气相沉积工艺,在所述第一插塞材料层131表面形成第三插塞材料层141,在所述第二插塞材料层132表面形成第四插塞材料层142,且第四插塞材料层142填充满所述第二开口122。

37.请参考图4,在所述介质层120表面、第三插塞材料层141以及第四插塞材料层142表面形成粘附层(图中未示出);在所述粘附层表面形成第五插塞材料层(图中未示出);平坦化所述第三插塞材料层141、第四插塞材料层142、粘附层、以及第五插塞材料层,直至暴露出介质层120表面。

38.上述方法中,由于选择性化学气相沉积工艺能够在第一导电层111和第二导电层112暴露出的表面上逐层生长的同时,不会在介质层120表面生长,使得形成的膜层质量较好,致密度较好,不容易产生孔洞,且不需要提前形成粘附层,从而有利于减低接触电阻。

39.然而,由于第一开口121和第二开口122内残留的副产物量不同,导致通过选择性化学气相沉积工艺形成的第一插塞材料层131和第二插塞材料层132的速率一致性较差,使得第一开口121内的第一插塞材料层131填充满第一开口121的同时,所述第二开口122内的膜层未填充满第二开口122,且生长速率较快的第一插塞材料层131容易在第二开口122的顶部发生了提前闭合,导致在第二开口122内有空洞a的产生,使得第二开口122内的导电结构的接触电阻较大。

40.为了解决所述技术问题,本发明实施例提供一种半导体结构的形成方法,包括:对所述第一插塞材料层和第二插塞材料层进行钝化处理,所述钝化处理能够降低后续采用第二选择性化学气相沉积工艺形成膜层的速率,使得在第一开口内形成的第一插塞材料层和第三插塞材料层的整体厚度,与第二开口内形成第二插塞材料层和第四插塞材料层的整体厚度接近,从而提高在第一开口内形成的膜层和第二开口内形成的膜层形貌均一性,有利于提高形成的半导体结构的性能。

41.为使本发明的上述目的、特征和有益效果能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

42.图5至图14是本发明一实施例中的半导体结构的形成方法各步骤的结构示意图。

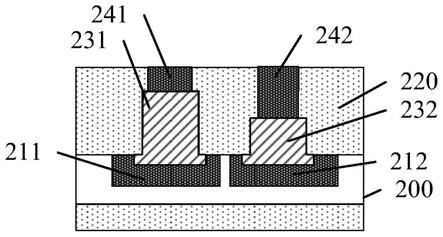

43.请参考图5,提供基底200,所述基底200内具有相互分立的第一导电层211和第二导电层212。

44.在本实施例中,所述基底200包括:衬底(图中未标示)和位于衬底表面的第二介质层(图中未标示),所述第一导电层211和第二导电层212位于所述第二介质层内,且所述第

二介质层暴露出所述第一导电层211和第二导电层212。

45.所述第一导电层211的材料包括金属,所述金属包括:铜、钨、铝、钛、氮化钛或者钽;所述第二导电层212的材料包括:金属,所述金属包括铜、钨、铝、钛、氮化钛或者钽。

46.在本实施例中,所述第一导电层211和所述第二导电层212的材料相同,均为钴。

47.所述衬底的材料包括:硅、锗、锗硅、绝缘体上硅或绝缘体上锗。在本实施例中,所述衬底的材料为硅。

48.所述第二介质层的材料为绝缘材料,包括:氧化硅、氮化硅、氮碳化硅、氮硼化硅、氮碳氧化硅或氮氧化硅中的一种或者几种。在本实施例中,所述第二介质层的材料为氧化硅。

49.请参考图6,在所述基底200上形成第一介质层220,所述第一介质层220内具有第一开口221和第二开口222,且所述第一开口221暴露出所述第一导电层211,所述第二开口222暴露出所述第二导电层212。

50.所述第一介质层220的材料为绝缘材料,包括:氧化硅、氮化硅、氮碳化硅、氮硼化硅、氮碳氧化硅和氮氧化硅中的一种或者几种。在本实施例中,所述第一介质层220的材料为氧化硅。

51.需要说明的是,在本实施例中,所述第一开口221还位于所述第一导电层211内,且所述第一开口221位于第一导电层211内部分的宽度大于位于第一介质层220内部分的宽度,即,所述第一开口221具有凸出部分,所述凸出部分能够在后续第一开口221内填充了材料并进行平坦化工艺的过程中,对所述平坦化工艺采用的研磨溶液起到一定的阻挡作用,从而减小研磨溶液对第一开口221底部的第一导电层211造成刻蚀损伤,进而有利于提高形成的半导体结构的性能。

52.同样的,在本实施例中,所述第二开口222还位于所述第二导电层212内,且所述第二开口222位于第二导电层212内部分的宽度大于位于第一介质层220内部分的宽度,同理,所述第二开口222具有凸出部分,所述凸出部分能够在后续第二开口222内填充了材料并进行平坦化工艺的过程中,对所述平坦化工艺采用的研磨溶液起到一定的阻挡作用,从而减小研磨溶液对第二开口222底部的第二导电层212造成刻蚀损伤,进而有利于提高形成的半导体结构的性能。

53.请参考图7,采用第一选择性化学气相沉积工艺,在所述第一开口221内形成第一插塞材料层231,在所述第二开口222内形成第二插塞材料层232,且所述第一插塞材料层221的顶部表面高于所述第二插塞材料层232的顶部表面。

54.所述第一插塞材料层231为后续在第一开口221内形成第一插塞提供材料;所述第二插塞材料层232为后续在第二开口222内形成第二插塞提供材料。

55.所述第一插塞材料层231和第二插塞材料层232的材料相同;所述第一插塞材料层231和第二插塞材料层232的材料包括:金属,所述金属包括铜、钨、铝、钛、氮化钛或者钽。在本实施例中,所述第一插塞材料层231和所述第二插塞材料层232的材料均为钨。

56.所述第一选择性化学气相沉积工艺的参数包括:通入的气体包括wf6和h2,所述wf6的流量范围为0毫升/分钟至1000毫升/分钟,所述h2的流量范围为0毫升/分钟至10000毫升/分钟,压强为0托至100托。

57.采用所述第一选择性化学气相沉积工艺,形成第一插塞材料层231和第二插塞材

料层232的膜层质量较好,致密度较好,不容易产生孔洞,且不需要形成粘附层,从而有利于减低接触电阻。

58.需要说明的是,所述第一介质层220包括待注入区a,所述待注入区a将被后续的第一离子注入工艺注入第一离子。

59.请参考图8,对所述第一开口221和第二开口222暴露出的第一介质层220进行第一离子注入,使高于所述第一插塞材料层231表面的第一开口221的宽度减小,使高于所述第二插塞材料层232的第二开口222的宽度减小。

60.需要说明的是,所述第一介质层220包括待注入区a,所述第一离子注入使所述待注入区a形成注入区b,且所述注入区b的宽度大于所述待注入区a的宽度。

61.所述宽度指的是垂直于第一开口221或第二开口222侧壁方向上的尺寸。

62.所述第一离子注入工艺的参数包括:注入第一离子,且所述第一离子的相对原子质量大于所述第一介质层中的一种元素的相对原子质量,注入能量范围为1千电子伏至100千电子伏,剂量范围为1e10原子每平方厘米至1e100原子每平方厘米,循环次数为1至1000。

63.由于注入的第一离子能够取代第一介质层220材料的晶格中原子位置,且第一离子的相对原子质量大于第一介质层220中的一种元素的相对原子质量,使得第一离子注入处理后的膜层膨胀,即,所述第一介质层220的待注入区a被注入第一离子之后尺寸增大,从而能够减小高于所述第一插塞材料层231表面的第一开口221的宽度和高于第二插塞材料层232表面的第二开口222的宽度,即,注入区b的宽度大于所述待注入区a的宽度。并且,所述第一插塞材料层231的顶部表面高于所述第二插塞材料层232的顶部表面,则高于所述第一插塞材料层231表面的第一开口221的高度小于高于所述第二插塞材料层表面的第二开口222的高度,所述第一离子注入使所述第一开口221宽度减小的高度小于所述第二开口222宽度减小的高度,从而有利于增强后续钝化处理对第一插塞材料层231和第二插塞材料层232的钝化作用,加大后续在第一开口221内和第二开口222内形成膜层速率的差异,从而有利于提高在第一开口221内形成的膜层和第二开口222内形成的膜层形貌均一性,有利于提高形成的半导体结构的性能。

64.所述第一离子注入工艺的剂量范围为1e10原子每平方厘米至1e12原子每平方厘米,所述第一离子注入工艺具有较高剂量范围,有利于充分使第一介质层220的注入区膨胀,使得第一插塞材料层231暴露出的第一开口221减小的程度较大,使第二插塞材料层232暴露出的第二开口222减小的程度较大,从而提高在第一开口221内形成的膜层和第二开口222内形成的膜层形貌均一性。

65.在本实施例中,所述第一介质层220的材料含有硅元素和氧元素,所述第一离子的相对原子质量大于硅元素的相对原子质量。所述第一离子为:锗离子。在其他实施例中,所述第一离子还可以为锡离子。

66.请参考图9,所述第一离子注入之后,对所述第一插塞材料层231和第二插塞材料层232进行钝化处理。

67.所述钝化处理的方法包括:采用远程等离子体工艺,通入钝化气体;所述远程等离子体工艺的参数包括:所述钝化气体的入射方向与基底表面法线之间具有夹角,且所述夹角大于0度。

68.所述钝化气体包括:含氮气体,所述含氮气体包括氮气、氨气、一氧化氮或者一氧

化二氮。在本实施例中,所述钝化气体为氮气。

69.通过对所述第一插塞材料层231和第二插塞材料层232进行钝化处理,所述钝化处理能够降低后续采用第二选择性化学气相沉积工艺形成膜层的速率。由于位于第一开口221内的第一插塞材料层231的顶部表面高于位于第二开口222内的第二插塞材料层232的顶部表面,所述钝化处理对第一插塞材料层231造成钝化作用的程度大于对第二插塞材料层232造成钝化作用的程度,使得后续形成第三插塞材料层的速率小于第四插塞材料层的速率。

70.在其他实施例中,还可以不进行所述第一离子注入工艺,形成所述第一插塞材料层和第二插塞材料层之后,对所述第一插塞材料层和第二插塞材料层进行钝化处理。

71.请参考图10,所述钝化处理之后,进行清洁处理。

72.所述清洁处理的方法包括:通入还原性气体,使所述还原性气体与第一插塞材料层和第二插塞材料层表面的杂质反应。

73.所述还原性气体包括氢气。

74.通过清洁处理,通入的还原性气体与第一插塞材料层231和第二插塞材料层232表面的杂质反应,从而能够清除表面杂质,提高第一插塞材料层231和第二插塞材料层232表面光滑度,从而提高后续采用第二选择性化学气相沉积工艺形成的膜层的质量。

75.在其他实施例中,所述钝化处理之后,还可以不进行所述清洁处理。

76.请参考图11,采用第二选择性化学气相沉积工艺,在所述第一开口221内第一插塞材料层231表面形成第三插塞材料层241,使所述第三插塞材料层241填充满所述第一开口221,在所述第二开口222内第二插塞材料层232表面形成第四插塞材料层242,使所述第四插塞材料层242填充满所述第二开口222,且形成所述第三插塞材料层241的速率小于形成所述第四插塞材料层242的速率。

77.所述第三插塞材料层241为后续在第一开口221内形成第一插塞提供材料;所述第四插塞材料层242为后续在第二开口222内形成第二插塞提供材料。

78.所述第二选择性化学气相沉积工艺参数包括:通入的气体包括wf6和h2,所述wf6的流量范围为0毫升/分钟至1000毫升/分钟,所述h2的流量范围为0毫升/分钟至10000毫升/分钟,压强为0托至100托。

79.所述第三插塞材料层241和第四插塞材料层242的材料相同;所述第三插塞材料层241和第四插塞材料层242的材料包括:金属,所述金属包括铜、钨、铝、钛、氮化钛或者钽。在本实施例中,所述第三插塞材料层241和所述第四插塞材料层242的材料为钨。

80.采用所述第一选择性化学气相沉积工艺,形成第一插塞材料层231和第二插塞材料层232的膜层质量较好,致密度较好,不容易产生孔洞,且不需要形成粘附层,从而有利于减低接触电阻。由于所述钝化处理能够降低采用选择性化学气相沉积工艺形成膜层的速率,且对第一插塞材料层231造成钝化作用的程度大于对第二插塞材料层232造成钝化作用的程度,使得采用第二选择性化学气相沉积工艺,形成第三插塞材料层241的速率小于第四插塞材料层242的速率,进而缩小了采用第一选择性化学气相沉积工艺,在第一开口221内和第二开口222内形成膜层速率的差异,使得在第一开口221内形成的第一插塞材料层231和第三插塞材料层241的整体厚度,与第二开口222内形成第二插塞材料层232和第四插塞材料层242的整体厚度接近,从而提高在第一开口221内形成的膜层和第二开口222内形成

的膜层形貌均一性,有利于提高形成的半导体结构的性能。

81.请参考图12,形成第三插塞材料层241和第四插塞材料层242之后,对所述第一介质层220进行第二离子注入,减小第一插塞材料层231、第二插塞材料层232、第三插塞材料层241以及第四插塞材料层242与第一介质层220之间的缝隙。

82.所述第二离子注入的工艺参数包括:注入第二离子,且所述第二离子的相对原子质量大于所述第一介质层材料中的一种元素的相对原子质量,注入能量范围为1千电子伏至100千电子伏,剂量范围为1e10原子每平方厘米至1e100原子每平方厘米,循环次数为1至1000。

83.由于注入的第二离子能够取代第一介质层220材料的晶格中原子位置,且第二离子的相对原子质量大于第一介质层220中的一种元素的相对原子质量,使得第二离子注入处理后的膜层膨胀,从而能够减小第一插塞材料层231、第二插塞材料层232、第三插塞材料层241以及第四插塞材料层242与第一介质层220之间的缝隙,有利于减小后续平坦化工艺中采用的研磨溶液对第一导电层211和第二导电层212造成的损耗,从而提高形成的半导体结构的性能。

84.采用所述较高注入能量范围的第二离子注入,能够使注入的第一介质层220的区域足够深,从而能够使第一开口221内的膜层和第一介质层220之间整个深度的缝隙减小,使第二开口222内的膜层和第一介质层220之间整个深度的缝隙减小,从而保证有效减小后续平坦化工艺中采用的研磨溶液对第一导电层211和第二导电层212造成的损耗,从而提高形成的半导体结构的性能。

85.在本实施例中,所述第一介质层220的材料含有硅元素和氧元素,所述第二离子的相对原子质量大于硅元素的相对原子质量。所述第二离子为锗离子。

86.在其他实施例中,所述第二离子还可以为锡离子。

87.在其他实施例中,还可以不进行所述第二离子注入。

88.请参考图13,在所述第二离子注入之后,在所述第一介质层220、第三插塞材料层241以及第四插塞材料层242表面形成粘附层251;在所述粘附层251表面形成第五插塞材料层252。

89.所述粘附层251的作用在于,所述粘附层251能够较好地形成于所述第一介质层220表面,后续第五插塞材料层252能够较好地粘附于所述粘附层251,从而使得第五插塞材料层252能够较好地形成于所述第一介质层220上。

90.所述粘附层251的材料包括:氮化钛或者氮化钽。

91.通过形成所述第五插塞材料层252,且所述第五插塞材料层252的整体表面较平整,有利于后续较好地进行平坦化工艺。

92.所述第五插塞材料层252的材料包括:金属,所述金属包括铜、钨、铝、钛、氮化钛或者钽。在本实施例中,所述第五插塞材料层252的材料为钨。

93.请参考图14,平坦化所述第五插塞材料层252、粘附层251、第三插塞材料层241以及第四插塞材料层242,直至齐平于或者低于第二插塞材料层232表面,在所述第一开口221内形成第一插塞261,在所述第二开口222内形成第二插塞262。

94.在本实施例中,所述平坦化工艺,直至齐平于第二插塞材料层232(图7中所示)表面为止。

95.所述平坦化工艺包括:化学机械研磨工艺。

96.所述化学机械研磨工艺中采用了研磨液。

97.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。