一种微型led芯片与逻辑电路基板整合结构

技术领域

1.本实用新型专利属于微型led显示屏技术领域,具体涉及一种微型led芯片与逻辑电路基板整合结构。

背景技术:

2.随着人类对显示电子产品应用的多元化,精细化,显示领域各厂商也在致力于新型显示器的研发,新型显示器的特点是更小,更精密,应用场景更加广泛,深入到人类活动的各个角落其现有主要潜在应用场景主要有可穿戴电子产品,比如ar、vr,及医疗、军事远程通讯视频等。

3.micro led(微型led)特指其单颗发光点尺寸在3

–

10μm的自发光led。

4.micro led是在镀有外延层的sapphire基底上制作单颗在3-10μm的led芯片,然后通过巨量转移的将micro led芯片焊接在带有逻辑电路的基板(一下简称cmos)上,从而满足不同的应用场景。

5.在cmos上进行led的组装完成显示屏幕的制作。常见的作法有将led组装到带有tft的基板上,或分别将led和驱动芯片组在玻璃等基板上组装等。该技术因为存在较多的步骤,其理论良率较低。

6.将led和cmos进行整合使得每个led芯片有自己的驱动,其后再在较大的基底上进行组装。该方式可以视为miniled做patchwall技术的一种延伸。每个结构单元上有自己的驱动,理论上可以提高良率和减少后续修补工艺。

7.现有技术中将led和cmos进行整合存在以下问题:1、micro led巨量转移到cmos上在共晶过程中多余金属焊料外溢形成两颗相邻led芯片短路的问题;2、micro led巨量转移过程中micro led和cmos难以精准对位的问题。以上两个问题综合导致micro led巨量转移至cmos进行整合良率低的现状。

8.为了解决以上问题,提出本实用新型。

技术实现要素:

9.本实用新型目的在于解决micro led巨量转移良率低的问题,led表面会有高度差,其基板也会有一定的翘曲度,如果共晶材料较薄会造成因为较低处的led共晶时接触不良或接触不到,从而无法点亮。如果共晶材料较厚会造成较高出的led共晶时融化的多余焊料外溢,与相邻led短路。增加了绝缘凹槽可以很好的决绝这个问题,从而提高micro led巨量转移的良率。另外,由于凹槽的存在led与cmos对位会起到预定位的作用,从而提高生产效率。

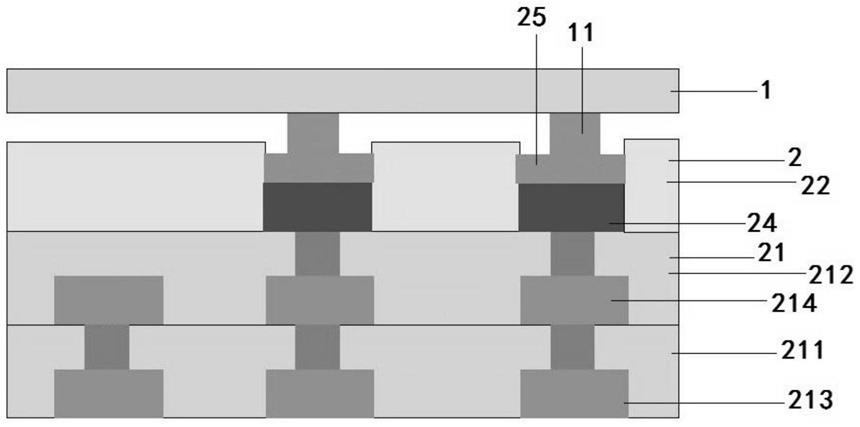

10.本实用新型提供一种微型led芯片与逻辑电路基板整合结构,其包括逻辑电路基板2,以及位于所述逻辑电路基板2上的多个微型led芯片1;

11.所述逻辑电路基板2包括驱动背板21、缓冲绝缘层23、第三金属膜24和第一焊接合金25;

12.所述缓冲绝缘层23上具有轴向贯穿所述缓冲绝缘层23的凹槽251,所述第三金属膜24和所述第一焊接合金25容纳于所述凹槽251中,所述第一焊接合金25位于所述第三金属膜24的正上方;

13.所述微型led芯片1上具有的第二焊接合金11;

14.所述逻辑电路基板2和所述微型led芯片1通过所述第一焊接合金25和所述第二焊接合金11共晶焊接整合,且所述第二焊接合金11共晶焊接后熔化后的厚度与所述第一焊接合金25的厚度与所述第三金属膜24的三者之和等于所述凹槽251的深度。

15.优选地,所述逻辑电路基板2上还具有第三绝缘层22;

16.所述第三绝缘层22位于所述驱动背板21和所述缓冲绝缘层23之间;

17.所述第三绝缘层22上具有轴向贯穿所述第三绝缘层22的第三金属膜容纳槽241,当所述逻辑电路基板2上具有第三绝缘层22时,所述第三金属膜24容纳于所述第三金属膜容纳槽241中,且所述第三金属膜24的厚度和所述第三金属膜容纳槽241的深度相同;

18.所述第一焊接合金25容纳于所述凹槽251中,且所述第二焊接合金11共晶焊接后熔化后的厚度与所述第一焊接合金25的厚度两者之和等于所述凹槽251的深度。

19.优选地,所述第三绝缘层22的材料为二氧化硅sio2或氮化硅sin等氧化绝缘材料;所述缓冲绝缘层23的材料为pln负性光刻胶;所述第三金属膜24的材料为ti钛和ni镍;所述第一焊接合金25的材料为金锡ausn。

20.优选地,第二焊接合金11的材料为金锡ausn。

21.优选地,所述驱动背板21包括第一绝缘层211和第二绝缘层212;

22.所述第一绝缘层211内具有第一金属膜213;所述第二绝缘层212内具有第二金属膜214;

23.所述第二金属膜214位于所述第三金属膜24正下方;所述第一金属膜213位于所述第二金属膜214正下方。

24.驱动背板21的结构为现有使用的常规结构。

25.本发明第二方面提供一种所述的微型led芯片与逻辑电路基板整合结构的制备方法,包括以下步骤:

26.①

取si驱动背板,上光阻;

27.②

利用曝光显影的方法,定义第三金属膜图形;

28.③

第三金属膜金属膜沉积于光阻上;

29.④

去除光阻,保留第三金属膜于指定位置;

30.⑤

沉积的缓冲绝缘层,缓冲绝缘层为具有弹性的有机材料;

31.⑥

上光阻;

32.⑦

利用曝光显影的方法,定义驱动背板侧共晶用之金属所需图形;

33.⑧

蚀刻缓冲绝缘层;

34.⑨

利用曝光显影的方法,定义驱动背板侧共晶用之第一焊接合金所需图形;

35.⑩

共晶用之第一焊接合金沉积于光阻上;

36.去除光阻,保留共晶用之第一焊接合金于指定位置;

37.巨量转移前的贴合对准,micro led基板上共晶用之第二焊接合金厚度取决于共晶后金属固化所需空间;

38.驱动背板与micro led基版贴合;

39.雷射加热,使共晶用之金属融化,持续压合,完成共晶过程。

40.本发明第三方面提供一种所述的微型led芯片与逻辑电路基板整合结构的制备方法,包括以下步骤:

41.①

取si驱动背板,上光阻;

42.②

利用曝光显影的方法,定义第三金属膜图形;

43.③

第三金属膜金属膜沉积于光阻上;

44.④

去除光阻,保留第三金属膜于指定位置;

45.⑤

沉积平坦的第三绝缘层;

46.⑥

采用化学机械平坦化(cmp),将第三绝缘层减薄至第三金属膜表面露出;

47.⑦

沉积的缓冲绝缘层,缓冲绝缘层为具有弹性的有机材料;

48.⑧

上光阻;

49.⑨

缓冲层开孔,缓冲层厚度与开孔面积取决于led与驱动背板侧共晶层金属体积;

50.⑩

上光阻;

51.利用曝光显影的方法,定义驱动背板侧共晶用之第一焊接合金所需图形;然后将共晶用之第一焊接合金沉积于光阻上;

52.去除光阻,保留共晶用之第一焊接合金于指定位置;

53.巨量转移前的贴合对准;

54.micro led基板上共晶用之第二焊接合金厚度取决于共晶后金属固化所需空间;

55.驱动背板与micro led基版贴合;

56.雷射加热,使共晶用之金属融化,持续压合,完成共晶过程。

57.相对于本发明第三方面所述的第二种情况,本发明第二方面所述的第一种情况的制备方法相当于直接取消第三绝缘层22,而是将缓冲绝缘层23一部分作为第三绝缘层22,另一部分作为缓冲绝缘层23。

58.相对于现有技术,本实用新型具有以下有益效果:

59.1、本实用新型通过在cmos金属焊接点周围镀制绝缘材料(绝缘材料为sio2等氧化绝缘材料),在绝缘材料上再形成具有凹槽的缓冲绝缘层23,形成凹槽来防止多余焊料外溢,缓冲绝缘层为具有弹性的有机材料,且所述第二焊接合金11共晶焊接后熔化后的厚度与所述第一焊接合金25的厚度两者之和等于所述凹槽251的深度。本实用新型通过设置具有凹槽的缓冲绝缘层,并控制凹槽251和第一焊接合金25量,实现共晶焊接过程中第一焊接合金25与第二焊接合金11焊接材料不外溢,且凹槽便于精准对位,从两方面解决micro led巨量转移至cmos进行整合良率低的问题。

60.2、本实用新型第一步在coms有共晶点的一面镀一层绝缘材料,绝缘材料有且不限于sio2,绝缘材料的厚度要比后续镀制的共晶焊料厚(公斤焊料一般为ausn或者insn)以便后期形成凹槽,第二步在绝缘材料表面涂一层光刻胶,通过光刻和刻蚀工艺把共晶点位置的绝缘材料去除,以漏出共晶点的金属导电材料;第三步在绝缘材料的凹槽内镀焊接材料,其先后顺序是钛(ti)、镍(ni)、金锡(ausn)或铟锡(insn)由于绝缘材料的厚度大于焊接材

料的厚度,所以在led和cmos共晶时led共晶点上的多余焊接材料融化时就不会溢出与相邻的led焊接材料连接在一起造成短路了。

61.总的来说,晶粒底部采用锡(sn)或金锡(au-sn)等合金作接触面镀层,晶粒可焊接于镀有金或银的基板上。当基板被加热至适合的共晶温度时,金或银元素渗透到金锡合金层,共晶层固化并将led焊于基板上。

62.当microled尺寸越小,对准精度要求越高,本实用新型可以透过控制led侧的共晶金属厚度,以及驱动背板侧凹槽高度吸纳因加热而融化的金属,避免相邻led电极于共晶过程导致短路或是其他共晶贴合异常等问题。具体的为,本实用新型通过控制缓冲绝缘层23上凹槽251的深度和第一焊接合金25与第二焊接合金11的厚度,实现共晶焊接过程中第一焊接合金25与第二焊接合金11焊接材料不外溢,且精准对位,从两方面解决micro led巨量转移至cmos进行整合良率低的问题。

63.3、本实用新型由于在cmos金属焊接点左右绝缘凹槽,多余焊料不会外溢,所以可以在cmos和led焊接面可以相对多的增加焊料,以防止因接触面的不平整二焊接不良的问题,由此提高了良率。

64.4、由于共晶点有绝缘凹槽,在led和cmos对位时,位置不易偏离,起到了定位的作用。

附图说明

65.图1为传统微型led芯片与逻辑电路基板共晶焊接前结构示意图;

66.图2为传统微型led芯片与逻辑电路基板整合结构示意图;

67.图3为传统微型led芯片与逻辑电路基板整合过程示意图;

68.图4为本实用新型第一种实施方式中微型led芯片与逻辑电路基板共晶焊接前结构示意图;

69.图5为本实用新型第一种实施方式中微型led芯片与逻辑电路基板整合结构示意图;

70.图6为本实用新型第一种实施方式中微型led芯片与逻辑电路基板整合过程示意图;

71.图7为本实用新型第二种实施方式中微型led芯片与逻辑电路基板共晶焊接前结构示意图;

72.图8为本实用新型第二种实施方式中微型led芯片与逻辑电路基板整合结构示意图;

73.图9为本实用新型第二种实施方式中微型led芯片与逻辑电路基板整合过程示意图;

74.附图标记的名称为:1-微型led芯片、11-第二焊接合金、2-逻辑电路基板、21-驱动背板、22-第三绝缘层、23-缓冲绝缘层、24-第三金属膜、25-第一焊接合金、211-第一绝缘层、212-第二绝缘层、213-第一金属膜、214-第二金属膜、251-凹槽。

具体实施方式

75.下面结合实施例对本实用新型作进一步的详细描述。

76.本领域技术人员将会理解,下列实施例仅用于说明本实用新型,而不应视为限定本实用新型的范围。实施例中未注明具体技术或条件者,按照本领域内的文献所描述的技术或条件或者按照产品说明书进行。所用材料或设备未注明生产厂商者,均为可以通过购买获得的常规产品。

77.本技术领域技术人员可以理解,除非特意声明,这里使用的单数形式“一”、“一个”、“所述”和“该”也可包括复数形式。应该进一步理解的是,本实用新型的说明书中使用的措辞“包括”是指存在所述特征、整数、步骤、操作、元件和/或组件,但是并不排除存在或添加一个或多个其他特征、整数、步骤、操作、元件、组件和/或它们的组。应该理解,当我们称元件被“连接”到另一元件时,它可以直接连接到其他元件,或者也可以存在中间元件。此外,这里使用的“连接”可以包括无线连接。

78.在本实用新型的描述中,除非另有说明,“多个”的含义是两个或两个以上。术语“内”、“上”、“下”等指示的方位或状态关系为基于附图所示的方位或状态关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。

79.在本实用新型的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“连接”、“设有”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连。对于本领域的普通技术人员而言,根据具体情况理解上述术语在本实用新型中的具体含义。

80.本技术领域技术人员可以理解,除非另外定义,这里使用的所有术语包括技术术语和科学术语具有与本实用新型所属领域中的普通技术人员的一般理解相同的意义。还应该理解的是,诸如通用字典中定义的那些术语应该被理解为具有与现有技术的上下文中的意义一致的意义,并且除非像这里一样定义,不会用理想化或过于正式的含义来解释。

81.以下附图及对比例实施例中,metal 3即第三金属膜,metal 2即第二金属膜,metal 1即第一金属膜,绝缘层3即第三绝缘层,绝缘层2即第二绝缘层,绝缘层1即第一绝缘层。

82.对比例

83.本对比例为传统微型led芯片与逻辑电路基板整合结构以及整合过程说明。

84.如图1-图3所示,

85.传统微型led芯片与逻辑电路基板整合过程为:

86.①

取si驱动背板,上光阻;

87.②

利用曝光显影的方法,定义第三金属膜图形;

88.③

将第三金属膜金属膜沉积于光阻上;

89.④

去除光阻,保留第三金属膜于指定位置;

90.⑤

沉积平坦的第三绝缘层;

91.⑥

第三绝缘层挖洞;

92.⑦

上光阻;

93.⑧

第三绝缘层挖孔处上的光阻开孔;

94.⑨

沉积共晶用的第一焊接合金;

95.⑩

去除光阻,保留共晶用的第一焊接合金于指定位置;

96.巨量转移前的贴合对准,micro led基板上共晶用之第二焊接合金厚度取决于共晶后金属固化所需空间。(以及缓冲层厚度);

97.驱动背板与micro led基版贴合;

98.雷射加热,使共晶用之第一焊接合金和第二焊接合金融化,持续压合。完成共晶过程。

99.这种制备存在的潜在问题:第一焊接合金和第二焊接合金金属用量评估与实际有所落差或贴合对准偏差过大,导致合金层溢出孔洞范围,造成贴合异常。

100.实施例1

101.本实施例为本发明微型led芯片与逻辑电路基板整合结构以及整合过程说明。

102.如图4-图6所示,

103.本实用新型提供一种微型led芯片与逻辑电路基板整合结构,其包括逻辑电路基板2,以及位于所述逻辑电路基板上的多个微型led芯片1;

104.所述逻辑电路基板2包括驱动背板21、第三绝缘层22、缓冲绝缘层23、第三金属膜24和第一焊接合金25;

105.所述第三绝缘层22上具有轴向贯穿所述第三绝缘层22的第三金属膜容纳槽241,所述第三金属膜24容纳于所述第三金属膜容纳槽241中,且所述第三金属膜24的厚度和所述第三金属膜容纳槽241的深度相同;

106.所述缓冲绝缘层23上具有轴向贯穿所述缓冲绝缘层23的凹槽251,所述第一焊接合金25容纳于所述凹槽251中,且所述第一焊接合金25的厚度小于所述凹槽251的深度;

107.所述凹槽251位于所述第三金属膜容纳槽241的正上方;

108.所述微型led芯片1上具有的第二焊接合金11;

109.所述逻辑电路基板2和所述微型led芯片1通过所述第一焊接合金25和所述第二焊接合金11共晶焊接整合。

110.所述第一焊接合金25和所述第二焊接合金11的厚度之和等于所述缓冲绝缘层23的厚度。所述第三绝缘层22的材料为二氧化硅sio2;所述缓冲绝缘层23的材料为pln负性光刻胶;所述第三金属膜24的材料为ti钛和ni镍;所述第一焊接合金25的材料为金锡ausn。第二焊接合金11的材料为金锡ausn。

111.所述驱动背板21包括第一绝缘层211和第二绝缘层212;所述第一绝缘层211内具有第一金属膜213;所述第二绝缘层212内具有第二金属膜214;所述第二金属膜214位于所述第三金属膜24正下方;所述第一金属膜213位于所述第二金属膜214正下方。

112.本发明微型led芯片与逻辑电路基板整合过程为:

113.①

取si驱动背板,上光阻;

114.②

利用曝光显影的方法,定义第三金属膜图形;

115.③

第三金属膜金属膜沉积于光阻上;

116.④

去除光阻,保留第三金属膜于指定位置;

117.⑤

沉积平坦的第三绝缘层(相邻第三金属膜的隔离);

118.⑥

采用化学机械平坦化(cmp),将第三绝缘层减薄至第三金属膜表面露出;

119.⑦

沉积的缓冲绝缘层(缓冲绝缘层为具有弹性的有机材料);

120.⑧

上光阻;

121.⑨

缓冲层开孔(缓冲层厚度与开孔面积取决于led与驱动背板侧共晶层金属体积);

122.⑩

上光阻;

123.利用曝光显影的方法,定义驱动背板侧共晶用之第一焊接合金所需图形;然后将共晶用之第一焊接合金沉积于光阻上(厚度小于100nm);

124.去除光阻,保留共晶用之第一焊接合金于指定位置;

125.巨量转移前的贴合对准;

126.micro led基板上共晶用之第二焊接合金厚度取决于共晶后金属固化所需空间。(以及缓冲层厚度);

127.驱动背板与micro led基版贴合;

128.雷射加热,使共晶用之金属融化,持续压合,完成共晶过程。

129.实施例2

130.本实施例为本发明微型led芯片与逻辑电路基板整合结构以及整合过程说明。

131.如图7-图9所示,

132.本实用新型提供一种微型led芯片与逻辑电路基板整合结构,其包括逻辑电路基板2,以及位于所述逻辑电路基板上的多个微型led芯片1;

133.所述逻辑电路基板2包括驱动背板21、缓冲绝缘层23、第三金属膜24和第一焊接合金25;

134.所述缓冲绝缘层23上具有轴向贯穿所述缓冲绝缘层23的第三金属膜容纳槽241,所述第三金属膜24容纳于所述第三金属膜容纳槽241中,且所述第三金属膜24的厚度和所述第三金属膜容纳槽241的深度相同;

135.所述缓冲绝缘层23上具有轴向贯穿所述缓冲绝缘层23的凹槽251,所述第一焊接合金25容纳于所述凹槽251中,且所述第一焊接合金25的厚度小于所述凹槽251的深度;

136.所述凹槽251位于所述第三金属膜容纳槽241的正上方;

137.所述微型led芯片1上具有的第二焊接合金11;

138.所述逻辑电路基板2和所述微型led芯片1通过所述第一焊接合金25和所述第二焊接合金11共晶焊接整合。

139.所述第一焊接合金25和所述第二焊接合金11的厚度之和等于所述缓冲绝缘层23的厚度。所述第三绝缘层22的材料为二氧化硅sio2;所述缓冲绝缘层23的材料为pln负性光刻胶;所述第三金属膜24的材料为ti钛和ni镍;所述第一焊接合金25的材料为金锡ausn。第二焊接合金11的材料为金锡ausn。在此实施例中直接取消了第三绝缘层22,也就是说,将第三绝缘层22和缓冲绝缘层23可以合并为缓冲绝缘层23。

140.所述驱动背板21包括第一绝缘层211和第二绝缘层212;所述第一绝缘层211内具有第一金属膜213;所述第二绝缘层212内具有第二金属膜214;所述第二金属膜214位于所述第三金属膜24正下方;所述第一金属膜213位于所述第二金属膜214正下方。

141.①

取si驱动背板,上光阻;

142.②

利用曝光显影的方法,定义第三金属膜图形;

143.③

第三金属膜金属膜沉积于光阻上;

144.④

去除光阻,保留第三金属膜于指定位置;

145.⑤

沉积的缓冲绝缘层(缓冲绝缘层为具有弹性的有机材料)(相邻第三金属膜的隔离);

146.⑥

上光阻;

147.⑦

利用曝光显影的方法,定义驱动背板侧共晶用之金属所需图形;

148.⑧

蚀刻缓冲绝缘层;

149.⑨

利用曝光显影的方法,定义驱动背板侧共晶用之第一焊接合金所需图形;

150.⑩

共晶用之第一焊接合金沉积于光阻上(厚度小于100nm);

151.去除光阻,保留共晶用之第一焊接合金于指定位置;

152.巨量转移前的贴合对准,micro led基板上共晶用之第二焊接合金厚度取决于共晶后金属固化所需空间。(以及缓冲层厚度);

153.驱动背板与micro led基版贴合;

154.雷射加热,使共晶用之金属融化,持续压合,完成共晶过程。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。