1.本发明属于集成电路设计与应用领域,具体涉及一种高速数据转换器中的同步分频电路。

背景技术:

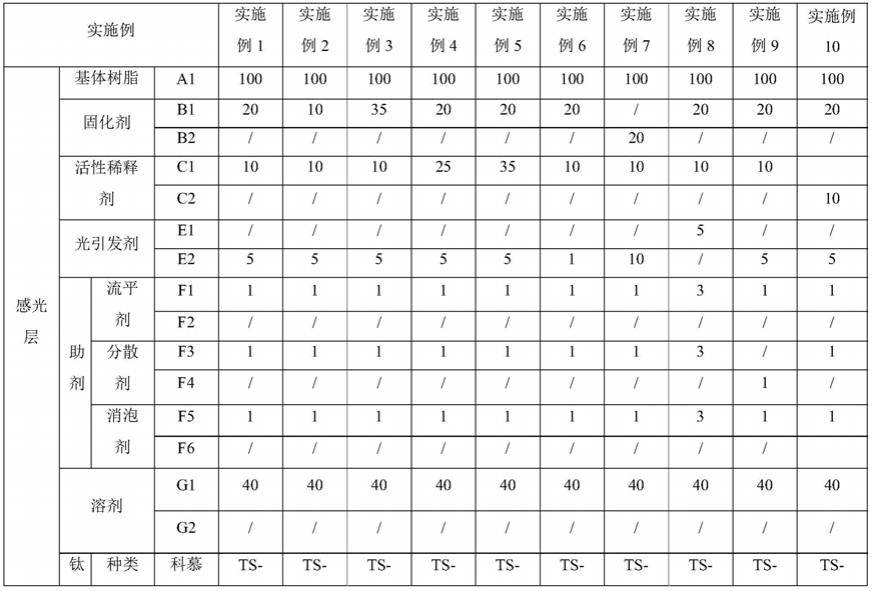

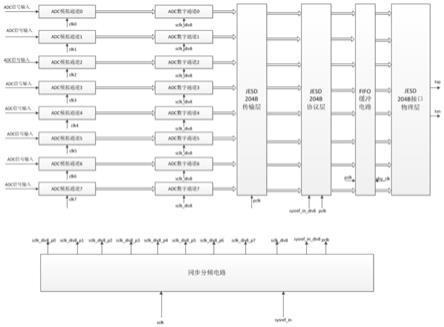

2.随着微电子技术和通信技术的迅猛发展,高集成度的相控阵数字雷达已经变得可行和越来越迫切。接收与发射通道是相控阵数字雷达的重要组成部分。一部相控阵数字雷达通常需要上千甚至过万个接收通道,它们的性能好坏直接决定相控阵雷达整体性能关键因素。对于宽带雷达系统来说,转换器超过ghz的高速高精度adc芯片是雷达收发链路中的核心器件。相比于传统的mhz级别的adc芯片,受限于工艺的限制,采样速率超过ghz的高速adc在内核设计时大多采用多通道交织的方法;在数据传输设计时,传统的低速率的cmos并行接口已经无法满足芯片低功耗、小型化的需求,取而代之的是采用jesd204b协议的高速串行的seders接口,来实现adc的高速数据传输。同步时钟分频电路对多通道交织adc通道间的数据路径的相位关系以及不同时钟域之间的数据同步至关重要。传统的低速率adc时钟分频电路如附图1所示。低速下adc多采用单通道实现,并不需要进行多通道交织方法,实现较为简单。附图2是高速数据转换器的时钟域架构,在采样率为ghz级别的高速高精度adc一方面,为降低电路实现压力,采用多通道交织架构来实现,这就需要与采样时钟电路同步的多相位分频时钟,还需要保证adc模拟电路和adc数字电路的同步关系;另一方面,高速高精度adc大都采用基于jesd204b协议的serdes进行数据传输,在协议层和adc数字电路之间、协议层和物理层之间都需要做跨时钟域的同步信号处理。

技术实现要素:

3.本发明的目的在于针对高速高精度adc的同步分频电路设计难点,提出了一种应用于高速高精度adc系统的同步分频电路装置,解决了多通道交织架构的高速高精度adc电路的同步电路设计问题。具体内容如下:用于产生高速交织型架构adc的工作时钟,包括adc模拟通道工作时钟,adc数字通道工作时钟,jesd204b传输层工作时钟,jesd204b协议层工作时钟,fifo缓冲电路工作时钟。

4.所述的一种同步分频电路,包括8分频器电路,8x1时钟选择器电路,同步取沿电路1,2分频器电路1, 打拍扩展电路1,同步取沿电路2,2分频器电路2,打拍扩展电路2,同步取沿电路3,2分频器电路3,打拍扩展电路3,2x1时钟选择器电路1,2x1时钟选择器电路2,2x1时钟选择器电路3和sysref同步器。

5.所述8分频器电路,根据采样时钟sclk产生相位相差固定的8分频时钟sclk_div8_p0、sclk_div8_p1、sclk_div8_p2、sclk_div8_p3、sclk_div8_p4、sclk_div8_p5、sclk_div8_p6、sclk_div8_p7,用于8通道交织架构的子adc的采样时钟,该8相分频时钟是由采样时钟sclk根据同步控制输入信号sysref_in产生。

6.所述8x1时钟选择器电路,产生8分频的时钟信号sysclk_div8。用于adc数字电路采样模拟8相输入信号,该8分频的采样时钟取sclk_div8_p0、sclk_div8_p1、sclk_div8_p2、sclk_div8_p3、sclk_div8_p4、sclk_div8_p5、sclk_div8_p6、sclk_div8_p7之一。

7.所述的同步取沿电路1,将输入的同步控制信号sysref_in进行在高速采样时钟sclk域的同步处理,将输入信号的脉宽调整到一个采样周期内,用于进行2分频时钟的同步脉冲控制信号sysref_pos。

8.所述的2分频器电路1,用于根据采样时钟sclk和同步取沿电路1后的同步控制信号sysref_pos,产生输出相位固定的两分频的输同步出时钟sclk_div2。

9.所述的打拍扩展电路1,其特征在于将同步电路取沿电路1后的sysref_pos同步控制信号做脉冲扩展处理,将同步控制信号脉宽扩展成为原信号周期的两倍宽度sysref_in_div2。

10.所述同步取沿电路2,将打拍扩展电路1后的信号,经过两分频输出时钟sclk_div2同步后,产生基于sclk_div2时钟域同步脉冲信号sclk_div2_pos。

11.所述2分频器电路2,将采样时钟的两分频时钟sclk_div2通过同步取沿电路2产生的sclk_div2_pos信号,产生输出四分频时钟sclk_div4。所述的打拍扩展电路2,将同步电路取沿电路2后的sysref_div2_pos信号做脉冲扩展处理,将同步控制信号脉宽扩展成为原信号周期的四倍宽度sysref_in_div4。

12.所述同步取沿电路3,将打拍扩展电路2后的信号,通过四分频输出时钟sclk_div4同步后,产生基于sclk_div4时钟域同步脉冲信号sclk_div4_pos。

13.所述2分频器电路3,将采样时钟的四分频时钟sclk_div4通过同步取沿3电路产生的sclk_div4_pos信号,产生输出相位固定的八分频时钟sclk_div8。

14.所述的打拍扩展电路3,将同步电路取沿电路3产生的sysref_div4_pos信号做脉冲扩展处理,将同步信号脉宽扩展成为原信号周期的八倍宽度sysref_in_div8。

15.所述2x1时钟选择器电路1,根据204b协议传输层的用户模式采用2选1的时钟选择器来选择采样时钟sclk和sclk的两分频时钟sclk_div2。

16.所述2x1时钟选择器电路2,根据204b协议传输层的用户模式采用2选1的时钟选择电路来选择采样时钟sclk的四分频时钟sclk_div4和sclk的八分频时钟sclk_div8。

17.所述2x1时钟选择器电路3,根据204b协议传输层的用户模式采用2选1的时钟选择电路来选择2x1时钟选择器电路1和2x1时钟选择器电路2的时钟输出信号,产生204b接口协议层的同步时钟pclk。

18.所述sysref同步器,将打拍扩展3产生的扩展后的同步脉冲信号sysref_in_div8同步到pclk时钟域,用于204b协议链路层的本地多帧信号产生。

19.本发明的有益效果在于:本发明解决了交织架构的adc 模拟通道、adc数字通道、高速204b接口传输层、高速204b接口协议层、fifo缓冲电路、高速 204b接口物理层的同步问题,可以将同步分频电路装置应用到高速高精度dac的同步设计中,提高dac芯片的性能。

附图说明

20.图1为传统adc时钟同步方案结构框图。

21.图2为高速数据转换器的时钟域架构。

22.图3为高速数据转换器的同步分频电路。

23.图4为八相位时钟分频电路时序图。

24.图5为同步时钟分频电路时序图。

具体实施方式

25.下面结合附图与具体实施方式对本发明作进一步详细描述,但本发明的保护范围不局限于以下描述。

26.如图3所示,一种高速高精度数据转换器同步分频电路用于产生高速交织型架构adc的工作时钟,包括adc模拟通道工作时钟,adc数字通道工作时钟,jesd204b传输层工作时钟,jesd204b协议层工作时钟,fifo缓冲电路工作时钟, jesd204b物理层工作时钟。附图4和附图5为本发明电路的时序图。

27.下面对同步分频电路和方法进行详细说明。

28.高速高精度交织架构adc接收来自于时钟发生器的高精度采样时钟sysclk和低速的同步控制信号sysref_in信号,同步分频电路对输入同步控制信号sysref经过同步取沿电路,产生同步脉冲信号sysref_pos1。所述的同步取沿电路1是由3级触发器构成,其中,第1和第2级触发器用于对输入的sysref_in信号进行两级信号延迟产生sysref_r1和sysref_r2信号,第3级触发器产生sysref_r3信号,sysref_r2和sysref_r3通过异或门产生与采样时钟sclk周期相同脉宽的同步取沿信号sysref_pos1。

29.所述的8分频电路由计数器电路产生,根据同步取沿信号sysref_pos1,保证了分频时钟初始相位的确定性,delay0~delay7单元产生8个相位相差45度的8分频时钟sysclkdiv_p0,sysclkdiv_p1,sysclkdiv_p2,sysclkdiv_p3,sysclkdiv_p4,sysclkdiv_p5,sysclkdiv_p6,sysclkdiv_p7,用于给adc模拟子通道产生8相位工作时钟和adc数字通道工作时钟。如图4时序图所示,当系统时钟采样到同步取沿后的脉冲信号后,分频计数器开始清零并从0-7开始循环计数,进而精确产生8个相位的8分频时钟。

30.所述2分频电路1,用于根据同步取沿的脉中信号sysref_in_pos信号,产生初始相位固定的2分频时钟sysclk_div2。

31.所述打拍扩展电路1为一级触发器电路和异或门电路,用于产生脉宽扩展的同步信号sysref_div2_pos,脉冲宽度为采样时钟2分频的时钟周期。

32.所述同步取沿电路2为一级触发器电路和与门电路,用于产生2分频时钟脉冲宽度的同步信号。

33.所述2分频电路2,用于根据同步脉冲信号sysref_div2_pos,由2分频时钟精确产生采样时钟的4分频时钟sysclk_div4。

34.所述打拍扩展电路2为一级触发器电路和异或门电路,用于产生脉宽扩展的同步信号sysref_div4,脉冲宽度为采样时钟4分频周期时钟宽度。

35.所述同步取沿电路3为两级触发器延时电路和与门电路,用于产生4分频时钟脉宽的同步控制信号sysref_div4_pos。

36.所述2分频3电路,用于根据同步脉冲信号sysref_div4_pos,由2分频时钟精确产生采样时钟8分频时钟sysclk_div8。

37.所述打拍扩展电路3为一级触发器电路和异或门电路,用于产生脉宽扩展的同步信号sysref_div8,脉冲宽度为采样时钟8分频周期时钟宽度。

38.所述sysref同步器,为两级触发器延时电路,用于将sysclk_div8时钟域的同步信号sysref_div8同步到pclk时钟域。

39.所述2x1时钟选择电路1用来选择采样时钟sclk和两分频时钟sclk_div2,所述2x1时钟选择电路2用来选择四分频采样时钟sclk_div4和八分频采样时钟sclk_div8.所示2x1时钟选择电路3用来选择时钟选择电路1和时钟选择电路2后的时钟输出,用来作为pclk,提供给高速接口电路传输层和协议层。

40.本发明不局限于上述具体的实施方式,本发明可以有各种更改和变化。凡是依据本发明的技术实质对以上实施方式所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。