1.本发明涉及集成电路技术领域,特别涉及一种相位插值电路、锁相环、芯片及电子设备。

背景技术:

2.高性能小数锁相环中由delta-sigma调制器引入的量化相位误差会影响锁相环性能,包括增加相位噪声和杂散。在锁相环内引入相位插值器是一种降低量化相位误差的方法,如图1所示,通过对振荡器周期进行内插分割,产生步长小于振荡周期的相位信号,比如1/4、1/2、3/4振荡周期等,从而大幅降低增量总和调制量化步长,从源上降低量化噪声。

3.但是,现有各种相位插值器的误差均很大,在没有校准的情况下很大做到小于振荡周期的1%,如果直接应用于小数锁相环,其相位误差直接表现为反馈通路非线性,造成量化噪声混叠并产生较强小数杂散,从而恶化锁相环整体带内相噪,无法达到高性能锁相环的要求。

技术实现要素:

4.本发明要解决的技术问题是为了克服现有技术中相位插值器误差较大,无法达到高性能锁相环要求的缺陷,提供一种相位插值电路、锁相环、芯片及电子设备。

5.本发明是通过下述技术方案来解决上述技术问题:

6.本发明的第一方面提供一种相位插值电路,包括:相位插值器、整数分频器、控制器、第一时钟触发器、数据选择器、第二时钟触发器以及合并单元,所述数据选择器和所述第二时钟触发器的数量均为m,m为2的整数倍;

7.所述相位插值器用于对振荡器产生的振荡时钟信号进行相位插值处理,生成m个插值时钟信号;

8.所述控制器用于接收频率控制字,并根据所述频率控制字向所述整数分频器输出分频器控制字,其中,所述分频器控制字为相邻两个振荡周期的整数差值;

9.以及对所述频率控制字的小数部分进行量化处理,根据最终量化结果向每个数据选择器输出选通信号;其中,量化步长为1/m个振荡周期;

10.所述整数分频器用于根据所述分频器控制字对所述振荡时钟信号进行降频,生成第一分频时钟信号;

11.所述第一时钟触发器的数据输入端用于接收所述第一分频时钟信号,时钟输入端用于接收所述振荡时钟信号,输出第二分频时钟信号;其中,所述第二分频时钟信号比所述第一分频时钟信号的相位滞后一个振荡周期;

12.m个数据选择器的第一数据输入端均用于接收所述第一分频时钟信号,第二数据输入端均用于接收所述第二分频时钟信号,选通信号输入端均与所述控制器连接,输出端分别与m个第二时钟触发器连接;

13.m个第二时钟触发器的时钟输入端分别用于接收m个插值时钟信号;

14.所述合并单元用于将m个第二时钟触发器输出的m个相位插值信号进行等权重合并,输出反馈时钟信号。

15.可选地,所述控制器包括量化单元、数据信号调制器、处理单元;所述处理单元分别与所述量化单元和所述数据信号调制器连接;

16.所述量化单元用于根据量化步长对所述频率控制字的小数部分进行量化得到中间量化结果,并将无法量化的部分输入所述数据信号调制器;

17.所述处理单元用于根据所述数据信号调制器的输出结果和所述中间量化结果得到最终量化结果。

18.可选地,所述分频器控制字具体为当前振荡周期与前一振荡周期的整数差值。

19.可选地,所述合并单元包括第一pmos管和第二pmos管,所述第一pmos管和所述第二pmos管的数量均为m;所述第一pmos管和所述第二pmos管一一对应;

20.第一pmos管的源极和对应第二pmos管的源极均连接至同一个电流源;第一pmos管的栅极和对应第二pmos管的栅极均连接至同一个第二时钟触发器;

21.所有第一pmos管的漏极均连接,形成第一输出端;所有第二pmos管的漏极均连接,形成第二输出端;所述第一输出端和所述第二输出端用于输出差分的反馈时钟信号。

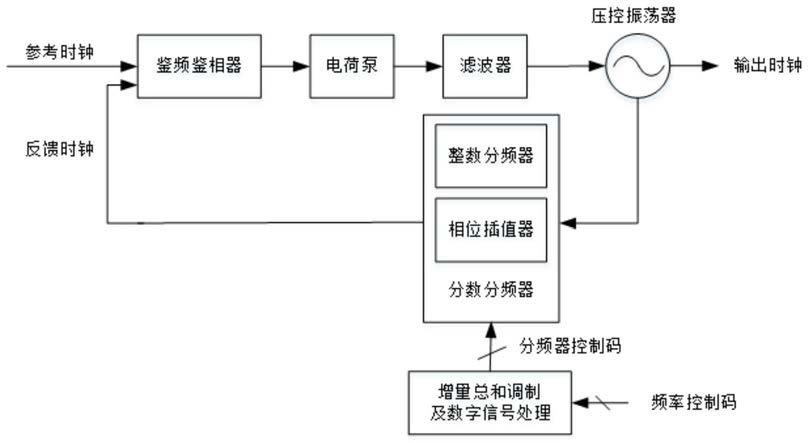

22.可选地,所述第一时钟触发器和/或所述第二时钟触发器为d触发器。

23.本发明的第二方面提供一种锁相环,包括如第一方面所述的相位插值电路以及依次连接的鉴频鉴相器、电荷泵、滤波器、振荡器,所述相位插值电路的输入端连接所述振荡器,输出端连接所述鉴频鉴相器。

24.可选地,所述振荡器为压控振荡器。

25.可选地,所述滤波器为低通滤波器。

26.本发明的第三方面提供一种芯片,包括如第二方面所述的锁相环。

27.本发明的第四方面提供一种电子设备,包括如第二方面所述的锁相环。

28.在符合本领域常识的基础上,上述各可选条件可任意组合,即得本发明各较佳实例。

29.本发明的积极进步效果在于:控制器通过向数据选择器输出选通信号,可以使得数据选择器输出第一分频时钟信号或者第二分频时钟信号,从而实现插值相位在本参考周期保持静止还是前进一个振荡周期,第二时钟触发器经过对应的插值时钟信号同步,输出的每个相位插值信号的相位变化以整个振荡周期为步长,可以保证输出插值相位的线性,不受相位插值器误差的影响,从而可以降低锁相环的量化噪声,改善前馈通路的线性度。

附图说明

30.图1为现有技术中小数锁相环的结构示意图。

31.图2为本发明实施例1提供的一种相位插值电路的结构框图。

32.图3为本发明实施例1提供的一种相位插值器的连接结构图。

33.图4为本发明实施例1提供的一种相位插值电路的内部结构示意图。

34.图5为本发明实施例1提供的一种后退1/8振荡周期的序列示意图。

35.图6为本发明实施例1提供的一种前进1/8振荡周期的序列示意图。

36.图7为本发明实施例1提供的一种后退1/4振荡周期的序列示意图。

37.图8为本发明实施例1提供的一种前进1/4振荡周期的序列示意图。

38.图9为本发明实施例1提供的一种合并单元的电路原理图。

39.图10为本发明实施例2提供的一种锁相环的结构示意图。

具体实施方式

40.下面通过实施例的方式进一步说明本发明,但并不因此将本发明限制在所述的实施例范围之中。

41.实施例1

42.本实施例提供一种相位插值电路,如图2所示,包括:相位插值器、整数分频器、控制器、第一时钟触发器、数据选择器、第二时钟触发器以及合并单元。其中,所述数据选择器和所述第二时钟触发器的数量均为m,m为2的整数倍。在具体实施中,所述第一时钟触发器和所述第二时钟触发器可以采用d触发器。

43.所述相位插值器用于对振荡器产生的振荡时钟信号进行相位插值处理,生成m个插值时钟信号。其中,振荡器可以为压控振荡器,所述相位插值器的精度要求不高,允许存在插值相位误差,具体可以包括加权插值电路、锁定延时线插值电路或者二进制多层加权插值电路等。

44.在如图3所示的例子中,m=8,压控振荡器vco输出的振荡时钟信号经过相位插值器的8位相位插值处理,得到8个插值时钟信号,分别为:φ0、φ1、φ2、φ3、φ4、φ5、φ6、φ7。

45.如图4所示,所述控制器用于接收频率控制字n.f,并根据所述频率控制字n.f向所述整数分频器输出分频器控制字ni。其中,所述分频器控制字为相邻两个振荡周期的整数差值。需要说明的是,相邻两个振荡周期的整数差值不一定是固定的,换句话说,控制器每个振荡周期向整数分频器输出的分频器控制字ni不一定是相同的。

46.在可选的一种实施方式中,所述分频器控制字具体为当前振荡周期与前一振荡周期的整数差值。在一个具体的例子中,假设频率控制字n.f=100.3,经过累加之后,前4个振荡周期依次为:100.3、200.6、300.9、401.2。向整数分频器输出的分频器控制字ni依次为200-100=100、300-200=100、401-300=101。

47.所述控制器还用于对所述频率控制字的小数部分即0.f进行量化处理,根据最终量化结果向每个数据选择器mux输出选通信号。其中,量化步长为1/m个振荡周期。

48.所述整数分频器用于根据所述分频器控制字对所述振荡时钟信号进行降频,生成第一分频时钟信号φ

lead

。

49.所述第一时钟触发器的数据输入端用于接收所述第一分频时钟信号,时钟输入端用于接收所述振荡时钟信号,输出第二分频时钟信号φ

lag

。其中,第二分频时钟信号φ

lag

比第一分频时钟信号φ

lead

的相位滞后一个振荡周期。

50.m个数据选择器mux的第一数据输入端均用于接收第一分频时钟信号φ

lead

,第二数据输入端均用于接收第二分频时钟信号φ

lag

,选通信号输入端均与所述控制器连接,输出端分别与m个第二时钟触发器连接。

51.m个第二时钟触发器的时钟输入端分别用于接收m个插值时钟信号。

52.所述合并单元用于将m个第二时钟触发器输出的m个相位插值信号进行等权重合并,输出反馈时钟信号。在如图4所示的例子中,8个第二时钟触发器输出8个相位插值信号,

分别为clk0、clk1、clk2、clk3、clk4、clk5、clk6、clk7。对clk0~clk7这8个相位插值信号进行等权重合并,得到反馈时钟信号。

53.本实施方式中,控制器通过向数据选择器输出选通信号,可以使得数据选择器输出第一分频时钟信号φ

lead

或者第二分频时钟信号φ

lag

,从而实现插值相位在本参考周期保持静止还是前进一个振荡周期,经过对应的插值时钟信号同步,可以保证输出插值相位的线性。

54.在可选的一种实施方式中,所述控制器包括量化单元、数据信号调制器(data signal modulator,dsm)、处理单元。所述处理单元分别与所述量化单元和所述数据信号调制器连接。所述量化单元用于根据量化步长对所述频率控制字的小数部分进行量化得到中间量化结果,并将无法量化的部分输入所述数据信号调制器。所述处理单元用于根据所述数据信号调制器的输出结果和所述中间量化结果得到最终量化结果。

55.在一个具体的例子中,假设频率控制字的小数部分为0.6,量化步长为1/8个振荡周期。根据量化步长对0.6进行量化,得到中间量化结果4/8,无法量化的部分为0.8/8,将0.8/8输入dsm,dsm输出一定概率的0或1。若dsm输出1,那么最终量化结果为4/8 1/8=5/8;若dsm输出0,那么最终量化结果为4/8 0/8=4/8。

56.需要说明的是,dsm除了可以输出0或1以外,还可以输出一定概率的负值或者其他值。在一个具体的例子中,dsm可以输出-1、0、1、2。

57.下面主要介绍控制器如何根据最终量化结果向每个数据选择器mux输出选通信号。

58.假设振荡时钟信号经过相位插值器进行相位插值处理之后,理想的插值相位可以表示为而实际插值相位与理想插值相位的误差可以表示为ε,则总平均相位可以表示为

[0059][0060]

当其中一个相位增加一个振荡周期,则总平均相位变为:

[0061][0062]

通过比较上述两个等式可知,通过移动一个相位一个整数振荡周期,m路相位插值可以实现线性1/m的量化步长,与相位误差无关。同理,移动两个相位一个整数振荡周期,m路相位插值可以实现线性2/m的量化步长;移动四个相位一个整数振荡周期,m路相位插值可以实现线性4/m的量化步长。

[0063]

以m=8为例,8个插值时钟信号按相位连续排列成序列,按照时间先后标识为插值时钟信号0、1、2、3、4、5、6、7。当位于序列前端的插值时钟信号0后退一个振荡周期,也就是说序列变成插值时钟信号1、2、3、4、5、6、7、0,其整体平均相位则后退1/8振荡周期,如图5所示。当位于序列尾部的插值时钟信号7前进一个振荡周期,也就是说序列变成插值时钟信号7、0、1、2、3、4、5、6,其整体平均相位则前进1/8振荡周期,如图6所示。当位于序列前端的插值时钟信号0和1后退一个振荡周期,也就是说序列变成插值时钟信号2、3、4、5、6、7、0、1,其整体平均相位则后退2/8即1/4振荡周期,如图7所示。当位于序列尾部的插值时钟信号6和7前进一个振荡周期,也就是说序列变成插值时钟信号6、7、0、1、2、3、4、5,其整体平均相位则

前进2/8即1/4振荡周期,如图8所示。

[0064]

在一个具体的例子中,100.3可以量化为100 2/8 0.4/8,将0.4/8输入dsm,若dsm输出0,则100.3的最终量化结果为100 2/8。控制器可以通过向数据选择器mux0~1输出选择第二分频时钟信号φ

lag

的选通信号,以及向数据选择器mux2~7输出选择第一分频时钟信号φ

lead

的选通信号,以实现整体平均相位后退2/8振荡周期,也即实现线性2/8的量化步长。

[0065]

在另一个具体的例子中,200.6可以量化为200 5/8 0.8/8,将0.8/8输入dsm,若dsm输出1,则200.6的最终量化结果为200 6/8。控制器可以通过向数据选择器mux0~5输出选择第二分频时钟信号φ

lag

的选通信号,以及向数据选择器mux6~7输出选择第一分频时钟信号φ

lead

的选通信号,以实现整体平均相位后退6/8振荡周期,也即实现线性6/8的量化步长。

[0066]

在另一个具体的例子中,300.9可以量化为300 7/8 0.2/8,将0.2/8输入dsm,若dsm输出0,则300.9的最终量化结果为300 7/8。控制器可以通过向数据选择器mux0~6输出选择第二分频时钟信号φ

lag

的选通信号,以及向数据选择器mux7输出选择第一分频时钟信号φ

lead

的选通信号,以实现整体平均相位后退7/8振荡周期,也即实现线性7/8的量化步长。

[0067]

在另一个具体的例子中,100.1可以量化为100 0.8/8,将0.8/8输入dsm,若dsm输出-1,则100.1的最终量化结果为100-1/8。在具体实施中,将100.1的最终量化结果从(100-1/8)变换为(99 7/8)。控制器可以通过向数据选择器mux0~6输出选择第二分频时钟信号φ

lag

的选通信号,以及向数据选择器mux7输出选择第一分频时钟信号φ

lead

的选通信号,以实现整体平均相位后退7/8振荡周期,也即实现线性7/8的量化步长。

[0068]

本实施方式中,振荡器产生的振荡时钟信号经过相位插值器产生多路插值时钟信号,其相位差的平均值可以等效为分数相位差值,从而可以减小量化步长。经过多路第二时钟触发器输出的每个相位插值信号的相位变化以整个振荡周期为步长,因而是线性的,不受相位插值器误差的影响,从而可以降低锁相环的量化噪声,改善前馈通路线性度。

[0069]

需要说明的是,上述合并单元可以用硬件电路的方式实现,也可以用软件方式实现。在用硬件电路实现的一种实施方式中,上述合并单元包括第一pmos管和第二pmos管,所述第一pmos管和所述第二pmos管的数量均为m;所述第一pmos管和所述第二pmos管一一对应。

[0070]

第一pmos管的源极和对应第二pmos管的源极均连接至同一个电流源。第一pmos管的栅极和对应第二pmos管的栅极均连接至同一个第二时钟触发器。所有第一pmos管的漏极均连接,形成第一输出端;所有第二pmos管的漏极均连接,形成第二输出端;所述第一输出端和所述第二输出端用于输出差分的反馈时钟信号。

[0071]

本实施方式中,第二时钟触发器输出的相位插值信号为差分信号,经过合并单元的等权重合并之后,输出的反馈时钟信号也为差分信号。

[0072]

在如图9所示的电路中,上述合并单元包括7个第一pmos管和7个第二pmos管,其中,第一pmos管q11和第二pmos管q21对应,源极均连接至电流源i1。第一pmos管q12和第二pmos管q22对应,源极均连接至电流源i2。第一pmos管q13和第二pmos管q23对应,源极均连接至电流源i3。第一pmos管q14和第二pmos管q24对应,源极均连接至电流源i4。第一pmos管

q15和第二pmos管q25对应,源极均连接至电流源i5。第一pmos管q16和第二pmos管q26对应,源极均连接至电流源i6。第一pmos管q17和第二pmos管q27对应,源极均连接至电流源i7。

[0073]

第一pmos管q11~q17的漏极均连接,形成第一输出端out-,第二pmos管q21~q27的漏极均连接,形成第二输出端out 。

[0074]

实施例2

[0075]

本实施例提供一种锁相环,如图10所示,包括实施例1中的相位插值电路以及依次连接的鉴频鉴相器、电荷泵、滤波器、振荡器,所述相位插值电路的输入端连接所述振荡器,输出端连接所述鉴频鉴相器。其中,本实施例提供的锁相环为小数锁相环。

[0076]

其中,所述鉴频鉴相器用于检测参考时钟信号与反馈时钟信号的相位误差,并输出误差信号。电荷泵用于根据误差信号生成控制电流。滤波器用于将所述控制电流转换为低频电压信号。所述振荡器用于根据所述低频电压信号生成输出振荡时钟信号。所述相位插值电路用于根据频率控制字对所述振荡时钟信号进行处理,输出反馈时钟信号。

[0077]

在可选的一种实施方式中,所述振荡器为压控振荡器。

[0078]

在可选的一种实施方式中,所述滤波器为低通滤波器。

[0079]

本实施例中,相位插值电路中输出的每个相位插值信号的相位变化以整个振荡周期为步长,可以保证输出插值相位的线性,不受相位插值器误差的影响,将其应用于锁相环可以降低锁相环的量化噪声,从而改善前馈通路的线性度。

[0080]

实施例3

[0081]

本实施例提供一种芯片,包括实施例2的锁相环。

[0082]

本实施例还提供一种电子设备,包括实施例2的锁相环。

[0083]

虽然以上描述了本发明的具体实施方式,但是本领域的技术人员应当理解,这仅是举例说明,本发明的保护范围是由所附权利要求书限定的。本领域的技术人员在不背离本发明的原理和实质的前提下,可以对这些实施方式做出多种变更或修改,但这些变更和修改均落入本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。