技术特征:

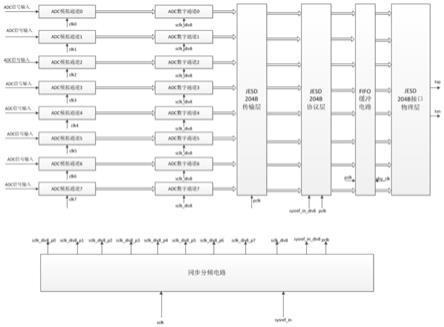

1.一种同步分频电路,用于产生高速交织型架构adc的工作时钟,包括adc模拟通道工作时钟,adc数字通道工作时钟,jesd204b传输层工作时钟,jesd204b协议层工作时钟和fifo缓冲电路工作时钟,其特征在于:包括8分频器电路,8x1时钟选择器电路,同步取沿电路1,2分频器电路1, 打拍扩展电路1,同步取沿电路2,2分频器电路2,打拍扩展电路2,同步取沿电路3,2分频器电路3,打拍扩展电路3,2x1时钟选择器电路1,2x1时钟选择器电路2, 2x1时钟选择器电路3和同步器;所述8分频器电路,根据采样时钟产生的相位相差,将固定的8分频时钟用于8通道交织架构的子adc的采样时钟,该8分频时钟由采样时钟根据同步控制输入信号产生;所述8x1时钟选择器电路,产生8分频的时钟信号,用于adc数字电路采样模拟8相输入信号,该8分频的时钟取其中之一;所述的同步取沿电路1,将输入的同步控制信号在采样时钟域进行同步处理,将输入信号的脉宽调整到一个采样周期内,用于产生2分频时钟的同步脉冲控制信号;所述的2分频器电路1,用于根据采样时钟和同步取沿电路1的同步脉冲控制信号,输出相位固定的两分频的输出同步时钟;所述的打拍扩展电路1,将同步电路取沿电路1产生的同步脉冲控制信号做脉冲扩展处理,将脉宽扩展成为原信号周期的两倍宽度;所述同步取沿电路2,将打拍扩展电路1输出的信号,经过两分频的输出同步时钟同步后,产生基于扩展处理后的同步脉冲控制信号的时钟域同步脉冲信号;所述2分频器电路2,将采样时钟的两分频时钟通过同步取沿电路2产生的时钟域同步脉冲信号,产生输出四分频时钟;所述的打拍扩展电路2,将同步电路取沿2电路后的时钟域同步脉冲信号做脉冲扩展处理,将脉宽扩展成为原信号周期的四倍宽度;所述同步取沿电路3,将打拍扩展电路2扩展后的信号,通过四分频输出时钟同步后,产生基于扩展后时钟域同步脉冲信号的时钟域同步脉冲信号;所述2分频器电路3,将四分频时钟通过同步取沿电路3产生的时钟域同步脉冲信号,产生输出相位固定的八分频时钟;所述的打拍扩展电路3,将同步电路取沿3电路产生的时钟域同步脉冲信号做脉冲扩展处理,将脉宽扩展成为原信号周期的八倍宽度;所述2x1时钟选择器电路1,根据204b协议传输层的用户模式,采用2选1的时钟选择器来选择采样时钟的两分频时钟;所述2x1时钟选择器电路2,根据204b协议传输层的用户模式,采用2选1的时钟选择电路来选择采样时钟的四分频时钟和八分频时钟;所述2x1时钟选择器电路3,根据204b协议传输层的用户模式,采用2选1的时钟选择电路来选择2x1时钟选择器电路1和2x1时钟选择器电路2的时钟输出信号,产生204b接口协议层的同步时钟;所述步器,将打拍扩展电路3产生的扩展后的同步脉冲信号同步到时钟域,用于204b协议链路层的本地多帧信号产生。

技术总结

随着微电子技术和通信技术的迅猛发展,高集成度的相控阵数字雷达已经变得可行和越来越迫切。接收与发射通道是相控阵数字雷达的重要组成部分。对于宽带雷达系统来说,转换器超过GHz的高速高精度ADC芯片是雷达收发链路中的核心器件。相比于传统的MHz级别的ADC芯片,受限于工艺的限制,采样速率超过GHz的高速ADC在内核设计时大多采用多通道交织的方法;在数据传输设计时,传统的低速率的CMOS并行接口已经无法满足芯片低功耗、小型化的需求,取而代之的是采用JESD204B协议的高速串行的SEDERS接口,来实现ADC的高速数据传输。同步时钟分频电路对多通道交织ADC通道间的数据路径的相位关系以及不同时钟域之间的数据同步至关重要。本发明的针对高速高精度ADC的同步分频电路设计难点,提出了一种应用于高速高精度ADC系统的同步分频电路装置,解决了多通道交织架构的高速高精度ADC电路的同步电路设计问题。高速高精度ADC电路的同步电路设计问题。高速高精度ADC电路的同步电路设计问题。

技术研发人员:吴俊杰 徐宏林 张浩

受保护的技术使用者:中国电子科技集团公司第十四研究所

技术研发日:2021.12.26

技术公布日:2022/4/29

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。