1.本实用新型涉及功率器件技术领域,具体涉及一种功率半导体器件表面钝化结构。

背景技术:

2.表面钝化技术是半导体器件制造过程中的重要工艺环节,对器件的电学特性和可靠性有重要影响。目前常用的一些钝化材料有二氧化硅、磷硅玻璃、氮化硅、氮氧化硅、三氧化二铝、半绝缘多晶硅、聚酰亚胺( pi)、玻璃料等,这些介质的性能不同、钝化保护作用和效果也不同。如果上述介质单一用做钝化保护,都存在局限性,所以在半导体工艺上往往采用复合的多元介质结构做钝化保护膜。

3.目前国内半导体芯片表面钝化的常规技术虽然都采用了三层或四层的多层介质复合结构,不同程度地考虑到利用多元介质取长补短获得较好的钝化保护效果。但是每一种结构都会存在局限性,其共同的弱点是未能考虑同时兼顾绝缘、吸杂、抗辐射、抵御外力和湿热等方面的综合钝化能力。如何解决上述问题,是本领域技术人员致力于解决的事情。

技术实现要素:

4.本实用新型的目的是克服现有技术的不足,提供一种功率半导体器件表面钝化结构。

5.为达到上述目的,本实用新型采用的技术方案是:一种功率半导体器件表面钝化结构,所述钝化结构包括由下至上依次叠加于硅基衬底上表面上的sio2层、psg层、si3n4层及pi层。

6.作为一种具体的实施方式,所述sio2层采用热氧化生长工艺的方式生长于硅基衬底的上表面上。

7.作为一种具体的实施方式,psg层采用lpcvd方法沉积在sio2层的上表面。

8.作为一种具体的实施方式,si3n4层采用脉冲激光沉积方法沉积在psg层的上表面。

9.作为一种具体的实施方式,所述pi层的厚度大于sio2层、psg层及si3n4层中的任一一层的厚度。

10.作为一种具体的实施方式,所述硅基衬底为n型si衬底,或者为n型si外延层,亦或者为带有n型si外延层的n型si衬底。

11.这里,所述硅基衬底内、从左至右依次间隔的设置有第一p型掺杂区、第二p型掺杂区、第三p型掺杂区及n型掺杂区,所述第一p型掺杂区和n型掺杂区分别位于硅基衬底的左右两侧端部上,所述第一p型掺杂区的面积大于第二p型掺杂区、第三p型掺杂区及n型掺杂区中任一区域的面积。

12.另外,第一p型掺杂区、第二p型掺杂区、第三p型掺杂区及n型掺杂区的纵深均不超过硅基衬底的1/2。

13.由于上述技术方案的运用,本实用新型与现有技术相比具有下列优点:本实用新

型的功率半导体器件表面钝化结构,其在硅基衬底的正面由下至上依次叠加有sio2层、psg层、si3n4层及pi层,其通过将sio2层作为第一钝化层,为器件提供了最初的保护,能与硅基衬底间实现很好的粘附,并能降低与其他钝化层之间的界面应力,为其他钝化层的沉积和功能实现提供了基础;psg层和si3n4层分别具有吸收和隔离外部杂质离子的作用;最上面的pi层能够为下方各钝化层乃至整个器件起到综合性的保护作用,该结构使得整个器件能够承受高电压的同时保持很低的漏电流。

附图说明

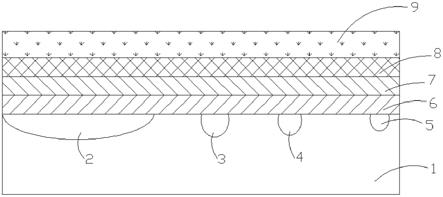

14.附图1为设置有本实用新型所述的功率半导体器件表面钝化结构的器件结构示意图;

15.其中:1、硅基衬底;2、第一p型掺杂区;3、第二p型掺杂区;4、第三p型掺杂区;5、n型掺杂区;6、sio2层;7、psg层;8、si3n4层;9、pi层。

具体实施方式

16.下面结合附图及具体实施例来对本实用新型的技术方案作进一步的阐述。

17.一种功率半导体器件表面钝化结构,参见图1所示,其包括由下至上依次叠加于硅基衬底1上表面上的sio2层6、psg层7、si3n4层8及pi层9,以此在功率半导体器件表面形成sio

2-psg

‑ꢀ

si3n

4-pi复合钝化结构。

18.具体的,所述sio2层6采用热氧化生长工艺的方式生长于硅基衬底1的上表面上,热氧化工艺生长的sio2薄膜均匀、致密、绝缘性和抗蚀性好、与硅的晶格相近,是首选的钝化基础层。将sio2层6作为第一钝化层,为器件提供了最初的保护,能与硅基衬底1间实现很好的粘附,并能降低与其他钝化层之间的界面应力,为其他钝化层的沉积和功能实现提供了基础。

19.本例中,psg层7采用lpcvd方法沉积在sio2层6的上表面;si3n4层8采用脉冲激光沉积方法沉积在psg层7的上表面。这里,psg层7和si3n4层8分别具有吸收和隔离外部杂质离子的作用。lpcvd工艺淀积的psg薄膜具有阻挡、提取和稳定sio2薄膜中钠离子(na )的作用。

20.另外,最上面的pi层9的作用是能够为下方各钝化层乃至整个器件起到综合性的保护作用,这里pi层9可采用旋涂法和热处理工艺进行制备。

21.本例中,所述pi层9的厚度大于sio2层6、psg层7及si3n4层8中的任一一层的厚度,其余三层厚度一致,该设置方式的目的是为了能够在降低整个器件厚度的同时使其具有较好的绝缘性及抗蚀性,能够在承受高电压的同时保持很低的漏电流,钝化效果明显。

22.另外,所述硅基衬底1为n型si衬底,或者为n型si外延层,亦或者为带有n型si外延层的n型si衬底。本例中,该硅基衬底1选用了n型si衬底。

23.本例中,该硅基衬底1内从左至右依次间隔的设置有第一p型掺杂区2、第二p型掺杂区3、第三p型掺杂区4及n型掺杂区5,所述第一p型掺杂区2和n型掺杂区5分别位于硅基衬底1的左右两侧端部上,所述第一p型掺杂区2的面积大于第二p型掺杂区3、第三p型掺杂区4及n型掺杂区5中任一区域的面积。第一p型掺杂区2、第二p型掺杂区3、第三p型掺杂区4及n型掺杂区5的纵深均不超过硅基衬底1的1/2。

24.上述实施例只为说明本实用新型的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本实用新型的内容并据以实施,并不能以此限制本实用新型的保护范围。凡根据本实用新型精神实质所作的等效变化或修饰,都应涵盖在本实用新型的保护范围之内。

技术特征:

1.一种功率半导体器件表面钝化结构,其特征在于,所述钝化结构包括由下至上依次叠加于硅基衬底上表面上的sio2层、psg层、si3n4层及pi层,所述pi层的厚度大于sio2层、psg层及si3n4层中的任一一层的厚度,其余三层厚度一致,所述硅基衬底内、从左至右依次间隔的设置有第一p型掺杂区、第二p型掺杂区、第三p型掺杂区及n型掺杂区,所述第一p型掺杂区和n型掺杂区分别位于硅基衬底的左右两侧端部上,所述第一p型掺杂区的面积大于第二p型掺杂区、第三p型掺杂区及n型掺杂区中任一区域的面积。2.根据权利要求1所述的功率半导体器件表面钝化结构,其特征在于,所述sio2层采用热氧化生长工艺的方式生长于硅基衬底的上表面上。3.根据权利要求1所述的功率半导体器件表面钝化结构,其特征在于,psg层采用lpcvd方法沉积在sio2层的上表面。4.根据权利要求1所述的功率半导体器件表面钝化结构,其特征在于,si3n4层采用脉冲激光沉积方法沉积在psg层的上表面。5.根据权利要求1所述的功率半导体器件表面钝化结构,其特征在于,所述硅基衬底为n型si衬底,或者为n型si外延层,亦或者为带有n型si外延层的n型si衬底。

技术总结

本实用新型公开了一种功率半导体器件表面钝化结构,所述钝化结构包括由下至上依次叠加于硅基衬底上表面上的SiO2层、PSG层、Si3N4层及PI层。本实用新型的功率半导体器件表面钝化结构,结构简单,具有较好的绝缘性及抗蚀性,能够在承受高电压的同时保持很低的漏电流,钝化效果明显。效果明显。效果明显。

技术研发人员:王源政 周炳

受保护的技术使用者:张家港意发功率半导体有限公司

技术研发日:2021.11.18

技术公布日:2022/4/26

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。