1.本发明涉及一种半导体器件及制备方法,具体涉及一种功率半导体器件及其制备方法。

背景技术:

2.近年来,为了实现高击穿电压、高频率、高温环境下应用的半导体器件,已经开始采用碳化硅作为新一代半导体器件的材料,并且已经在开关稳压电源、高频加热、电动汽车以及功率放大器等诸多领域取得了广泛的应用。碳化硅是一种比硅半导体材料能带间隙大的宽带隙半导体,也是唯一一种能够直接热氧化形成sio2栅绝缘层的宽带隙半导体材料。碳化硅金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)具有导通电阻低、开关速度快、温度可靠性高等优势,有望成为下一代高压功率开关器件。

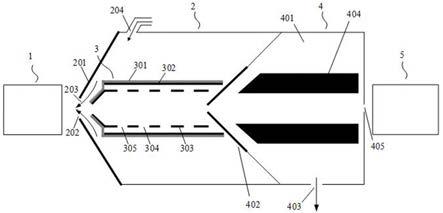

3.如图1所示的一种碳化硅功率半导体结构中,01为n 型衬底、02为n-型漂移层、03为p-型掺杂层、04为p 型第一源区、05为n 型第二源区、06为栅氧化层、07为栅极多晶硅层、08为包裹覆盖在所述的栅极上部和侧边的介质层、09为源极接触层、10为漏极、11为金属源极。其通过现在p-型掺杂层03中形成p 型第一源区04,使得p-型掺杂层03的欧姆接触面积增大,从而减小了功率半导体器件源极欧姆接触电阻,进而降低了器件功率的损耗。但如图1的结构中会采用刻蚀工艺刻蚀掉部分n 型第二源区05以露出p 型第一源区04,形成台阶式形状,这种异向刻蚀会导致梯形图形或者底部即第一源区04露出的表面不平,如图2所示,而这会导致后面工艺形成的源极接触层09接触不良,而且随着工艺特征尺寸越来越小,很有可能造成过刻蚀到第一源区04,极大的影响了器件可靠性性能。

技术实现要素:

4.发明目的:针对上述现有技术,提出一种碳化硅功率半导体器件及其制备方法,解决异向刻蚀导致第一源区表面不平整而影响源极接触层接触不良的问题。

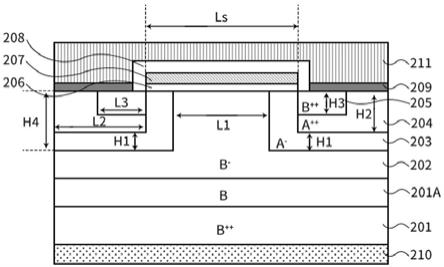

5.技术方案:一种碳化硅功率半导体器件,包括b 型衬底,所述b 型衬底的上表面设有b型外延层,所述b型外延层的上表面设有b-型漂移区,所述b-型漂移区的上表面左右两边分别向下离子注入形成a-型掺杂区,所述b-型漂移区的上表面设有栅氧化层,所述栅氧化层的上表面设有栅极多晶硅,所述栅极多晶硅横跨于左右两边的a-型掺杂区的部分区域以及之间的b-型漂移区,所述栅极多晶硅两侧的所述a-型掺杂区的上表面分别进行重掺杂形成a 型第一源区,所述a 型第一源区的上表面位于所述栅极多晶硅两侧的部分区域向下反型掺杂形成b 型第二源区,所述栅极多晶硅的上表面和侧面设有介质层,在所述a 型第一源区和b 型第二源区显露的上表面设有源极接触层,并在所述源极接触层和所述介质层的上表面淀积金属形成金属源极,所述b 型衬底的下表面设有漏极。

6.进一步的,所述a-型掺杂区的深度h4为1.0~2.5um,掺杂浓度为1

×

10

16

~9

×

10

17

cm-3

。

7.进一步的,所述a 型第一源区的底部距离所述a-型掺杂区底部的距离h1为0.5~1.5um,所述a 型第一源区的深度h2为0.5~1um,掺杂浓度为1

×

10

19

~5

×

10

21

cm-3

。

8.进一步的,所述b 型第二源区的深度h3为0.1~0.5um,掺杂浓度为1

×

10

19

~5

×

10

21

cm-3

,所述b 型第二源区的长度为所述a 型第一源区长度的1/2。

9.一种碳化硅功率半导体器件的制备方法,包括如下步骤:步骤1:在b 型衬底上外延生长b型外延层,在所述b型外延层的上表面形成b-型漂移区;步骤2:根据图形化掩膜版,通过氧化、涂胶、显影、离子注入步骤在所述b-型漂移区的左右两边分别向下轻掺杂离子注入形成a-型掺杂区;步骤3:洗掉器件表面的光刻胶,根据图形化掩膜版,在所述b-型漂移区的上表面淀积氧化物质形成栅氧化层,随后在所述栅氧化层的上表面淀积生长形成栅极多晶硅,所述栅极多晶硅横跨于左右两边的a-型掺杂区的部分区域以及之间的b-型漂移区;步骤4:在所述栅极多晶硅两侧的所述a-型掺杂区的上表面分别进行重掺杂形成a 型第一源区;步骤5:根据图形化掩膜版,通过氧化、涂胶,显影、离子注入步骤分别在所述a 型第一源区的上表面位于所述栅极多晶硅两侧的部分区域向下反型掺杂形成b 型第二源区;步骤6:洗掉器件表面的光刻胶和氧化层,通过图形化掩膜版,在所述栅极多晶硅上表面和侧面淀积介质层,并对所述介质层表面进行平坦化处理;步骤7:通过图形化掩膜版在所述a 型第一源区和b 型第二源区显露的上表面淀积形成源极接触层;步骤8:在所述b 型衬底的下表面淀积金属形成漏极,并在所述源极接触层和所述介质层的上表面淀积金属形成金属源极。

10.进一步的,所述步骤2中,所述a-型掺杂区的掺杂深度h4为1.0~2.5um,掺杂浓度为1

×

10

16

~9

×

10

17

cm-3

。

11.进一步的,所述a 型第一源区的底部距离所述a-型掺杂区底部的距离h1为0.5~1.5um,所述a 型第一源区的深度h2为0.5~1um,掺杂浓度为1

×

10

19

~5

×

10

21

cm-3

。

12.进一步的,所述b 型第二源区的深度h3为0.1~0.5um,掺杂浓度为1

×

1019~5

×

1021cm-3,所述b 型第二源区的长度l3为所述a 型第一源区长度l2的1/2。

13.有益效果:本发明在保证现有技术中减小源极欧姆接触电阻,降低器件功率损耗的前提下,通过调整源区的布局和自对准注入方式,不采用刻蚀方式,保证了第一源区和第二源区显露出的表面平整,形成了良好的源极接触层,解决了各向异性刻蚀露出部分第一源区表面不平整导致源极接触层接触不良问题,同时也解决了在工艺特征尺寸越来越小的情况下出现过刻蚀到第一源区问题,减少了工艺带来的的误差,增加了器件可靠性性能。

附图说明

14.图1为一种现有的碳化硅功率半导体结构的示意图;图2为现有技术中异向刻蚀导致第一源区表面不平的示意图;图3为本发明的碳化硅功率半导体器件的结构示意图;

图4为步骤1得到的结构示意图;图5为步骤2得到的结构示意图;图6为步骤3得到的结构示意图;图7为步骤4得到的结构示意图;图8为步骤5得到的结构示意图;图9为步骤6得到的结构示意图;图10为步骤7得到的结构示意图;图11为步骤8得到的结构示意图。

具体实施方式

15.下面结合附图对本发明做更进一步的解释。

16.如图3所示,一种碳化硅功率半导体器件,包括b 型衬底201,b 型衬底201的上表面设有b型外延层201a,b型外延层201a的上表面设有b-型漂移区202,b-型漂移区202的上表面左右两边分别向下离子注入形成a-型掺杂区203;b-型漂移区202的上表面设有栅氧化层206,栅氧化层206的上表面设有栅极多晶硅207,栅极多晶硅207横跨于左右两边的a-型掺杂区203的部分区域以及之间的b-型漂移区202;栅极多晶硅207两侧的a-型掺杂区203的上表面分别进行重掺杂形成a 型第一源区204,a 型第一源区204的上表面位于栅极多晶硅207两侧的部分区域向下反型掺杂形成b 型第二源区205;栅极多晶硅207的上表面和侧面设有介质层208;在a 型第一源区204和b 型第二源区205显露的上表面设有源极接触层209,并在源极接触层209和介质层208的上表面淀积金属形成金属源极211;b 型衬底201的下表面设有漏极210。

17.其中,a-型掺杂区203的深度h4为1.0~2.5um,掺杂浓度为1

×

10

16

~9

×

10

17

cm-3

。a 型第一源区204的底部距离a-型掺杂区203底部的距离h1为0 .5~1.5um,a 型第一源区204的深度h2为0.5~1um,掺杂浓度为1

×

10

19

~5

×

10

21

cm-3

。b 型第二源区205的深度h3为0.1~0.5um,掺杂浓度为1

×

10

19

~5

×

10

21

cm-3

,b 型第二源区205的长度为a 型第一源区204长度的1/2。导电类型a和b的方案为:a为p型,b为n型;或者,a为n型,b为p型。a 表示导电类型a的重掺杂,掺杂浓度为1e21-1e25;a-表示导电类型a的轻掺杂,掺杂浓度为1e14-5e17;b 表示导电类型b的重掺杂,掺杂浓度为1e21-1e25;b-表示导电类型b的轻掺杂,掺杂浓度为1e14-5e17。

18.以上碳化硅功率半导体器件的制备方法,包括如下步骤:步骤1:在重掺杂的b 型衬底201上外延生长b型外延层201a,在b型外延层201a的上表面形成轻掺杂的b-型漂移区202,如图4所示。

19.外延生长的b型外延层201a可以有效平衡b离子浓度分布的不均匀,使得器件有更好的耐压性。

20.步骤2:根据图形化掩膜版,通过氧化、涂胶、显影、离子注入步骤在b-型漂移区202的左右两边分别向下轻掺杂离子注入形成a-型掺杂区203,如图5所示。

21.其中,a-型掺杂区203的掺杂深度h4为1.0~2.5um,掺杂浓度为1

×

10

16

~9

×

10

17

cm-3

。a-型掺杂区203形成于b-型漂移区202的左右两侧,左右两边的a-型掺杂区203不重叠,两者之间的距离为l1,且l1必须小于后续形成的栅极多晶硅207的长度ls。

22.步骤3:洗掉器件表面的光刻胶,根据图形化掩膜版,在b-型漂移区202的上表面淀积氧化物质形成长度为ls的栅氧化层206,随后在栅氧化层206的上表面淀积生长形成长度为ls的栅极多晶硅207,栅极多晶硅207横跨于左右两边的a-型掺杂区203的部分区域以及之间的b-型漂移区202。

23.步骤4:在栅极多晶硅207两侧的a-型掺杂区203的上表面分别进行重掺杂形成a 型第一源区204,左边的a 型第一源区204的右侧与栅极多晶硅207左侧自对准,右边的a 型第一源区204的左侧与栅极多晶硅207右侧自对准,如图7所示。

24.其中,a 型第一源区204的底部距离a-型掺杂区203底部的距离h1为0.5~1.5um,a 型第一源区204的深度h2为0.5~1um,掺杂浓度为1

×

10

19

~5

×

10

21

cm-3

。

25.步骤5:根据图形化掩膜版,通过氧化、涂胶,显影、离子注入步骤分别在a 型第一源区204的上表面位于栅极多晶硅207两侧的部分区域向下反型掺杂形成b 型第二源区205,左边的b 型第二源区205的右侧与栅极多晶硅207左侧自对准,右边的b 型第二源区205的左侧与栅极多晶硅207右侧自对准,如图8所示。

26.其中,b 型第二源区205的深度h3为0.1~0.5um,掺杂浓度为1

×

10

19

~5

×

10

21

cm-3

,b 型第二源区205的长度l3为a 型第一源区204长度l2的1/2。

27.步骤6:洗掉器件表面的光刻胶和氧化层,通过图形化掩膜版,在栅极多晶硅207上表面和侧面淀积介质层208,并对介质层208表面进行平坦化处理。介质层208包裹覆盖于栅极上部和侧面,介质层208侧面的宽度不可以完全覆盖b 型第二源区205显露的表面,如图9所示。

28.此步骤中通过湿法腐蚀将表面的光刻胶和氧化层洗掉,其中洗掉氧化层的物质是一种可以洗掉氧化层但是不会与衬底材料反应的酸性无机溶剂,如氢氟酸溶液,避免了采用刻蚀方式,保证了a 型第一源区204和b 型第二源区205显露出的表面平整,形成了良好的源极接触层。

29.步骤7:通过图形化掩膜版在a 型第一源区204和b 型第二源区205显露的上表面淀积形成源极接触层209,如图10所示。

30.步骤8:在器件背面即b 型衬底201的下表面淀积金属形成漏极210,并在器件上表面即源极接触层209和介质层208的上表面淀积金属形成金属源极211,如图11所示。

31.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。