1.本公开涉及通信技术领域,特别涉及一种极化码的编码方法、极化码的译码方法、极化码的编码装置、极化码的译码装置、信息传输系统和非易失性计算机可读存储介质。

背景技术:

2.极化码(polar code)是一种前向错误更正编码方式,用于通信技术中的信号传输。极化码是一种被证明可以达到香农极限的编码译码方法。

3.在相关技术中,利用sc(successive-cancellation,连续消除)译码算法将码元按顺序连续地判定并译出。译出的过程同时也是删除的过程。sc译码算法中后一码元的判定依赖于前一码元。

4.由此带来两个问题:1.如果前一码元译码出错,后一码元以及其后码元的译码结果必然出错,并且译码错误没有机会得到纠正;2)无法实现并行译码,译码时间长。

技术实现要素:

5.本公开的发明人发现上述相关技术中存在如下问题:前一码元译码出错,后一码元以及其后码元的译码结果必然出错,并且译码错误没有机会得到纠正,导致编码和译码的性能差。

6.鉴于此,本公开提出了一种极化码的编码技术方案,能够提高编码和译码的性能。

7.根据本公开的一些实施例,提供了一种极化码的编码方法,包括:根据第一待编码码元序列,划分出m个长度为n的码元分段,m和n为2的整数次幂;分别对各码元分段中的各信息码元进行校验码生成运算,以得到各码元分段相应的校验码;利用ldpc(low-density parity-check,低密度奇偶校验)算法,对各校验码进行编码,以得到各编码校验码;根据第一待编码码元序列的极化码编码结果,确定第一编码码元序列;传输第一编码码元序列、各编码校验码,以便极化码的译码装置对第一编码码元序列进行分段译码后,利用各编码校验码对相应的码元分段中的信息码元进行校验。

8.在一些实施例中,传输第一编码码元序列、各编码校验码包括:利用ldpc信道传输各编码校验码。

9.在一些实施例中,根据第一待编码码元序列的极化码编码结果,确定第一编码码元序列包括:对第一待编码码元序列的极化码编码结果进行交织编码,确定第一编码码元序列。

10.在一些实施例中,根据第一待编码码元序列,划分出m个长度为n的码元分段包括:按照预设规则将第一待编码码元序列进行位置置换,以得到待分段码元序列;将待分段码元序列,划分为m个长度为n的码元分段。

11.在一些实施例中,将待分段码元序列,划分为m个长度为n的码元分段包括:对待分段码元序列进行分段变换处理,划分出各码元分段,分段变换处理根据待分段码元序列中不同的奇数位码元确定不同的码元分段中的奇数位码元,根据待分段码元序列中不同的偶

数位码元确定不同的码元分段中的偶数位码元。

12.在一些实施例中,各校验码为crc(cyclic redundancy check,循环冗余校验)校验码、奇偶校验码或哈希校验码。

13.在一些实施例中,利用ldpc算法,对各校验码进行编码,以得到各编码校验码包括:将各码元分段相应的校验码组合成第二待编码码元序列;利用ldpc算法,对第二待编码码元序列进行编码,以得到第二编码码元序列;传输第一编码码元序列、各编码校验码包括:传输第一编码码元序列、第二编码码元序列,以便极化码的译码装置对第一编码码元序列进行分段译码后,利用第二编码码元序列经译码后得到的各分段校验码,对相应的码元分段中的信息码元进行校验。

14.根据本公开的另一些实施例,提供一种极化码的译码方法,包括:接收极化码的编码装置传输来的第一编码码元序列、各编码校验码;利用ldpc算法,对各编码校验码进行译码,以得到各校验码;利用极化码译码算法,对第一编码码元序列进行译码,以得到m个长度为n的码元分段,m和n为2的整数次幂;利用各校验码对相应的码元分段中的信息码元进行校验,以确定第一译码码元序列。

15.在一些实施例中,接收极化码编码装置传输来的第一编码码元序列、各编码校验码包括:利用ldpc信道接收各编码校验码。

16.在一些实施例中,利用极化码译码算法,对第一编码码元序列进行译码,以得到m个长度为n的码元分段包括:将第一编码码元序列的交织译码结果,划分为m个长度为n的交织译码分段;利用极化码译码算法,对各交织译码分段进行译码,以得到各码元分段。

17.在一些实施例中,利用各校验码对相应的码元分段中的信息码元进行校验,以确定第一译码码元序列包括:根据校验结果,从极化码译码算法的各备选译码路径中确定最终译码路径,以确定各码元分段中信息码元的译码码元;按照预设规则将各译码码元进行位置置换,以确定第一译码码元序列,位置置换与编码过程中的位置置换互为逆操作。

18.在一些实施例中,根据校验结果,从极化码译码算法的各备选译码路径中确定最终译码路径,以确定各码元分段中信息码元的译码码元包括:根据各最终译码路径确定的译码结果,确定第二译码码元序列;对第二译码码元序列中的码元进行联合判决处理,以确定第一译码码元序列,联合判决与编码过程中的分段变换处理互为逆操作。

19.在一些实施例中,各校验码为crc校验码、奇偶校验码或哈希校验码。

20.在一些实施例中,接收极化码的编码装置传输来的第一编码码元序列、各编码校验码包括:接收极化码的编码装置传输来的第一编码码元序列、第二编码码元序列,第二编码码元序列为编码装置利用ldpc算法,对各校验码组合成的待编码码元序列进行编码而生成;利用ldpc算法,对各编码校验码进行译码,以得到各校验码包括:利用ldpc算法,对第二编码码元序列进行译码,以得到各校验码。

21.根据本公开的又一些实施例,提供了一种极化码的编码装置,包括:划分单元,用于根据第一待编码码元序列,划分出m个长度为n的码元分段,m和n为2的整数次幂;生成单元,用于分别对各码元分段中的各信息码元进行校验码生成运算,以得到各码元分段相应的校验码;编码单元,用于利用ldpc算法,对各校验码进行编码,以得到各编码校验码,根据第一待编码码元序列的极化码编码结果,确定第一编码码元序列;传输单元,用于传输第一编码码元序列、各编码校验码,以便极化码的译码装置对第一编码码元序列进行分段译码

后,利用各编码校验码对相应的码元分段中的信息码元进行校验。

22.在一些实施例中,传输单元利用ldpc信道传输各编码校验码。

23.在一些实施例中,编码单元对第一待编码码元序列的极化码编码结果进行交织编码,确定第一编码码元序列。

24.在一些实施例中,编码单元按照预设规则将第一待编码码元序列进行位置置换,以得到待分段码元序列;划分单元将待分段码元序列,划分为m个长度为n的码元分段。

25.在一些实施例中,划分单元对待分段码元序列进行分段变换处理,划分出各码元分段,分段变换处理根据待分段码元序列中不同的奇数位码元确定不同的码元分段中的奇数位码元,根据待分段码元序列中不同的偶数位码元确定不同的码元分段中的偶数位码元。

26.在一些实施例中,各校验码为crc校验码、奇偶校验码或哈希校验码。

27.在一些实施例中,编码单元将各码元分段相应的校验码组合成第二待编码码元序列;利用ldpc算法,对第二待编码码元序列进行编码,以得到第二编码码元序列;传输单元传输第一编码码元序列、第二编码码元序列,以便极化码的译码装置对第一编码码元序列进行分段译码后,利用第二编码码元序列经译码后得到的各分段校验码,对相应的码元分段中的信息码元进行校验。

28.根据本公开的再一些实施例,提供一种极化码的译码装置,包括:接收单元,用于接收极化码的编码装置传输来的第一编码码元序列、各编码校验码;译码单元,用于利用ldpc算法,对各编码校验码进行译码,以得到各校验码,利用极化码译码算法,对第一编码码元序列进行译码,以得到m个长度为n的码元分段,m和n为2的整数次幂;校验单元,用于利用各校验码对相应的码元分段中的信息码元进行校验,以确定第一译码码元序列。

29.在一些实施例中,接收单元利用ldpc信道接收各编码校验码。

30.在一些实施例中,译码装置还包括划分单元,用于将第一编码码元序列的交织译码结果,划分为m个长度为n的交织译码分段。译码单元利用极化码译码算法,对各交织译码分段进行译码,以得到各码元分段。

31.在一些实施例中,译码单元根据校验结果,从极化码译码算法的各备选译码路径中确定最终译码路径,以确定各码元分段中信息码元的译码码元;按照预设规则将各译码码元进行位置置换,以确定第一译码码元序列,位置置换与编码过程中的位置置换互为逆操作。

32.在一些实施例中,译码单元根据各最终译码路径确定的译码结果,确定第二译码码元序列;对第二译码码元序列中的码元进行联合判决处理,以确定第一译码码元序列,联合判决与编码过程中的分段变换处理互为逆操作。

33.在一些实施例中,各校验码为crc校验码、奇偶校验码或哈希校验码。

34.在一些实施例中,接收单元接收极化码的编码装置传输来的第一编码码元序列、第二编码码元序列,第二编码码元序列为编码装置利用ldpc算法,对各校验码组合成的待编码码元序列进行编码而生成;译码单元利用ldpc算法,对第二编码码元序列进行译码,以得到各校验码。

35.根据本公开的再一些实施例,提供一种电子设备,包括:存储器;和耦接至存储器的处理器,处理器被配置为基于存储在存储器装置中的指令,执行上述任一个实施例中的

编码方法或者译码方法。

36.根据本公开的再一些实施例,提供一种信息传输系统,包括:信息发送端,包括用于执行上述任一个实施例中编码方法的极化码的编码器;信息接收端,包括用于执行上述任一个实施例中译码方法的极化码的译码器。

37.根据本公开的再一些实施例,提供一种非易失性计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现上述任一个实施例中的编码方法或者译码方法。

38.在上述实施例中,将待第一编码码元序列进行了分段,并利用ldpc算法生成了各分段独立的编码校验码。这样,能够辅助译码装置进行译码校验,从而提高编码和译码性能。

附图说明

39.构成说明书的一部分的附图描述了本公开的实施例,并且连同说明书一起用于解释本公开的原理。

40.参照附图,根据下面的详细描述,可以更加清楚地理解本公开:

41.图1示出本公开的极化码的编码方法的一些实施例的流程图;

42.图2示出本公开的极化码的译码方法的一些实施例的流程图;

43.图3示出本公开的极化码的编码装置的一些实施例的框图;

44.图4示出本公开的极化码的译码装置的一些实施例的框图;

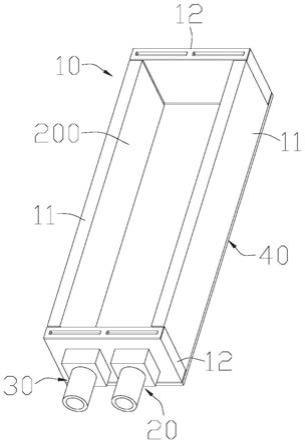

45.图5示出本公开的电子设备的一些实施例的框图;

46.图6示出本公开的电子设备的另一些实施例的框图;

47.图7示出本公开的信息传输系统的一些实施例的框图。

具体实施方式

48.现在将参照附图来详细描述本公开的各种示例性实施例。应注意到:除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对布置、数字表达式和数值不限制本公开的范围。

49.同时,应当明白,为了便于描述,附图中所示出的各个部分的尺寸并不是按照实际的比例关系绘制的。

50.以下对至少一个示例性实施例的描述实际上仅仅是说明性的,决不作为对本公开及其应用或使用的任何限制。

51.对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,技术、方法和设备应当被视为授权说明书的一部分。

52.在这里示出和讨论的所有示例中,任何具体值应被解释为仅仅是示例性的,而不是作为限制。因此,示例性实施例的其它示例可以具有不同的值。

53.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步讨论。

54.针对上述技术问题,本公开可以利用ldpc方法生成编码校验码,以便信息接收端经ldpc译码后获得的校验码对分段译码结果进行校验。根据校验结果,从多条备选路径如

scl译码方法的l条备选路径中选出正确的译码路径。

55.还可以利用超低误码率的ldpc编译码信道独立传输校验码,降低校验码的传输差错,提高校验码辅助的分段耦合-联合判决的译码性能。例如,可以通过如下的实施例实现本公开的技术方案。

56.图1示出本公开的极化码的编码方法的一些实施例的流程图。

57.如图1所示,在步骤110中,根据第一待编码码元序列,划分出m个长度为n的码元分段,m和n为2的整数次幂。

58.在一些实施例中,按照预设规则将第一待编码码元序列进行位置置换,以得到待分段码元序列;将待分段码元序列,划分为m个长度为n的码元分段。

59.例如,:按照预设规则将码元长度为n的第一待编码码元序列进行位置置换,以得到m个码元长度为n的置换码元分段与译码侧的备选分段译码结果对应,n、m和n为2的整数次幂。这样,可以根据scl译码过程中联合判决后的码元顺序,设置位置置换方法,使得位置置换后的码元顺序与联合判决后的码元顺序匹配。

60.在一些实施例中,可以对待分段码元序列进行分段变换处理,划分出各码元分段。分段变换处理根据待分段码元序列中不同的奇数位码元确定不同的码元分段中的奇数位码元,根据待分段码元序列中不同的偶数位码元确定不同的码元分段中的偶数位码元。

61.例如,在位置置换的基础上,按照分段变换公式,获取m个码元长度为n的码元分段与译码侧的联合分段译码结果对应。

62.例如,分段变换公式分别从待分段码元序列中选择多个奇数位码元进行异或运算,确定各码元分段中的奇数位码元。不同的码元分段可以选取不同的奇数位码元组合进行运算;分别从待分段码元序列中选择多个偶数位码元进行异或运算,确定各码元分段中的偶数位码元。不同的码元分段可以选取不同的偶数位码元组合进行运算。

63.在步骤120中,分别对各码元分段中的各信息码元进行校验码生成运算,以得到各码元分段相应的校验码。例如,各校验码为crc校验码、奇偶校验码或哈希校验码。

64.在一些实施例中,可以各码元分段并行生成校验码,也可以串并结合生成校验码。

65.在步骤130中,利用ldpc算法,对各校验码进行编码,以得到各编码校验码。

66.在一些实施例中,分别对每个码元分段中进行校验码生成运算以得到相对应的校验码,对m个分段校验码进行ldpc编码获得编码校验码。

67.在步骤140中,根据待分段码元序列的极化码编码结果,确定第一编码码元序列。

68.在一些实施例中,对待分段码元序列的极化码编码结果进行交织编码,确定第一编码码元序列。

69.例如,对第一待编码码元序列进行极化编码,再经交织编码后输出交织编码码字,以确定第一编码码元序列;将各编码校验码和第一编码码元序列进行合并后输出如各编码校验码在前,第一编码码元序列在后。

70.在步骤150中,传输第一编码码元序列、各编码校验码,以便极化码的译码装置对第一编码码元序列进行分段译码后,利用各编码校验码对相应的码元分段中的信息码元进行校验。

71.在一些实施例中,利用ldpc信道传输各编码校验码。这样,传输校验码的ldpc信道独立于传输信息码元编码序列的极化码信道,从而可以按照需要选择ldpc信道参数和码

型,提高编码和译码性能。

72.在一些实施例中,将所述各码元分段相应的校验码组合成第二待编码码元序列;利用ldpc算法,对第二待编码码元序列进行编码,以得到第二编码码元序列。

73.传输第一编码码元序列、第二编码码元序列,以便极化码的译码装置对第一编码码元序列进行分段译码后,利用第二编码码元序列经译码后得到的各分段校验码,对相应的码元分段中的信息码元进行校验。这样,可以提高编码和译码的效率。

74.图2示出本公开的极化码的译码方法的一些实施例的流程图。

75.如图2所示,在步骤210中,接收极化码的编码装置传输来的第一编码码元序列、各编码校验码。例如,利用ldpc信道接收各编码校验码。例如,各编码校验码是利用ldpc算法进行编码的校验码,分别对应各码元分段。

76.在步骤220中,利用ldpc算法,对各编码校验码进行译码,以得到各校验码。

77.在步骤230中,利用极化码译码算法,对第一编码码元序列进行译码,以得到m个长度为n的码元分段。m和n为2的整数次幂。

78.在一些实施例中,将第一编码码元序列的交织译码结果,划分为m个长度为n的交织译码分段;利用极化码译码算法,对各交织译码分段进行译码,以得到各码元分段。

79.例如,对接收的第一编码码元序列中的交织编码码字进行解交织后,得到译码装置的输入信号分量序列(交织译码结果);按顺序(也可以按照其他分段方式)将输入信号分量序列划分为m个等长的交织译码分段。经分段scl译码器对各交织译码分段进行独立的译码后,得到包含l条备选路径的m个备选译码结果。

80.在步骤240中,利用各校验码对相应的码元分段中的信息码元进行校验,以确定第一译码码元序列。例如,可以对各码元分段并行校验,也可以串并结合进行校验。

81.在一些实施例中,根据校验结果,从极化码译码算法的各备选译码路径中确定最终译码路径,以确定各码元分段中信息码元的译码码元;按照预设规则将各译码码元进行位置置换,以确定第一译码码元序列,译码过程中的位置置换与编码过程中的位置置换互为逆操作。

82.在一些实施例中,根据各最终译码路径确定的译码结果,确定第二译码码元序列;对第二译码码元序列中的码元进行联合判决处理,以确定第一译码码元序列。译码过程中的联合判决与编码过程中的分段变换处理互为逆操作。

83.例如,利用对应m个码元分段的校验码,对相应码元分段的备选译码结果进行校验,生成m个备选分段译码结果;对m个备选分段译码进行联合判决,输出m个联合分段译码结果;m个联合分段译码结果经过译码过程中的位置置换,输出第一译码码元序列。

84.在一些实施例中,如果任意一个备选译码结果没有通过校验,则译码失败,接收端不再对接收的极化码编码码字进行译码处理。

85.在一些实施例中,如果任意一个备选译码结果没有通过校验,则以出现概率最大的备选路径为最终译码路径。这样,可以避免出现译码失败,提高译码性能。

86.在一些实施例中,接收极化码的编码装置传输来的第一编码码元序列、第二编码码元序列。第二编码码元序列为所述编码装置利用ldpc算法,对各校验码组合成的待编码码元序列进行编码而生成。利用ldpc算法,对所述第二编码码元序列进行译码,以得到各校验码。

87.在一些实施例中,译码装置可以独立进行m个分段的sc译码,因此可以灵活采用不同的具体实现方式。

88.例如,可以用m个scl译码器并行执行scl译码,以便在最短的时间完成译码;也可以采用一个scl译码器串行地执行m个分段的scl译码,这样需要的硬件资源最少;还可以采用串并混合方式由少于m个的scl译码器执行串并混合的分组scl译码,以均衡硬件资源要求和译码时间要求。

89.串行或者分组scl译码方式的好处在于译码过程中一旦某个第一分段译码结果没有通过校验,则可放弃其余分段的译码,节省计算资源。

90.在上述实施例中,实现了分段独立的校验码辅助scl译码,提高了译码性能;用于传输校验码的ldpc信道独立于传输信息码元系列的极化码信道,可以按照需要选择ldpc信道参数和码型。

91.利用码率比极化码信道更低因而性能更好的ldpc信道传输校验码,基于ldpc具有任意构造码率灵活性的优势能相应地降低漏检率和误检率,提高极化码的译码性能。

92.图3示出本公开的极化码的编码装置的一些实施例的框图。

93.如图3所示,极化码的编码装置3包括划分单元31、生成单元32、编码单元33和传输单元34。

94.划分单元31,用于根据第一待编码码元序列,划分出m个长度为n的码元分段,m和n为2的整数次幂。

95.生成单元32,用于分别对各码元分段中的各信息码元进行校验码生成运算,以得到各码元分段相应的校验码。

96.编码单元33,用于利用ldpc算法,对各校验码进行编码,以得到各编码校验码,根据第一待编码码元序列的极化码编码结果,确定第一编码码元序列。

97.传输单元34,用于传输第一编码码元序列、各编码校验码,以便极化码的译码装置对第一编码码元序列进行分段译码后,利用各编码校验码对相应的码元分段中的信息码元进行校验。

98.在一些实施例中,传输单元34利用ldpc信道传输各编码校验码。

99.在一些实施例中,编码单元33对第一待编码码元序列的极化码编码结果进行交织编码,确定第一编码码元序列。

100.在一些实施例中,编码单元33按照预设规则将第一待编码码元序列进行位置置换,以得到待分段码元序列;划分单元31将待分段码元序列,划分为m个长度为n的码元分段。

101.在一些实施例中,划分单元31对待分段码元序列进行分段变换处理,划分出各码元分段。分段变换处理根据待分段码元序列中不同的奇数位码元确定不同的码元分段中的奇数位码元,根据待分段码元序列中不同的偶数位码元确定不同的码元分段中的偶数位码元。

102.在一些实施例中,各校验码为crc校验码、奇偶校验码或哈希校验码。

103.在一些实施例中,编码单元33将各码元分段相应的校验码组合成第二待编码码元序列;利用ldpc算法,对第二待编码码元序列进行编码,以得到第二编码码元序列;传输单元34传输第一编码码元序列、第二编码码元序列,以便极化码的译码装置对第一编码码元

序列进行分段译码后,利用第二编码码元序列经译码后得到的各分段校验码,对相应的码元分段中的信息码元进行校验。

104.图4示出本公开的极化码的译码装置的一些实施例的框图。

105.如图4所示,极化码的译码装置4包括接收单元41、译码单元42、校验单元43。

106.接收单元41,用于接收极化码的编码装置传输来的第一编码码元序列、各编码校验码。

107.译码单元42,用于利用ldpc算法,对各编码校验码进行译码,以得到各校验码,利用极化码译码算法,对第一编码码元序列进行译码,以得到m个长度为n的码元分段,m和n为2的整数次幂。

108.校验单元43,用于利用各校验码对相应的码元分段中的信息码元进行校验,以确定第一译码码元序列。

109.在一些实施例中,接收单元41利用ldpc信道接收各编码校验码。

110.在一些实施例中,译码装置4还包括划分单元44,用于将第一编码码元序列的交织译码结果,划分为m个长度为n的交织译码分段。译码单元42利用极化码译码算法,对各交织译码分段进行译码,以得到各码元分段。

111.在一些实施例中,译码单元42根据校验结果,从极化码译码算法的各备选译码路径中确定最终译码路径,以确定各码元分段中信息码元的译码码元;按照预设规则将各译码码元进行位置置换,以确定第一译码码元序列,位置置换与编码过程中的位置置换互为逆操作。

112.在一些实施例中,译码单元42根据各最终译码路径确定的译码结果,确定第二译码码元序列;对第二译码码元序列中的码元进行联合判决处理,以确定第一译码码元序列,联合判决与编码过程中的分段变换处理互为逆操作。

113.在一些实施例中,各校验码为crc校验码、奇偶校验码或哈希校验码。

114.在一些实施例中,接收单元41接收极化码的编码装置传输来的第一编码码元序列、第二编码码元序列。第二编码码元序列为编码装置利用ldpc算法,对各校验码组合成的待编码码元序列进行编码而生成。译码单元42利用ldpc算法,对第二编码码元序列进行译码,以得到各校验码。

115.图5示出本公开的电子设备的一些实施例的框图。

116.如图5所示,该实施例的电子设备5包括:存储器51以及耦接至该存储器51的处理器52,处理器52被配置为基于存储在存储器51中的指令,执行本公开中任意一个实施例中的编码方法或者译码方法。

117.其中,存储器51例如可以包括系统存储器、固定非易失性存储介质等。系统存储器例如存储有操作系统、应用程序、引导装载程序boot loader、数据库以及其他程序等。

118.图6示出本公开的电子设备的另一些实施例的框图。

119.如图6所示,该实施例的电子设备6包括:存储器610以及耦接至该存储器610的处理器620,处理器620被配置为基于存储在存储器610中的指令,执行前述任意一个实施例中的编码方法或者译码方法。

120.存储器610例如可以包括系统存储器、固定非易失性存储介质等。系统存储器例如存储有操作系统、应用程序、引导装载程序boot loader以及其他程序等。

121.电子设备6还可以包括输入输出接口630、网络接口640、存储接口650等。这些接口630、640、650以及存储器610和处理器620之间例如可以通过总线660连接。其中,输入输出接口630为显示器、鼠标、键盘、触摸屏、麦克、音箱等输入输出设备提供连接接口。网络接口640为各种联网设备提供连接接口。存储接口650为sd卡、u盘等外置存储设备提供连接接口。

122.图7示出本公开的信息传输系统的一些实施例的框图。

123.如图7所示,信息传输系统7包括:信息发送端71,包括用于执行上述任一个实施例中编码方法的极化码的编码器;信息接收端72,包括用于执行上述任一个实施例中译码方法的极化码的译码器。

124.本领域内的技术人员应当明白,本公开的实施例可提供为方法、系统、或计算机程序产品。因此,本公开可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本公开可采用在一个或多个其中包含有计算机可用程序代码的计算机可用非瞬时性存储介质包括但不限于磁盘存储器、cd-rom、光学存储器等上实施的计算机程序产品的形式。

125.至此,已经详细描述了根据本公开的极化码的编码方法、极化码的译码方法、极化码的编码装置、极化码的译码装置、信息传输系统和非易失性计算机可读存储介质。为了避免遮蔽本公开的构思,没有描述本领域所公知的一些细节。本领域技术人员根据上面的描述,完全可以明白如何实施这里公开的技术方案。

126.可能以许多方式来实现本公开的方法和系统。例如,可通过软件、硬件、固件或者软件、硬件、固件的任何组合来实现本公开的方法和系统。用于方法的步骤的上述顺序仅是为了进行说明,本公开的方法的步骤不限于以上具体描述的顺序,除非以其它方式特别说明。此外,在一些实施例中,还可将本公开实施为记录在记录介质中的程序,这些程序包括用于实现根据本公开的方法的机器可读指令。因而,本公开还覆盖存储用于执行根据本公开的方法的程序的记录介质。

127.虽然已经通过示例对本公开的一些特定实施例进行了详细说明,但是本领域的技术人员应该理解,以上示例仅是为了进行说明,而不是为了限制本公开的范围。本领域的技术人员应该理解,可在不脱离本公开的范围和精神的情况下,对以上实施例进行修改。本公开的范围由所附权利要求来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。