1.本发明涉及半导体技术领域,具体涉及一种半导体器件及其制作方法。

背景技术:

2.近些年,nand闪存是一种功耗低、质量轻和性能佳的非易失存储产品,在断电情况下仍然能保持存储的数据信息,在电子产品中得到了广泛的应用。而3d nand(三维存储器)是一种新型的闪存类型,能够在二维nand闪存的基础上,进一步提高了存储容量,降低存储成本,在三维存储器的制备中,主要是通过在衬底上形成堆叠层,堆叠层会设置若干沟道开孔,在沟道开孔中设置有的存储功能层及沟道层,然而在沟道层上的填充物在制作填充时会影响沟道层的性能。

3.因此,亟需一种半导体器件及其制作方法以解决上述技术问题。

技术实现要素:

4.本发明提供一种半导体器件及其制作方法,可以缓解目前在沟道层上的填充物在制作填充时影响沟道层的性能的技术问题。

5.本发明提供一种半导体器件的制作方法,包括:

6.提供一包括多个沟道开孔的堆叠层;

7.在所述沟道开孔内及所述堆叠层上形成存储功能层及沟道层;

8.在第一温度条件下,在所述沟道层上形成保护层;

9.其中,所述第一温度为450℃至500℃。

10.优选的,所述半导体器件的制作方法还包括:利用原子层沉积工艺,在所述保护层上形成功能调节层。

11.优选的,所述利用原子层沉积工艺,在所述保护层上形成功能调节层的步骤包括:利用原子层沉积工艺,在第二温度条件下,在所述保护层上形成功能调节层;其中,所述第二温度为550℃至700℃。

12.优选的,所述功能调节层的厚度大于所述保护层的厚度。

13.优选的,所述保护层的厚度为1nm至5nm,所述功能调节层的厚度为5nm至20nm。

14.优选的,所述保护层材料为氧化硅、氮化硅、氧化铝中任一种,所述功能调节层的材料为氧化硅、氮化硅、氧化铝、多晶硅中任一种。

15.优选的,所述半导体器件的制作方法还包括:在第三温度条件下,在所述功能调节层上形成平坦层;其中,所述第三温度大于所述第一温度,所述第三温度小于形成所述功能调节层的第二温度。

16.优选的,所述第三温度为450℃至550℃。

17.优选的,所述提供一包括多个沟道开孔的堆叠层的步骤包括:在衬底上形成堆叠材料层;在所述堆叠材料层形成多个纵截面形状为倒梯形的沟道开孔。

18.本发明还提供了一种半导体器件,所述半导体器件由任一上述的半导体器件的制

作方法制作而成。

19.本发明的有益效果为:本发明通过在沟道层上在450℃至500℃的温度下,制作形成保护层,较低的形成温度可以减少沟道层的界面氧化或缺陷,在后续制作时,保护层也可以对沟道层起到一定的保护作用,保护了半导体器件,提高了半导体器件的寿命及性能。

附图说明

20.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

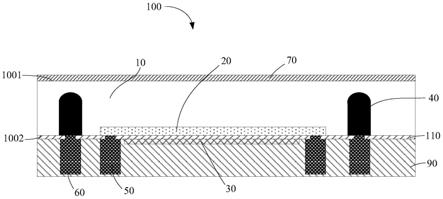

21.图1是本发明实施例提供的半导体器件的制作方法的第一种步骤流程图;

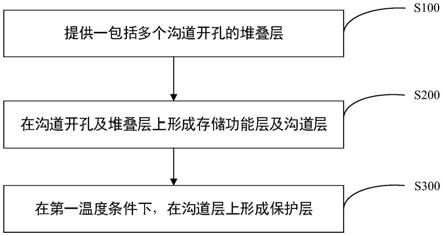

22.图2是本发明实施例提供的半导体器件的制作方法的第二种步骤流程图;

23.图3是本发明实施例提供的半导体器件的制作方法的第三种步骤流程图;

24.图4a至图4e是本发明实施例提供的半导体器件的制作方法中的第一种结构示意图;

25.图5是本发明实施例提供的半导体器件的制作方法中的第二种结构示意图。

具体实施方式

26.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。此外,应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。在本发明中,在未作相反说明的情况下,使用的方位词如“上”和“下”通常是指装置实际使用或工作状态下的上和下,具体为附图中的图面方向;而“内”和“外”则是针对装置的轮廓而言的。

27.近些年,nand闪存是一种功耗低、质量轻和性能佳的非易失存储产品,在断电情况下仍然能保持存储的数据信息,在电子产品中得到了广泛的应用。而3d nand(三维存储器)是一种新型的闪存类型,能够在二维nand闪存的基础上,进一步提高了存储容量,降低存储成本,在三维存储器的制备中,主要是通过在衬底上形成堆叠层,堆叠层会设置若干沟道开孔,在沟道开孔中设置有的存储功能层及沟道层,然而在沟道层上的填充物在制作填充时会影响沟道层的性能。

28.请参阅图1,本发明实施例提供了一种半导体器件100的制作方法,包括:

29.s100、提供一包括多个沟道开孔430的堆叠层400;

30.s200、在沟道开孔430内及堆叠层400上形成存储功能层500及沟道层600;

31.s300、在第一温度条件下,在沟道层600上形成保护层700;

32.其中,第一温度为450℃至500℃。

33.本发明通过在沟道层上450℃至500℃的温度下,制作形成保护层,较低的形成温度可以减少沟道层的界面氧化或缺陷,在后续制作时,保护层也可以对沟道层起到一定的保护作用,保护了半导体器件,提高了半导体器件的寿命及性能。

34.现结合具体实施例对本发明的技术方案进行描述。

35.本实施例中,半导体器件100的制作方法包括:

36.s100、提供一包括多个沟道开孔430的堆叠层400,具体请参阅图4a。

37.在一些实施例中,步骤s100包括:

38.s110、提供一衬底200。

39.s120、在衬底200上形成沟道终止层300。

40.沟道终止层300用于在堆叠层400上形成沟道开孔430时方便进行开孔终止,沟道终止层300的材料与沟道层600的材料为半导体材料。

41.在一些实施例中,沟道层600或/和沟道终止层300的材料可以为硅基材料;进一步地,可以为多晶硅材料,例如,包括单质多晶硅或者掺杂多晶硅;此外,沟道层600或/和沟道终止层300的材料还可以包括多晶锗硅、碳硅、锗等半导体材料中的至少一种。

42.s130、在沟道终止层300上形成堆叠材料层。

43.在一些实施例中,堆叠材料层为未形成沟道开孔430的堆叠层400,堆叠材料层包括交替层叠的层间绝缘层410与栅极层420。层间绝缘层410由绝缘材料制成,包括但不限于氧化硅、氮化硅、氮氧化硅或以上材料的组合,栅极层420由导电材料制成,包括但不限于钨、钴、铜、铝、掺杂硅、硅化物或以上材料的组合。

44.s140、在堆叠材料层形成多个沟道开孔430。

45.在一些实施例中,在堆叠材料层形成多个沟道开孔430,以形成包括多个沟道开孔430的堆叠层400。

46.在一些实施例中,步骤s140包括:

47.s141、在堆叠材料层形成多个纵截面形状为倒梯形的沟道开孔430,请参阅图5。

48.在一些实施例中,具体请参阅图5,沟道开孔430的纵截面形状为倒梯形。倒梯形的沟道开孔430有利于保护层700的形成覆盖,与沟道层600之间接触更紧密,更好地保护沟道层600,在形成功能调节层800及平坦层900时,也有利于两膜层的致密填充,减少膜层缝隙,避免相邻膜层错动或膜层褶皱,避免影响半导体器件100的性能。

49.s200、在沟道开孔430内及堆叠层400上形成存储功能层500及沟道层600,具体请参阅图4b。

50.在一些实施例中,步骤s200包括:

51.s210、在沟道开孔430内及堆叠层400上形成存储功能层500。

52.在一些实施例中,存储功能层500的形成工艺可以通过化学沉积或原子层沉积方法沉积形成。

53.在一些实施例中,步骤s210包括:

54.s211、在沟道开孔430内及堆叠层400上形成第一氧化硅层。

55.s212、在第一氧化硅层上形成氮化硅层。

56.s213、在氮化硅层上形成第二氧化硅层。

57.在一些实施例中,第一氧化硅层与第二氧化硅层均为氧化硅材料,氮化硅层为氮化硅材料,其中的氧化硅或氮化硅,是指硅氧化合物或氮硅化合物,如sixoy,sixny。

58.s220、在存储功能层500上形成沟道层600。

59.在一些实施例中,沟道层600的材料可以为硅基材料;进一步地,可以为多晶硅材料,例如,包括单质多晶硅或者掺杂多晶硅;此外,沟道层600的材料还可以包括多晶锗硅、

碳硅、锗等半导体材料中的至少一种。

60.s300、在第一温度条件下,在沟道层600上形成保护层700,具体请参阅图4c。

61.在一些实施例中,第一温度为450℃至500℃。

62.在沟道层上450℃至500℃的温度下,制作形成保护层700,较低的形成温度可以减少沟道层600的界面氧化或缺陷,在后续制作时,保护层700也可以对沟道层600起到一定的保护作用,保护了半导体器件100,提高了半导体器件100的寿命及性能。

63.在一些实施例中,步骤s300的形成工艺可以为ice(inhibition conttrol enhancement)原子层沉积或fur(furnace)炉管原子沉积,采用的气体环境可以为二叔丁氨基硅烷(btbas,别称:双(叔丁基氨基)硅烷),可以用较低的温度形成保护层700。

64.在一些实施例中,保护层700的材料为氧化硅、氮化硅、氧化铝中任一种。此处氧化硅是指硅氧化合物,如sixoy,氮化硅,是指氮硅化合物,如sixny。

65.在一些实施例中,请参阅图2,半导体器件100的制作方法还包括:

66.s400、利用原子层沉积工艺,在保护层700上形成功能调节层800,具体请参阅图4d。

67.利用原子层沉积工艺形成的功能调节层800具有更好的覆盖性,可以更好地覆盖沟道层600和保护层700,可以更好地在制作半导体器件100时调节弯曲度(bow)值,避免在制作过程中由于弯曲度值过大或者过小导致的机台宕机破片等问题。

68.可以理解的是,功能调节层800只需要满足可以整体覆盖沟道即可,具体的形成工艺不限于原子层沉积工艺。

69.由于有保护层700,功能调节层800的材料选择可以更灵活,形成温度的要求可以宽松,功能调节层800的形成可以降低对沟道层600的影响,减少沟道层600的界面氧化或缺陷,保护了半导体器件100,提高了半导体器件100的寿命及性能。

70.在一些实施例中,功能调节层800的材料为氧化硅、氮化硅、氧化铝、多晶硅中任一种。此处氧化硅是指硅氧化合物,如sixoy,氮化硅,是指氮硅化合物,如sixny。

71.在一些实施例中,步骤s400包括:

72.s410、利用原子层沉积工艺,在第二温度条件下,在保护层700上形成功能调节层800。

73.在一些实施例中,第一温度小于第二温度。

74.在一些实施例中,第二温度为550℃至700℃。

75.在一些实施例中,保护层700与功能调节层800的材料相同时,第一温度小于第二温度,保护层700的薄膜应力小于功能调节层800的薄膜应力,可以通过控制保护层700与功能调节层800的形成温度,可以调节保护层700的薄膜应力。

76.保护层700具有较小的薄膜应力,具有更强的挺性,可以更好地保护沟道层600,在后续制程可以减少对沟道层600的损坏,同时较低形成温度,可以降低在形成保护层700时减少对沟道层600的截面氧化或减少形成缺陷。

77.在一些实施例中,步骤s400的形成工艺可以为ald(atomic layer deposition)原子层沉积,采用的气体环境可以为六氯硅烷(hcd),可以在500℃至700℃温度下形成功能调节层800。

78.在一些实施例中,保护层700的厚度小于功能调节层800的厚度。

79.保护层700主要作用为降低沟道层600的氧化和缺陷,不需要很厚即可实现对沟道层600的保护,同时,较薄的保护层700还可以留给功能调节层800以较大的厚度调节空间,以在制作时,调节弯曲度值。

80.在一些实施例中,保护层700的厚度为1nm至5nm,功能调节层800的厚度为5nm至20nm。保护层700在该厚度范围即可实现对沟道层600的保护,功能调节层800在该厚度范围可以达到更好的填充覆盖率。

81.本实施例中,请参阅图3,半导体器件100的制作方法还包括:

82.s500、在第三温度条件下,在功能调节层800上形成平坦层900,请参阅图4e。

83.在一些实施例中,第三温度小于第二温度,第三温度大于第一温度。

84.平坦层900可以填充膜层空隙,防止后续工艺对沟道层600造成影响,在平坦化的同时保护半导体器件100。

85.在一些实施例中,步骤s500的形成工艺可以为ice原子层沉积或fur炉管原子沉积,采用的气体环境可以为二叔丁氨基硅烷(btbas,别称:双(叔丁基氨基)硅烷),可以用较低的温度形成平坦层900。

86.在一些实施例中,平坦层900的材料为氧化硅。此处氧化硅是指硅氧化合物,如sixoy。

87.在一些实施例中,第三温度为450℃至550℃。

88.在一些实施例中,平坦层900的厚度为10nm至20nm。

89.若对保护层700的厚度进行大范围变化,容易对沟道层600造成损伤,影响电性;平坦层900主要为了填充密实性,在制作时反应气体含有f,对电性有影响,不宜做较大改动,所以在制作时,根据不同的工艺要求,利用功能调节层800时的制作温度、制作厚度,可以调节弯曲度参数,保护了半导体器件100,保证了半导体器件100的寿命及性能。

90.本发明通过在沟道层上450℃至500℃的温度下,制作形成保护层,较低的形成温度可以减少沟道层的界面氧化或缺陷,在后续制作时,保护层也可以对沟道层起到一定的保护作用,保护了半导体器件,提高了半导体器件的寿命及性能。

91.请参阅图4e、图5,本发明实施例还提供一种半导体器件100,半导体器件100由如任一上述的半导体器件100的制作方法制作而成。

92.本发明通过在沟道层上450℃至500℃的温度下,制作形成保护层,较低的形成温度可以减少沟道层的界面氧化或缺陷,在后续制作时,保护层也可以对沟道层起到一定的保护作用,保护了半导体器件,提高了半导体器件的寿命及性能。

93.现结合具体实施例对本发明的技术方案进行描述。

94.本实施例中,具体请参阅图4e,半导体器件100包括衬底200、位于衬底200上的堆叠层400、位于堆叠层400上的存储功能层500、位于存储功能层500上的沟道层600、位于沟道层600上的保护层700及位于保护层700上的功能调节层800。

95.在一些实施例中,具体请参阅图4e,半导体器件100还包括位于衬底200及堆叠层400之间的沟道终止层300,沟道终止层300用于在堆叠层400上形成沟道开孔430时方便进行开孔终止,沟道层600的材料包括半导体材料。

96.在一些实施例中,沟道层600或/和沟道终止层300的材料可以为硅基材料;进一步地,可以为多晶硅材料,例如,包括单质多晶硅或者掺杂多晶硅;此外,沟道层600或/和沟道

终止层300的材料还可以包括多晶锗硅、碳硅、锗等半导体材料中的至少一种。

97.在一些实施例中,具体请参阅图4e,堆叠层400包括多个沟道开孔430,存储功能层500位于沟道开孔430内及覆盖堆叠层400,存储功能层500位于沟道层600与堆叠层400之间。

98.在一些实施例中,具体请参阅图4e,在形成存储功能层500及沟道层600后,需要有绝缘保护膜层进行保护,而一般的绝缘保护膜层的形成温度在600℃左右,会使沟道层600与绝缘保护膜层的界面氧化严重或产生缺陷,如果均采用低温保护膜层,则会导致半导体器件的弯曲度(bow)值上升,机台无法贴合,影响后续制程。

99.若对保护层700的厚度进行大范围变化,容易对沟道层600造成损伤,影响电性;平坦层900主要为了填充密实性,在制作时反应气体含有f,对电性有影响,不宜做较大改动,所以在制作时,根据不同的工艺要求,利用功能调节层800时的制作温度、制作厚度,可以调节弯曲度参数,保护了半导体器件100,保证了半导体器件100的寿命及性能。

100.在一些实施例中,保护层700的厚度小于功能调节层800的厚度,功能调节层800的厚度小于平坦层900的厚度。

101.保护层700主要作用为降低沟道层600的氧化和缺陷,不需要很厚即可实现对沟道层600的保护,同时,较薄的保护层700还可以留给功能调节层800以较大的厚度调节空间,以在制作时,调节弯曲度值。

102.在一些实施例中,保护层700的厚度为1nm至5nm,功能调节层800的厚度为5nm至20nm,平坦层900的厚度为10nm至20nm。

103.在一些实施例中,保护层700及功能调节层800的材料为氧化硅,存储功能层500包括第一氧化硅层、第二氧化硅层及位于第一氧化硅层与第二氧化硅层之间的氮化硅层,膜层结构容易理解,故没有作图。

104.第一氧化硅层与第二氧化硅层均为氧化硅材料,氮化硅层为氮化硅材料,其中的氧化硅或氮化硅,是指硅氧化合物或氮硅化合物,如sixoy,sixny。

105.在一些实施例中,具体请参阅图5,沟道开孔430的纵截面形状为倒梯形。倒梯形的沟道开孔430有利于保护层700的形成覆盖,与沟道层600之间接触更紧密,更好地保护沟道层600,在形成功能调节层800及平坦层900时,也有利于两膜层的致密填充,减少膜层缝隙,避免相邻膜层错动或膜层褶皱,避免影响半导体器件100的性能。

106.在一些实施例中,具体请参阅图4e,堆叠层400包括交替层叠的层间绝缘层410与栅极层420。层间绝缘层410由绝缘材料制成,包括但不限于氧化硅、氮化硅、氮氧化硅或以上材料的组合,栅极层420由导电材料制成,包括但不限于钨、钴、铜、铝、掺杂硅、硅化物或以上材料的组合。

107.在一些实施例中,沟道层600的材料可以为硅基材料;进一步地,可以为多晶硅材料,例如,包括单质多晶硅或者掺杂多晶硅;此外,沟道层600的材料还可以包括多晶锗硅、碳硅、锗等半导体材料中的至少一种。

108.在一些实施例中,沟道层600可以通过化学沉积或原子层沉积方法沉积形成。沟道层600的厚度可以为3nm至20nm。

109.本发明通过在沟道层上450℃至500℃的温度下,制作形成保护层,较低的形成温度可以减少沟道层的界面氧化或缺陷,在后续制作时,保护层也可以对沟道层起到一定的

保护作用,保护了半导体器件,提高了半导体器件的寿命及性能。

110.本发明实施例公开了一种半导体器件及其制作方法;该半导体器件的制作方法包括:提供一包括多个沟道开孔的堆叠层;在该沟道开孔内及该堆叠层上形成存储功能层及沟道层;在第一温度条件下,在该沟道层上形成保护层;该第一温度为450℃至500℃;本发明通过在沟道层上450℃至500℃的温度下,制作形成保护层,较低的形成温度可以减少沟道层的界面氧化或缺陷,在后续制作时,保护层也可以对沟道层起到一定的保护作用,保护了半导体器件,提高了半导体器件的寿命及性能。

111.以上对本发明实施例所提供的一种半导体器件及其制作方法进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。