1.本技术涉及半导体封装领域,具体涉及一种芯片封装结构、形成方法及电子设备。

背景技术:

2.随着电子芯片的集成度越来越高,芯片封装的复杂度不断提高。不同功能的芯片对封装的要求也不同,有些芯片对气密性要求较高,需要气密性封装,有些芯片要求曝光性较好,需要裸露。

3.现有技术中,对于同时要求气密性和曝光性的芯片,在进行封装时通常是在pcb(printed circuit board,印制电路板)上使用环氧树脂围堰形成特定的密闭空间,并通过玻璃盖形成特定的曝光区间,以满足芯片气密性和曝光性的要求。基板工艺实现的芯片集成,其封装体积较大、集成度较低、且环氧树脂空腔无法到达气密性需求。

技术实现要素:

4.鉴于此,本技术提供一种芯片封装结构、形成方法及电子设备,以解决现有的芯片同时要求气密性和曝光性时,基板封装的体积较大、集成度较低、且环氧树脂空腔无法到达气密性需求的问题。

5.本技术提供的一种芯片封装结构,所述芯片封装结构包括:半导体基底,所述半导体基底的第一表面上贴装有至少第一芯片和第二芯片;位于所述半导体基底第一表面上的保护结构,所述保护结构包括至少第一空间和第二空间,所述第一空间为第一凹槽,所述第二空间为一密闭空腔,所述第一凹槽的底部到开口的第一深度大于所述密闭空腔内底部到顶部的第二深度;所述第一芯片位于所述第一凹槽的底部,所述第二芯片位于所述密闭空腔的底部。

6.可选的,所述保护结构的材料与所述半导体基底的材料相同。

7.可选的,在所述第一凹槽和/或所述密闭空腔的至少部分内壁表面上形成有屏蔽层。

8.可选的,所述第一芯片为光传感芯片或气体传感芯片;所述第二芯片为以下器件中的至少一种:垂直腔面发射激光器、红外激光器和气体发射器。

9.可选的,当所述第一芯片为所述光传感芯片时,所述第一凹槽的顶部开口上具有滤波片,且所述滤波片高于所述密闭空腔的顶部,并贴装对应的镜头。

10.可选的,所述第二空间为第二凹槽;所述滤波片覆盖所述第二凹槽的顶部开口。

11.可选的,所述半导体基底的第一表面上形成有塑封层,所述塑封层至少覆盖所述保护结构的侧壁。

12.可选的,所述芯片还包括至少一第三芯片,所述半导体基底上贴装有所述第三芯片,所述第三芯片塑封在所述保护结构的外部,所述塑封层还覆盖所述第三芯片。

13.可选的,当所述第一芯片为飞行时间传感芯片、所述第二芯片为垂直腔面发射激光器时,所述第三芯片包括驱动器和图像信号处理器。

14.可选的,所述半导体基底内形成有电连接结构,所述第一芯片和第二芯片分别电连接至所述电连接结构;所述半导体基底还包括与所述第一表面相对的第二表面;所述形成方法还包括:在所述半导体基底的第二表面形成电连接触点,以将所述第一芯片和所述第二芯片的信号引出。

15.可选的,所述半导体基底以及所述保护结构均为晶圆级尺寸,所述芯片封装结构通过晶圆级封装技术封装形成。

16.本技术还提供一种芯片封装结构的形成方法,包括:提供半导体基底,所述半导体基底的第一表面上贴装有至少第一芯片和第二芯片;提供保护结构,所述保护结构内形成有至少第一凹槽和第二凹槽,所述第一凹槽的深度大于所述第二凹槽的深度;将所述保护结构的凹槽开口所在侧固定于所述半导体基底的第一表面,使得所述第一芯片位于所述第一凹槽内,所述第二芯片位于所述第二凹槽内,对应形成两个密闭的第一空间和第二空间,所述第一空间的顶部高于所述第二空间的顶部;对所述保护结构进行整面减薄,直至至少暴露出所述第一空间内部。

17.可选的,所述提供保护结构,所述保护结构内形成有至少第一凹槽和第二凹槽的步骤,包括:提供保护基底;通过控制不同的刻蚀时间或刻蚀速度刻蚀所述保护基底,在所述保护基底内形成所述第一凹槽和第二凹槽以形成所述保护结构。

18.可选的,所述将所述保护结构的凹槽开口所在侧固定于所述半导体基底的第一表面的步骤,包括:在所述保护结构的开口所在侧表面和/或所述半导体基底的第一表面的对应位置处形成键合层;通过所述键合层以实现将所述保护结构的凹槽开口所在侧表面与所述半导体基底的第一表面键合连接。

19.可选的,所述对所述保护结构进行整面减薄的方法包括:在所述半导体基底的第一表面形成塑封层,所述塑封层至少覆盖所述保护结构的侧壁;沿所述塑封层表面朝向所述半导体基底方向进行减薄,直至暴露出所述第一空间内部。

20.可选的,所述形成方法还包括:继续减薄,直至暴露出所述第二空间内部。

21.可选的,所述半导体基底以及所述保护基底均为晶圆级尺寸;通过所述的形成方法形成多个晶圆级分布的芯片封装结构后,进行切割,形成多个独立的芯片封装结构。

22.本技术还提供一种电子设备,包括所述的芯片封装结构。

23.一种芯片封装结构、形成方法及电子设备,通过第一深度和第二深度不同的第一凹槽和密闭空腔,将不同电路功能的第一芯片和第二芯片分别包围在不同深度的第一凹槽和密闭空腔内,可以实现第一芯片裸露以实现透光,同时对气密性有要求的第二芯片仍然在密闭空腔内,以满足气密性要求。

24.进一步的,由于半导体基底和保护结构材料相同,cte(热膨胀系数)匹配远优于pcb板,且密闭空腔内的气密性远大于环氧树脂空腔的气密性。

25.进一步的,在塑封后再将所述第一凹槽的顶部进行整面减薄至暴露出所述第一芯片,防止减薄时保护结构发生移动,影响气密性,且整面减薄时不受后续制程影响,比如重布线制程。

26.进一步的,当第二空间为第二凹槽时,由于第一凹槽和第二凹槽具有槽内高度差异,通过设定不同减薄截止层,可以实现两个透光需求的凹槽。

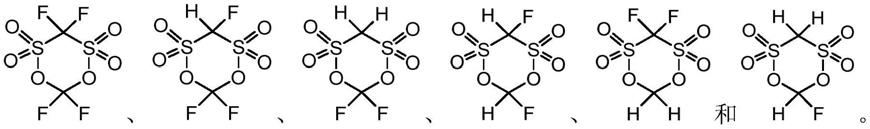

附图说明

27.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

28.图1为本技术一实施例的芯片封装结构的形成方法的流程示意图;

29.图2~图10为本技术一实施例的芯片封装结构的形成过程的结构示意图;

30.图11~图15为本技术一实施例的芯片封装结构的示意图。

具体实施方式

31.如背景技术中所述,现有技术中,在进行封装时通常是在pcb基板上,使用环氧树脂围堰形成特定的密闭空间,并通过玻璃盖形成特定的曝光区间,以满足芯片气密性和曝光性的要求。基板工艺实现的芯片集成,其封装体积较大、集成度较低、且环氧树脂空腔无法到达气密性需求。为此,发明人提出一种新的芯片封装结构的形成方法,通过半导体基底和保护结构,所述保护结构包括至少第一空间和第二空间,所述第一空间为第一凹槽,所述第二空间为一密闭空腔,所述第一凹槽的底部到开口的第一深度大于所述密闭空腔内底部到顶部的第二深度;所述第一芯片位于所述第一凹槽的底部,所述第二芯片位于所述密闭空腔的底部,可以在要求气密性和曝光性的同时,可以降低封装尺寸,提高集成度,气密性性能更好。

32.下面结合附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本技术一部分实施例,而非全部实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。在不冲突的情况下,下述各个实施例及其技术特征可以相互组合。

33.请参看图1,本技术一实施例的芯片封装结构的形成方法的流程示意图。

34.本实施例的芯片封装结构的形成方法,包括以下步骤:

35.步骤s1、提供半导体基底,所述半导体基底的第一表面上贴装有至少第一芯片和第二芯片。

36.步骤s2、提供保护结构,所述保护结构内形成有至少第一凹槽和第二凹槽,所述第一凹槽的深度大于所述第二凹槽的深度。

37.步骤s3、将所述保护结构的凹槽开口所在侧固定于所述半导体基底的第一表面,使得所述第一芯片位于所述第一凹槽内,所述第二芯片位于所述第二凹槽内,对应形成两个密闭的第一空间和第二空间,所述第一空间的顶部高于所述第二空间的顶部。

38.步骤s4、对所述保护结构进行整面减薄,直至至少暴露出所述第一空间内部。

39.本实施例的芯片封装结构的形成方法,通过第一凹槽和第二凹槽,所述第一凹槽的深度大于所述第二凹槽的深度,第一芯片位于所述第一凹槽内,所述第二芯片位于所述第二凹槽内,行整面减薄,直至至少暴露出所述第一空间内部后,可以实现第一芯片裸露以实现透光,同时对气密性有要求的第二芯片仍然在密闭空腔内,以满足气密性要求。另外,第一空间在整面减薄时不受后续制程影响,比如塑封,重布线制程。

40.另外,利用第一凹槽和第二凹槽深度不同,在满足裸露和气密性的同时,第一芯片

和第二芯片之间可以实现隔离,避免了信号干扰。在所述第一凹槽和所述第二凹槽相连处的侧壁上设置有金属层,以进一步加强隔离效果,进一步避免第一芯片和第二芯片之间的信号干扰。通过调整减薄截至层的位置可以实现第二凹槽气密性要求或透光要求。

41.在可选的一种实施方式中,通过继续降低减薄截至层将所述保护结构的顶部整面继续进行减薄并刻蚀成通孔以暴露出所述第二芯片。通过调整减薄截至层对保护结构的顶部整面进行减薄和刻蚀可以方便形成一个曝光区和一个气密性空腔,或是两个曝光区,以满足不同功能芯片的要求。

42.在可选的一种实施方式中,所述形成方法还包括:在所述半导体基底上形成塑封区域。在塑封区域内可以继续集成其他功能的电路,比如驱动电路、isp(图像信号处理)电路等。

43.在可选的一种实施方式中,当所述第一芯片为飞行时间传感芯片、所述第二芯片为垂直腔面发射激光器,所述形成方法为晶圆级形成方法时,所述形成方法还包括:在所述第一凹槽的顶部开口处盖上滤波片并贴装对应的镜头;对晶圆进行切片以形成封装后的芯片晶粒。

44.通过晶圆级封装,实现tof芯片包括sensor(传感芯片),driver(驱动器),vcsel,isp等等的槽内高度集成;对比传统cob(chips on board,板上芯片封装)模组封装,可以大大降低封装尺寸,同时槽内高度集成后,可以有效减少布线层和走线长度,从而提高信号传递速度。另外,利用多保护结构,可以实现塑封过程中芯片感光保护,避免传统塑封造成的信号阻隔;同时密闭空腔又是独立结构,实现芯片的隔离,减小各芯片间信号的干扰。不同槽内高度硅槽的套用即可实现感光也可以实现气密封装需求。另外,晶圆级封装槽内高度集成,可以有效降低单颗加工周期和成本;同时封装晶圆级测试效率也比较高;也减少基板投入,可用于快速系统级验证,投入成本更低。

45.以下,结合具体的结构示意图,对芯片封装结构的形成过程进行具体描述。

46.请参考图2至图10,为本发明一实施例的芯片封装过程的结构示意图,进一步对上述步骤中的具体实施方式进行描述。

47.请参考图2,提供半导体基底100,半导体基底100的第一表面上贴装有第一芯片1和第二芯片2,所述半导体基底100内形成有电连接结构101,所述第一芯片1和第二芯片2分别电连接至所述电连接结构101。具体的,所述第一芯片1为光传感芯片或气体传感芯片;光传感芯片包括以下传感芯片中的至少一种:飞行时间(tof)传感芯片、红外传感芯片和激光测距传感芯片。所述第二芯片2为以下器件中的至少一种:垂直腔面发射(vcsel)激光器、红外激光器和气体发射器。第二芯片2为与第一芯片1之间具有配合工作的芯片,例如当第一芯片1为tof芯片时,所述第二芯片2为光发射芯片,包括vcsel激光器。本实施例中第一芯片1为tof传感芯片,第二芯片2为vcsel激光器。在其他可选的实施例中,第一芯片1和第二芯片2的数量可以为其他数值。

48.所述半导体基底100的材料可以为单晶硅衬底、锗硅衬底、碳化硅衬底等。

49.请参考图3,提供保护结构200,所述保护结构200内形成有至少第一凹槽210和第二凹槽220,所述第一凹槽210的深度,即槽内高度h1大于所述第二凹槽220的深度,即槽内高度h2。第一凹槽210和第二凹槽220的顶部与底部保持在同一水平。具体的,提供保护基底;通过控制不同的刻蚀时间或刻蚀速度刻蚀所述保护基底,在所述保护基底内形成所述

第一凹槽210和第二凹槽220以形成保护结构200。

50.所述保护结构200的材料与所述半导体基底100的材料相同。具体的,所述保护结构200的材料可以为单晶硅、锗硅、碳化硅等,且与所述半导体基底100的材料相同。本实施例中,所述保护结构200为硅槽,所述半导体基底100为硅基底。由于保护结构200的材料与所述半导体基底100的材料是一致的,cte(热膨胀系数)匹配远优于pcb板,且密闭空腔内的气密性远大于环氧树脂空腔的气密性。

51.请参考图4,在所述保护结构200的开口所在侧表面和所述半导体基底100的第一表面的对应位置处形成键合层201;通过所述键合层201以实现将所述保护结构200的凹槽开口所在侧表面与所述半导体基底100的第一表面键合连接,所述第一芯片1位于所述第一凹槽内210,所述第二芯片2位于所述第二凹槽内220。

52.所述键合层201为金属层,所述键合层201的材料可以为cu、w、al、au、ag等金属材料中的至少一种。可以采用化学气相沉积工艺、蒸镀工艺或者溅射等工艺中的至少一种方法,形成所述键合层201。

53.在可选的其他实施方式中,所述键合层201也可以为玻璃胶,将所述保护结构200的开口与所述半导体基底100的第一表面进行压合。比如,通过在所述保护结构200的开口处与对应的所述半导体基底100的第一表面处涂敷玻璃胶或金属;通过所述玻璃胶或所述金属以实现将所述保护结构200的开口与所述半导体基底100的第一表面的固定连接。

54.具体的,对保护结构200施加足够的压力以对保护结构200和半导体基底100进行压合,经过压合后一方面实现保护结构200和半导体基底100固定连接,另一方面保证了第一凹槽和第二凹槽与半导体基底100形成第一空间和第二空间的气密性。

55.在其他可选的实施方式中,也可以使用其他方式实现两者的固定连接。

56.请参考图5,将图4中的所述半导体基底100的第一表面形成塑封层300,所述塑封层300覆盖所述保护结构2,在其他实施方式中,塑封层300至少覆盖所述保护结构2的侧壁。所述半导体基底100还包括与所述第一表面相对的第二表面;在所述半导体基底100的第二表面形成电连接触点400以将所述第一芯片1和所述第二芯片2的信号引出。本实施例中电连接触点400为焊盘。

57.请参考图6,沿所述塑封层300表面朝向所述半导体基底100方向进行减薄,直至暴露出所述第一空间内部。具体的,通过调整减薄截至层将所述保护结构200的顶部整面进行减薄并在第一空间顶部刻蚀成第一通孔以暴露出所述第一芯片1。可见,第一芯片1对应的tof传感芯片通过第一通孔实现裸露透光,第二芯片2对应的vcsel激光器通过第二凹槽220形成的密闭空腔满足气密性要求,同时可以实现tof传感芯片和vcsel激光器的相互隔离。

58.可见,利用多保护结构,可以实现塑封过程中芯片感光保护,避免传统塑封造成的信号阻隔;同时密闭空腔又是独立结构,实现芯片的隔离,减小各芯片间信号的干扰。不同高度硅槽的套用即可实现感光也可以实现气密封装需求。

59.请参考图7,通过继续降低减薄截至层将所述保护结构200的顶部整面继续进行减薄并刻蚀成第二通孔以暴露出所述第二空间内部的所述第二芯片2。

60.在可选的一种实施方式中,当所述第一芯片为光传感芯片、所述第二芯片为垂直腔面发射激光器,所述形成方法还包括:所述第一凹槽210的顶部开口上具有滤波片,且所述滤波片高于所述密闭空腔的顶部,并贴装对应的镜头。

61.在可选的一种实施方式中,所述半导体基底以及所述保护基底均为晶圆级尺寸;通过所述的形成方法形成多个晶圆级分布的芯片封装结构后,进行切割,形成多个独立的芯片封装结构,对晶圆进行切片以形成封装后的芯片晶粒。

62.通过晶圆级封装,实现tof芯片包括sensor,driver,vcsel,isp等等的高度集成;对比传统cob模组封装,可以大大降低封装尺寸,同时高度集成后,可以有效减少布线层和走线长度,从而提高信号传递速度。晶圆级封装高度集成,可以有效降低单颗加工周期和成本;同时封装晶圆级测试效率也比较高;也减少基板投入,可用于快速系统级验证,投入成本更低。

63.在可选的另一种实施方式中,请参考图8,所述芯片还包括至少一第三芯片3,所述半导体基底100上贴装有所述第三芯片3。第三芯片3包括驱动器,isp等集成电路芯片。

64.请参考图9,所述形成方法还包括:将所述第三芯片3塑封在所述塑封层300内,且第三芯片3在保护结构200的外部。在后续的保护结构减薄过程中依然保持第三芯片3塑封在所述塑封层300内。通过将第三芯片塑封在所述塑封层内,进一步提高了芯片的集成度。

65.请参考图10,所述形成方法还包括:在所述第一凹槽和/或所述密闭空腔的至少部分内壁表面上形成有屏蔽层。具体的,在所述第一凹槽210和所述第二凹槽220相连处的侧壁上形成金属层,比如在第一凹槽210的内侧壁上通过溅射工艺形成第一金属层610,在第二凹槽220的内侧壁上通过溅射工艺形成第二金属层620。通过该金属层可以增强隔离,进一步避免信号干扰。

66.请参考图11,本技术一实施例的芯片封装结构的结构示意图。

67.本技术的芯片封装结构中,所述芯片包括第一芯片1和第二芯片2,所述第一芯片1为以下传感芯片中的至少一种:飞行时间传感芯片、红外传感芯片和激光测距传感芯片;所述第二芯片2为以下器件中的至少一种:垂直腔面发射激光器、红外激光器和气体发射器。

68.所述芯片封装结构包括:

69.半导体基底100,所述半导体基底100的第一表面贴装有线路互联的所述第一芯片1和所述第二芯片2;

70.位于所述半导体基底100上的保护结构200,所述保护结构200塑封在塑封层300内,所述保护结构200包括相邻连接的第一空间和第二空间,即第一凹槽210和第二凹槽220,所述第一凹槽210的槽内高度大于所述第二凹槽220的槽内高度。

71.所述第一凹槽210的顶部具有第一通孔,所述第一通孔上具有滤波片500,且所述第一芯片1位于所述第一凹槽210的底部,所述第二凹槽220为密闭的空腔,且所述第二芯片2位于所述空腔内。

72.所述保护结构200的开口所在侧表面和所述半导体基底100的第一表面的对应位置处有键合层201;通过所述键合层201以实现将所述保护结构200的凹槽开口所在侧表面与所述半导体基底100的第一表面键合连接。

73.所述半导体基底100的第一表面有塑封层300,所述塑封层300覆盖所述保护结构2。所述半导体基底100还包括与所述第一表面相对的第二表面;在所述半导体基底100的第二表面形成有电连接触点400以将所述第一芯片1和所述第二芯片2的信号引出。

74.本实施例的芯片的封装结构,半导体基底为硅基底,保护结构为硅结构,通过槽内高度不同的相邻连接的第一凹槽和第二凹槽,即不同槽内高度的硅槽或硅盖,将不同电路

功能的第一芯片和第二芯片分别包围在不同的硅槽内,再在塑封后将所述第一凹槽的顶部减薄至暴露出所述第一芯片,由于第一凹槽和第二凹槽具有槽内高度差异,设定不同减薄截止层,可以实现第一芯片裸露以实现透光,同时对气密性有要求的第二芯片仍然在密闭空腔内,以满足气密性要求。另外,第一凹槽和第二凹槽,或者第一硅盖或第二硅盖槽内高度是不同的,在整面减薄时不受后续制程影响,比如塑封,重布线制程。另外,由于半导体基底和硅槽材料是一致的,cte(热膨胀系数)匹配远优于pcb板,且密闭空腔内的气密性远大于环氧树脂空腔的气密性。另外,利用第一凹槽和第二凹槽深度不同,在满足裸露和气密性的同时,第一芯片和第二芯片之间可以实现隔离,避免了信号干扰。

75.在可选的一种实施方式中,请参见图12,在所述第一凹槽210和所述第二凹槽220相连处的侧壁上设置有金属层,金属层包括第一金属层610和第二金属层620,第一金属层610设置在第一凹槽210的内侧壁,第二金属层620设置在第二凹槽220的内侧壁。通过在述第一凹槽210和所述第二凹槽220相连处的侧壁上设置金属层,可以提高述第一凹槽210和所述第二凹槽220的隔离性能,进一步防止信号干扰。

76.在可选的一种实施方式中,请参见图13,所述第二凹槽220的顶部具有第二通孔;所述滤波片500覆盖所述第二通孔。第一凹槽210和所述第二凹槽220相连处的侧壁上设置有第一金属层610和第二金属层620,该第一金属层610和第二金属层620可以省略。进一步的通过第二通孔可以满足两种不同的芯片曝光的要求,又实现两种芯片的信号隔离。

77.在可选的一种实施方式中,请参见图14或图15,所述芯片还包括至少一第三芯片3,所述半导体基底100上贴装有所述第三芯片3,所述第三芯片3塑封在所述保护结构200的外部。可选的,当所述第一芯片为飞行时间传感芯片、所述第二芯片为垂直腔面发射激光器时,所述第三芯片包括驱动器和图像信号处理器。在其他可选的实施例中,第一芯片、第二芯片和第三芯片可以根据需要设置为其他功能芯片。

78.通过增加第三芯片,可以实现多种类型的芯片封装,提高芯片的集成度。

79.在可选的一种实施方式中,所述半导体基底以及所述保护结构均为晶圆级尺寸,所述芯片封装结构通过晶圆级封装技术封装形成。

80.通过晶圆级封装,实现tof芯片包括传感器,驱动器,vcsel,isp等等的高度集成;对比传统cob模组封装,可以大大降低封装尺寸,同时高度集成后,可以有效减少布线层和走线长度,从而提高信号传递速度。晶圆级封装高度集成,可以有效降低单颗加工周期和成本;同时封装晶圆级测试效率也比较高;也减少基板投入,可用于快速系统级验证,投入成本更低。

81.本发明的实施例还提供一种电子设备,例如tof相机、距离检测装置等。该电子设备采用上述的芯片的封装结构,降低了电子设备的体积,提高了电子设备的集成度。

82.以上所述仅为本技术的实施例,并非因此限制本技术的专利范围,凡是利用本技术说明书及附图内容所作的等效结构或等效流程变换,例如各实施例之间技术特征的相互结合,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。