1.本发明涉及半导体技术领域,特别是涉及一种氮化镓(gan)高电子迁移率晶体管(high-electron mobility transistor,hemt)及其制作方法。

背景技术:

2.高电子迁移率晶体管常被应用于高频的高功率放大器元件,其具有高击穿电压、高饱和电子移动速度及高温操作的特性。

3.典型的hemt中,在半导体异质接面处产生二维电子气(2deg)。2deg代表了非常薄的导电层,所述导电层具有高度可移动且高度集中的电荷载子,所述电荷载子可在所述导电层的两个维度上自由移动,但被垂直于所述导电层的第三维度上的移动所限制。氮化镓高电子迁移率晶体管(gan hemt)由于其高击穿场、高电子迁移率和高电子速度,因此特别适合应用在高速和高电压电路。

4.对于p型gan增强模式(enhancement mode或e-mode)高电子迁移率晶体管而言,为了达到常关型(normally-off(临界电压vth》0))元件,必须降低氮化铝镓阻障层中的铝的所占比例,然而,降低氮化铝镓阻障层中的铝的比例却会面临导通电组(ron)升高的问题。

技术实现要素:

5.本发明的主要目的在于提供一种改良的高电子迁移率晶体管,能克服现有技术中的缺点和不足。

6.本发明一方面提供了一种高电子迁移率晶体管,包含一基底;一通道层,设于所述基底上;一氮化铝镓层,设于所述通道层上;以及一p型氮化镓栅,设于所述氮化铝镓层上,其中,所述氮化铝镓层包含一第一区域和一第二区域,又其中,所述第一区域的组成不同于所述第二区域的组成。

7.根据本发明实施例,所述第一区域位于所述p型氮化镓栅下方。

8.根据本发明实施例,所述第一区域具有由al

x

ga

1-x

n表示的分子式,其中x=0.05~0.25,而所述第二区域具有由alyga

1-y

n表示的分子式,其中y=0.15~1.0,其中,y》x。

9.根据本发明实施例,所述通道层包含氮化镓或氮化铝镓。

10.根据本发明实施例,所述高电子迁移率晶体管另包含一缓冲层,位于所述通道层和所述基底之间。

11.根据本发明实施例,所述高电子迁移率晶体管另包含一源极区域和一漏极区域,位于所述氮化铝镓层上;以及一源极电极和一漏极电极,分别位于所述源极区域和所述漏极区域内的所述氮化铝镓层上。

12.根据本发明实施例,所述高电子迁移率晶体管另包含一钝化层,位于所述氮化铝镓层上,其中所述钝化层覆盖所述第二区域。

13.根据本发明实施例,所述氮化铝镓层的厚度介于8至30纳米。

14.根据本发明实施例,所述p型氮化镓栅的厚度介于50至100纳米。

15.本发明另一方面提供一种高电子迁移率晶体管的制作方法,包含:提供一基底;于所述基底上形成一通道层;于所述通道层上形成一氮化铝镓层;于所述氮化铝镓层上形成一p型氮化镓栅;以及对所述氮化铝镓层进行一热处理,从而在所述氮化铝镓层中形成一第一区域和一第二区域,其中所述第一区域具有与所述第二区域不同的组成。

16.根据本发明实施例,所述热处理在一快速热处理腔室、一快速热退火腔室、一炉管或一金属有机化学气相沉积腔室中进行的。

17.根据本发明实施例,所述热处理包括以下条件:在h2、n2、nh3或其组合的气体环境中,以摄氏500到1200度之间的温度,加热时间约1分钟到2个小时。

18.根据本发明实施例,在对所述氮化铝镓层进行所述热处理后,所述方法另包含:于所述第二区域上形成一钝化层。

19.根据本发明实施例,所述第一区域位于所述p型氮化镓栅下方。

20.根据本发明实施例,所述第一区域具有由al

x

ga

1-x

n表示的分子式,其中x=0.05~0.25,而所述第二区域具有由alyga

1-y

n表示的分子式,其中y=0.15~1.0,其中,y》x。

21.根据本发明实施例,所述通道层包含氮化镓或氮化铝镓。

22.根据本发明实施例,所述方法另包含:在形成所述通道层之前,在所述基底上形成一缓冲层。

附图说明

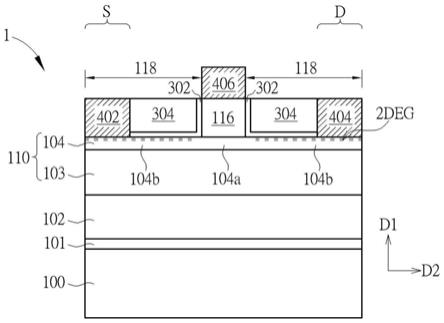

23.图1至图5为依据本发明实施例所绘示的一种高电子迁移率晶体管的制作方法的剖面示意图。

24.图6a至图6d例示完成热处理之后,氮化铝镓层在第二区域中由alyga

1-y

n表示的分子式中的y值,对氮化铝镓层在第二区域的深度的作图。

25.图7例示完成热处理之后,氮化铝镓层在第一区域中由al

x

ga

1-x

n表示的分子式中的x值,对氮化铝镓层在第一区域的深度的作图。

26.图8为在对氮化铝镓层进行热处理前,氮化铝镓层在第一区域和第二区域中由al

x

ga

1-x

n表示的分子式中的x值,对氮化铝镓层的深度的作图。

27.主要元件符号说明

[0028]1ꢀꢀ

高电子迁移率晶体管

[0029]

100

ꢀꢀ

基底

[0030]

101

ꢀꢀ

成核层

[0031]

102

ꢀꢀ

缓冲层

[0032]

103

ꢀꢀ

通道层

[0033]

104

ꢀꢀ

氮化铝镓层

[0034]

104a

ꢀꢀ

第一区域

[0035]

104b

ꢀꢀ

第二区域

[0036]

106

ꢀꢀ

p型氮化镓层

[0037]

110

ꢀꢀ

主动层

[0038]

116

ꢀꢀ

p型氮化镓栅

[0039]

118

ꢀꢀ

读取区域

[0040]

200

ꢀꢀ

热处理

[0041]

302

ꢀꢀ

钝化层

[0042]

304

ꢀꢀ

介电层

[0043]

402

ꢀꢀ

源极电极

[0044]

404

ꢀꢀ

漏极电极

[0045]

406

ꢀꢀ

栅极电极

[0046]

2deg

ꢀꢀ

二维电子云

[0047]sꢀꢀ

源极区域

[0048]dꢀꢀ

漏极区域

[0049]

d1

ꢀꢀ

第一方向

[0050]

d2

ꢀꢀ

第二方向

具体实施方式

[0051]

在下文中,将参照附图说明细节,该些附图中的内容亦构成说明书细节描述的一部分,并且以可实行该实施例之特例描述方式来绘示。下文实施例已描述足够的细节以使该领域的一般技术人士得以具以实施。

[0052]

当然,也可采行其他的实施例,或是在不悖离文中所述实施例的前提下作出任何结构性、逻辑性、及电性上的改变。因此,下文的细节描述不应被视为是限制,反之,其中所包含的实施例将由随附的权利要求来加以界定。

[0053]

请参阅图1至图5,其为依据本发明实施例所绘示的一种高电子迁移率晶体管的制作方法的剖面示意图。如图1所示,高电子迁移率晶体管1在一第一方向d1上依序包含一基底100、一缓冲层(buffer layer)102,设于基底100上、一主动层(active layer)110设于缓冲层102上,以及一p型氮化镓(p-gan)层106,设于主动层110上。根据本发明一实施例,主动层110可以包含一通道层(channel layer)103,例如,氮化镓(gan)层或氮化铝镓(algan),介于缓冲层102和p型氮化镓层106之间。根据本发明一实施例,主动层110可以包含一氮化铝镓层104,设于通道层103上,并且介于通道层103和p型氮化镓层106之间。

[0054]

根据本发明实施例,氮化铝镓层104的厚度约介于8至30纳米,但不限于此。根据本发明实施例,p型氮化镓层106的厚度约介于50至100纳米,例如,较佳为80纳米,但不限于此。

[0055]

根据本发明一实施例,缓冲层102、主动层110,以及p型氮化镓层106可以利用金属有机化学气相沉积(metal organic chemical vapor deposition,mocvd)或分子束外延(molecular beam epitaxy,mbe)等方法在第一方向d1上依序形成在基底100上。

[0056]

根据本发明一实施例,例如,缓冲层102可以包含氮化镓,但不限于此。根据本发明其它实施例,缓冲层102可以包含氮化铝镓、氮化铝、氮化铝/氮化镓超晶格(aln/gan superlattice)或梯度氮化铝镓(graded algan),但不限于此。根据本发明一实施例,例如,在基底100和缓冲层102之间,可选择形成一成核层(nucleation layer)101,例如,氮化铝,但不限于此。

[0057]

根据本发明一实施例,例如,缓冲层102可以是单层或多层结构。例如,基底100可以是一导电基底。例如,基底100可以是一硅基底,但不限于此。根据本发明一实施例,在氮

化铝镓层104与通道层103界面处,会在第二方向d2上形成二维电子云2deg。

[0058]

如图2所示,进行一光刻制作工艺及一蚀刻制作工艺,将p型氮化镓层106图案化,形成一p型氮化镓栅116,设于氮化铝镓层104上。根据本发明一实施例,在p型氮化镓栅116旁边则形成读取区域(access region)118。根据本发明一实施例,此时在读取区域118内的氮化铝镓层104是被显露出来的。根据其他实施例,上述p型氮化镓栅116可以是p型氮化铝铟镓栅。

[0059]

如图3所示,对氮化铝镓层104进行一热处理200,从而在氮化铝镓层104中形成一第一区域104a和一第二区域104b,其中第一区域104a与第二区域104b互不重叠。根据本发明实施例,第一区域104a位于p型氮化镓栅116下方。根据本发明实施例,第一区域104a位于p型氮化镓栅116正下方。

[0060]

根据本发明实施例,氮化铝镓层104中的第一区域104a与第二区域104b为不同比例的氮化铝镓所组成,这是因为经由上述热处理200,部分的镓原子会从氮化铝镓层104中第二区域104b逸散,而氮化铝镓层104中的镓原子在第一区域104a内因为p型氮化镓栅116阻挡的关系则不会逸散,因此相对地降低了第二区域104b的氮化铝镓层104中镓的比例,且相对提升了所述第二区域104b的氮化铝镓的铝的比例,第一区域104a的材料为al

x

ga

1-x

n,第二区域104b的材料为alyga

1-y

n,故y》x,这样的好处是可以降低ron,而可以维持vth。

[0061]

根据本发明实施例,上述热处理200可以在一快速热处理(rapid thermal process)腔室、一快速热退火(rapid thermal anneal)腔室、一炉管(furnace)或一金属有机化学气相沉积(mocvd)腔室中进行的。根据本发明实施例,例如,上述热处理200包括以下条件:在h2、n2、nh3或其组合的气体环境中,以摄氏500到1200度之间的温度,加热时间约1分钟到2小时。

[0062]

根据本发明实施例,例如,第一区域104a具有由al

x

ga

1-x

n表示的分子式,其中x=0.05~0.25,而第二区域104b具有由alyga

1-y

n表示的分子式,其中y=0.15~1.0。根据本发明实施例,其中y》x。

[0063]

例如,第一区域104a的分子式以al

x

ga

1-x

n表示,其中x=0.05~0.1,而第二区域104b的分子式以alyga

1-y

n表示,其中0.1《y≤1.0。

[0064]

例如,第一区域104a的分子式以al

x

ga

1-x

n表示,其中x=0.1~0.15,而第二区域104b的分子式以alyga

1-y

n表示,其中0.15《y≤1.0。

[0065]

例如,第一区域104a的分子式以al

x

ga

1-x

n表示,其中x=0.15~0.2,而第二区域104b的分子式以alyga

1-y

n表示,其中0.2《y≤1.0。

[0066]

例如,第一区域104a的分子式以al

x

ga

1-x

n表示,其中x=0.2~0.25,而第二区域104b的分子式以alyga

1-y

n表示,其中0.25《y≤1.0。

[0067]

请参阅图6a至6d和图7,其中图6a至图6d例示完成上述热处理200之后,氮化铝镓层104在第二区域104b中由alyga

1-y

n表示的分子式中的y值(例如y=0.25~1.0),对氮化铝镓层104在第二区域104b的深度的作图,其中,所述深度是从所述氮化铝镓层104的上表面开始量测而最深至氮化铝镓层104的全部厚度(约8~30nm)。图7例示完成上述热处理200之后,氮化铝镓层104在第一区域104a中由al

x

ga

1-x

n表示的分子式中的x值(例如x=0.1~0.25)对氮化铝镓层104在第一区域104a的深度的作图。

[0068]

如图6a至图6d所示,根据本发明实施例,在对氮化铝镓层104进行热处理200后,氮

化铝镓层104在第二区域104b中由alyga

1-y

n表示的分子式中的y值至少随部分深度增加而非线性降低。在图6a至图6d中,系透过不同的热处理条件(例如,不同加热时间),使得在第二区域104b中由alyga

1-y

n表示的分子式中的y值有不同的梯度变化。例如,在图6a中,以例如摄氏1000度进行约3分钟的热处理后,可以使氮化铝镓层104在第二区域104b中alyga

1-y

n的y值会在2nm深度于第一方向d1往表面内快速增加。例如,在图6b中,以例如摄氏900度进行约30分钟的热处理后,从第二区域104b的底面往第一方向d1使氮化铝镓层104在第二区域104b中alyga

1-y

n的y值会较图6a缓慢的增加。例如,在图6c中,以例如摄氏800度进行约10分钟的热处理后,氮化铝镓层104在第二区域104b中alyga

1-y

n的y值会在约4nm深度开始往第一方向d1缓慢的增加。例如,在图6d中,以例如摄氏800度进行约20分钟的热处理后,氮化铝镓层104在第二区域104b中alyga

1-y

n的y值会从第二区域104b的底面开始往第一方向d1缓慢的增加。根据本发明一实施例,例如,进行热处理200后,氮化铝镓层104在第一区域104a内以分子式al

x

ga

1-x

n表示,其中x=0.05~0.15,而在第二区域104b以alyga

1-y

n表示,其中y=0.16~1.0。

[0069]

根据本发明另一实施例,例如,进行热处理200后,氮化铝镓层104在第一区域104a内以分子式al

x

ga

1-x

n表示,其中x=0.05~0.1,而在第二区域104b以alyga

1-y

n表示,其中y=0.2~0.5。

[0070]

根据本发明又另一实施例,例如,进行热处理200后,氮化铝镓层104在第一区域104a内以分子式al

x

ga

1-x

n表示,其中x=0.1~0.2,而在第二区域104b以alyga

1-y

n表示,其中y=0.25~1.0。

[0071]

相较之下,如图7所示,在对氮化铝镓层104进行热处理200后,氮化铝镓层104在第一区域104a中由al

x

ga

1-x

n表示的分子式中的x值基本上维持固定,而未有明显变化。请同时参阅图8,其为在对氮化铝镓层104进行热处理200前,氮化铝镓层104在第一区域104a和第二区域104b中由al

x

ga

1-x

n表示的分子式中的x值,对氮化铝镓层104的深度的作图。如图8所示,进行热处理200前,第一区域104a和第二区域104b有相同的组成,也就是以al

x

ga

1-x

n表示的分子式。从图7和图8可看出在进行热处理200前,氮化铝镓层104在第一区域104a中组成基本上是相同的。

[0072]

如图4所示,根据本发明实施例,在对氮化铝镓层104进行热处理200后,接着,在第二区域104b上形成一钝化层302。钝化层302可以设于氮化铝镓层104上,还可以延伸至p型氮化镓栅116上。例如,钝化层302可以包含氮化硅或氧化铝等,但不限于此。例如,钝化层302的厚度约为2000埃左右,但不限于此。然后,可以于钝化层302上形成一介电层304,例如,硅氧层。后续,可以利用一平坦化制作工艺,去除部分的介电层304和钝化层302,显露出p型氮化镓栅116的上表面。

[0073]

根据本发明实施例,如图5所示,高电子迁移率晶体管1另包含一源极区域s和一漏极区域d,位于氮化铝镓层104上。接着,分别于源极区域s和漏极区域d内的氮化铝镓层104上形成一源极电极402和一漏极电极404,再于p型氮化镓栅116上形成一栅极电极406。

[0074]

本发明的主要优点在于:在形成p型氮化镓栅116之后,且在形成钝化层302之前,透过进行热处理200,在氮化铝镓层104中形成一第一区域104a和一第二区域104b,其中第一区域104a具有与第二区域104b不同的组成,使得高电子迁移率晶体管1能够具有维持vth和降低ron的优异性能。

[0075]

以上所述仅为本发明的较佳实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。