1.本发明涉及一种控制装置以及控制方法。

背景技术:

2.在生产现场所使用的机械或设备典型而言由可编程逻辑控制器(programmable logic controller;以下称为plc)等控制装置进行控制。典型而言,用户使用信息处理装置来制作由控制装置所执行的控制程序。将此种由用户自由设计、制作的程序也称为用户程序。

3.plc包含中央处理装置(中央处理器,central processing unit;以下也称为cpu)及输入输出(input/output,i/o)单元等功能单元。i/o单元进行自外部的开关或传感器的信号输入、以及向外部的继电器或致动器的信号输出。关于功能单元,有时使用现场可编程门阵列(field-programmable gate array,fpga)等可编程电路来实现。

4.可编程电路具有用户可独自构建电路的优点。另一方面,可编程电路具有下述缺点,即:有可能产生设于可编程电路的内部且保存配置数据(configuration data)的配置随机存取存储器(configuration random access memory,configram)(以下也称为cram)的信息因辐射线等而变更的、软错误(soft error)。特别在利用静态随机存取存储器(static random access memory,sram)作为cram的情况下,容易产生软错误。

5.cram中,构成功能单元的使用区域、与不构成功能单元的未使用区域混合存在,软错误有可能在使用区域及未使用区域的任一个产生。在使用区域中产生软错误的情况下,有可能控制装置的控制产生不良状况,相对于此,在未使用区域中产生软错误的情况下,控制装置的控制产生不良状况的可能性低。因此,专利文献1中公开了下述控制装置,即:基于映射信息来判定产生软错误的位置,在产生软错误的位置包含于功能部的未使用区域的情况下,继续运转而可防止不需要的运转停止。

6.现有技术文献

7.专利文献

8.专利文献1:日本公开专利公报《日本专利特开2018-128820号公报》

技术实现要素:

9.发明所要解决的问题

10.但是,所述那样的现有技术中,若一旦产生软错误,则每当fpga部周期性地进行错误检测时,向处理器部发送打断通知。因此,处理器部需要每次中断通常的处理而进行软错误的分析。此时,由于以几毫秒(ms)~几十毫秒一次等高频率产生打断处理,因而有处理器部的控制周期产生波动,难以进行高精度的控制等问题。

11.本发明的一实施例的目的在于,在控制装置中降低与软错误的处理有关的、运算处理部的负荷。

12.解决问题的技术手段

13.为了解决所述问题,本发明的一方面的控制装置包括:运算处理部,可执行用户程序;可编程电路部,连接于所述运算处理部,构成功能部;以及异常通知部,所述可编程电路部包括:保存部,保存所述功能部的配置数据;异常检测部,检测所述保存部的软错误;以及异常记录部,记录所述异常检测部所检测到的所述软错误的信息,所述异常通知部判定在所述异常记录部是否记录有新的所述软错误的信息,在判定为记录有新的所述软错误的信息的情况下,向所述运算处理部通知所述新的软错误的产生。

14.本发明的一方面的控制装置的控制方法为包括下述部分的控制装置的控制方法:运算处理部,可执行用户程序;以及可编程电路部,连接于所述运算处理部,构成功能部,且所述控制装置的控制方法包括:异常检测步骤,检测保存部的软错误,所述保存部保存所述功能部的配置数据;异常记录步骤,记录所述异常检测步骤中检测到的所述软错误的信息;以及异常通知步骤,判定是否在所述异常记录步骤中记录有新的所述软错误的信息,在判定为记录有新的所述软错误的信息的情况下,向所述运算处理部通知所述新的软错误的产生。

15.发明的效果

16.根据本发明的一实施例,可在控制装置中降低与软错误的处理有关的、运算处理部的负荷。

附图说明

17.图1为表示本发明的实施方式1的控制装置的硬件结构的一例的框图。

18.图2为表示图1的fpga部及处理器部的结构例的框图。

19.图3为表示图1的控制装置的控制方法的各步骤的时机的图。

20.图4为表示图1的控制装置的控制方法的流程图。

21.图5为表示本发明的实施方式2的控制装置中的、fpga部及处理器部的结构例的框图。

具体实施方式

22.以下,基于附图对本发明的一方面的实施方式(以下也表述为“本实施方式”)进行说明。

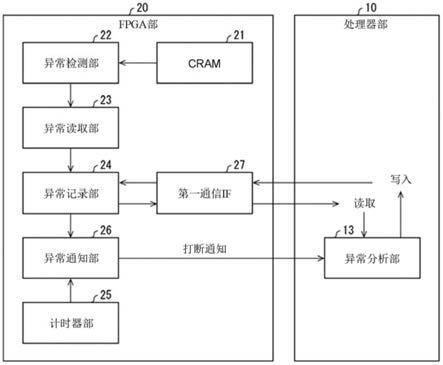

23.〔实施方式1〕

24.§

1适用例

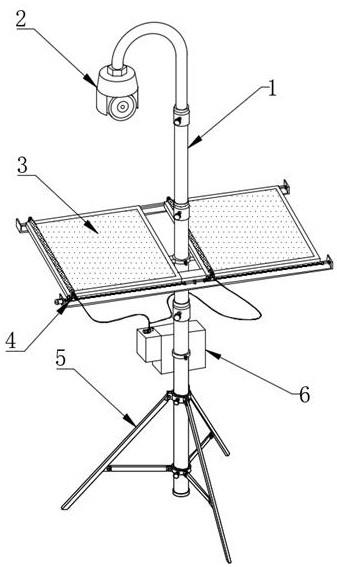

25.图1为表示实施方式1的控制装置100的硬件结构的一例的框图。首先,使用图1对适用本发明的场景的一例进行说明。控制装置100包括处理器部(运算处理部)10及fpga部(可编程电路部)20。处理器部10通过执行用户程序,从而主要进行与控制对象的控制及动作相关的处理。fpga部20构成功能单元(功能部),对从处理器部10输入的数字值执行特定的处理。

26.图2为表示图1的fpga部20及处理器部10的结构例的框图。处理器部10包括异常分析部13。fpga部20包括cram(保存部)21、异常检测部22、异常记录部24及异常通知部26。cram21保存功能部的配置数据。异常检测部22检测cram21的软错误。异常记录部24记录异常检测部22所检测到的软错误的信息。异常通知部26判定是否在异常记录部24记录有新的

软错误的信息,在判定为记录有新的软错误的信息的情况下,向处理器部10打断通知新的软错误的产生。

27.根据本实施方式,异常通知部26在判定为未在异常记录部24记录有新的软错误的信息的情况下,可不向处理器部10进行打断通知而结束处理。因此,可降低对处理器部10的异常通知的频率,降低与软错误的处理有关的、处理器部10的负荷。

28.§

2结构例

29.如图1所示,作为一例,实施方式1的控制装置100是使用plc(programmable logic controller)而安装。控制装置100通过执行预先保存的程序(系统程序及用户程序等)从而算出指令值。控制装置100将指令值给予经由i/o(input/output)单元30所连接的控制对象(例如马达驱动器等)。而且,控制装置100从所述控制对象获取状态值。即,控制装置100通过反馈控制对象的状态值,从而可动态生成适当的指令值,根据状况适当进行控制对象的控制。

30.控制装置100包括处理器部10、fpga部20、只读存储器(read only memory,rom)11、ram12及i/o单元30。控制装置100内的各零件由总线连接。总线的示例可举出:平行总线、以及内部集成电路(inter-integrated circuiti2c)及串行外设接口(serial peripheral interface,spi)等串行总线。处理器部10进行顺序处理,fpga部20进行并列处理。

31.处理器部10包含cpu,通过执行保存于rom11及ram12的程序,从而主要进行与控制对象的控制及动作相关的处理。fpga部20构成功能单元,对从处理器部10输入的数字值执行特定的处理。rom11保存对控制装置100进行控制的程序、及程序的动作所需要的数据等。ram12作为处理器部10的工作区发挥功能。i/o单元30提供与控制对象之间的接口。输入输出机器200为如触摸屏那样对用户提示信息并受理来自用户的操作输入的装置。

32.fpga部20为了构成执行特定处理的功能单元,需要进行向器件内写入配置数据的配置。一般而言,在刚投入电源后对fpga部20进行配置,获得可实现所需的电路动作的功能单元。

33.但是,fpga部20有可能产生保存有配置数据的cram的信息因辐射线等而变更的、软错误。因此,fpga部20为了检测cram的软错误而进行错误检测。以下,对fpga部20的软错误检测进行详细说明。

34.如图2所示,处理器部10包括异常分析部13。fpga部20包括cram21、异常检测部22、异常读取部23、异常记录部24、计时器部25、异常通知部26及第一通信接口(以下称为通信if)27。

35.fpga部20在启动时,读出保存于fpga部20的外部的rom(例如rom11)的、配置数据,并保存于fpga部20的内部的cram21。保存有配置数据的cram21用作用户电路。此处,cram21例如为sram(static random access memory)。

36.异常检测部22例如使用循环冗余校验(cyclic redundancy check,crc)码来进行cram21的软错误的检测。具体而言,异常检测部22根据保存于cram21的数据的值来计算crc值,并进行将此计算出的crc值、与保存于cram21的crc值进行比较的crc校验。若所计算出的crc值与所保存的crc值不一致,则异常检测部22检测到cram21的软错误。异常检测部22对fpga部20所含的多个帧依次进行crc校验,若所有帧的crc校验完成,则再次从最初的帧

开始循环进行crc校验。

37.此外,异常检测部22也可并非以fpga部20所含的所有帧为一个单位进行crc校验,而是分为预定的块,并对所述块分别进行crc校验。例如,异常检测部22也可将fpga部20分为构成功能单元a的块到构成功能单元d的块此四个块,对各个块分别进行crc校验。

38.异常读取部23读取异常检测部22所检测到的软错误的信息,并写入异常记录部24。异常记录部24记录异常检测部22所检测到的软错误的信息。软错误的信息例如包含软错误的位置(错误地址)的信息及软错误的种类的信息。软错误的种类例如可举出单比特错误及邻接双比特错误。异常记录部24包含一个以上的日志寄存器(log register)及状态寄存器(status register)作为寄存器。

39.异常记录部24将最初检测到的软错误的信息记录于第一日志寄存器。另外,针对第二次以后检测到的软错误,若所检测到的软错误的信息与记录于第一日志寄存器的软错误的信息相同则不记录,仅在不同的情况下,将所述软错误的信息记录于第二日志寄存器。同样地,针对此后检测到的软错误,若所检测到的软错误的信息与记录于第一日志寄存器或第二日志寄存器的软错误的信息相同则不记录,仅在不同的情况下,将所述软错误的信息记录于第三日志寄存器。

40.本实施方式中,设有第一日志寄存器~第三日志寄存器此合计三个日志寄存器,但日志寄存器的个数不限定于此,也可设有两个以下或四个以上的日志寄存器。此外,本实施方式中,在异常检测部22检测到第四个软错误的情况下,异常记录部24也可在输入输出机器200显示催促用户进行重启的警告。cram21为易失性存储器,因而若重启控制装置100,则cram21的软错误被除去。

41.而且,异常记录部24可将第一日志寄存器、第二日志寄存器及第三日志寄存器中记录的各软错误的状态及所检测到的软错误的检测个数记录于状态寄存器。此外,本说明书中,将第一日志寄存器、第二日志寄存器及第三日志寄存器中记录的软错误的状态分别称为第一状态、第二状态及第三状态。第一状态、第二状态及第三状态在初始状态下,设定为“未分析”。

42.计时器部25每当经过规定时间,向异常通知部26通知打断生成进程的开始。异常通知部26在接到来自计时器部25的通知时,判定是否在异常记录部24记录有新的软错误的信息。异常通知部26可通过来自计时器部25的通知,定期进行所述判定处理。另外,异常通知部26在判定为记录有新的软错误的信息的情况下,向处理器部10的异常分析部13打断通知新的软错误的产生。

43.第一通信if27为fpga部20中的异常记录部24与处理器部10的异常分析部13之间的通信if。

44.处理器部10包括异常分析部13。异常分析部13在从异常通知部26通知了新的软错误的产生时,对异常记录部24中记录的软错误的信息进行分析,将此软错误为分析完毕写入异常记录部24。异常分析部13例如分析产生软错误的位置是包含于保存有用于构成功能单元的配置数据的使用区域,还是包含于未保存有所述配置数据的未使用区域。而且,异常分析部13也可在软错误的位置包含于使用区域的情况下,分析是否为使用区域中的软错误应对完毕电路部分。关于软错误应对完毕电路的示例,可举出冗余电路。

45.§

3动作例

46.图3为表示控制装置100的控制方法的各步骤的时机的图。纵轴表示时刻。图3的示例中,表示cram21在时刻t1与时刻t2之间产生软错误的情况。如图3所示,首先在时刻t1,计时器部25对异常通知部26通知打断生成进程的开始。接到来自计时器部25的通知的异常通知部26从异常记录部24读取软错误的信息。在此时机,并未检测到新的软错误,因而异常通知部26直接结束处理。

47.另外,设cram21在时刻t1与时刻t2之间产生软错误。异常检测部22每隔一定期间检测软错误。异常读取部23读取异常检测部22所检测到的软错误的信息,并写入异常记录部24。异常记录部24将异常检测部22所检测到的软错误的信息记录于空的日志寄存器。异常记录部24将软错误的检测个数(记录于日志寄存器的软错误的个数)写入状态寄存器。

48.在从时刻t1经过规定时间的时刻t2,计时器部25对异常通知部26通知打断生成进程的开始。接到来自计时器部25的通知的异常通知部26从异常记录部24读取软错误的信息。在此时机,检测到新的软错误,因而异常通知部26向异常分析部13进行需要打断处理的打断通知。

49.接到来自异常通知部26的打断通知的异常分析部13进行打断处理。异常分析部13经由第一通信if27,从异常记录部24读取状态寄存器及日志寄存器的信息。异常分析部13分析与“未分析”的状态对应的、新的软错误的信息。

50.异常分析部13分析软错误的位置是包含于保存有功能单元的配置数据的使用区域,还是包含于未保存有功能单元的配置数据的未使用区域。异常分析部13获得“使用区域”或“未使用区域”作为软错误的位置的分析结果。

51.异常分析部13经由第一通信if27,将“使用区域”或“未使用区域”作为经分析的软错误的状态写入异常记录部24的状态寄存器。状态为“使用区域”或“未使用区域”表示对应的软错误分析完毕。而且,异常分析部13根据分析结果,使由fpga部20运行的功能单元的动作继续或停止。

52.接下来,在从时刻t2经过规定时间的时刻t3,计时器部25对异常通知部26通知打断生成进程的开始。接到来自计时器部25的通知的异常通知部26从异常记录部24读取软错误的信息。在此时机,未检测到新的软错误,因而异常通知部26直接结束处理。

53.图4为表示控制装置100的控制方法的流程图。如图4所示,若从计时器部25通知打断生成进程的开始,则异常通知部26从异常记录部24读取软错误的信息(软错误的检测个数以及第一状态、第二状态及第三状态)(步骤s1)。

54.接下来,异常通知部26判定异常记录部24的第一状态是否为未分析(步骤s2)。在第一状态为未分析的情况下(步骤s2中为是(yes)),进入步骤s21,异常通知部26判定为软错误的分析个数为0。

55.在第一状态并非未分析的情况下(步骤s2中为否(no)),进入步骤s3,异常通知部26判定异常记录部24的第二状态是否为未分析。在第二状态为未分析的情况下(步骤s3中为是(yes)),进入步骤s31,异常通知部26判定为软错误的分析个数为1。

56.在第二状态并非未分析的情况下(步骤s3中为否(no)),进入步骤s4,异常通知部26判定异常记录部24的第三状态是否为未分析。在第三状态为未分析的情况下(步骤s4中为是(yes)),进入步骤s41,异常通知部26判定为软错误的分析个数为2。

57.在第三状态并非未分析的情况下(步骤s4中为否(no)),进入步骤s5,异常通知部

26判定为软错误的分析个数为3。步骤s21、s31、s41或s5结束后,进入步骤s6,异常通知部26判定软错误的分析个数是否与软错误的检测个数不同。

58.在软错误的检测个数与软错误的分析个数不同的情况下(步骤s6中为是(yes)),异常通知部26判定为新的软错误的信息记录于异常记录部24的日志寄存器。接下来,异常通知部26向异常分析部13进行需要打断处理的打断通知(步骤s7)。步骤s7之后,处理结束。在步骤s6中为否(no)的情况下,异常通知部26不对处理器部10的异常分析部13进行打断通知,处理结束。

59.[作用、效果]

[0060]

如以上那样,根据所述结构,异常通知部26在判定为在异常记录部24记录有新的软错误的信息的情况下,向处理器部10通知新的软错误的产生。因此,可降低对处理器部10的异常通知的频率,可降低与软错误的处理有关的、处理器部10的负荷。

[0061]

而且,异常分析部13对异常记录部24中记录的软错误的信息进行分析,将分析结果写入异常记录部24。因此,异常通知部26能可靠地判定是否在异常记录部24记录有新的软错误的信息。

[0062]

而且,异常分析部13分析产生软错误的位置是包含于保存有功能部的配置数据的使用区域,还是包含于未保存有配置数据的未使用区域。因此,在产生软错误的位置包含于功能部的未使用区域的情况下,可继续运转,因而可防止不需要的运转停止。

[0063]

而且,处理器部10进行顺序处理,fpga部20进行并列处理。因此,可进行并列处理的fpga部20进行软错误的检测及软错误的信息的记录,因而因这些处理而妨碍其他处理进行的可能性低。

[0064]

另一方面,处理器部10进行顺序处理,若被通知产生软错误,则需要中断其他处理。但是,异常通知部26在判定为在异常记录部24记录有新的软错误的信息的情况下,向处理器部10通知新的软错误的発生,因而向运算处理部通知软错误的产生的频率低。因此,即便在处理器部10进行顺序处理的情况下,也可降低中断其他处理的频率。

[0065]

而且,异常通知部26接收来自计时器部25的通知,定期进行下述处理,即:判定是否在异常记录部24记录有新的软错误的信息。因此,异常通知部26可不从异常检测部22接收通知而进行是否记录有新的软错误的信息的、判定处理。因此,例如可使用现有的fpga,不变更异常检测部22的处理而实现控制装置100。

[0066]

而且,fpga部20包括异常通知部26,因而无需为了设置异常通知部26而设置专用集成电路(application specific integrated circuit,asic)等其他芯片。因此,可使控制装置100的结构简单。

[0067]

〔实施方式2〕

[0068]

以下对本发明的另一实施方式进行说明。此外,为了方便说明,对与所述实施方式中说明的构件具有相同功能的构件标注相同符号,不重复进行其说明。

[0069]

图5为表示实施方式2的控制装置100中的、fpga部20及处理器部10的结构例的框图。实施方式2在下述方面与实施方式1不同,即:控制装置100还包括asic部40,asic部40包括计时器部45及异常通知部46。

[0070]

具体而言,fpga部20包括cram21、异常检测部22、异常读取部23、异常记录部24、第一通信if27及第二通信if28。第二通信if28为fpga部20的、与asic部40的通信if。

[0071]

asic部40包括计时器部45、异常通知部46及第三通信if47。asic部40的计时器部45及异常通知部46分别具有与实施方式1中说明的fpga部20的计时器部25及异常通知部26相同的功能。第三通信if47为asic部40的、与fpga部20的通信if。

[0072]

这样,计时器部45及异常通知部46也可形成为与包含cram21的fpga部20不同的电路。

[0073]

§

4变形例

[0074]

以上,对本发明的实施方式进行了详细说明,但到此为止的说明在所有方面仅为本发明的例示。当然可不偏离本发明的范围而进行各种改良或变形。例如,可进行以下那样的变更。

[0075]

实施方式2中,异常通知部46设于asic部40,但也可设于与fpga部20不同的fpga部,或者也可设于与处理器部10不同的处理器部。

[0076]

此外,异常分析部13也可经由第一通信if27,向异常记录部24的状态寄存器写入分析完毕的软错误的个数(状态并非“未分析”的软错误的个数)。异常通知部26也可从状态寄存器读取分析完毕的软错误的个数。

[0077]

此外,异常记录部24也可不在状态寄存器中记录软错误的检测个数。异常通知部26也可根据记录有软错误的日志寄存器的个数来确定软错误的检测个数。

[0078]

〔总结〕

[0079]

本发明的一方面的控制装置包括:运算处理部,可执行用户程序;可编程电路部,连接于所述运算处理部,构成功能部;以及异常通知部,所述可编程电路部包括:保存部,保存所述功能部的配置数据;异常检测部,检测所述保存部的软错误;以及异常记录部,记录所述异常检测部所检测到的所述软错误的信息,所述异常通知部判定是否在所述异常记录部记录有新的所述软错误的信息,在判定为记录有新的所述软错误的信息的情况下,向所述运算处理部通知所述新的软错误的产生。

[0080]

根据所述结构,异常通知部在判定为在异常记录部记录有新的软错误的信息的情况下,向运算处理部通知新的软错误的产生,因而可降低对运算处理部的异常通知的频率。因此,可降低与软错误的处理有关的、运算处理部的负荷。

[0081]

所述一方面的控制装置中,所述运算处理部也可包括:异常分析部,在从所述异常通知部通知了所述新的软错误的产生时,对所述异常记录部中所记录的所述软错误的信息进行分析,将所述软错误为分析完毕写入所述异常记录部。根据所述结构,异常通知部能可靠地判定是否在异常记录部记录有新的软错误的信息。

[0082]

所述一方面的控制装置中,所述异常分析部也可分析产生所述软错误的位置是包含于保存有所述功能部的所述配置数据的使用区域,还是包含于未保存有所述配置数据的未使用区域。根据所述结构,在产生软错误的位置包含于功能部的未使用区域的情况下,可继续运转,因而可防止不需要的运转停止。

[0083]

所述一方面的控制装置中,也可为所述运算处理部进行顺序处理,所述可编程电路部进行并列处理。根据所述结构,可进行并列处理的可编程电路部进行软错误的检测及软错误的信息的记录,因而因这些处理而妨碍其他处理进行的可能性低。

[0084]

另一方面,运算处理部进行顺序处理,因而若被通知产生软错误,则需要中断其他处理。但是,异常通知部在判定为在异常记录部记录有新的软错误的信息的情况下,向运算

处理部通知新的软错误的产生,因而向运算处理部通知软错误的产生的频率低。因此,即便在运算处理部进行顺序处理的情况下,也可降低中断其他处理的频率。

[0085]

所述一方面的控制装置中,所述异常通知部也可定期进行下述处理,即:判定是否在所述异常记录部记录有新的所述软错误的信息。根据所述结构,异常通知部可不从异常检测部接收通知而进行是否记录有新的软错误的信息的、判定处理。因此,例如可使用市售的fpga,不变更异常检测部的处理而实现所述控制装置。

[0086]

所述一方面的控制装置中,所述可编程电路部也可包括所述异常通知部。根据所述结构,无需为了设置异常通知部而设置asic(application specific integrated circuit)等其他芯片,因而可使控制装置的结构简单。

[0087]

本发明的一方面的控制装置的控制方法为包括下述部分的控制装置的控制方法:运算处理部,可执行用户程序;以及可编程电路部,连接于所述运算处理部,构成功能部,且所述控制装置的控制方法包括:异常检测步骤,检测保存部的软错误,所述保存部保存所述功能部的配置数据;异常记录步骤,记录所述异常检测步骤中检测到的所述软错误的信息;以及异常通知步骤,判定是否在所述异常记录步骤中记录有新的所述软错误的信息,在判定为记录有新的所述软错误的信息的情况下,向所述运算处理部通知所述新的软错误的产生。

[0088]

本发明的各实施例的控制装置也可由计算机来实现,此时,通过使计算机作为所述控制装置所包括的各部(软件元件)运行从而由计算机来实现所述控制装置的、控制装置的控制程序以及记录有所述控制程序的计算机可读取的记录介质也包含于本发明的范畴。

[0089]

本发明不限定于所述各实施方式,可在权利要求所示的范围内进行各种变更,将不同实施方式中分别公开的技术手段适当组合而得的实施方式也包含于本发明的技术范围。

[0090]

符号的说明

[0091]

10:处理器部(运算处理部)

[0092]

13:异常分析部

[0093]

20:fpga部(可编程电路部)

[0094]

21:cram(保存部)

[0095]

22:异常检测部

[0096]

23:异常读取部

[0097]

24:异常记录部

[0098]

25、45:计时器部

[0099]

26、46:异常通知部

[0100]

100:控制装置

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。