用于dp接口的控制电路装置及其自适应均衡方法

技术领域

1.本发明涉及集成电路技术领域,具体为一种用于dp接口的控制电路装置及用于该dp接口接收通道的自适应均衡方法。

背景技术:

2.dp(displayport)接口是一种依赖数据包化数据传输技术的显示通信端口,可用于内部显示连接,也可用于外部的显示连接。目前比较主流的用于dp接口接收通道的均衡技术主要有3大类:(1)只包含ctle(continuous time linear equalization,连续线性时间均衡)电路,并且通常通过模拟的方式检测数据跳变沿的陡峭程度来调节ctle参数;(2)包含ctle电路与dfe电路(decision feedback equalization,判决反馈均衡器)两种电路,但是只有dfe电路能进行自适应调节,ctle电路的控制参数需要手动配置;(3)包含ctle电路与dfe电路,并且依赖于特殊训练序列进行自适应调节,ctle参数需要通过数据跳变沿的符号统计判断决定调节方向或者通过统计ctle电路输出信号的眼宽来决定调节方向。

3.如果只有ctle电路,只能均衡高、低频分量的幅度,而不能消除信道传输带来的isi(inter symbol interference,码间干扰),isi的存在可能会引起数据比较器(data slicer)的判决错误,从而增加误码率,此外,通过模拟方式检测数据跳变沿的陡峭程度来调节ctle参数的方法不可靠,后期使用时可配置性差;很多设计中虽然使用ctle电路和dfe电路的组合电路结构,但是由于只有dfe电路部分能够通过自适应的方式进行调节,ctle电路仍要依赖于外部手动配置经验值,这不是完全意义上的自适应均衡,并且针对不同应用场合,ctle电路需要配置的参数可能差别较大,因此在应用上不够灵活。

技术实现要素:

4.针对现有技术中存在的缺陷,本发明提出了一种用于dp接口的控制电路装置及其自适应均衡方法,其不依赖于特殊的训练序列,可提高应用灵活性,可实现高、低频分量的均衡,可消除isi,降低接收信号的误码率。

5.为实现上述目的,本发明采用如下技术方案:

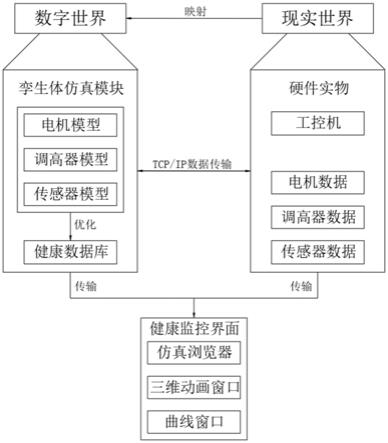

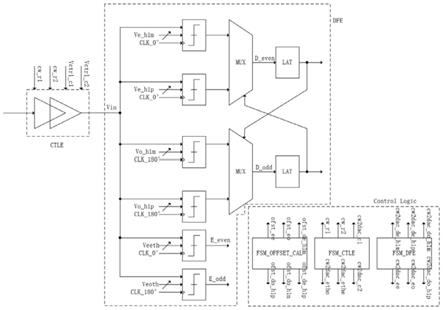

6.一种用于dp接口的控制电路装置,包括ctle电路、cdr电路,所述ctle电路的输出连接所述cdr电路的输入,其特征在于,所述ctle电路包括二级级联,所述ctle电路的控制端连接控制单元fsm_ctle、两路dac电路,所述控制单元fsm_ctle用于输出电阻值控制字,两路所述dac电路用于输出电容值控制字;所述dfe电路采用半数据率预处理结构,所述dfe电路的输入分别连接所述ctle电路的输出、时钟控制信号、门限电压控制信号,所述半数据率预处理结构包括比较器:干扰比较器、数据比较器,所述半数据率预处理指:根据采样时钟的相位将所述dac电路划分为奇数路、偶数路,根据不同的数据分割判决门限将所述奇数路、偶数路分为四路,四路所述比较器分别同时工作,在最终输出时根据前1bit的值来选择相应比较器实现均衡调节。

7.其进一步特征在于,

8.通过所述控制单元fsm_ctle输出的电阻值、两路dac电路输出的电容值对所述ctle电路的每级进行控制,所述控制单元fsm_ctle输出的电阻值控制字包括电阻cw_r1、电阻cw_r2,两路所述dac电路输出的电容值控制字分别为vctrl_c1、vctrl_c2;

9.所述奇数路包括数据奇数路、干扰奇数路,所述偶数路包括数据偶数路、干扰偶数路,所述dfe电路包括四路数据比较器(data slicer)、两路干扰比较器(error slicer),四路所述数据比较器包括第一数据比较器~第四数据比较器,所述数据偶数路包括第一数据比较器、第二数据比较器,所述数据奇数路包括第三数据比较器、第四数据比较器,所述干扰偶数路包括第五干扰比较器,所述干扰奇数路包括第六干扰比较器;

10.所述dfe电路还包括两个数据选择器:第一数据选择器、第二数据选择器,所述第一数据选择器的输入连接所述数据偶数路的输出,所述第一数据选择器、第二数据选择器的选择端、输出分别通过第一锁存器、第二锁存器交叉连接;

11.所述不同门限电压信号包括门限电压ve_h1m、ve_h1p、vo_h1m、vo_h1p、veeth和veoth,所述时钟控制信号包括时钟信号clk_0

°

、互补的时钟信号clk_180

°

;

12.所述第一比较器~第六比较器的输入端分别连接门限电压ve_h1m、ve_h1p、vo_h1m、vo_h1p、veeth和veoth,所述第一比较器、第二比较器、第五比较器的输入端还分别连接时钟信号clk_0

°

,所述第三比较器、第四比较器、第六比较器的输入端还分别连接时钟信号clk_180

°

。

13.一种自适应均衡方法,该方法基于上述控制电路装置实现,用于对dp接口接收通道进行自适应均衡调节,其特征在于,所述自适应均衡方法包括:s1、偏置校准阶段;

14.s2、ctle电路自适应调节阶段;

15.s3、cdr电路锁定阶段;

16.s4、dfe电路自适应调节阶段;

17.其中,ctle电路自适应调节阶段要主动控制cdr电路,使时钟处于未锁定状态,ctle电路自适应调节完成后,等待cdr电路锁定后进行dfe电路自适应调节。

18.其进一步特征在于,

19.进一步的,所述偏置校准阶段对所述比较器引入的偏置进行校准,所述偏置校准包括:s11、所述ctie电路向所述dfe电路输入差分信号对vin_p和vin_n,差分电压信号vin=vin_p-vin_n,将vin_p和vin_n短接并通过钳位电路钳位至一个固定电压值;s12、依次对所述四路数据路径进行校准;

20.进一步的,寻找相应比较器偏置值的步骤包括:a1、调节相应比较器的门限电压,使所述门限电压由预先设定最小值逐步提升,即dac电路的输入端控制码从7’h00开始增加;a2、门限电压调节过程中,对每个门限电压相应的时间段t内的比较器的输出数据进行统计;a3、调节相应比较器门限电压的过程中,所述比较器输出数据中包含0时,对应的所述门限电压值即为该比较器所在路径的偏置值;

21.进一步的,基于所述寻找相应比较器偏置值的步骤,进行若干轮校准,相应比较器的最终偏置值为若干轮校准偏置值的平均值;

22.进一步的,采用四个比较器分时顺序进行偏置值校准的方法,并且对偶数路的其中一个比较器进行校准时,要控制奇数路中的两个比较器的门限电压同时为最大值或最小值,同理,对奇数路的其中一个比较器进行校准时,要控制偶数路两个比较器的门限电压同

时为最大值或最小值;

23.进一步的,所述ctle电路自适应调节时,从时域波形中寻找欠均衡和过均衡的特征,当低频分量的幅度明显大于高频分量幅度时,信号状态判断为欠均衡,当低频分量幅度和高频分量幅度一致,但数据跳变沿有过冲信号时,信号状态判断为过均衡;

24.进一步的,所述ctle电路自适应调节开始后,通过调节期望值幅度控制干扰比较器的门限电压,初始状态下,外部配置信号最大摆幅的期望值,电容值控制字取最小值,使ctle电路的输出信号处于欠均衡状态;

25.进一步的,信号状态判断为过均衡的具体步骤包括:第一步,调节电阻值控制字,实现直流增益控制,具体包括:调节所述ctle电路输出信号中低频分量的幅度,当干扰比较器的输出数据中包含“1”时,表明低频分量的幅度达到期望值;

26.第二步,逐步增加电容值控制字,使高频增益提高,具体包括:调节所述ctle电路输出信号中高频分量的幅度,当所述干扰比较器的输出数据中“1”的数量多于第一步中“1”数量时,表明此刻的信号状态为过均衡。

27.进一步的,所述dfe电路自适应调节时,根据码型选择相应的门限电压,所述dfe电路的控制单元的状态机对应四种码型,分时对四种码型进行统计,计算得到当前比特对应的模拟电压期望值,四种码型00、01、10、11对应求得四组当前比特对应的模拟电压期望值dlev00、dlev01、dlev01、dlev11,这四组期望值对应于状态机四个状态时分时输出控制干扰比较器的门限电压;

28.进一步的,所述ctle电路中两级级联的电容值通过电压来控制,该控制电压来自两路所述dac电路,所述dfe电路中所有比较器的门限电压来自各自对应的所述dac电路,所述dac电路的控制字均来自数字控制单元,所述dac电路要求输入的控制字为格雷码。

29.采用本发明上述结构及方法可以达到如下有益效果:用于dp接口的控制电路装置中包括ctle电路、cdr电路,ctle电路的控制端连接控制单元fsm_ctle、两路dac电路,通过控制单元fsm_ctle输出的电阻值控制字、两路dac电路输出的电容值控制字对ctle电路的每级进行控制,其控制不依赖于外部手动配置经验值,也不依赖于特殊的训练序列,提高了应用灵活性。

30.基于ctle电路、dfe电路的半数据率预处理结构对dp接口的接收通道进行自适应均衡调节,调节过程中,通过对时域波形幅值的估计实现ctle电路电阻值和电容值的调节,从而实现高频分量、低频分量的均衡,dfe电路为半速率预处理结构,有利于消除isi,最终使接收信号的误码率小于10~12。

附图说明

31.图1为本发明用于dp接口的控制电路装置的电路结构框图;

32.图2为本发明自适应均衡方法的流程图;

33.图3为本发明自适应均衡方法中偏置校准阶段的偏置校准算法流程图;

34.图4为本发明自适应均衡方法中接收信号经过ctle电路之前欠均衡以及经过ctle电路之后过均衡的时域波形;

35.图5为本发明自适应均衡方法中ctle电路自适应调节过程中的状态控制图。

calibration)阶段,该过程在芯片上电后完成基本的控制寄存器配置后进行;2)ctle电路自适应(ctle adaptation)阶段,为确保该过程有效的进行,要求dp接口上的串行数据不能为单频信号;3)等待时钟相位锁定阶段,ctle adaptation完成后,监测cdr电路的锁定信号(即lock指示信号)变为1;4)dfe电路自适应(dfe adaptation)阶段,分时对状态机的四种码型00、01、10、11的码型进行统计,d-1为前1bit数据,d0为当前bit数,计算得到1阶post cursor干扰(即采样点后面的干扰)的系数 h1和-h1。上述四个阶段的总状态机控制流程的如图2所示。

40.偏置校准(offset calibration)阶段,由于dfe电路中六路slicer存在较大的电压偏置(dc offset),所以为了提高电路性能,需要对比较器(slicer)电路进行偏置校准(offset calibration),偏置校准的具体步骤包括:图2中总状态机的状态state=s_offset_cal时,表示当前顶层自适应过程的状态进入offset校准阶段,error slicer和data slicer的校准同时进行,实际电路中ctle电路发送至dfe电路的信号为一对差分对vin_p和vin_n(图1中vin=vin_p-vin_n),此阶段将vin_p和vin_n短接并通过钳位电路钳位至一个固定电压,理想情况下此时各slicer输入的差分值应该为vin=0,但实际情况中由于各slicer两根差分线的失配,造成slicer输入的差分值不为0,而是存在一个offset值,该步校准的目的就是计算出此offset值的大小。此阶段图1中的门限电压veeth和veoth分别由fsm_offset_cal算法控制模块输出的偶数路error slicer的offset值ofst_ee[6:0]和奇数路error slicer的offset值ofst_eo[6:0]控制,ofst_ee和ofst_eo初始值为7’h00,此时这两路控制信号通过dac电路后输出一个较小的电压值作为error slicer的门限,所以对error slicer的输出统计一段时间后会发现数字信号一直为1,逐步增加ofst_ee和ofst_eo,当在一段时间内统计到error slicer的输出出现0时,即可认为已经找到了offset值。由于data path采用了预处理的结构,判决器的最终输出数据总是有前1bit来决定,所以四路data slicer的offset校准采用依次执行方式,具体执行步骤包括:第一步,控制dac电路的输入端控制码ofst_do_h1m=0,ofst_do_h1p=0,此时奇数路选择器的输出始终为1,偶数路始终选择门限为ve_h1m的判决器输出,此时统计data even的采样数据,并按照error slicer的校准过程逐步进行,最终找到data even-h1路径的offset值;第二步,控制dac电路的输入端控制码ofst_do_h1m=127,ofst_do_h1p=127,此时奇数路选择器的输出始终为0,偶数路始终选择门限为ve_h1p的判决器输出,此时统计data even的采样数据,并按照error slicer的校准过程逐步进行,最终找到data even h1路径的offset值;第三步,控制ofst_de_h1m=0,ofst_de_h1p=0,此时偶数路选择器的输出始终为1,奇数路始终选择门限为vo_h1m的判决器输出,此时统计data odd的采样数据,并按照error slicer的校准过程逐步进行,最终找到data odd-h1路径的offset值;第四步,控制dac电路的输入端控制码ofst_de_h1m=127,ofst_de_h1p=127,此时偶数路选择器的输出始终为0,奇数路始终选择门限为vo_h1p的判决器输出,此时统计data odd的采样数据,并按照error slicer的校准过程逐步进行,最终找到data odd h1路径的offset值。六路offset校准都完成后标志着一轮校准完成,由于干扰的存在,可能有的校准结果不准确,所以需进行多轮校准,然后对校准结果取平均值得到最终的校准结果。该步骤的校准流程控制如图3所示,图3中“idle”表示初始化,“wait-cycle”表示等待cdr锁定统计,“round_over=1?”表示判断比较器的输出数据是否包含“1”,“para_adj”表示进入偏置校准阶段,“wait_cycle”状态下在

一段时间内统计对应slicer输出的数据中存在的“0”的数目,并判断统计数目是否大于设置的门限,没有超过门限,则进入“para_adj”状态增加slicer门限电压的控制字,并等待dac settle后再次进入“wait_cycle”状态统计新结果。

[0041]

将上述偏置校准阶段估计出来的偏置值写入状态寄存器(状态寄存器包括第一锁存器、第二锁存器)保存,并在后续的ctle电路和dfe电路自适应阶段,在比较器门限电压控制字中扣除对应的偏置值。

[0042]

ctle电路自适应调节阶段,图2中总状态机的状态值state=s_ctle_cal时开始进行ctle电路的自适应调节,从图4时域波形来看,长时间处于高电平“1”或长时间处于低电平“0”的波形展现的是低频分量的幅度,跳变沿的陡峭程度展现的是高频分量的幅度,单比特0和1交替出现(即单位时间间隔内高低电平交替出现时)的波形展现的是高频分量的幅度,图4是接收信号经过ctle之前欠均衡以及经过ctle之后过均衡的时域波形,图4中横轴表示数据序号索引,纵轴表示电压值,曲线a表示ctle电路自适应均衡前的幅度变换曲线,曲线b表示ctle电路自适应均衡后的幅度变换曲线。从图4中波形可以看出,均衡之前,信号处于欠均衡状态时,高频分量幅度较小,低频分量幅度较大,跳变沿变化较慢;经过ctle电路均衡之后,高频分量符合低频分量幅度相差不大,跳变沿变得十分陡峭,但是存在过冲现象(图4中圆圈标记的地方),所以此时信号处于过均衡状态。本技术提供了一种过均衡、欠均衡的具体算法:第一步,调节ctle电路的电阻值、电容值,使电阻值r的值为中间值,获得直流增益的中间值,使电容值c的值为最小值,获得最小增益补偿,此时通过信道衰减的接收信号经过ctle电路后仍然处于欠均衡状态,此时设置信号摆幅的期望值,ctle电路自适应调节阶段,该期望值分别减掉error even/odd slicer对应的offset值后对应两路slicer的门限值控制字,初始状态下一段时间内统计error slicer输出的采样数据,如果数据全为0,则表明当前低频分量摆幅未达到设定值,需要增加电阻值(即r值)以提高直流增益,直至将r值调节到某一值,使当前r值下统计的数据中1的数量和前一个r值下统计的数据中1的数量分布在设定的1的数量门限两侧,表明当前低频分量的幅度已经达到信号摆幅的期望值,记录当前r值下数据中1的数量n0。第二步,逐步增加电容值(c值),使信号朝过均衡的方向调节,随着电容值的增加,信号波形中高频分量的幅度增加,每调节一次c值都要去统计error slicer输出数据中1的数目,当相邻的两次调节使统计的符号1的数量分布在数量n0两侧时,认为均衡恰当,当前的r值和c值便是最佳均衡时的配置值。图5为ctle自适应调节过程中的状态控制图,图5中wait_cycle为结果统计状态,r_adj为直流增益调节状态,只调节电阻值控制字,c_adj为peak增益调节状态,只调节电容值控制字,调节过程中r_adj_over=1?,即判断电容值控制字中是否包含“1”,c_adj_over=1?,即判断电阻值控制字中是否包含“0”。

[0043]

dfe电路自适应调节阶段,图2中总状态机输出的控制信号state=s_dfe_cal时,进入dfe自适应阶段,对于1-tap dfe电路(即半数据率预处理结构的dfe电路)而言,我们只考虑前1bit数据对当前数据的影响,1阶post cursor对当前数据的影响为h1,当前数据的冲击响应值为h0,当码型d-1d0=00时,当前数据的幅值dlev00=-h1-h0,当码型d-1d0=01时,当前数据的幅值dlev01=-h1 h0,当码型d-1d0=10时,当前数据的幅值dlev10=h1-h0,当码型d-1d0=11时,当前数据的幅值dlev11=h1 h0,所以-h1=(dlev00 dlev01)/2, h1=(dlev10 dlev11)/2。结合上述偏置校准得到的各路slicer的校准值,在dfe电路自适

应调节阶段,可以得到cw2dac_de_h1m=-h1 ofst_de_h1m,cw2dac_de_h1p= h1 ofst_de_h1p,cw2dac_do_h1m=-h1 ofst_do_h1m,cw2dac_do_h1p= h1 ofst_do_h1p,cw2dac_ee=dlev** ofst_ee,cw2dac_eo=dlev**_ofst_eo,“*”表示“0”或“1”。由于dfe电路中的状态机用于控制码型的分时统计,所以对于不同的码型统计时段,error slicer的门限控制字分别使用dlev00、dlev01、dlev10、dlev11来计算。dfe自适应控制算法的实现过程主要分为两步:第一步,初始状态下,cw2dac_de_h1m=0,cw2dac_de_h1p=0,cw2dac_do_h1m=0,cw2dac_do_h1p=0,此时data slicer能够最大概率的输出正确判决的数据,主要通过lms迭代算法计算dlev**,dlev**(n 1)=dlev**(n) u*sign(e)|d-1d0=**,u为设定的步长(步长为1~1/1024),e为error slicer判决输出的数据,dlev**的含义为当码型为**时,当前码元期望的模拟电压幅度,slicer当前输入的实际电压跟这个值比较得到的是error符号,通过一段时间的迭代运算dlev**会收敛于某个值。第二步,当经过一段时间的迭代运算,dlev**稳定后,通过本段开始给出的公式计算-h1和 h1,进而计算并更新得到的4路data slicer需要的门限电压控制字。

[0044]

综上可见,本技术提供的自适应均衡方法实现流程清晰,ctle电路与dfe电路组合结构的模拟电路设计、数字算法控制均便于实现,具有较强的可配置性,本技术中偏置校准的校准精度和ctle电路以及dfe电路的自适应调节精度最大程度取决于dac电路的精度,fsm_ctle控制单元的控制算法采用基于时域波形高、低频分量幅度特征作为均衡效果的判断依据,dfe控制算法采用基于误差符号的lms迭代算法,均衡范围覆盖1.62g~8.1g的波特率。本技术电路结构及自适应均衡算法在量产产品中使用,支持3~40英寸视频电缆,均衡完成后,能够灵活实现各电路参数的控制,达到产品在实际使用环境中对自适应均衡的要求。

[0045]

以上的仅是本技术的优选实施方式,本发明不限于以上实施例。可以理解,本领域技术人员在不脱离本发明的精神和构思的前提下直接导出或联想到的其他改进和变化,均应认为包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。