一种用于双电源静电保护的scr

技术领域

1.本发明涉及集成电路领域,特别是涉及一种用于双电源静电保护的scr。

背景技术:

2.对于双电源电路,不同电源域之间需要增加esd保护器件。而每一电源本身也需要电源对地的esd保护。通常的双电源esd设计至少需要3个esd器件。

3.可控硅(silicon controlled rectifier,scr)可以导通大量的电流,使多余的电荷得以快速泄放,防止内部电路被损坏,因此特别适合应用于esd保护。

4.lvtscr因为出色的esd能力和较小的面积,常被用来作为esd保护器件。

5.然而传统的lvtscr只能实现单一电源或单一io的esd保护。因此,需要提出一种新的scr结构解决上述问题。

技术实现要素:

6.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种用于双电源静电保护的scr,用于解决现有技术中传统scr只能实现单一电源或单一io的esd保护的问题。

7.为实现上述目的及其他相关目的,本发明提供一种用于双电源静电保护的scr,至少包括:

8.p型衬底;位于所述p型衬底内的p阱和n阱;所述p阱和n阱边缘彼此紧靠,并且所述p阱和所述n阱的上表面与所述p型衬底的上表面齐平;

9.所述n阱内设有第一p 区、第一n 区以及第四p 区;所述p阱内设有第二p 区、第二n 区以及第三n 区;所述p阱和所述n阱的分界处设有第三p 区;

10.所述第一p 区和所述第一n 区共同连接至第一电压;所述第四p 区、第三n 区共同连接至第二电压;所述第二p 区、第二n 区共同接地。

11.优选地,所述第一p 区、第一n 区以及第四p 区的上表面与所述n阱的上表面齐平。

12.优选地,所述第二p 区、第二n 区以及第三n 区的上表面与所述p阱的上表面齐平。

13.优选地,所述第三p 区横跨所述p阱和所述n阱并浮空。

14.优选地,由所述第二n 区和所述p阱形成的pn结、所述p阱和所述n阱形成的pn结、所述n阱和所述第一p 区形成的pn结形成第一esd电流通路。

15.优选地,由所述第一p 区、所述n阱以及所述第四p 区构成的pnp、所述第四p 区和所述n阱构成的二极管共同形成第二esd电流通路。

16.优选地,由所述第三n 区、所述p阱以及所述第二n 区构成的npn、所述p阱和所述第三n 区形成的二极管共同形成第三esd电流通路。

17.优选地,所述第一电压至地的电流通道为所述第一esd电流通路。

18.优选地,所述第二电压至地的电流通道为所述第三esd电流通路或所述第二esd电

流通路与所述第一esd电流通路。

19.优选地,所述第一电压与所述第二电压的电流通道为所述第二esd电流通路或所述第三esd电流通路与所述第一esd电流通路。

20.优选地,所述第一电压为5v vdd,其中vdd为电源电压。

21.优选地,所述第二电压为1.5v vdd。

22.如上所述,本发明的用于双电源静电保护的scr,具有以下有益效果:本发明对常规lvtscr结构进行了优化,在常规lvtscr的基础上,通过在n阱中增加p 区,在p阱中增加n 区,并把n 区,p 区短接到第二电压上,从而实现双电源的保护,并且本发明的结构也可以用于双io间的esd保护,也可以用于一电源一io之间的esd保护。

附图说明

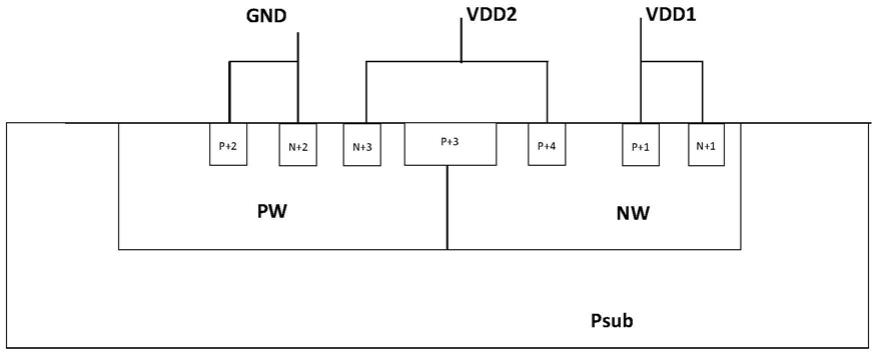

23.图1显示为本发明中的用于双电源静电保护的scr结构示意图;

24.图2显示为本发明中的用于双电源静电保护的scr的等效电路示意图。

具体实施方式

25.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

26.请参阅图1至图2。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

27.本发明提供一种用于双电源静电保护的scr,至少包括:

28.p型衬底;位于所述p型衬底内的p阱和n阱;所述p阱和n阱边缘彼此紧靠,并且所述p阱和所述n阱的上表面与所述p型衬底的上表面齐平;

29.所述n阱内设有第一p 区、第一n 区以及第四p 区;所述p阱内设有第二p 区、第二n 区以及第三n 区;所述p阱和所述n阱的分界处设有第三p 区;

30.所述第一p 区和所述第一n 区共同连接至第一电压;所述第四p 区、第三n 区共同连接至第二电压;所述第二p 区、第二n 区共同接地。

31.如图1所示,图1显示为本发明中的用于双电源静电保护的scr结构示意图,至少包括:p型衬底(psub);位于所述p型衬底(psub)内的p阱(pw)和n阱(nw);所述p阱(pw)和n阱(nw)边缘彼此紧靠,并且所述p阱(pw)和所述n阱(nw)的上表面与所述p型衬底(psub)的上表面齐平;

32.所述n阱(nw)内设有第一p 区(p 1)、第一n 区(n 1)以及第四p 区(n 4);所述p阱内设有第二p 区(p 2)、第二n 区(n 2)以及第三n 区(n 3);所述p阱(pw)和所述n阱(nw)的分界处设有第三p 区(p 3);

33.所述第一p 区(p 1)和所述第一n 区(n 1)共同连接至第一电压vdd1;所述第四p 区(p 4)和第三n 区(n 3)共同连接至第二电压vdd2;所述第二p 区(p 2)、第二n 区(n 2)

共同接地gnd。

34.本发明进一步地,本实施例中的所述第一p 区(p 1)、第一n 区(n 1)以及第四p 区(p 4)的上表面与所述n阱(nw)的上表面齐平。

35.本发明进一步地,本实施例中的所述第二p 区(p 2)、第二n 区(n 2)以及第三n 区(n 3)的上表面与所述p阱(pw)的上表面齐平。

36.本发明进一步地,本实施例中的所述第三p 区(p 3)横跨所述p阱(pw)和所述n阱(nw)并浮空。

37.如图2所示,图2显示为本发明中的用于双电源静电保护的scr的等效电路示意图。

38.本发明进一步地,本实施例中由所述第二n 区(n 2)和所述p阱(pw)形成的pn结、所述p阱(pw)和所述n阱(nw)形成的pn结、所述n阱(nw)和所述第一p 区(p 1)形成的pn结形成第一esd电流通路(esd path1)。

39.本发明进一步地,本实施例中由所述第一p 区(p 1)、所述n阱以及所述第四p 区(p 4)构成的pnp、所述第四p 区(p 4)和所述n阱(nw)构成的二极管共同形成第二esd电流通路(esd path2)。

40.本发明进一步地,本实施例中由所述第三n 区(n 3)、所述p阱(pw)以及所述第二n 区(n 2)构成的npn、所述p阱(pw)和所述第三n 区(n 3)形成的二极管共同形成第三esd电流通路(esd path3)。

41.本发明进一步地,本实施例中的所述第一电压vdd1至地gnd的电流通道为所述第一esd电流通路。

42.本发明进一步地,本实施例中的所述第二电压vdd2至地gnd的电流通道为所述第三esd电流通路或所述第二esd电流通路与所述第一esd电流通路。

43.本发明进一步地,本实施例中的所述第一电压与所述第二电压的电流通道为所述第二esd电流通路或所述第三esd电流通路与所述第一esd电流通路。

44.本发明进一步地,本实施例中的所述第一电压为5v vdd,其中vdd为电源电压。

45.本发明进一步地,本实施例中的所述第二电压为1.5v vdd。

46.也就是说,vdd1与gnd的esd电流可以走esd path1。vdd2与gnd之间的esd电流,可以走esd path3,同时也可以走esd path2加上esd path1。vdd1与vdd2之间的esd电流可以走esd path2,同时也可以这批esd path3加上esd path1。

47.综上所述,本发明对常规lvtscr结构进行了优化,在常规lvtscr的基础上,通过在n阱中增加p 区,在p阱中增加n 区,并把n 区,p 区短接到第二电压上,从而实现双电源的保护,并且本发明的结构也可以用于双io间的esd保护,也可以用于一电源一io之间的esd保护。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

48.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。