1.本技术涉及半导体技术领域,具体涉及一种功率半导体器件。

背景技术:

2.功率半导体器件是电力电子线路最基本的组成单元,其中,功率二极管常常用在功率电子电路中,为提升电路系统的鲁棒性,需要进一步提升功率二极管的鲁棒性。为了抵御电路异常,需要功率二极管承受很高的浪涌电流,例如在功率因数校正(power factor correction,pfc)应用中,系统可能存在无法被检测到的电路故障,电容的充电电流可能会以较高的频次达到正向电流的七倍以上。

3.其中,碳化硅结势垒肖特基(junction barrier controlled schottky,jbs)二极管利用pn结的空间电荷区扩展保护肖特基结,使得降低sic表面肖特基接触漏电降低。但是在现有技术中,设计如结势垒肖特基(jbs)二极管等功率器件时,出于工艺误差考虑,为保证pn结势垒区完全覆盖肖特基电极金属,最外围的pn结要宽于有源区的pn结,称为主结区。但是这种结构导致在承受多次浪涌电流时,可能导致主结区在芯片承受正向浪涌电流时先于有源区pn结开通。当主结区pn结开通后,由于电导调制效应会导致主结上承担的电流迅速增大,主结区的温度进一步升高,而pn结电流为负温度系数,最终芯片主结区域发生热奔走导致金属熔化后芯片功能失效。

技术实现要素:

4.针对上述问题,本技术提供了一种功率半导体器件,解决了现有技术中功率器件的主结区在浪涌电流作用下易失效的技术问题。

5.第一方面,本技术提供一种功率半导体器件,包括:第一导电类型衬底和位于所述衬底上方的第一导电类型漂移层,以及设置于所述漂移层上的有源区、终端区和位于所述有源区与所述终端区之间的主结区;

6.其中,所述有源区包括多个间隔设置于所述漂移层表面内的第二导电类型第一掺杂区,以及位于漂移层上方的第一金属层和第二金属层;

7.所述第一金属层覆盖所述第一掺杂区的部分上表面并与所述第一掺杂区形成欧姆接触;所述第二金属层覆盖所述漂移层未被所述第一掺杂区覆盖的部分上表面,并与该部分所述漂移层形成肖特基接触;

8.所述主结区包括设置于所述漂移层表面内的第二导电类型第二掺杂区,以及覆盖所述第二掺杂区部分上表面的电阻层;所述电阻层具有正的温度系数;

9.所述第一金属层、所述第二金属层和所述电阻层相互电连接。

10.根据本技术的实施例,可选地,上述功率半导体器件中,所述主结区还包括:覆盖所述电阻层部分上表面并与所述电阻层形成欧姆接触的第三金属层。

11.根据本技术的实施例,可选地,上述功率半导体器件中,还包括:位于所述第一金属层、所述第二金属层和所述第三金属层上方的阳极金属层;

12.其中,所述阳极金属层同时与所述第一金属层、所述第二金属层和所述第三金属层形成电连接。

13.根据本技术的实施例,可选地,上述功率半导体器件中,所述主结区还包括覆盖于所述电阻层上方的第一钝化层;

14.其中,所述第一钝化层上设置有贯穿所述第一钝化层的接触孔,所述第三金属层填充于所述接触孔内,并与所述接触孔底部的所述电阻层部分形成欧姆接触。

15.根据本技术的实施例,可选地,上述功率半导体器件中,所述第二金属层还覆盖所述电阻层未被所述第三金属层覆盖的部分上表面,并与该部分所述电阻层形成欧姆接触。

16.根据本技术的实施例,可选地,上述功率半导体器件中,所述第二金属层还还覆盖所述第一掺杂区未被所述第一金属层覆盖的部分上表面,并与该部分所述第一掺杂区形成欧姆接触。

17.根据本技术的实施例,可选地,上述功率半导体器件中,所述第二金属层与所述第一金属层接触。

18.根据本技术的实施例,可选地,上述功率半导体器件中,所述第二金属层延伸至所述第一金属层上方。

19.根据本技术的实施例,可选地,上述功率半导体器件中,所述电阻层的材料包括多晶硅。

20.根据本技术的实施例,可选地,上述功率半导体器件中,所述第一掺杂区在所述衬底上的正投影呈条形、方形或六边形。

21.根据本技术的实施例,可选地,上述功率半导体器件中,所述第一掺杂区的宽度小于所述第二掺杂区的宽度。

22.根据本技术的实施例,可选地,上述功率半导体器件中,所述第一掺杂区和所述第二掺杂区的掺杂浓度相同。

23.根据本技术的实施例,可选地,上述功率半导体器件中,所述第一掺杂区和所述第二掺杂区的深度相同。

24.根据本技术的实施例,可选地,上述功率半导体器件中,所述终端区包括设置于所述漂移层表面内的第二导电类型第三掺杂区,以及覆盖所述第三掺杂区的上表面的第二钝化层。

25.根据本技术的实施例,可选地,上述功率半导体器件中,所述第三掺杂区的掺杂浓度小于所述第一掺杂区和所述第二掺杂区的掺杂浓度。

26.根据本技术的实施例,可选地,上述功率半导体器件中,所述第三掺杂区靠近所述第二掺杂区的一侧与所述第二掺杂区接触。

27.根据本技术的实施例,可选地,上述功率半导体器件中,还包括位于所述衬底下方并与所述衬底形成电连接的阴极金属层。

28.采用上述技术方案,至少能够达到如下技术效果:

29.本技术提供一种功率半导体器件,该功率半导体器件包括第一导电类型碳化硅衬底和位于所述衬底上方的第一导电类型漂移层,以及设置于所述漂移层上的有源区、终端区和位于所述有源区与所述终端区之间的主结区;所述有源区包括多个间隔设置于所述漂移层表面内的第二导电类型第一掺杂区,以及位于漂移层上方的第一金属层和第二金属

层;所述主结区包括设置于所述漂移层表面内的第二导电类型第二掺杂区,以及覆盖所述第二掺杂区部分上表面的电阻层;所述电阻层具有正的温度系数;所述第一金属层、所述第二金属层和所述电阻层相互电连接。通过在主结区设置具有正的温度系数的电阻层,抑制芯片主结上的浪涌电流,降低主结金属被熔化的风险,提升芯片承受多次浪涌电流的能力和芯片长期应用的可靠性。该电阻层的电阻值可根据需要进行设定,进而灵活调节主结分担浪涌电流的大小。而且该电阻层与有源区的所述第一金属层、所述第二金属层形成电连接,不会损害芯片的反向阻断能力。

附图说明

30.附图是用来提供对本技术的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本技术,但并不构成对本技术的限制。在附图中:

31.图1是一种功率半导体器件的剖面结构示意图;

32.图2是本技术一示例性实施例示出的一种功率半导体器件的正面俯视示意图;

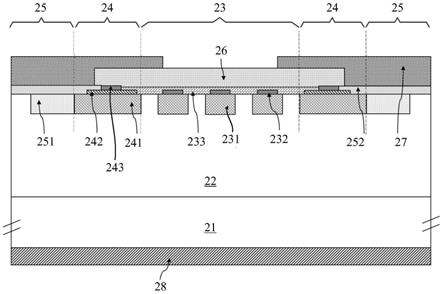

33.图3是图2沿a-a’切线的剖面结构示意图;

34.图4是本技术一示例性实施例示出的一种功率半导体器件的另一正面俯视意图;

35.图5是本技术一示例性实施例示出的另一种功率半导体器件的正面俯视示意图;

36.图6是本技术一示例性实施例示出的另一种功率半导体器件的正面俯视示意图;

37.图7是图3中的功率半导体器件的电位连接示意图;

38.图8是本技术一示例性实施例示出的另一种功率半导体器件的正面俯视示意图;

39.图9是图8中的功率半导体器件的剖面结构示意图;

40.在附图中,相同的部件使用相同的附图标记,附图并未按照实际的比例绘制。

具体实施方式

41.以下将结合附图及实施例来详细说明本技术的实施方式,借此对本技术如何应用技术手段来解决技术问题,并达到相应技术效果的实现过程能充分理解并据以实施。本技术实施例以及实施例中的各个特征,在不相冲突前提下可以相互结合,所形成的技术方案均在本技术的保护范围之内。在附图中,为了清楚,层和区的尺寸以及相对尺寸可能被夸大。自始至终相同附图标记表示相同的元件。

42.应理解,尽管可使用术语“第一”、“第二”、“第三”等描述各种元件、部件、区、层和/或部分,这些元件、部件、区、层和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层或部分与另一个元件、部件、区、层或部分。因此,在不脱离本技术教导之下,下面讨论的第一元件、部件、区、层或部分可表示为第二元件、部件、区、层或部分。

43.应理解,空间关系术语例如“在...上方”、位于...上方”、“在...下方”、“位于...下方”等,在这里可为了方便描述而被使用从而描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语意图还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,然后,描述为“在其它元件下方”的元件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在...下方”和“在...下”可包括上和下两个取向。器件可以另外地取向(旋转90度或其它取向)并且在此使用的空间描述语相应地被解释。

44.在此使用的术语的目的仅在于描述具体实施例并且不作为本技术的限制。在此使用时,单数形式的“一”、“一个”和“所述/该”也意图包括复数形式,除非上下文清楚指出另外的方式。还应明白术语“组成”和/或“包括”,当在该说明书中使用时,确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

45.这里参考作为本技术的理想实施例(和中间结构)的示意图的横截面图来描述本技术的实施例。这样,可以预期由于例如制备技术和/或容差导致的从所示形状的变化。因此,本技术的实施例不应当局限于在此所示的区的特定形状,而是包括由于例如制备导致的形状偏差。例如,显示为矩形的注入区在其边缘通常具有圆的或弯曲特征和/或注入浓度梯度,而不是从注入区到非注入区的二元改变。同样,通过注入形成的埋藏区可导致该埋藏区和注入进行时所经过的表面之间的区中的一些注入。因此,图中显示的区实质上是示意性的,它们的形状并不意图显示器件的区的实际形状且并不意图限定本技术的范围。

46.为了彻底理解本技术,将在下列的描述中提出详细的结构,以便阐释本技术提出的技术方案。本技术的较佳实施例详细描述如下,然而除了这些详细描述外,本技术还可以具有其他实施方式。

47.一种功率半导体器件,如图1所示,包括:衬底11、漂移层12、有源区13、主结区14、终端区15、阳极金属层16、保护胶层17和阴极金属层18。

48.其中,衬底11为第一导电类型的衬底,其厚度较厚。衬底11可以为碳化硅基底。

49.漂移层12为第一导电类型的漂移层,位于衬底11上方。根据芯片耐压能力不同,调整漂移层12的掺杂浓度和厚度。漂移层12的掺杂浓度可以小于衬底11的掺杂浓度,漂移层12的厚度可以小于衬底11的厚度。

50.有源区13、主结区14和终端区15均设置于漂移层12上,主结区14位于有源区13和终端区15之间。

51.有源区13包括多个有源区13包括多个间隔设置于漂移层12表面内的第二导电类型第一掺杂区131,以及位于漂移层12上方的第一金属层132和第二金属层133。

52.第一金属层132覆盖第一掺杂区131的部分上表面并与第一掺杂区131形成欧姆接触。

53.第二金属层133覆盖漂移层12未被第一掺杂区131覆盖的部分上表面,并与该部分漂移层12形成肖特基接触。

54.主结区14包括设置于漂移层12表面内的第二导电类型第二掺杂区141,以及位于第二掺杂区141上方的第三金属层142。其中,第二掺杂区141的宽度大于第一掺杂区131的宽度。

55.第一金属层132、第二金属层133和第三金属层142通过其上方的阳极金属层16形成电连接。

56.终端区15包括设置于漂移层12表面内的第二导电类型第三掺杂区151,以及位于第三掺杂区151上方的钝化层152。

57.保护胶层17覆盖钝化层152以及部分阳极金属层16。

58.阴极金属层18位于衬底11下方并与衬底11形成电连接。

59.该功率半导体器件中,由于第二掺杂区141的宽度大于第一掺杂区131的宽度,所以主结区14的pn结要宽于有源区13的pn结,虽然保证了pn结势垒区被肖特基电极金属(第二金属层133)完全覆盖。但是这种结构导致在承受多次浪涌电流时,可能导致主结区14在芯片承受正向浪涌电流时先于有源区13pn结开通。当主结区14的pn结开通后,由于电导调制效应会导致主结上承担的电流迅速增大,主结区14的温度进一步升高,而pn结电流为负温度系数,最终芯片主结区域发生热奔走导致金属熔化后芯片功能失效。

60.因此,本技术提供另一种的功率半导体器件,可大幅改善在承受浪涌情况下主结的电流分布,提高芯片承受浪涌电流的能力。

61.实施例一

62.图2是本技术一示例性实施例示出的一种功率半导体器件的正面俯视示意图。

63.图3是本技术一示例性实施例示出的一种功率半导体器件的剖面结构示意图。如图2和3所示,本技术实施例提供一种功率半导体器件,包括衬底21、漂移层22、有源区23、主结区24、终端区25、阳极金属层26、保护胶层27和阴极金属层28。

64.其中,衬底21为第一导电类型的衬底,其厚度较厚。衬底21可以为碳化硅基底。

65.漂移层22为第一导电类型的漂移层,位于衬底21上方。根据芯片耐压能力不同,调整漂移层22的掺杂浓度和厚度。漂移层22的掺杂浓度可以小于衬底21的掺杂浓度,漂移层22的厚度可以小于衬底21的厚度。

66.有源区23、主结区24和终端区25均设置于漂移层22上,主结区24位于有源区23和终端区25之间。

67.有源区23包括多个间隔设置于漂移层22表面内的第二导电类型第一掺杂区231,以及位于漂移层22上方的第一金属层232和第二金属层233。

68.第一金属层232覆盖第一掺杂区231的部分上表面并与第一掺杂区231形成欧姆接触。且第一金属层232不与漂移层22未被第一掺杂区231覆盖的部分接触。

69.第一金属层232的材料包括铝、镍等具有低接触电阻率的金属。

70.第二金属层233覆盖漂移层22未被第一掺杂区231覆盖的部分上表面,并与该部分漂移层22形成肖特基接触。

71.进一步的,第二金属层233还覆盖电阻层242未被第三金属层243覆盖的部分上表面,并与该部分电阻层242形成欧姆接触。

72.进一步的,第二金属层233与第一金属层232接触,甚至第二金属层233可以延伸至第一金属层232上方。

73.第二金属层233的材料包括钛、镍、钼等金属。

74.主结区24包括设置于漂移层22表面内的第二导电类型第二掺杂区241,以及覆盖第二掺杂区241部分上表面的电阻层242;电阻层242具有正的温度系数。

75.第一金属层232、第二金属层233和电阻层242相互电连接。

76.本实施例中,通过在主结区24设置具有正的温度系数的电阻层242,该电阻层242具有导电性和正温度系数。在芯片反向阻断时,主结区24通过电阻层242与第一金属层232、第二金属层233相连,不改变主结的电位分布,因此芯片的反向阻断能力不受影响。当芯片承受较高的浪涌电流时,电阻层242具有正的温度系数,可以在一定程度上抑制主结上的分担的电流,从而降低主结上金属(第三金属层243)被熔化的风险,来提升芯片承受多次浪涌

电流的能力和芯片长期应用的可靠性。

77.进一步的,电阻层242的材料包括多晶硅。电阻层242的厚度设置为50nm以上,优选n型多晶硅且其掺杂浓度根据实际器件需要进行调整,可以在1e12cm-3

以上。

78.电阻层242可以通过掺杂浓度调节电阻值,进而灵活调节主结分担浪涌电流的大小。

79.进一步的,主结区24还包括:覆盖电阻层242部分上表面并与电阻层242形成欧姆接触的第三金属层243。

80.进一步的,第二金属层233还覆盖电阻层242未被第三金属层243覆盖的部分上表面,并与该部分电阻层242形成欧姆接触。

81.而且,第二掺杂区241的宽度大于第一掺杂区231的宽度,即使有工艺误差,也使得有源区23的pn结完全被肖特基电极金属(第二金属层233)覆盖。

82.而本技术中,主结区24中电阻层242的设置,在保证有源区23的pn结完全被肖特基电极金属(第二金属层233)覆盖的同时,还抑制芯片主结上的浪涌电流,降低主结金属被熔化的风险。

83.阳极金属层26位于第一金属层232、第二金属层233和第三金属层243上方,并同时与第一金属层232、第二金属层233和第三金属层243形成电连接。

84.上述阳极金属层26的厚度较厚,其厚度可以为2~6μm。

85.可以理解为,第一金属层232、第二金属层233和第三金属层243通过阳极金属层26形成相互电连接。

86.在一些情况下,第一掺杂区231和第二掺杂区241的掺杂浓度相同,第一掺杂区231和第二掺杂区241的深度相同。

87.第一掺杂区231和第二掺杂区241可以通过相同的离子注入工艺制备而成。

88.本实施例中,如图4所示,第一掺杂区231在衬底21上的正投影呈条形,其中,条形是指上述多个第一掺杂区231沿第一方向延伸,并沿与第一方向垂直的第二方向排布。

89.或者,如图5所示,第一掺杂区231在衬底21上的正投影呈方形,其中,方形可以为正方形或长方形,可以理解为将图4中条形第一掺杂区231截断为多个方形的掺杂区。

90.或者,如图6所示,第一掺杂区231在衬底21上的正投影呈六边形。

91.本实施例中,终端区25包括设置于漂移层22表面内的第二导电类型第三掺杂区251,以及覆盖第三掺杂区251的上表面的第二钝化层252。

92.第三掺杂区251的掺杂浓度小于第一掺杂区231和第二掺杂区241的掺杂浓度。

93.进一步的,第三掺杂区251靠近第二掺杂区241的一侧与第二掺杂区241接触。

94.进一步的,第二钝化层252可以向主结区24的方向延伸,延伸至电阻层242上方,覆盖电阻层242的部分上表面。

95.第二钝化层252的材料可以为sio2、sipos、sion等绝缘材料。

96.阴极金属层28位于衬底21下方并与衬底21形成电连接。阴极金属层28的材料可以为铝等具有较低接触电阻率的金属。

97.上述各金属层之间的电连接关系,如图7所示,第一金属层232、第二金属层233和第三金属层243通过阳极金属层26连接同一电信号。

98.保护胶层27覆盖钝化层以及部分阳极金属层26。

99.本实施例中,上述功率半导体器件可以为碳化硅结势垒肖特基(jbs)二极管。

100.在本实施例中,第一导电类型和第二导电类型相反。例如,第一导电类型为n型时,第二导电类型为p型;第一导电类型为p型时,第二导电类型为n型。具体地,根据实际需要制备的器件类型进行合理选择即可。

101.本技术提供一种功率半导体器件,该功率半导体器件包括第一导电类型碳化硅衬底21和位于衬底21上方的第一导电类型漂移层22,以及设置于漂移层22上的有源区23、终端区25和位于有源区23与终端区25之间的主结区24;有源区23包括多个间隔设置于漂移层22表面内的第二导电类型第一掺杂区231,以及位于漂移层22上方的第一金属层232和第二金属层233;主结区24包括设置于漂移层22表面内的第二导电类型第二掺杂区241,以及覆盖第二掺杂区241部分上表面的电阻层242;电阻层242具有正的温度系数;第一金属层232、第二金属层233和电阻层242相互电连接。通过在主结区24设置具有正的温度系数的电阻层242,抑制芯片主结上的浪涌电流,降低主结金属(第三金属层243)被熔化的风险,提升芯片承受多次浪涌电流的能力和芯片长期应用的可靠性。该电阻层242的电阻值可根据需要进行设定,进而灵活调节主结分担浪涌电流的大小。而且该电阻层242与有源区23的第一金属层232、第二金属层233形成电连接,不会损害芯片的反向阻断能力。

102.实施例二

103.图8是本技术一示例性实施例示出的另一种功率半导体器件的正面俯视示意图。

104.图9是本技术一示例性实施例示出的另一种功率半导体器件的剖面结构示意图。如图8和9所示,本技术实施例提供一种功率半导体器件,包括衬底21、漂移层22、有源区23、主结区24、终端区25、阳极金属层26、保护胶层27和阴极金属层28。

105.其中,衬底21为第一导电类型的衬底21,其厚度较厚。衬底21可以为碳化硅基底。

106.漂移层22为第一导电类型的漂移层22,位于衬底21上方。根据芯片耐压能力不同,调整漂移层22的掺杂浓度和厚度。漂移层22的掺杂浓度可以小于衬底21的掺杂浓度,漂移层22的厚度可以小于衬底21的厚度。

107.有源区23、主结区24和终端区25均设置于漂移层22上,主结区24位于有源区23和终端区25之间。

108.有源区23包括多个间隔设置于漂移层22表面内的第二导电类型第一掺杂区231,以及位于漂移层22上方的第一金属层232和第二金属层233。

109.第一金属层232覆盖第一掺杂区231的部分上表面并与第一掺杂区231形成欧姆接触。且第一金属层232不与漂移层22未被第一掺杂区231覆盖的部分接触。

110.第一金属层232的材料包括铝、镍等具有低接触电阻率的金属。

111.第二金属层233覆盖漂移层22未被第一掺杂区231覆盖的部分上表面,并与该部分漂移层22形成肖特基接触。

112.进一步的,第二金属层233还覆盖电阻层242未被第三金属层243覆盖的部分上表面,并与该部分电阻层242形成欧姆接触。

113.进一步的,第二金属层233与第一金属层232接触,甚至第二金属层233可以延伸至第一金属层232上方。

114.第二金属层233的材料包括钛、镍、钼等金属。

115.主结区24包括设置于漂移层22表面内的第二导电类型第二掺杂区241,以及覆盖

第二掺杂区241部分上表面的电阻层242;电阻层242具有正的温度系数。

116.第一金属层232、第二金属层233和电阻层242相互电连接。

117.本实施例中,通过在主结区24设置具有正的温度系数的电阻层242,该电阻层242具有导电性和正温度系数。在芯片反向阻断时,主结区24通过电阻层242与第一金属层232、第二金属层233相连,不改变主结的电位分布,因此芯片的反向阻断能力不受影响。当芯片承受较高的浪涌电流时,电阻层242具有正的温度系数,可以在一定程度上抑制主结上的分担的电流,从而降低主结上金属(第三金属层243)被熔化的风险,来提升芯片承受多次浪涌电流的能力和芯片长期应用的可靠性。

118.进一步的,电阻层242的材料包括多晶硅。电阻层242的厚度设置为50nm以上,优选n型多晶硅且其掺杂浓度根据实际器件需要进行调整,可以在1e12cm-3

以上。

119.电阻层242可以通过掺杂浓度调节电阻值,进而灵活调节主结分担浪涌电流的大小。

120.本实施例中,主结区24还包括:覆盖于电阻层242上方的第一钝化层244;其中,第一钝化层244上设置有贯穿第一钝化层244的接触孔245。

121.主结区24还包括:覆盖电阻层242部分上表面并与电阻层242形成欧姆接触的第三金属层243。第三金属层243填充于接触孔245内,并与接触孔245底部的电阻层242部分形成欧姆接触。

122.接触孔245的数量可以为多个,如图8所示。

123.对应的,本实施例中,通过接触孔245的尺寸和数量的设计,可以调节电阻层242与第二掺杂区241之间的接触电阻。

124.进一步的,第二金属层233还覆盖电阻层242未被第三金属层243覆盖的部分上表面,并与该部分电阻层242形成欧姆接触。

125.而且,第二掺杂区241的宽度大于第一掺杂区231的宽度,即使有工艺误差,也使得有源区23的pn结完全被肖特基电极金属(第二金属层233)覆盖。

126.而本技术中,主结区24中电阻层242的设置,在保证有源区23的pn结完全被肖特基电极金属(第二金属层233)覆盖的同时,还抑制芯片主结上的浪涌电流,降低主结金属(第三金属层243)被熔化的风险。

127.阳极金属层26位于第一金属层232、第二金属层233和第三金属层243上方,并同时与第一金属层232、第二金属层233和第三金属层243形成电连接。

128.上述阳极金属层26的厚度较厚,其厚度可以为2~6μm。

129.可以理解为,第一金属层232、第二金属层233和第三金属层243通过阳极金属层26形成相互电连接。

130.在一些情况下,第一掺杂区231和第二掺杂区241的掺杂浓度相同,第一掺杂区231和第二掺杂区241的深度相同。

131.第一掺杂区231和第二掺杂区241可以通过相同的离子注入工艺制备而成。

132.本实施例中,第一掺杂区231在衬底21上的正投影呈条形,其中,条形是指上述多个第一掺杂区231沿第一方向延伸,并沿与第一方向垂直的第二方向排布。

133.或者,第一掺杂区231在衬底21上的正投影呈方形,其中,方形可以为正方形或长方形,可以理解为将上述条形第一掺杂区231截断为多个方形的掺杂区。

134.或者,第一掺杂区231在衬底21上的正投影呈六边形。

135.本实施例中,终端区25包括设置于漂移层22表面内的第二导电类型第三掺杂区251,以及覆盖第三掺杂区251的上表面的第二钝化层252。

136.第三掺杂区251的掺杂浓度小于第一掺杂区231和第二掺杂区241的掺杂浓度。

137.进一步的,第三掺杂区251靠近第二掺杂区241的一侧与第二掺杂区241接触。

138.进一步的,第二钝化层252可以向主结区24的方向延伸,延伸至电阻层242上方,覆盖电阻层242的部分上表面。

139.第二钝化层252的材料可以为sio2、sipos、sion等绝缘材料。

140.阴极金属层28位于衬底21下方并与衬底21形成电连接。阴极金属层28的材料可以为铝等具有较低接触电阻率的金属。

141.保护胶层27覆盖钝化层以及部分阳极金属层26。

142.本实施例中,上述功率半导体器件可以为碳化硅结势垒肖特基(jbs)二极管。

143.在本实施例中,第一导电类型和第二导电类型相反。例如,第一导电类型为n型时,第二导电类型为p型;第一导电类型为p型时,第二导电类型为n型。具体地,根据实际需要制备的器件类型进行合理选择即可。

144.本技术提供一种功率半导体器件,该功率半导体器件包括第一导电类型碳化硅衬底21和位于衬底21上方的第一导电类型漂移层22,以及设置于漂移层22上的有源区23、终端区25和位于有源区23与终端区25之间的主结区24;有源区23包括多个间隔设置于漂移层22表面内的第二导电类型第一掺杂区231,以及位于漂移层22上方的第一金属层232和第二金属层233;主结区24包括设置于漂移层22表面内的第二导电类型第二掺杂区241,以及覆盖第二掺杂区241部分上表面的电阻层242;电阻层242具有正的温度系数;第一金属层232、第二金属层233和电阻层242相互电连接。通过在主结区24设置具有正的温度系数的电阻层242,抑制芯片主结上的浪涌电流,降低主结金属被熔化的风险,提升芯片承受多次浪涌电流的能力和芯片长期应用的可靠性。该电阻层242的电阻值可根据需要进行设定,进而灵活调节主结分担浪涌电流的大小。而且该电阻层242与有源区23的第一金属层232、第二金属层233形成电连接,不会损害芯片的反向阻断能力。

145.实施例三

146.在实施例一或二的基础上,本实施例提供另一种功率半导体器件,包括衬底21、漂移层22、有源区23、主结区24、终端区25、阳极金属层26、保护胶层27和阴极金属层28。

147.本实施例中,第一基区为衬底21为n 衬底,其掺杂浓度为1e18~1e19cm-3

。n 衬底的掺杂浓度由芯片阻断电压优化选择。

148.漂移层22为n-漂移层,其掺杂浓度为1e14~5e16cm-3

。

149.有源区23包括多个间隔设置于漂移层22表面内的第二导电类型第一掺杂区231,以及位于漂移层22上方的第一金属层232和第二金属层233。

150.主结区24包括设置于漂移层22表面内的第二导电类型第二掺杂区241,以及覆盖第二掺杂区241部分上表面的电阻层242;电阻层242具有正的温度系数。

151.第一掺杂区231和第二掺杂区241均为p 掺杂区,其掺杂浓度大于或等于1e18cm-3

,深度为0.5~2μm。

152.在一些情况下,第一掺杂区231和第二掺杂区241,通过相同离子注入形成,具有相

同的浓度和深度。

153.电阻层242的材料可以为n型多晶硅且其掺杂浓度根据实际器件需要进行调整,可以在1e12cm-3

以上,厚度在50nm以上。

154.终端区25包括设置于漂移层22表面内的第二导电类型第三掺杂区251,以及覆盖第三掺杂区251的上表面的第二钝化层252。

155.第三掺杂区251均为p掺杂区,其掺杂浓度为5e16~1e18cm-3

。

156.上述各部件的位置关系与实施例一或二中相同,本实施例中不再赘述。

157.以上仅为本技术的优选实施例而已,并不用于限制本技术,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。虽然本技术所公开的实施方式如上,但的内容只是为了便于理解本技术而采用的实施方式,并非用以限定本技术。任何本技术所属技术领域内的技术人员,在不脱离本技术所公开的精神和范围的前提下,可以在实施的形式上及细节上作任何的修改与变化,但本技术的保护范围,仍须以所附的权利要求书所界定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。