1.本发明涉及半导体封装技术领域,具体涉及一种功率半导体芯片封装结构。

背景技术:

2.目前电力系统的大功率电力电子装置绝大多数都是采用硅电力电子器件,如igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)芯片器件、晶闸管芯片器件、gto(gate turn-off thyristor,可关断晶闸管)芯片器件等,来实现电能的控制和转换,由于硅电力电子器件受制于材料本身在耐压、工作温度等物理特性的限制,因此要想从根本上提高大功率电力电子装备的可靠性和稳定性,降低系统的总体损耗,提高能源的控制转换效率,需要研究开发更高耐压、更低功耗和耐高温的新型电力电子器件。碳化硅(silicon carbide,sic)器件是目前为止技术最成熟、应用最广泛的第三代半导体电力电子器件之一,可以打破传统硅基器件的物理极限,具有电压等级高、通流能力大、损耗小、散热快等优点,可广泛应用于固态变压器、固态断路器等新型电力电子装备以及传统的facts和直流输电装备,将对电力系统的经济安全运行等方面产生重要影响,实现电网技术的革新。

3.但目前针对于sic芯片的封装结构大多数仍然沿用硅基芯片的焊接封装型式,现有技术的功率半导体芯片封装结构的耐压性较低,其封装参数显然不适用于sic芯片高关断速度、低损耗的特性,因此需针对高压的功率芯片研发新型封装结构。

技术实现要素:

4.因此,本发明要解决的技术问题在于克服现有功率半导体芯片封装结构的耐压性较低,从而提供一种功率半导体芯片封装结构。

5.本发明提供一种功率半导体芯片封装结构,包括:第一基板电极;位于部分所述第一基板电极上且与所述第一基板电极电连接的功率半导体芯片;环绕所述功率半导体芯片的线圈屏蔽结构,所述线圈屏蔽结构包括导电线圈以及包覆所述导电线圈的绝缘体。

6.可选的,所述绝缘体包括陶瓷。

7.可选的,所述绝缘体与所述功率半导体芯片之间的距离1mm-10mm。

8.可选的,所述线圈屏蔽结构为圆环状结构。

9.可选的,所述功率半导体芯片背离所述第一基板电极的一侧表面具有发射极;所述功率半导体芯片封装结构还包括:位于所述发射极上的导电连接件,所述导电连接件包括第一子导电连接部、第二子导电连接部、以及位于所述第一子导电连接部和第二子导电连接部之间的绝缘部,所述第一子导电连接部、绝缘部和第二子导电连接部在平行于所述第一基板电极表面的方向排布,所述第一子导电连接部的高度大于所述第二子导电连接部的高度,所述第一子导电连接部和所述第二子导电连接部均与所述发射极连接;与所述第一基板电极相对设置的第二基板电极;位于所述第二基板电极和所述第一基板电极之间的辅助发射极电路板;所述第一子导电连接部贯穿所述辅助发射极电路板且与所述第二基板

电极电连接,所述第一子导电连接部与所述辅助发射极电路板电绝缘;所述第二子导电连接部与所述辅助发射极电路板电连接。

10.可选的,所述第一子导电连接部包括第一子底层连接层、以及位于所述第一子底层连接层上方的一层或多层第一子顶层连接层,所述第一子底层连接层为整面结构,所述第一子顶层连接层中具有若干第一微孔;所述第二子导电连接部包括第二子底层连接层、以及位于所述第二子底层连接层上方的一层或多层第二子顶层连接层,所述第二子底层连接层为整面结构,所述第二子顶层连接层中具有若干第二微孔。

11.可选的,所述辅助发射极电路板的数量为若干个,若干个辅助发射极电路板包括第一辅助发射极电路板和位于所述第一辅助发射极电路板背离所述第一基板电极一侧的第二辅助发射极电路板;部分功率半导体芯片的发射极通过所述第二子导电连接部与所述第一辅助发射极电路板电连接,部分功率半导体芯片的发射极通过所述第二子导电连接部与所述第二辅助发射极电路板电连接;所述第一辅助发射极电路板中的第一互联线与所述第二辅助发射极电路板中的第二互联线在所述第一基板电极表面的投影至少部分重合,对于在所述第一基板电极表面的投影重合的第一互联线和第二互联线,第一互连线中的电流方向与第二互连线中的电流方向相反。

12.可选的,所述功率半导体芯片背离所述第一基板电极的一面具有栅极;所述功率半导体芯片封装结构还包括:位于所述第一基板电极上且位于所述功率半导体芯片侧部的衬板,所述衬板背离所述第一基板电极的一侧表面具有导电柱;连接所述栅极和所述导电柱的键合引线;与所述第一基板电极相对设置的栅极电路板,所述功率半导体芯片、所述导电柱、所述衬板均位于所述栅极电路板和所述第一基板电极之间,所述导电柱与所述栅极电路板电连接。

13.可选的,还包括:支撑柱,位于所述衬板和所述栅极电路板之间且位于所述导电柱的侧部。

14.可选的,所述栅极电路板的数量为若干个,若干个栅极电路板包括第一栅极电路板和位于所述第一栅极电路板背离所述第一基板电极一侧的第二栅极电路板;部分功率半导体芯片的栅极通过所述键合引线和所述导电柱与所述第一栅极电路板电连接,部分功率半导体芯片的栅极通过所述键合引线和所述导电柱与所述第二栅极电路板电连接;所述第一栅极电路板中的第三互联线与所述第二栅极电路板中的第四互联线在第一基板电极表面的投影至少部分重合,对于在所述第一基板电极表面的投影重合的第三互连线和第四互连线,第三互连线中的电流方向与第四互连线中的电流方向相反。

15.可选的,还包括:管壳,所述管壳包围所述第一基板电极与所述第二基板电极。

16.本发明技术方案,具有如下优点:

17.本发明提供的功率半导体芯片封装结构,所述线圈屏蔽结构环绕所述功率半导体芯片,所述线圈屏蔽结构包括导电线圈以及包覆所述导电线圈的绝缘体,所述线圈屏蔽结构可均衡所述功率半导体芯片周围电场集中、降低所述功率半导体芯片击穿风险,使所述功率半导体芯片封装结构具有较高的耐压性。

18.进一步的,位于所述功率半导体芯片发射极上的导电连接件,所述导电连接件包括第一子导电连接部、第二子导电连接部、以及位于所述第一子导电连接部和第二子导电连接部之间的绝缘部;所述第一子导电连接部贯穿所述辅助发射极电路板且与所述第二基

板电极电连接,所述第一子导电连接部与所述辅助发射极电路板电绝缘;所述第二子导电连接部与所述辅助发射极电路板电连接,这样使得能从第二基板电极和辅助发射极电路板上分别引出发射极电流。其次,功率半导体芯片底面能通过第一基板电极散热,所述功率半导体芯片的发射极能通过第一子导电连接部和第二子导电连接部进行散热,因此所述导电连接件具备双面散热能力。

19.进一步的,所述第一子导电连接部包括第一子底层连接层、以及位于所述第一子底层连接层上方的一层或多层第一子顶层连接层,第一子底层连接层为整面结构,所述第一子顶层连接层中具有若干第一微孔;所述第二子导电连接部包括第二子底层连接层、以及位于所述第二子底层连接层上方的一层或多层第二子顶层连接层,第二子底层连接层为整面结构,所述第二子顶层连接层中具有若干第二微孔。由于第一子顶层连接层中具有若干第一微孔,第二子顶层连接层中具有若干第二微孔,所述第一微孔与所述第二微孔中的空隙在所述功率半导体芯片封装结构受到压力时使所述导电连接件产生微小形变,可均匀所述功率半导体芯片受到的压力。

20.进一步的,所述第一辅助发射极电路板中的第一互联线与第二辅助发射极电路板中的第二互联线在第一基板电极表面的投影至少部分重合,能最大限度的确保每个功率半导体芯片收到驱动信号的时间一致;对于在第一基板电极表面的投影重合的第一互联线和第二互联线,第一互连线中的电流方向与第二互连线中的电流方向相反,可以消除部分发射极回路因功率半导体芯片封装结构产生的寄生电感,降低测试时发射极电压过冲与震荡现象。

21.进一步的,所述第一栅极电路板中的第三互联线与第二栅极电路板中的第四互联线在第一基板电极表面的投影至少部分重合,能最大限度的确保每个功率半导体芯片收到驱动信号的时间一致;对于在第一基板电极表面的投影重合的第三互连线和第四互连线,第三互连线中的电流方向与第四互连线中的电流方向相反,可以消除部分栅极回路因功率半导体芯片封装结构产生的寄生电感,降低测试时发射极电压过冲与震荡现象。

附图说明

22.为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

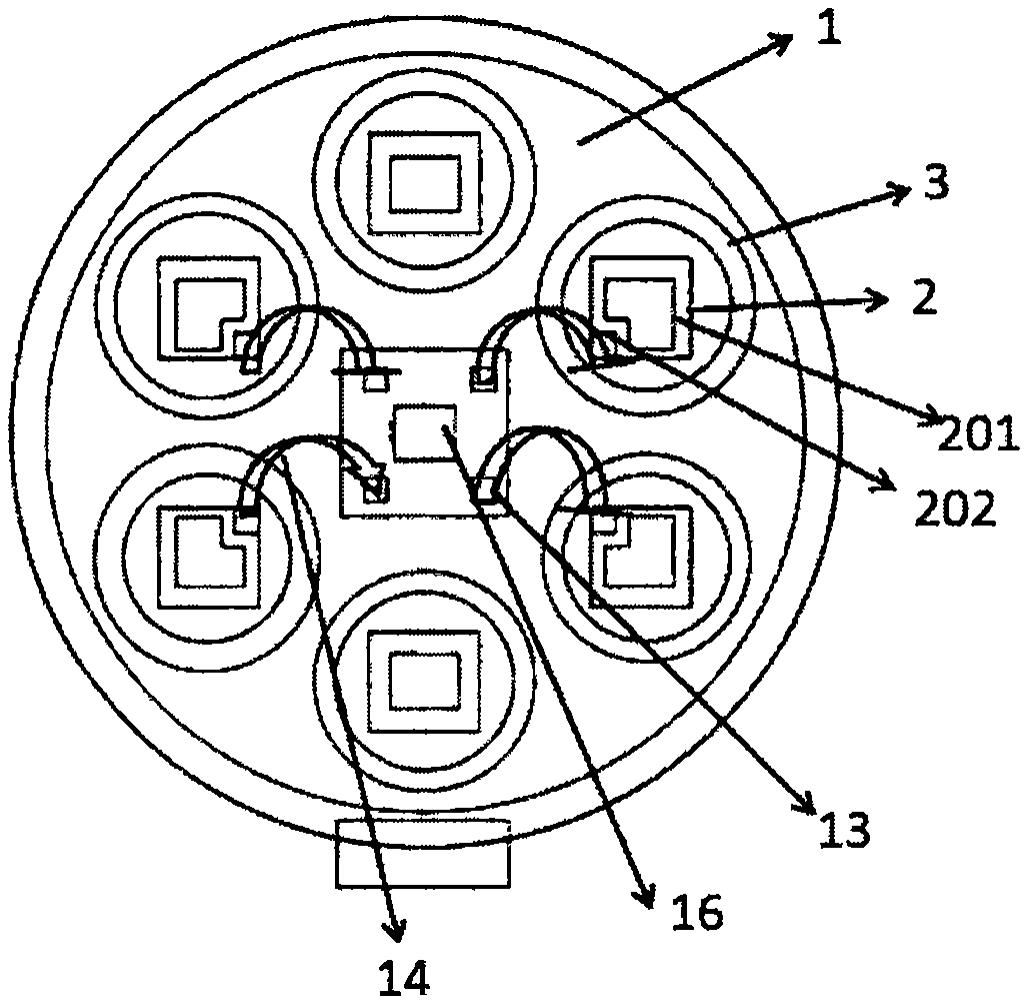

23.图1为本发明提供的功率半导体芯片的连接示意图;

24.图2为本发明提供的部分线圈屏蔽结构的结构示意图;

25.图3为本发明提供的导电连接件的结构示意图;

26.图4为本发明提供的第一辅助发射极电路板的结构示意图;

27.图5为本发明提供的第二辅助发射极电路板的结构示意图;

28.图6为本发明提供的第一绝缘垫板的结构示意图;

29.图7为本发明提供的第一栅极电路板的结构示意图;

30.图8为本发明提供的第二栅极电路板的结构示意图;

31.图9为本发明提供的第二绝缘垫板的结构示意图;

32.图10为本发明提供的管壳的结构示意图;

33.图11为本发明提供的功率半导体芯片封装结构的剖面图。

34.附图标记说明:

35.1-第一基板电极;2-功率半导体芯片;201-发射极;202-栅极;3-线圈屏蔽结构;4-导电线圈;5-绝缘体;6-导电连接件;7-第一子导电连接部;8-第二子导电连接部;9-绝缘部;71-第一子底层连接层;72-第一子顶层连接层;73-第一微孔;81-第二子底层连接层;82-第二子顶层连接层;83-第二微孔;10-第二基板电极;11-辅助发射极电路板;111-第一辅助发射极电路板;112-第二辅助发射极电路板;113-第一互连线;114-第二互连线;115-第一绝缘垫板;12-衬板;13-导电柱;14-键合引线;15-栅极电路板;16-支撑柱;151-第一栅极电路板;152-第二栅极电路板;153-第三互联线;154-第四互联线;155-第二绝缘垫板;17-管壳。

具体实施方式

36.下面将结合附图对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

37.在本发明的描述中,需要说明的是,术语“上”、“下”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

38.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

39.此外,下面所描述的本发明不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

40.本发明提供一种功率半导体芯片封装结构,结合参考图1与图2,包括:

41.第一基板电极1;

42.位于部分所述第一基板电极1上且与所述第一基板电极1电连接的功率半导体芯片2;

43.环绕所述功率半导体芯片2的线圈屏蔽结构3,所述线圈屏蔽结构3包括导电线圈4以及包覆所述导电线圈4的绝缘体5。

44.在一个实施例中,所述功率半导体芯片2的一侧表面具有集电极,功率半导体芯片2的集电极与所述第一基板电极1采用烧结工艺进行连接,例如纳米银烧结工艺;在其他实施例中,所述功率半导体芯片2与所述第一基板电极1还可以采用其他工艺进行连接。

45.所述功率半导体芯片2的集电极与所述第一基板电极1采用烧结工艺进行连接可以降低所述功率半导体芯片2的接触电阻与热阻,进一步降低所述功率半导体芯片封装结

构的损耗。

46.在一个实施例中,所述绝缘体5的材料包括陶瓷;在其他实施例中,所述绝缘体5的材料还可以包括其他绝缘材料。

47.在一个实施例中,所述绝缘体5采用耐高温且高绝缘胶固定在所述功率半导体芯片2的周围,例如所述耐高温且高绝缘胶的材料包括兼顾高绝缘强度与良好粘接强度的硅橡胶、环氧胶等材料;在其他实施例中,所述绝缘体5还可以采用其他方式固定在所述功率半导体芯片2的周围。

48.所述线圈屏蔽结构3可以均匀功率半导体芯片2周围的电场强度,提高功率半导体芯片2可靠性。在一个实施例中,所述线圈屏蔽结构3的形状为的形状为圆环状结构,圆环状结构的线圈屏蔽结构3能更好的均匀功率半导体芯片2周围的电场强度。

49.在其他实施例中,所述线圈屏蔽结构3的形状还可以是其他形状。

50.在一个实施例中,所述绝缘体5与所述功率半导体芯片2之间的距离为1mm-10mm,例如:2mm;若所述绝缘体5与所述功率半导体芯片2之间的距离小于1mm,则不利于绝缘灌封材料的填充,使所述功率半导体芯片封装结构容易存在缺陷,导致在测试过程中所述功率半导体芯片封装结构容易发生局放现象,使所述功率半导体芯片封装结构的绝缘性能不明显;若所述绝缘体5与所述功率半导体芯片2之间的距离大于10mm;则形成所述功率半导体芯片封装结构尺寸过大,造成空间浪费,使所述功率半导体芯片封装结构的功率密度达不到较优的效果。

51.在一个实施例中,所述导电线圈4包括:金属导线,例如:铜导线;在其他实施例中,所述导电线圈4还可以包括其他的金属。

52.所述功率半导体芯片2背离所述第一基板电极1的一侧表面具有发射极201和栅极202,栅极202与发射极201分立。

53.在一个实施例中,所述功率半导体芯片封装结构还包括:位于所述发射极201上的导电连接件6,结合参考图3,所述导电连接件6包括第一子导电连接部7、第二子导电连接部8、以及位于所述第一子导电连接部7和第二子导电连接部8之间的绝缘部9,第一子导电连接部7、绝缘部9和第二子导电连接部8在平行于所述第一基板电极1表面的方向排布,所述第一子导电连接部7的高度大于所述第二子导电连接部8的高度,所述第一子导电连接部7和所述第二子导电连接部8均与所述发射极201连接。

54.在一个实施例中,所述导电线圈4的高度小于第二子导电连接部8的高度。

55.在一个实施例中,所述功率半导体芯片2的发射极与所述导电连接件6采用烧结工艺进行连接,例如纳米银烧结工艺;在其他实施例中,所述功率半导体芯片2的发射极与所述导电连接件6还可以采用其他工艺进行连接。

56.所述功率半导体芯片2的发射极与所述导电连接件6采用烧结工艺进行连接,可以降低所述功率半导体芯片2的接触电阻与热阻,进一步降低所述功率半导体芯片封装结构的损耗。

57.所述第一子导电连接部7贯穿所述辅助发射极电路板11且与所述第二基板电极10电连接,所述第一子导电连接部7与所述辅助发射极电路板11电绝缘;所述第二子导电连接部8与所述辅助发射极电路板11电连接,这样使得能从所述第二基板电极10和所述辅助发射极电路板11上分别引出发射极电流。其次,功率半导体芯片2的底面能通过所述第一基板

电极1散热,所述功率半导体芯片2的发射极201能通过第一子导电连接部7和第二子导电连接部8进行散热,因此所述导电连接件6具备双面散热能力。在一个实施例中,所述第一子导电连接部7包括第一子底层连接层71、以及位于所述第一子底层连接层71上方的一层或多层第一子顶层连接层72,第一子底层连接层71为整面结构,所述第一子顶层连接层72中具有若干第一微孔73。

58.本实施例中,所述第一微孔73为均匀排布;在其他实施例中,所述第一微孔73还可以不均匀排布。

59.本实施例中,所述第一微孔73贯穿所述第一子顶层连接层72,每层的第一子顶层连接层72的第一微孔连通;在其他实施例中,所述第一微孔73可以不贯穿所述第一子顶层连接层72,每层的第一子顶层连接层72的第一微孔73可以不连通。

60.在一个实施例中,所述第一子顶层连接层72的层数根据绝缘要求与压接需求确定。

61.在一个实施例中,所述第一子底层连接层71的厚度为0.8mm-1.2mm,例如1mm。

62.在一个实施例中,每一层第一子顶层连接层72的厚度为0.8mm-1.2mm,例如1mm。

63.在一个实施例中,第一子顶层连接层72的层数为16-18。

64.在一个实施例中,所述第二子导电连接部8包括第二子底层连接层81、以及位于所述第二子底层连接层81上方的一层或多层第二子顶层连接层82,第二子底层连接层81为整面结构,所述第二子顶层连接层82中具有若干第二微孔83。

65.本实施例中,所述第二微孔83为均匀排布;在其他实施例中,所述第二微孔83还可以不均匀排布。

66.本实施例中,所述第二微孔83可以贯穿所述第二子顶层连接层82,每层的第二子顶层连接层82的第二微孔83连通;在其他实施例中,所述第二微孔83可以不贯穿所述第二子顶层连接层82,每层的第二子顶层连接层82的第二微孔83可以不连通。

67.所述绝缘部9用于隔离第一子导电连接部7和第二子导电连接部8。

68.在一个实施例中,所述绝缘部9的材料包括为橡胶等弹性绝缘材料,在其他实施例中,所述绝缘部9的材料还可以包括其他弹性绝缘材料。

69.在一个实施例中,所述第二子顶层连接层82的层数根据绝缘要求与压接需求确定。

70.在一个实施例中,所述第二子底层连接层81的厚度为0.8mm-1.2mm,例如1mm。

71.在一个实施例中,每一层第二子顶层连接层82的厚度为0.8mm-1.2mm,例如1mm。

72.在一个实施例中,第二子顶层连接层82的层数为14-16。

73.在一个实施例中,所述功率半导体芯片封装结构还包括:与所述第一基板电极1相对设置的第二基板电极10。

74.在一个实施例中,所述功率半导体芯片封装结构还包括:位于所述第二基板电极10和所述第一基板电极1之间的辅助发射极电路板11。

75.在一个实施例中,所述第一子导电连接部7贯穿所述辅助发射极电路板11且与所述第二基板电极10电连接,所述第一子导电连接部7与所述辅助发射极电路板11电绝缘;所述第二子导电连接部8与所述辅助发射极电路板11电连接。

76.在一个实施例中,所述辅助发射极电路板11的数量为若干个,参考图4至图5,若干

个辅助发射极电路板11包括第一辅助发射极电路板111和位于所述第一辅助发射极电路板111背离所述第一基板电极1一侧的第二辅助发射极电路板112。

77.在一个实施例中,部分功率半导体芯片2的发射极通过第二子导电连接部8与第一辅助发射极电路板111电连接,部分功率半导体芯片的发射极201通过第二子导电连接部8与第二辅助发射极电路板112电连接;所述第一辅助发射极电路板111中的第一互联线113与第二辅助发射极电路板112中的第二互联线114在第一基板电极1表面的投影至少部分重合,对于在第一基板电极1表面的投影重合的第一互联线113和第二互联线114,第一互连线113中的电流方向与第二互连线114中的电流方向相反,所述第一互连线113中的电流方向与第二互连线114中的电流方向相反,可以消除部分发射极回路因功率半导体芯片封装结构产生的寄生电感,降低测试时发射极电压过冲与震荡现象。

78.所述第一互联线113和所述第二互联线114背向所述第一基板电极1。

79.所述第一辅助发射极电路板111中的第一互联线113与第二辅助发射极电路板112中的第二互联线114在第一基板电极1表面的投影至少部分重合可以消除重合部分的寄生电感,从而降低所述功率半导体芯片封装结构寄生电感。

80.在一个实施例中,参考图6,所述辅助发射极电路板11还包括第一绝缘垫板115;所述第一绝缘垫板115位于所述第一辅助发射极电路板111与所述第二辅助发射极电路板112之间。

81.在一个实施例中,部分功率半导体芯片2的发射极201通过所述第二子导电连接部8与所述第一辅助发射极电路板111电连接,部分功率半导体芯片2的发射极201通过所述第二子导电连接部8与所述第二辅助发射极电路板112电连接,所述第一绝缘垫板115用于隔离第一辅助发射极电路板111与所述第二辅助发射极电路板112。

82.在一个实施例中,所述功率半导体芯片2背离所述第一基板电极1的一面具有栅极202。

83.在一个实施例中,所述功率半导体芯片封装结构还包括:位于所述第一基板电极1上且位于所述功率半导体芯片2侧部的衬板12,所述衬板12背离所述第一基板电极1的一侧表面具有导电柱13。所述衬板12的材料包括:氮化铝或铝碳化硅或陶瓷覆铜板或陶瓷覆铝板。

84.在一个实施例中,所述功率半导体芯片封装结构还包括:连接所述栅极202和所述导电柱13的键合引线14。

85.在一个实施例中,所述功率半导体芯片封装结构还包括:与所述第一基板电极1相对设置的栅极电路板15,所述功率半导体芯片2、所述导电柱13、所述衬板12均位于所述栅极电路板15和所述第一基板电极1之间,所述导电柱13与所述栅极电路板15电连接。

86.所述栅极电路板15位于辅助发射极电路板11和所述第一基板电极1之间。

87.在一个实施例中,所述功率半导体芯片封装结构还包括:支撑柱16,所述支撑柱16位于所述衬板12和所述栅极电路板15之间且位于所述导电柱13的侧部。

88.在一个实施例中,所述栅极电路板15的数量为若干个,参考图7至图8,若干个栅极电路板包括第一栅极电路板151和位于所述第一栅极电路板151背离所述第一基板电极1一侧的第二栅极电路板152;部分功率半导体芯片2的栅极通过所述键合引线14和所述导电柱13与所述第一栅极电路板151电连接,部分功率半导体芯片2的栅极通过所述键合引线14和

所述导电柱13与所述第二栅极电路板152电连接;所述第一栅极电路板151中的第三互联线153与第二栅极电路板152中的第四互联线154在第一基板电极1表面的投影至少部分重合,对于在第一基板电极1表面的投影重合的第三互连线153和第四互连线154,第三互连线153中的电流方向与第四互连线154中的电流方向相反,所述第三互连线153中的电流方向与第四互连线154中的电流方向相反,可以消除部分栅极回路因功率半导体芯片封装结构产生的寄生电感,降低测试时栅极电压过冲与震荡现象。

89.所述第三互连线153和第四互连线154朝向所述第一基板电极1。在一个实施例中,所述栅极电路板15还包括第二绝缘垫板155,参考图9,所述第二绝缘垫板155位于所述第一栅极电路板151与所述第二栅极电路板152之间。

90.在一个实施例中,所述栅极电路板15中具有贯穿所述栅极电路板15的第一孔,所述第一孔位于所述功率半导体芯片2的发射极的上方。辅助发射极电路板11中具有贯穿所述辅助发射极电路板11的第二孔,所述第二孔至少与部分所述第一孔连通。

91.所述第一子导电连接部7贯穿所述第一孔和所述第二孔且与所述第二基板电极10电连接。

92.所述功率半导体芯片2上的第一子导电连接部7贯穿所述第一孔和所述第二孔与所述第二基板电极10电连接,部分所述功率半导体芯片2上的所述第二子导电连接部8贯穿所述第一孔和所述第二孔与所述第二辅助发射极电路板112上的第二互联线114电连接;部分所述功率半导体芯片2上的所述第二子导电连接部8贯穿所述第一孔和所述第一辅助发射极电路板111的第二孔与所述第一辅助发射极电路板111上的第一互联线113电连接。

93.为了方便说明,将若干导电柱分为第一导电柱和第二导电柱。

94.部分功率半导体芯片2的栅极202通过所述键合引线14和第一导电柱与所述第一栅极电路板151上的第三互联线153电连接,所述第一导电柱未贯穿第一栅极电路板151;部分功率半导体芯片2的栅极202通过所述键合引线14和第二导电柱与所述第二栅极电路板152上的第四互联线154电连接,所述第二导电柱贯穿所述第一栅极电路板151且与第一栅极电路板151电绝缘。

95.所述第二子导电连接部8贯穿第一孔且与辅助发射极电路板11连接。

96.在一个实施例中,所述第一栅极电路板151与所述第二栅极电路板152利用所述功率半导体芯片2的栅极开孔位置通过通孔电气连接。

97.在一个实施例中,所述功率半导体芯片封装结构还包括:管壳17,参考图10,所述管壳17包围所述第一基板电极1与所述第二基板电极10。

98.在一个实施例中,所述管壳17的材料为高绝缘强度、耐高温的材料。

99.在一个实施例中,所述功率半导体芯片封装结构还包括:绝缘灌封材料,所述绝缘灌封材料包括硅凝胶和环氧胶;在其他实施例中,所述绝缘灌封材料还可以包括其他绝缘材料。

100.本发明提供的功率半导体芯片封装结构中的导电连接件6中的第一微孔73与第二微孔83、所述功率半导体芯片封装结构中的绝缘灌封材料及烧结工艺技术相结合,在保证所述功率半导体芯片封装结构通流能力的同时,可以释放所述功率半导体芯片2表面机械应力,使所述第一基板电极1与所述第二基板电极10之间具备一定的弹性,在提高功率半导体芯片封装结构的可靠性的同时还可以降低驱动回路对功率回路的影响。

101.在一个实施例中,绝缘灌封材料的包围所述导电连接件6。

102.参考图11,图11为所述功率半导体芯片封装结构的平剖面图。

103.显然,上述实施例仅仅是为清楚地说明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引伸出的显而易见的变化或变动仍处于本发明创造的保护范围之中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。