1.本发明涉及半导体器件领域,尤其涉及一种阻变式随机存取存储器(rram)及其制造方法。

背景技术:

2.阻变式随机存取存储器的基本结构包括顶电极、阻变层和底电极,通常使用自底而上逐层叠加的三明治结构,通常情况下,由于电极和阻变层接触面积过大使得导电细丝分布更加随机化,不利于器件的一致性。

3.此外,在对三明治结构进行刻蚀时,还会使阻变层的侧壁产生损伤,从而影响阻变层的性能。

4.如果是通过通孔(via)连接三明治结构的阻变式随机存取存储器,还会因为通孔材料支撑处产生凹陷,而导致阻变层不平坦,也会影响到阻变层的性能。

技术实现要素:

5.针对上述技术问题,本发明人创造性地提供了一种半导体集成电路器件及其制备方法。

6.根据本发明实施例的第一方面,提供一种半导体集成电路器件,该半导体集成电路器件包括:阻变层,为开口向上的沟槽状结构;位于阻变层外侧的第一电极,和位于阻变层内侧的第二电极,第一电极与第二电极在阻变层的侧壁两侧相对;阻变层、第一电极和第二电极形成第一存储单元。

7.根据本发明实施例一实施方式,该半导体集成电路器件还包括:位于第一电极下方的通孔;通过通孔与第一电极连接的第一金属层;与第二电极连接的第二金属层。

8.根据本发明实施例一实施方式,该半导体集成电路器件还包括:与第一存储单元具有相同结构的第二存储单元,第二存储单元的第一电极通过下方的通孔与第一金属层连接,第二存储单元的第二电极与第二金属层连接,第一存储单元和第二存储单元之间隔断。

9.根据本发明实施例一实施方式,该半导体集成电路器件还包括:与第一存储单元具有相同结构的第三存储单元,第三存储单元的第一电极通过下方的通孔与第一金属层连接。

10.根据本发明实施例一实施方式,第三存储单元的第二电极通过上方的第二金属层以及通孔与第三金属层连接,形成1t2r结构。

11.根据本发明实施例的第二方面,提供一种半导体集成电路器件的制造方法,该方法包括:在衬底上形成第一电极,衬底包括与第一金属层连接的第一通孔;在第一电极之上,与第一通孔错开的位置处刻槽,在槽内形成阻变层,使得该阻变层为开口向上的沟槽状结构;在阻变层的开口内形成第二电极得到第一存储单元。

12.根据本发明实施例一实施方式,该制造方法还包括:在第二电极之上形成第二金属层,使第二金属层与第一存储单元的第二电极连接。

13.根据本发明实施例一实施方式,该制造方法还包括:在制造第一存储单元的同时,制造第二存储单元,使得第二存储单元的第一电极通过下方的通孔与第一金属层连接,第二存储单元的第二电极与第二金属层连接;在第一存储单元和第二存储单元之间形成隔断。

14.根据本发明实施例一实施方式,该制造方法还包括:在制造第一存储单元的同时,制造第三存储单元,使得第三存储单元的第一电极通过下方的通孔与第一金属层连接。

15.根据本发明实施例一实施方式,该制造方法还包括:在第三存储单元的第二电极的上方形成通孔和第三金属层,使得第三存储单元的第二电极通过上方的第二金属层以及通孔与第三金属层连接,形成1t2r结构。

16.本发明公开了一种半导体集成电路器件及其制造方法,该半导体集成电路器件所采取的结构为第一电极在阻变层的侧壁和阻变层连接,并通过第二电极从阻变层内侧的接出。从而在施加电压后会在阻变层的侧壁形成导电细丝。如此,可以通过减小第一电极的高度减小阻变发生区域,这使得在电操作过程中电场更加集中的施加在阻变层上,从而改善器件的均一性。此外,由于阻变区域位于阻变层的侧壁,是沉积形成的,未经过刻蚀,也不存在因为刻蚀而产生的损伤;同时,阻变区域位于阻变层的侧壁也可避免因为通孔凹陷导致的阻变层不平坦的问题,因此可以使得阻变层的性能更好,使用寿命更长。

17.需要理解的是,本发明实施例的实施并不需要实现上面的全部有益效果,而是特定的技术方案可以实现特定的技术效果,并且本发明实施例的其他实施方式还能够实现上面未提到的有益效果。

附图说明

18.通过参考附图阅读下文的详细描述,本发明示例性实施方式的上述以及其他目的、特征和优点将变得易于理解。在附图中,以示例性而非限制性的方式示出了本发明的若干实施方式,其中:

19.在附图中,相同或对应的标号表示相同或对应的部分。

20.图1示出了本发明半导体集成电路器件一实施例的结构剖面示意图;

21.图2示出了图1所示实施例的俯视面示意图;

22.图3示出了本发明半导体集成电路器件另一实施例的结构剖面示意图;

23.图4示出了图3所示实施例的俯视面示意图;

24.图5示出了本发明半导体集成电路器件另一实施例的结构剖面示意图;

25.图6示出了图5所示实施例的俯视面示意图;

26.图7示出了本发明半导体集成电路器件的制造方法的流程示意图;

27.图8示出了本发明图1所示实施例的制造过程示意图;

28.图9示出了本发明图1所示实施例的制造过程中某一阶段的结构剖面示意图;

29.图10示出了本发明图1所示实施例的制造过程中某一阶段的结构剖面示意图;

30.图11示出了本发明图1所示实施例的制造过程中某一阶段的结构剖面示意图;

31.图12示出了本发明图1所示实施例的制造过程中某一阶段的结构剖面示意图;

32.图13示出了本发明图1所示实施例的制造过程中某一阶段的结构剖面示意图;

33.图14示出了本发明图1所示实施例的制造过程中某一阶段的结构剖面示意图;

34.图15示出了本发明图3或图5所示实施例的制造过程示意图;

35.图16示出了本发明图3或图5所示实施例的制造过程中某一阶段的结构剖面示意图;

36.图17示出了本发明图3或图5所示实施例的制造过程中某一阶段的结构剖面示意图;

37.图18示出了本发明图3或图5所示实施例的制造过程中某一阶段的结构剖面示意图;

38.图19示出了本发明图3或图5所示实施例的制造过程中某一阶段的结构剖面示意图;

39.图20示出了本发明图3或图5所示实施例的制造过程中某一阶段的结构剖面示意图。

具体实施方式

40.为使本发明的目的、特征、优点能够更加的明显和易懂,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而非全部实施例。基于本发明中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

41.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

42.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或隐含地包括至少一个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

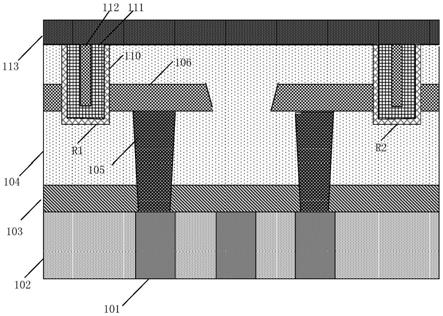

43.图1示出了本发明半导体集成电路器件一实施例的结构剖面示意图。如图1所述,该半导体集成电路器件包括:阻变层110,为开口向上的沟槽状结构;位于阻变层外侧的第一电极106,和位于阻变层内侧的第二电极112,第一电极106与第二电极112在阻变层110的侧壁两侧相对;阻变层110、第一电极106和第二电极112形成第一存储单元。

44.其中,阻变层110可以是阻变材料中的一种或多种制备而成的。常用的阻变材料包括:氧化铝(al

x

oy)、氧化铜(cu

x

oy)、氧化铪(hf

x

oy)等过渡金属氧化物(tmo)。

45.第一电极106和第二电极112可以是电极材料中的一种或多种制备而成。常用的电极材料包括铝(al)、铜(cu)、金(au)、铂金(pt)、钽(ta)、氮化钽(tan)、钛(ti)、氮化钛(tin)、钨(w)和氮化钨(wn)等。

46.在本实施例半导体集成电路器件中,阻变层110和第二电极112之间还会设置有一个储氧层111(oxygen ion reservoir,oir),以在施加电压时吸引或储备更多的氧。储氧层111的材料主要包括钛(ti)和钽(ta)等。储氧层是使得存储单元性能更好的增益结构,并非

存储单元必需的结构,实施者可根据需要选择设置或不设置。

47.如图1所示,在本实施例半导体集成电路器件所采取的结构使得第一电极106与第二电极112在阻变层110的侧壁两侧相对,只要使第一电极106和第二电极112分别与不同电极的电路相连,在施加电压后,即可在阻变层110的侧壁形成电场,并在电压达到形成电压时形成导电细丝得到阻变区域。

48.如此,可以通过减小第一电极106的高度减小阻变发生区域,这使得在电操作过程中电场更加集中的施加在阻变层上,从而改善器件的均一性。

49.此外,由于阻变区域位于阻变层110的侧壁,是沉积形成的,未经过刻蚀,也不存在因为刻蚀而产生的损伤;而且,阻变区域位于阻变层110的侧壁还可避免因为通孔凹陷导致的阻变层不平坦的问题,因此可以使得阻变层110的性能更好,使用寿命更长。

50.本实施例半导体集成电路器件,还包括:位于第一电极106下方的通孔105,通过通孔105与第一电极106连接的第一金属层101;与第二电极112连接的第二金属层113。

51.其中,第一金属层101和第二金属层113分别与半导体基础电路器件中的电路相连,以在施加电压后,即可在阻变层110的侧壁形成阻变区域。

52.理论上,只要具有了上述结构的存储单元,无论使用哪种接线方式,只要使第一电极和第二电极分别与不同电极的电路相连即可。但使用本实施例图1所示的上述由通孔105、第一金属层101和第二金属层113所形成的连线结构,可使半导体集成电路器件的结构更为紧凑,平面面积更小。

53.此外,本实施例半导体集成电路器件包括多个存储单元。图1仅示出了其中的两个存储单元,其中,左侧所示的存储单元为第一存储单元r1,右侧所示的另一存储单元为第二存储单元r2,第二存储单元r2与第一存储单元r1具有相同的结构,其第一电极也通过下方的通孔与第一金属层101连接,第二电极也与第二金属113层连接,但第一存储单元r1和第二存储单元r2之间隔断。

54.图2示出了本实施例半导体集成电路器件中第一存储单元r1和第二存储单元r2的俯视示意图(top view)。如图2所示,第二金属层113主要设置于第一存储单元r1和第二存储单元r2的正上方,并分别与第一存储单元r1和第二存储单元r2相连。

55.另外,本实施例半导体集成电路器件还包括一些常用的其他组成部分,例如绝缘层104,位于衬底102之上的电介质层103等。这些部分均为示例性的,并非对本技术半导体集成电路器件的限定,实施者可根据实施需要和实施条件,使用任何适用的布局和设计。

56.图3示出了本发明半导体集成电路器件另一实施例的结构剖面示意图。

57.在图3所示的实施例半导体集成电路器件中,包括以下与图1所示的实施例类似的结构:由开口向上的沟槽状结构的阻变层211、位于所述阻变层211外侧的第一电极206和位于阻变层211内侧的第二电极213及储氧层212所形成的第一存储单元r1,与第一存储单元r1结构相同的第二单元r2。

58.其中,第一存储单元r1和第二存储单元r2的第一电极(例如,第一电极206)均通过下方通孔(例如,通孔205)与第一金属层(例如第一金属层201)连接,第一存储单元r1和第二存储单元r2的第二电极(例如,第二电极213)均与第二金属层(例如,第二金属层214)连接。

59.与图1所示的实施例类似,图3所示的实施例中,也包括一些常用的其他组成部分,

例如绝缘层204和绝缘层207,位于衬底202之上的电介质层203等。

60.除此之外,图3所示的实施例半导体集成电路器件还包括:与第一存储单元r1具有相同结构的第三存储单元r3,第三存储单元r3的第一电极通过下方的通孔205与第一金属层201连接。其中,虽然位于第一存储单元r1和第二存储单元r2之间的第三存储单元r3之上也设置有第二金属层214,但第三存储单元r3之上的第二金属层214为四周隔断的金属块,并未与任何电路连接。因此,在向连接有电路的第二金属层214施加电压时,第三存储单元r3并不通电。

61.图4示出了图3所示的实施例半导体集成电路器件的俯视示意图。如图4所示,第一存储单元r1、第二存储单元r2以及第三存储单元r3均与第二金属层214相连。不同的是,第一存储单元r1和第二存储单元r2的第二金属层214会连接在一起,且第二金属层214为第一存储单元r1和第二存储单元r2的位线。第三存储单元r3上的第二金属214为四周隔断的金属块,不会由第二金属层接出。

62.在图3所示的实施例与图1所示的实施例相比,其结构更为均衡,特别是在进行磨平时,受力更为均匀,因此制造得到的半导体集成电路器件的质量也更高。同时,r3的存在也使得只需要改变215/216的光罩即可用同一套模具(mask)上做出1t1r以及1t2r,方便根据实际需要进行调整。

63.图5示出了本发明半导体集成电路器件另一实施例的结构剖面示意图。

64.图5所示的实施例半导体集成电路器件在图3所示的实施例半导体集成电路器件的基础上,还使得第三存储单元r3的第二电极通过上方的通孔215与第三金属层216连接,形成1t2r结构。

65.图6示出了图5所示的实施例半导体集成电路器件的俯视示意图。如图6所示,第一存储单元r1和第二存储单元r2均由第二金属层214接出,第三存储单元r3并不由第二金属层214接出,而是通过第二金属层作为连接支架(landing pad),在第二金属层之上形成通孔于第三金属层216连接,并由第三金属层216接出。

66.如此,第一存储单元r1和第三存储单元r3通过第一电极206下方的通孔205共同连接到第一金属层201,该第一金属层201可通过同一根源线连接同一个晶体管;而由于第一存储单元r1的第二电极与第二金属层214连接,第二金属层214连接有第一位线;第三存储单元r3的第二电极与第三金属层216连接,而第三金属层216连接有第二位线。如此,第一存储单元r1和第三存储单元r3就形成两个可分别独立控制的阻变式存储器。第一位线可独立控制第一存储单元r1,而第二位线可独立控制第三存储单元r3,从而实现了一个晶体管连两个阻变式存储器(1t2r)结构。

67.此外,1t2r结构通过在垂直方向不同高度上堆叠更多的阻变式存储器,可在不增加平面面积的前提下,进一步提高存储容量,满足日益提高的微缩化需求。

68.进一步地,本发明还提供一种半导体集成电路器件的制造方法,如图7所示,该方法包括:操作s710,在衬底上形成第一电极,衬底包括与第一金属层连接的第一通孔;操作s720,在第一电极之上,与第一通孔错开的位置处刻槽,在槽内形成阻变层,使得该阻变层为开口向上的沟槽状结构;操作s730,在阻变层的开口内形成第二电极得到第一存储单元。

69.在操作s710中,衬底指还包含有通孔的介电层,以及与第一金属层连接的电路等。在衬底上形成第一电极,通常使用沉积电极材料,然后进行图案化,形成多个隔离的存储单

元。其中,电极材料可使用任意适用的电极材料,而沉积工艺也可使用任何适用的沉积工艺,例如,物理气相沉积法、化学气相沉积法或原子沉积法等。

70.在操作s720中,在与第一通孔错开的位置处刻槽,在槽内形成阻变层,可使第一电极位于阻变层的外侧,且通过在槽内沉积阻变层材料,可形成开口向上的沟槽状结构。其中,阻变层材料可使用任何适用的现有材料,而沉积工艺也可使用任何适用的沉积工艺,例如,物理气相沉积法、化学气相沉积法或原子沉积法等。

71.之后,再通过操作s730在开口内沉积电极材料就可以得到位于阻变层内侧的第二电极。如此,即可得到第一电极和第二电极分别位于阻变层侧壁两侧的存储单元。

72.需要说明的是,上述步骤仅为制造本发明实施例半导体集成电路器件的主要步骤,而不是全部步骤。在制造半导体集成电路器件的过程中,还可能会依据半导体集成电路器件的产品设计,包括沉积阻氧层、沉积储氧层以及形成其他结构的步骤等。其中,沉积工艺可根据具体实施情况选择任何使用的沉积工艺,例如,物理气相沉积、化学气相沉积或原子沉积等。

73.根据本发明实施例一实施方式,该制造方法还包括:在第二电极之上形成第二金属层,使第二金属层与第一存储单元的第二电极连接。

74.根据本发明实施例一实施方式,该制造方法还包括:在制造第一存储单元的同时,制造第二存储单元,使得第二存储单元的第一电极通过下方的通孔与第一金属层连接,第二存储单元的第二电极与第二金属层连接;在第一存储单元和第二存储单元之间形成隔断。

75.根据本发明实施例一实施方式,该制造方法还包括:在制造第一存储单元的同时,制造第三存储单元,使得第三存储单元的第一电极通过下方的通孔与第一金属层连接。

76.根据本发明实施例一实施方式,该制造方法还包括:在第三存储单元的第二电极的上方形成通孔和第三金属层,使得第三存储单元的第二电极通过上方的通孔与第三金属层连接,形成1t2r结构。

77.图8示出了制造图1所示的半导体集成电路器件的主要过程,包括:

78.步骤s810,在衬底102上沉积第一电极材料形成第一电极层106,得到如图9所示的结构;

79.其中,衬底102上包括介电层103,第一金属层101,绝缘层104和与第一金属层101连接的通孔105。

80.步骤s820,对第一电极层106进行图案化处理,得到图10所示的结构;

81.其中,图案化处理主要指根据设计的布局或图案在存储单元之间形成隔断107。

82.形成隔断107的工艺可使用先光刻再蚀刻的工艺。

83.步骤s830,在第一电极层之上沉积绝缘材料,并将隔断107填平,得到如图11所示的结构;

84.步骤s840,在第一电极之上,与第一通孔错开的位置处刻槽形成向上开口的槽108和槽109,得到如图12所示的结构;

85.其中,刻槽的工艺为先光刻再蚀刻。

86.步骤s850,在槽108和槽109内依次沉积阻变层材料110、储氧层材料111和第二电极材料112,得到如图13所示的结构;

87.其中,沉积阻变层材料时可使用原子沉积工艺,阻变层材料可使用氧化铝(al

x

oy)、氧化铜(cu

x

oy)、氧化铪(hf

x

oy)等过渡金属氧化物(tmo)。

88.步骤s860,使用磨平工艺去除阻变层110水平方向的顶部部分,得到如图14所示的结构;

89.其中,磨平工艺可使用化学机械抛光工艺(cmp)。

90.步骤s870,沉积第二金属层113,即可得到图1所示的半导体集成电路器件。

91.图15示出了制造图3或图5所示的半导体集成电路器件的主要过程,包括:

92.步骤s1510,在衬底202上沉积第一电极材料形成第一电极层206,得到如图16所示的结构;

93.其中,衬底202上包括介电层203,第一金属层201,绝缘层204和与第一金属层201连接的通孔205。

94.其中,沉积工艺可使用气相沉积工艺,第一电极材料可使用任意适用的电极材料,例如,铝(al)、铜(cu)、金(au)、铂金(pt)、钽(ta)、氮化钽(tan)、钛(ti)、氮化钛(tin)、钨(w)和氮化钨(wn)等。

95.步骤s1520,在第一电极层206之上沉积绝缘材料207,得到如图17所示的结构;

96.步骤s1530,在第一电极之上,与第一通孔错开的位置处刻槽形成向上开口的槽208、槽209和槽210,得到如图12所示的结构;

97.步骤s1540,在槽208、槽209和槽210依次沉积阻变层材料211、储氧层材料212和第二电极材料213,得到如图19所示的结构;

98.步骤s1550,使用磨平工艺去除阻变层211水平方向的顶部部分,得到如图20所示的结构;

99.步骤s1560,在第一存储单元r1、第二存储单元r2和第三存储单元r3之上制造如图4所示的第二金属层214,即可得到图3所示的半导体集成电路器件;

100.其中,包括沉积绝缘层材料207,在图4所示的第二金属层214处的位置刻槽,在槽内沉积第二金属层材料即可。

101.在此基础上,如果继续以下步骤:

102.步骤s1570,在第三存储单元r3上的第二金属层之上制造通孔215,并在通孔之上制造如图6所示的第三金属层216,则可得到图5所示的半导体集成电路器件。

103.其中,包括:沉积绝缘层材料207,在图6所示的通孔215处刻孔;沉积通孔材料得到通孔215;继续沉积绝缘层材料207,在图6所示的第三金属层216处的位置刻槽,在槽内沉积第三金属层材料即可。

104.需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

105.在本技术所提供的几个实施例中,应该理解到,所揭露的器件和方法,可以通过其它的方式实现。以上所描述的器件实施例仅仅是示意性的,例如,单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,如:多个单元或组件可以结合,或可以

集成到另一个装置,或一些特征可以忽略,或不执行。另外,所显示或讨论的各组成部分相互之间的耦合、或直接耦合、或通信连接可以是通过一些接口,设备或单元的间接耦合或通信连接,可以是电性的、机械的或其它形式的。

106.以上,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。