1.本发明涉及半导体集成电路制造领域,特别是涉及一种沟槽功率半导体器件。

背景技术:

2.目前,功率半导体器件在日常生活、生产等领域的应用越来越广泛,特别是功率金属氧化物半导体场效应晶体管,由于它们拥有较快的开关速度、较小的驱动电流、较宽的安全工作区,因此受到了众多研究者们的青睐。如今,功率半导体器件正向提高工作电压、增大工作电流、减小导通电阻和集成化的方向快速发展。

3.功率mosfet是多子导电器件,具有开关速度快、输入阻抗高、易驱动等优点。传统的双扩散mosfet采用双扩散技术形成体区,因此元胞宽度大,同时由于其内部jfet(结型场效应晶体管)区的存在,使得其导通电阻较大。而槽栅mosfet的栅极沟槽处于体区,并深入漂移区,导电沟道为纵向沟道,因此可以提高元胞密度和消除jfet区电阻,所以其导通电阻更小,但导通电阻仍然在“硅极限”以上。

4.为进一步提升功率mosfet的性能,sgt(shield-gate trench)结构被提出。sgt结构是在常规的槽栅内引入新电极,由于屏蔽栅的存在,结构具有电荷耦合效应,在传统沟槽mosfet垂直耗尽的基础上引入了水平耗尽,能对器件漂移区的载流子进行辅助耗尽。同时,sgt结构可减小栅电极与漏电极交叠引起的弥勒电容与栅电荷。

5.虽然现有的sgt结构能很好实现导通损耗和驱动损耗的折中,但由于屏蔽栅的引入,sgt结构存在着与时间相关的雪崩击穿的不稳定性,这已经严重影响了sgt器件的可靠性。具体的,在sgt器件中存在寄生二极管,该寄生二极管是正向阻断,反向容易导通。在大电感条件下快速开关应用时,器件的寄生二极管反向恢复电流(irr)下降期间易发生动态雪崩,击穿点多指向器件的元胞区与终端区的过渡区、元胞区与栅极焊垫(gate pad)过渡区等单位面积源极孔(source孔)较少的地方,这是带有终端的需要承受电压的器件难以消除的弱点。

技术实现要素:

6.本发明的目的在于提供一种沟槽功率半导体器件,减少器件寄生二极管反向恢复期间的动态雪崩,提高器件在大电感条件下和快速开关情况下的应用能力。

7.本发明提供一种沟槽功率半导体器件,包括:元胞区及环绕所述元胞区设置的终端区,所述元胞区和所述终端区位于基于第一导电类型衬底生长的第一导电类型外延层内,所述第一导电类型衬底异于所述第一导电类型外延层一面连接漏极金属, 所述第一导电类型外延层上依次形成有层间介质层及源极金属,所述层间介质层中设置有与所述源极金属连接的第一导电类型多晶硅层,所述终端区靠近所述层间介质层的一侧设置有第二导电类型阱区,所述第一导电类型多晶硅层和所述第二导电类型阱区通过一第二导电类型多晶硅层连接;所述源极金属连接所述第一导电类型多晶硅层,所述第一导电类型多晶硅层与第

二导电类型多晶硅层形成第一二极管dn,所述第二导电类型多晶硅层连接所述第二导电类型阱区,所述第二导电类型阱区与所述第一导电类型外延层形成第二二极管di,所述第一导电类型外延层通过所述第一导电类型衬底连接所述漏极金属,以在所述源极金属与所述漏极金属之间增加由所述第一二极管dn和所述第二二极管di反向串联的支路。

8.可选的,所述层间介质层中设置至少两个沿所述第一导电类型衬底的表面方向延伸的第一导电类型多晶硅层,所述终端区靠近所述层间介质层的一侧相应设置至少两个沿所述第一导电类型衬底的表面方向延伸的第二导电类型阱区,所述第二导电类型多晶硅层包括相互连接的水平连接部和竖直连接部,所述水平连接部位于相邻所述第一导电类型多晶硅层之间,所述竖直连接部从所述层间介质层伸入所述终端区连接相邻所述第二导电类型阱区。

9.可选的,相邻所述第二导电类型阱区之间设置有浅沟槽隔离结构,所述竖直连接部至少部分伸入所述浅沟槽隔离结构,以连接相邻所述第二导电类型阱区。

10.可选的,所述元胞区内设置有第一沟槽,所述第一沟槽内设置有与所述源极金属连接的源极多晶硅,所述第一沟槽的顶部两侧设置有第二类型体区及位于所述第二类型体区内的第一类型掺杂区,所述第二类型体区与所述源极金属连接。

11.可选的,所述第一沟槽内还设置有栅极多晶硅,所述栅极多晶硅和所述源极多晶硅之间通过栅介质层绝缘。

12.可选的,所述栅极多晶硅和所述源极多晶硅之间为上下结构,或者所述栅极多晶硅和所述源极多晶硅之间为左右结构。

13.可选的,所述终端区设置有第二沟槽,所述第二沟槽内设置有浮动多晶硅。

14.可选的,所述第一二极管dn和所述第二二极管di对应设置在所述终端区的终端结位置,和/或所述第一二极管dn和所述第二二极管di对应设置在所述终端区台面位置。

15.可选的,所述第一二极管dn和所述第二二极管di对应设置在相邻所述第二沟槽之间的台面位置。

16.可选的,所述第二二极管所在终端区的静态耐压大于所述元胞区的静态耐压,所述第二二极管所在终端区的静态耐压小于所述第二沟槽所在终端区的静态耐压。

17.可选的,对于n型沟槽功率半导体器件,第一导电类型为n型导电,第二导电类型为p型导电;对于p型沟槽功率半导体器件,第一导电类型为p型导电,第二导电类型为n型导电。

18.综上,本发明提供一种沟槽功率半导体器件,在器件终端区深沟槽的终端结位置和/或台面(mesa)位置对应形成第一二极管和第二二极管,以在源极金属与漏极金属之间增加由所述第一二极管和所述第二二极管反向串联的支路。在器件寄生二极管正向导通时,第一二极管不导通;寄生二极管反向恢复期间过剩空穴累积量超过一定程度,反向串联的支路中第二二极管耗尽穿通,第一二极管导通,即在终端区增加了若干个高效且几乎无不利影响的空穴抽取路径,大幅度减少了元胞区和终端区之间的过渡区附近过剩空穴累积量,降低了电场峰值,使动态雪崩薄弱点得以加固而可靠,大幅度提高了器件在大电感条件下和快速开关情况下的应用能力。

附图说明

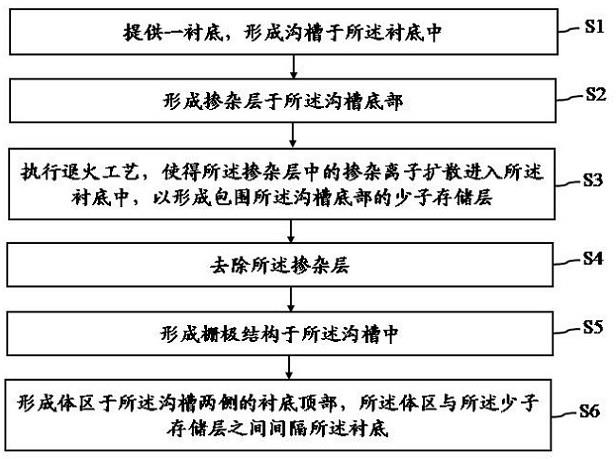

19.图1为一沟槽功率半导体器件的结构示意图;图2为本发明一实施例提供的沟槽功率半导体器件的结构示意图;图3为本发明一实施例提供的沟槽功率半导体器件区域划分的结构示意图;图4为本发明一实施例提供的沟槽功率半导体器件的电流路径示意图;图5为本发明一实施例提供的沟槽功率半导体器件的另一电流路径示意图。

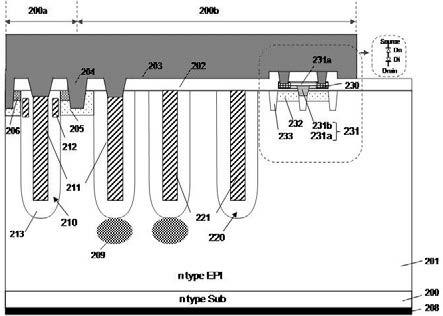

20.其中,附图标记为:100、200-n型衬底;100a、200a-元胞区;200b、200b-终端区;110、210-第一沟槽;111、211-源极多晶硅;112、212-栅极多晶硅;101、201-n型外延层;103、203-源极金属;105、205-p型体区;106、206-n型掺杂区;213-栅介质层;202-层间介质层;204-金属接触通孔;208-漏极金属;220-第二沟槽;209-场限环;221-浮动多晶硅;230-n型多晶硅层;231-p型多晶硅层;231a-水平连接部;231b-竖直连接部;232-p型阱区;233-浅沟槽隔离结构;300-过剩空穴;dn-第一二极管;di-第二二极管。

具体实施方式

21.图1为一沟槽功率半导体器件的结构示意图,如图1所示,所述沟槽功率半导体器件包括元胞区(cell)100a和环绕所述元胞区200a设置的终端区(terminal)100b,所述元胞区100a和所述终端区100b位于基于n型衬底(n type sub)100生长的n型外延层(n type epi)101内,元胞区(cell)100a中形成有第一沟槽110,所述第一沟槽110内形成有源极多晶硅111和栅极多晶硅112,所述第一沟槽110两侧的p-body区105、n型外延层101和n型掺杂区106形成的寄生二极管,如图1所示。当在外围电路应用出现反向偏压的情况,即源极金属103接高电位,漏极金属108接低电位,栅极多晶硅112接低电位时,这个寄生二极管就会开始工作,实现正向导通。沟槽功率半导体器件反向恢复过程实质是寄生二极管的关断过程,当寄生二极管从正向导通状态向反向截止状态过渡时,需要首先释放存储在外延层(漂移区)中的剩余载流子(qrr),这个过程需要一段时间称为放电时间也即反向恢复时间(trr),在此期间电流反向流过寄生二极管,空穴在高压电场作用下,被排斥到p-body区105,最后从源极处流出,电子在高压电场作用下,被吸引到n型衬底100,最后从漏极流出,这个过程直到漂移区中的空穴被抽取完全为止。

22.然而,在大电感条件下寄生体二极管反向恢复电流(irr)下降期间易发生了动态雪崩,寄生二极管正向导通期间所注入的大量空穴在元胞区与终端区的过渡区有存储,反向恢复期间在过渡区附近的抽取路径(source孔)相比于空穴存储量是过少的,元胞区基本抽取完毕时过渡区附近仍有大量的过剩空穴,由于器件设计耐压基本上是按最佳杂质浓度设计的,这样此时的耐压是元胞区明显高于过渡区附近, 元胞区与终端区的过渡区附近就成了耐压的薄弱点而先于元胞区击穿,从而容易发生雪崩。

23.因此,在大电感条件下快速开关应用时寄生体二极管反向恢复电流(irr)下降期间发生的动态雪崩,击穿点多指向元胞区与终端区的过渡区、 元胞区与栅极焊垫(gate pad)过渡区等单位面积source孔较少的地方,这是带有终端的需要承受电压的器件难以消除的弱点。为解决上述问题,本发明提供一种沟槽功率半导体器件,在器件终端区深沟槽的

终端结位置和/或台面(mesa)位置对应形成第一二极管和第二二极管,以在源极金属与漏极金属之间增加由所述第一二极管和所述第二二极管反向串联的支路。在器件寄生二极管正向导通时,第一二极管不导通;寄生二极管反向恢复期间过剩空穴累积量超过一定程度,反向串联的支路中第二二极管耗尽穿通,第一二极管导通,即在终端区增加了若干个高效且几乎无不利影响的空穴抽取路径,大幅度减少了元胞区和终端区之间的过渡区附近过剩空穴累积量,降低了电场峰值,使动态雪崩薄弱点得以加固而可靠,大幅度提高了器件在大电感条件下和快速开关情况下的应用能力。

24.以下结合附图和具体实施例对本发明的沟槽功率半导体器件作进一步详细说明。根据下面的说明和附图,本发明的优点和特征将更清楚,然而,需说明的是,本发明技术方案的构思可按照多种不同的形式实施,并不局限于在此阐述的特定实施例。附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

25.在说明书中的术语“第一”“第二”等用于在类似要素之间进行区分,且未必是用于描述特定次序或时间顺序。要理解,在适当情况下,如此使用的这些术语可替换,例如可使得本文所述的本发明实施例能够以不同于本文所述的或所示的其他顺序来操作。类似的,如果本文所述的方法包括一系列步骤,且本文所呈现的这些步骤的顺序并非必须是可执行这些步骤的唯一顺序,且一些所述的步骤可被省略和/或一些本文未描述的其他步骤可被添加到该方法。若某附图中的构件与其他附图中的构件相同,虽然在所有附图中都可轻易辨认出这些构件,但为了使附图的说明更为清楚,本说明书不会将所有相同构件的标号标于每一图中。

26.本实施例提供的一种沟槽功率半导体器件,所述沟槽功率半导体器件包括:元胞区及环绕所述元胞区设置的终端区,所述元胞区和所述终端区位于基于第一导电类型衬底生长的第一导电类型外延层内,所述第一导电类型衬底异于所述第一导电类型外延层一面连接漏极金属, 所述第一导电类型外延层上依次形成有层间介质层及源极金属,所述层间介质层中设置有与所述源极金属连接的第一导电类型多晶硅层,所述终端区靠近所述层间介质层的一侧设置有第二导电类型阱区,所述第一导电类型多晶硅层和所述第二导电类型阱区通过一第二导电类型多晶硅层连接;所述源极金属连接所述第一导电类型多晶硅层,所述第一导电类型多晶硅层与第二导电类型多晶硅层形成第一二极管dn,所述第二导电类型多晶硅层连接所述第二导电类型阱区,所述第二导电类型阱区与所述第一导电类型外延层形成第二二极管di,所述第一导电类型外延层通过所述第一导电类型衬底连接所述漏极金属,以在所述源极金属与所述漏极金属之间增加由所述第一二极管dn和所述第二二极管di反向串联的支路。

27.本实施例提供的沟槽功率半导体器件,在所述终端区深沟槽(trench)的终端结位置和/或台面(mesa)位置对应形成第一二极管dn和第二二极管di,以在所述源极金属与所述漏极金属之间增加由所述第一二极管dn和所述第二二极管di反向串联的支路。这样在寄生二极管正向导通时,dn不导通,当寄生二极管正向导通期间所注入的空穴累积量超过一定程度,di耗尽穿通,dn导通,即在终端区增加了若干个高效且几乎无不利影响的空穴抽取路径,大幅度减少了元胞区和终端区之间的过渡区附近过剩空穴累积量,降低了电场峰值,使动态雪崩薄弱点得以加固而可靠,大幅度提高了器件在大电感条件下和快速开关情况下的应用能力。

28.本实施例中,对于n型沟槽功率半导体器件,第一导电类型为n型导电,第二导电类型为p型导电;对于p型沟槽功率半导体器件,第一导电类型为p型导电,第二导电类型为n型导电。下面以n型沟槽功率半导体器件为例对本发明提供的沟槽功率半导体器件进行介绍。

29.图2为本实施例提供的沟槽功率半导体器件的结构示意图。如图2所示,所述沟槽功率半导体器件包括:元胞区(cell)200a及环绕所述元胞区200a设置的终端区(terminal)200b,所述元胞区200a和所述终端区200b位于基于n型衬底(n type sub)200生长的n型外延层(n type epi)201内,所述n型衬底200异于所述n型外延层201一面连接漏极金属208,所述n型外延层201上依次形成有层间介质层202及源极金属203。

30.本实施例中,所述元胞区200a内设置有第一沟槽210,所述第一沟槽210内形成有与所述源极金属203连接的源极多晶硅(source poly si)211,所述第一沟槽210的顶部两侧形成有p型体区(p-body)205及位于所述p型体区205内的n型掺杂区206,所述p型体区205 和所述n型掺杂区206与所述源极金属203连接。示例性的,所述源极多晶硅211、所述p型体区205和所述n型掺杂区206通过金属接触通孔204连接所述源极金属203。所述第一沟槽210内还形成有栅极多晶硅(gate poly si)212,所述栅极多晶硅212和所述源极多晶硅211之间通过栅介质层213绝缘。所述栅极多晶硅212和所述源极多晶硅211之间为上下结构,或者所述栅极多晶硅212和所述源极多晶硅211之间左右结构。本实施例中,图2仅示出了所述栅极多晶硅212和所述源极多晶硅211之间左右结构的情况。

31.本实施例中,所述终端区200b设置有第二沟槽220,所述第二沟槽220内设置有浮动多晶硅(floating poly si)221,所述第二沟槽220内形成有绝缘氧化层,以隔绝所述浮动多晶硅221与n型外延层201。所述第二沟槽220的底部设置有p型阱区(p type ring)充当场限环209。

32.继续参考图2所示,在终端区200b,所述层间介质层202中设置有与所述源极金属203连接的n 型多晶硅层230,所述n型外延层201靠近所述层间介质层202的一侧设置有p型阱区(p well)232,所述n 型多晶硅层230和所述p型阱区通过p型多晶硅层231连接。

33.具体的,所述层间介质层202中设置至少两个沿所述n型衬底200的方向延伸的n型多晶硅层230,所述n型外延层201靠近所述层间介质层202的一侧相应设置至少两个沿所述n型衬底200的方向延伸的p型阱区232,所述p型多晶硅层231包括相互连接的水平连接部231a和竖直连接部232b,所述水平连接部231a位于相邻所述n 型多晶硅层230之间,所述竖直连接部232b从所述层间介质层202伸入所述n型外延层201连接相邻所述p型阱区232。进一步的,相邻所述p型阱区232之间设置有浅沟槽隔离结构(shallow trench isolation,sti)233,所述p型多晶硅层231的竖直连接部232b至少部分伸入所述浅沟槽隔离结构233,以连接相邻所述p型阱区232。

34.如图2所示,所述源极金属203连接所述n型多晶硅层230,所述n型多晶硅层230与p型多晶硅层231形成第一二极管dn,所述p型多晶硅层231连接所述p型阱区232,所述p型阱区232与所述n型外延层201形成第二二极管di,所述n型外延层201通过所述n型衬底200连接所述漏极金属208,以在所述源极金属203与所述漏极金属208之间增加由所述第一二极管dn和所述第二二极管di反向串联的支路。

35.本实施例中,第一二极管dn和第二二极管di的整体结构紧凑,寄生电感小,利于高速开关的应用,且所述第二二极管di中p型阱区采用绝缘介质填充的浅沟槽隔离结构进行

隔离,减小了低速开关应用时第二二极管di对所加区域电场分布的影响,很大程度上抑制了对静态特性的折损。示例性的,可通过调节所述n型多晶硅层230与p型多晶硅层231的掺杂浓度来调节第一二极管dn的寄生电阻,从而调节通过第一二极管dn的电流;也可以单独设计第二二极管di,比如通过局部p 型注入改变第二二极管di处的n型外延层epi浓度,使其静态耐压不低于元胞区(cell)200a、不高于终端区(terminal)200b,保证了器件的静态耐压和漏电特性几乎不受影响。

36.如图3和图4所示,器件寄生二极管反向恢复期间,当过剩空穴300累积量较低时,静态耐压(bvdss)关系仍为元胞区(cell)低于第二二极管di 、第二二极管di低于终端区(terminal),即bvdss|cell 《 bvdss|di 《 bvdss|terminal,电流主要路径(箭头指示方向)仍为元胞区(cell),如图4所示,这个时期于本实施例提供的沟槽功率半导体器件与普通结构的沟槽功率半导体器件(如图1所示)无区别。

37.如图3和图5所示,器件寄生二极管反向恢复期间,当元胞区(cell)以外的区域相对于元胞区(cell)过剩空穴300累积量很高时(超过一设定程度),耐压关系(bvdss)将变为元胞区(cell)高于终端区(terminal)、终端区(terminal)高于第二二极管di,即bvdss|di 《 bvdss|terminal 《bvdss|cell。对于普通结构的沟槽功率半导体器件(如图1所示),电流将集中在元胞区(cell)与终端区(terminal)之间过渡区,诱发动态雪崩;而对于本实施例提供的沟槽功率半导体器件,其将开通电流受控的di-dn支路,抽取累积的过剩空穴300,改变电流主要路径(箭头指示方向),电流路径变为di-dn支路、元胞区(cell)与终端区(terminal)之间过渡区,与cell区,如图5所示。di-dn支路相当于在终端区增加的空穴抽取路径,过剩空穴300通过增加的抽取路径而减少,避免器件动态雪崩。通过di-dn支路抽取过剩空穴300直到过剩空穴300累积量减少到一设定程度后,所述第二二极管di恢复高耐压,关闭di-dn电流支路。

38.本实施例中,由漏极(drain)经第二二极管di到第一二极管dn再到源极(source)的电流所致热功率,通过第一二极管dn阻值控制,第一二极管dn阻值通过n型多晶硅层230与p型多晶硅层231的掺杂浓度来调节。其中,所述第二二极管di为利用静电释放(esd)原理或类似用途的穿通型二极管,通常情况下下,在安全工作区(safe operating area,soa)内电场较低,不会导致电压所引起的雪崩,且di-dn和esd器件一样,在soa内,电压、电流、功率、热损耗都受控,并不会引起器件和它们本身的损坏。

39.需要说明的是,所述第一二极管dn和所述第二二极管di反向串联的支路可以对应形成在所述终端区深沟槽(trench)的终端结位置和/或(mesa)台面位置。本示例中,所述第一二极管dn和所述第二二极管di反向串联的支路可以对应形成在所述终端区深沟槽(trench)的终端结位置,如图2所示。在本发明其他实施例中,所述第一二极管dn和所述第二二极管di反向串联的支路也可以对应形成在所述终端区台面(mesa)位置,示例性的,所述第一二极管dn和所述第二二极管di反向串联的支路可以对应设置在终端区200b第二沟槽220之间。且上述第二二极管di的静态耐压是指第二二极管di所在终端区的静态耐压,所述终端区的静态耐压是指第二沟槽220所在终端区的静态耐压,如图3中虚线框所示。

40.对于在所述源极金属203与所述漏极金属208之间增加由所述第一二极管dn和所述第二二极管di反向串联的支路,可以通过以下方式实现。以包含sgt(屏蔽栅沟槽型,shield gate trench)结构的mosfet器件为例,参考图2所示,首先,基于现有左右结构的

sgt工艺形成mosfet器件的主体结构;然后,在终端区n型外延层201对应位置增加一段sti工艺,制作第二二极管di,在mosfet器件终端区深沟槽(trench)的终端结位置和/或台面(mesa)位置对应的层间介质层203增加一段集成esd 二极管的工艺,制作第一二极管dn;接着,在mosfet器件终端区深沟槽(trench)的终端结位置和/或(mesa)台面位置的上方的源极金属203打孔,进行金属填充,使源极金属203与所述第一二极管dn串接,所述第一二极管dn与第二二极管di连接,所述第二二极管di通过n型衬底200连接漏极金属208,这样即可在所述源极金属203与所述漏极金属208之间增加由所述第一二极管dn和所述第二二极管di反向串联的支路。当然,在本发明其他实施例中也可以采用其他方法来实现所述第一二极管dn和所述第二二极管di反向串联的支路的制作,在此不作具体限制。

41.综上,本发明提供一种沟槽功率半导体器件,在器件终端区深沟槽的终端结位置和/或台面(mesa)位置对应形成第一二极管和第二二极管,以在源极金属与漏极金属之间增加由所述第一二极管和所述第二二极管反向串联的支路。在器件寄生二极管正向导通时,第一二极管不导通;寄生二极管反向恢复期间过剩空穴累积量超过一定程度,反向串联的支路中第二二极管耗尽穿通,第一二极管导通,即在终端区增加了若干个高效且几乎无不利影响的空穴抽取路径,大幅度减少了元胞区和终端区之间的过渡区附近过剩空穴累积量,降低了电场峰值,使动态雪崩薄弱点得以加固而可靠,大幅度提高了器件在大电感条件下和快速开关情况下的应用能力。

42.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。