1.本发明涉及半导体器件技术领域,特别涉及一种半导体器件及其制备方法。

背景技术:

2.通过改进工艺技术、电路设计、编程算法和制造工艺,将平面存储单元缩小到更小的尺寸。然而,随着存储单元的特征尺寸接近下限,平面工艺和制造技术变得具有挑战性且成本高昂。结果,针对平面存储单元的存储密度接近上限。

3.为了解决在平面存储单元中的密度限制,以及降低存储单元的开发成本,开发了三维存储器件。

技术实现要素:

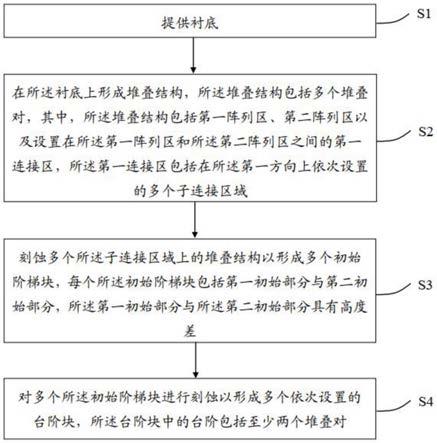

4.本发明提供一种半导体器件的制备方法,包括:提供衬底;在所述衬底上形成堆叠结构,所述堆叠结构包括多个堆叠对,其中,所述堆叠结构包括第一阵列区、第二阵列区以及设置在所述第一阵列区和所述第二阵列区之间的第一连接区,所述第一连接区包括在所述第一方向上依次设置的多个子连接区域;刻蚀多个所述子连接区域上的堆叠结构以形成多个初始阶梯块,每个所述初始阶梯块包括第一初始部分与第二初始部分,所述第一初始部分与所述第二初始部分具有高度差;对多个所述初始阶梯块进行刻蚀以形成多个依次设置的台阶块,所述台阶块中的台阶包括至少两个堆叠对。

5.其中,所述台阶块包括第一台阶部与第二台阶部,所述第一台阶部与所述第二台阶部相对设置,且所述第一台阶部中的台阶与所述第二台阶部中的台阶错位排布。

6.其中,在所述第一方向上,所述台阶块包括相邻的第一台阶块与第二台阶块,所述第二台阶块的起始台阶比所述第一台阶块的尾端台阶至少高一个堆叠对的高度。

7.其中,所述初始阶梯块的所述第一初始部分比所述第二初始部分高三个所述堆叠对的高度。

8.其中,“对多个所述初始阶梯块进行刻蚀以形成多个依次设置的台阶块”包括:以至少两个堆叠对的高度为刻蚀单元对多个所述初始阶梯块进行刻蚀以形成多个中间台阶块,所述初始阶梯块的第一初始部分刻蚀后形成所述中间台阶块的第一台阶部,所述初始阶梯块的第二初始部分刻蚀后形成所述中间台阶块的第二台阶部,所述中间台阶块的第一台阶部与所述第二台阶部相对设置,且所述中间台阶块的第一台阶部的台阶与第二台阶部的台阶错位排布,所述第一台阶部比所述第二台阶部高三个堆叠对的高度。

9.其中,所述第一连接区还包括第一顶栅区域和第二顶栅区域,多个所述子连接区域在所述第一方向上连接在所述第一顶栅区域和所述第二顶栅区域之间;在刻蚀多个所述子连接区域上的堆叠结构之前,所述制备方法还包括:以一个堆叠对的高度为刻蚀单元对所述第一顶栅区域上的堆叠结构进行刻蚀以形成第一顶部选择栅台阶块,和/或,以一个堆叠对的高度为刻蚀单元对所述第二顶栅区域上的堆叠结构进行刻蚀以形成第二顶部选择栅台阶块,其中,位于顶部的所述台阶块的起始台阶比所述第一顶部选择栅台阶块和/或所

述第二顶部选择栅台阶块的尾端台阶至少高一个堆叠对的高度。

10.其中,所述堆叠结构还包括第二连接区和第三连接区,在所述第一方向上,所述第二连接区位于所述第一阵列区远离所述第一连接区的一侧,所述第三连接区位于所述第二阵列区远离所述第一连接区的一侧,所述第二连接区包括第一底栅区域,所述第三连接区包括第二底栅区域;在形成所述中间台阶块之后,且在形成所述台阶块之前,所述制备方法还包括:以一个堆叠对的高度为刻蚀单元对所述第一底栅区域上的堆叠结构进行刻蚀以形成第一初始底部选择栅台阶块;和/或,以一个堆叠对的高度为刻蚀单元对所述第二底栅区域上的堆叠结构进行刻蚀以形成第二初始底部选择栅台阶块;其中,所述中间台阶块的底端台阶比所述第一初始底部选择栅台阶块和/或第二初始底部选择栅台阶块的尾端台阶高至少四个堆叠对的高度。

11.其中,在形成所述中间台阶块、所述第一初始底部选择栅台阶块和/或所述第二初始底部选择栅台阶块之后,且在形成所述台阶块之前,所述制备方法还包括:对多个所述中间台阶块执行刻蚀工艺以形成多个依次设置的所述台阶块;以及对所述第一初始底部选择栅台阶块执行刻蚀工艺以形成第一底部选择栅台阶块;和/或,对所述第二初始底部选择栅台阶块执行刻蚀工艺以形成第二底部选择栅台阶块;其中,所述第一底部选择栅台阶块和/或所述第二底部选择栅台阶块的顶端台阶比位于底部的所述台阶块的尾端台阶至少高一个堆叠对的高度。

12.其中,在形成所述台阶块之后,所述制备方法还包括:在所述第一阵列区上的堆叠结构和在所述第二阵列区上的堆叠结构内形成沟道结构,其中,所述沟道结构穿过多个所述堆叠对伸入到所述衬底内。

13.其中,所述堆叠结构还包括多个桥接区域,所述桥接区域在第二方向上位于所述子连接区域之间;在刻蚀多个所述子连接区域上的堆叠结构之前,所述制备方法还包括:在所述堆叠结构上形成掩膜层,其中,所述掩膜层覆盖多个所述桥接区域上的堆叠结构。

14.本发明提供一种半导体器件,包括:衬底;多个依次设置的台阶块,位于所述衬底上,所述台阶块中的台阶包括至少两个堆叠对。

15.其中,所述台阶块包括第一台阶部与第二台阶部,所述第一台阶部与所述第二台阶部相对设置,且所述第一台阶部中的台阶与所述第二台阶部中的台阶错位排布。

16.其中,在所述第一方向上,所述台阶块包括相邻的第一台阶块与第二台阶块,所述第二台阶块的起始台阶比所述第一台阶块的尾端台阶至少高一个堆叠对的高度。

17.其中,所述半导体器件还包括第一顶部选择阶梯块和第二顶部选择阶梯块,多个所述台阶块在所述第一方向上位于所述第一顶部选择栅阶梯块和所述第二顶部选择栅阶梯块之间;位于顶部的所述台阶块的起始台阶比所述第一顶部选择栅台阶块和/或所述第二顶部选择栅台阶块的尾端台阶至少高一个堆叠对的高度。

18.其中,所述半导体器件还包括第一底部选择栅台阶块和第二底部选择栅台阶块,所述第一底部选择栅阶梯块位于所述第一顶部选择栅台阶块远离所述台阶块的一侧,所述第二底部选择栅台阶块位于所述第二顶部选择栅台阶块远离所述台阶块的一侧;所述第一底部选择栅台阶块和/或所述第二底部选择栅台阶块的顶端台阶比位于底部的所述台阶块的尾端台阶至少高一个堆叠对的高度。

19.其中,所述半导体器件还包括第一存储阵列与第二存储阵列,所述第一存储阵列

位于所述第一底部选择栅台阶块与所述第一顶部选择栅台阶块之间,所述第二存储阵列位于所述第二底部选择栅台阶块与所述第二顶部选择栅台阶块之间,所述第一存储阵列与所述第二存储阵列上均形成有沟道结构,所述沟道结构穿过多个所述堆叠对伸入到所述衬底内。

20.其中,所述半导体器件还包括多个桥接结构,在第二方向上,多个所述桥接结构间隔设置,所述多个台阶块位于多个所述桥接结构之间。

21.综上所述,本技术通过设置台阶块的每个台阶包括两个堆叠对,即在对堆叠结构刻蚀的过程中,每次以两个堆叠对为刻蚀单元进行刻蚀,两个堆叠对形成一个台阶,相邻台阶的台阶角落里不会有残留物残留,台阶块后续的操作空间较大。

附图说明

22.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

23.图1是本发明实施例提供的半导体器件的制备方法的流程示意图。

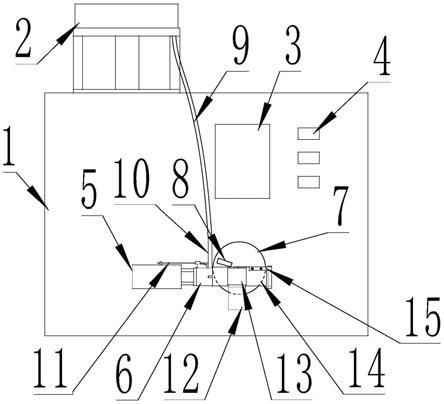

24.图2是本发明的半导体器件的俯视结构示意图。

25.图3是图2中的初始阶梯块的结构示意图。

26.图4是图2中的多个台阶块的结构示意图。

27.图5是图2中的一个台阶块的结构示意图。

28.图6第一顶部选择阶梯块或第二顶部选择阶梯块的第一种结构示意图。

29.图7第一顶部选择阶梯块或第二顶部选择阶梯块的第二种结构示意图。

30.图8是中间台阶块的结构示意图。

31.图9是3个相邻台阶块以及第一顶部选择栅台阶块的结构示意图。

32.图10是底部台阶块和第一底部选择栅台阶块的层结构示意图。

33.图11是形成本技术半导体器件的第一种掩膜层的俯视示意图。

34.图12是形成本技术半导体器件的第二种掩膜层的俯视示意图。

35.图13是形成本技术半导体器件的第三种掩膜层的俯视示意图。

36.图14是形成本技术半导体器件的第四种掩膜层的俯视示意图。

具体实施方式

37.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

38.本发明提供一种半导体器件的制备方法。请参阅图1,图1为本发明提供的一种半导体器件的制备方法的流程示意图。本技术中,通过设置台阶块20的每个台阶包括两个堆叠对120,即在对堆叠结构刻蚀的过程中,每次以两个堆叠对120为刻蚀单元进行刻蚀,两个堆叠对120形成一个台阶,相邻台阶的台阶角落里不会有残留物残留,台阶块20后续的操作

空间较大。本技术改善了由单个堆叠对120与多个堆叠对120(如三个堆叠120与n个堆叠对120)形成的台阶,在去除台阶角落里的残留物时,由多个堆叠对120(如三个堆叠120与n个堆叠对120)形成的台阶在台阶角落里的残留物清除干净时,由单个堆叠对120形成的台阶在台阶角落里的残留物仍然存在,台阶块20后续的可操作空间较小的技术问题。

39.半导体器件的制备方法在图1中示出。如图1所示,该方法可以大致概括为如下过程:提供衬底110(s1),在衬底110上形成堆叠结构,堆叠结构包括多个堆叠对120(s2),刻蚀多个子连接区域101上的堆叠结构以形成多个初始阶梯块500(s3),对多个初始阶梯块500进行刻蚀以形成多个依次设置的台阶块20(s4)。以下将分别描述。

40.请参阅图1,该方法首先执行s1-s4的操作:

41.s1,提供衬底110。衬底110的材质例如为硅,当然还可以为其他含硅的衬底110,例如绝缘体上有硅(silicon on insulator,soi)、sige、si:c等,该衬底110内可通过离子注入等工艺形成了器件所需的p-型/n-型或深或浅的各种势阱。

42.s2,请参阅图2,在衬底110上形成堆叠结构,堆叠结构包括多个堆叠对120,其中,堆叠结构包括第一阵列区50、第二阵列区60以及设置在第一阵列区50和第二阵列区60之间的第一连接区10,第一连接区10包括在第一方向上依次设置的多个子连接区域101。可以理解的是,多个堆叠对120在第三方向z上层叠。堆叠对120为绝缘层和栅极牺牲层层叠的叠层,即每个堆叠对120包括一层绝缘层和一层栅极牺牲层。可以采用化学气相沉积(chemical vapor eposition,cv)、原子层沉积(atomic layer eposition,al)或其他合适的沉积方法,依次在衬底110上交替沉积。绝缘层例如由氧化硅构成,栅极牺牲层例如由氮化硅构成,其会在后续工艺中会被金属替换而作为栅极层。绝缘层还可以为氮氧化硅等,栅极牺牲层还可以为无定型硅、多晶硅、氧化铝等。

43.s3,请参阅图3,刻蚀多个子连接区域101上的堆叠结构以形成多个初始阶梯块500,每个初始阶梯块500包括第一初始部分501与第二初始部分502,第一初始部分501与第二初始部分502具有高度差;

44.s4,请参阅图4,对多个初始阶梯块500进行刻蚀以形成多个依次设置的台阶块20,台阶块20中的台阶包括至少两个堆叠对120。可选地,台阶块20的台阶包括两个堆叠对120。

45.本技术中,通过设置台阶块20的每个台阶包括两个堆叠对120,即在对堆叠结构刻蚀的过程中,每次以两个堆叠对120为刻蚀单元进行刻蚀,两个堆叠对120形成一个台阶,相邻台阶的台阶角落里不会有残留物残留,台阶块20后续的操作空间较大。本技术改善了由单个堆叠对120与多个堆叠对120(如三个堆叠120与n个堆叠对120)形成的台阶,在去除台阶角落里的残留物时,由多个堆叠对120(如三个堆叠120与n个堆叠对120)形成的台阶在台阶角落里的残留物清除干净时,由单个堆叠对120形成的台阶在台阶角落里的残留物仍然存在,台阶块20后续的可操作空间较小的技术问题。

46.请参阅图5,在一个具体的实施例中,台阶块20包括第一台阶部201与第二台阶部202,第一台阶部201与第二台阶部202相对设置,且第一台阶部201中的台阶与第二台阶部202中的台阶错位排布。如,第一台阶部201的台阶依次为1、3、5、7、9,第二台阶部202的台阶依次为4、6、8、10、12,第一台阶部201的台阶与第二台阶部202的台阶是错位排布设置。第一台阶部201中的台阶与第二台阶部202中的台阶错位排布,可以使得台阶块20中的台阶形成连续的台阶。可以理解的是,初始阶梯块500的第一初始部分501刻蚀后形成第一台阶部

201,初始阶梯块500的第二初始部分502刻蚀后形成第二台阶部202。第一台阶部201与第二台阶部202在中间部分可以形成连续的台阶。

47.在一个具体的实施例中,在第一方向上,台阶块20包括相邻的第一台阶块与第二台阶块,第二台阶块的起始台阶比第一台阶块的尾端台阶至少高一个堆叠对120的高度。可选地,第二台阶块的起始台阶比第一台阶块的尾端台阶高一个堆叠对120的高度。如在第一台阶块中,第一台阶部201的台阶依次为1、3、5、7、9,第二台阶部202的台阶依次为4、6、8、10、12;在第二台阶块中,第一台阶部201的台阶依次为11、13、15、17、19,第二台阶部202的台阶依次为14、16、18、20、22,第二台阶块的台阶11可以与第一台阶块中的台阶10、12形成连续的台阶。第二台阶块的起始台阶比第一台阶块的尾端台阶至少高一个堆叠对120的高度,可以使得相邻的两个台阶块20中的台阶形成连续的台阶,方便于将所有的台阶引出。

48.请继续参阅图3,在一个具体的实施例中,初始阶梯块500的第一初始部分501比第二初始部分502高三个堆叠对120的高度。可以理解的是,第一初始部分501为边缘平齐的结构,第一初始部分501上没有形成台阶;第二初始部分502为边缘平齐的结构,第二初始部分502上没有形成台阶。可以理解的是,在形成初始阶梯块500之前,子连接区域101上的堆叠结构上形成有阻挡层801,阻挡层801露出部分的堆叠结构,如图13中,子连接区域101上的阻挡层801为间隔的条形状,如此可以露出部分的子连接区域101的部分堆叠结构,以该阻挡层801为掩膜刻蚀堆叠结构后,可以形成初始阶梯块500。

49.本技术中,通过设置初始阶梯块500的第一初始部分501比第二初始部分502高三个堆叠对120的高度,可以使得后续形成的台阶块20中的第一台阶部201中的台阶与第二台阶部202中的台阶错位排布。而且,在对初始阶梯块500每次刻蚀2个堆叠对120时,避免了形成单个堆叠对120的台阶。本技术的台阶角落里不会有残留物残留,台阶块20后续的操作空间较大。

50.在一个具体的实施例中,“对多个初始阶梯块500进行刻蚀以形成多个依次设置的台阶块20”包括:

51.请参阅的图8,以至少两个堆叠对120的高度为刻蚀单元对多个初始阶梯块500进行刻蚀以形成多个中间台阶块520,初始阶梯块500的第一初始部分501刻蚀后形成中间台阶块520的第一台阶部201,初始阶梯块500的第二初始部分502刻蚀后形成中间台阶块520的第二台阶部202,中间台阶块520的第一台阶部201与第二台阶部202相对设置,且中间台阶块520的第一台阶部201的台阶与第二台阶部202的台阶错位排布,第一台阶部201比第二台阶部202高三个堆叠对120的高度。可以理解的是,本步骤对初始阶梯块500的第一初始部分501与第二初始部分502均进行了刻蚀,第一初始部分501刻蚀出台阶后形成了中间台阶块520的第一台阶部201,第二初始部分502刻蚀出台阶后形成了中间台阶块520的第二台阶部202。

52.请参阅图2和图9,在一个具体的实施例中,第一连接区10还包括第一顶栅区域102和第二顶栅区域103,多个子连接区域101在第一方向上连接在第一顶栅区域102和第二顶栅区域103之间;在刻蚀多个子连接区域101上的堆叠结构之前,制备方法还包括:

53.以一个堆叠对120的高度为刻蚀单元对第一顶栅区域102上的堆叠结构进行刻蚀以形成第一顶部选择栅台阶块70。请参阅图12,可以理解的是,在刻蚀之前,在第一顶栅区域102上的堆叠结构上形成阻挡层801,刻蚀阻挡层801,并以刻蚀后的阻挡层801为掩膜刻

蚀第一顶栅区域102上的堆叠结构,以形成第一顶部选择栅台阶块70。第一顶部选择栅台阶块70可以为图6中对称的结构,第一顶部选择栅台阶块70也可以为图7中非对称的结构,一侧的台阶多于另一侧的台阶。

54.和/或,以一个堆叠对120的高度为刻蚀单元对第二顶栅区域103上的堆叠结构进行刻蚀以形成第二顶部选择栅台阶块。请参阅图12,可以理解的是,在刻蚀之前,在第二顶栅区域103上的堆叠结构上形成阻挡层,刻蚀阻挡层,并以刻蚀后的阻挡层为掩膜刻蚀第二顶栅区域103上的堆叠结构,以形成第二顶部选择栅台阶块。第二顶部选择栅台阶块可以为对称的结构,第二顶部选择栅台阶块也可以为非对称的结构,一侧的台阶多于另一侧的台阶。

55.其中,位于顶部的台阶块20的起始台阶比第一顶部选择栅台阶块70和/或第二顶部选择栅台阶块的尾端台阶至少高一个堆叠对120的高度。可选地,位于顶部的台阶块20的起始台阶比第一顶部选择栅台阶块70和/或第二顶部选择栅台阶块的尾端台阶高一个堆叠对120的高度。可以理解的是,第一顶部选择栅台阶块70和/或第二顶部选择栅台阶块的台阶可以为连续的台阶,如台阶可以为1、2、3、4、5、6

……

。

56.本技术中,位于顶部的台阶块20的不连续的台阶可以通过第一顶部选择栅台阶块70和/或第二顶部选择栅台阶块中的台阶进行补充。

57.在一个具体的实施例中,堆叠结构还包括第二连接区30和第三连接区40,在第一方向上,第二连接区30位于第一阵列区50远离第一连接区10的一侧,第三连接区40位于第二阵列区60远离第一连接区10的一侧,第二连接区30包括第一底栅区域130,第三连接区40包括第二底栅区域140;在形成中间台阶块520之后,且在形成台阶块20之前,制备方法还包括:

58.以一个堆叠对120的高度为刻蚀单元对第一底栅区域130上的堆叠结构进行刻蚀以形成第一初始底部选择栅台阶块;

59.和/或,以一个堆叠对120的高度为刻蚀单元对第二底栅区域140上的堆叠结构进行刻蚀以形成第二初始底部选择栅台阶块;

60.其中,中间台阶块520的底端台阶比第一初始底部选择栅台阶块和/或第二初始底部选择栅台阶块的尾端台阶高至少四个堆叠对120的高度。可以理解的是,第一底栅区域130上的堆叠结构刻蚀了7个堆叠对120以形成第一初始底部选择栅台阶块,和/或,第二底栅区域140上的堆叠结构刻蚀了7个堆叠对120以形成第二初始底部选择栅台阶块。

61.请参阅图2,在一个具体的实施例中,在形成中间台阶块520、第一初始底部选择台阶块和/或第二初始底部选择台阶块之后,且在形成台阶块20之前,制备方法还包括:

62.对多个中间台阶块520执行刻蚀工艺以形成多个依次设置的台阶块20;

63.以及对第一初始底部选择栅台阶块执行刻蚀工艺以形成第一底部选择栅台阶块;

64.和/或,对第二初始底部选择栅台阶块执行刻蚀工艺以形成第二底部选择栅台阶块;

65.其中,第一底部选择栅台阶块和/或第二底部选择栅台阶块的顶端台阶比位于底部的台阶块20的尾端台阶至少高一个堆叠对120的高度。

66.可以理解的是,第一初始底部选择台阶块、第二初始底部选择台阶块以及中间台阶块520形成之后,同步对第一初始底部选择台阶块、第二初始底部选择台阶块以及中间台

阶块520进行刻蚀工艺,由于中间台阶块520的尾端台阶比第一初始底部选择栅台阶块和/或第二初始底部选择栅台阶块的尾端台阶高至少四个堆叠对120的高度,则第一初始底部选择栅台阶块和/或第二初始底部选择栅台阶块则首先刻蚀到底部,即首先第一初始底部选择栅台阶块和/或第二初始底部选择栅台阶块首先刻蚀到预设位置,如刻蚀到衬底110,此时最底部的台阶块20的底端台阶比衬底110高四个堆叠对120的高度,由于台阶块20的台阶包括两个堆叠对120的高度,则最底部的台阶块20的第一台阶部201可以为7、9、11、13、15,第二台阶部202可以为4、6、8、10、12;第一底部选择栅台阶块和/或第二底部选择栅台阶块的台阶可以为1、2、3、4、5、6、7,第一底部选择栅台阶块和/或第二底部选择栅台阶块的台阶5可以补充中间台阶块5204、6的缺失的台阶。

67.本技术中,位于底部的台阶块20的不连续的台阶可以通过第一底部选择栅台阶块和/或第二底部选择栅台阶块中的台阶进行补充。

68.也就是说,本技术的多个台阶块20中的位于最顶部的台阶块20缺失的台阶可以通过第一顶部选择栅台阶块70和/或第二顶部选择栅台阶块的台阶进行补充,位于最底部的台阶块20缺失的台阶可以通过第一底部选择栅台阶块和/或第二底部选择栅台阶块的台阶进行补充,位于最顶部与最底部之间的台阶块20的台阶相互补充以形成连续的台阶。

69.如图4中,图4中的第一连接区10具有12个台阶块20,每个台阶块20的第一台阶部201具有13个台阶,第一台阶部201比第二台阶部202高3个堆叠对120的高度。如图9所示,台阶块20b的第一台阶部201从上到下的台阶依次是280、278、276、274、272、270、268、266、264、262、260、258、256、254;台阶块20b的第二台阶部202从下到上的台阶依次是257、259、261、263、265、267、269、271、273、275、277、379、381、383。根据台阶块20b的第一台阶部201和第二台阶部202可知,台阶块20b缺乏台阶255和台阶279,存在台阶280。

70.与台阶块20b相邻的台阶块20为台阶块20a和台阶块20c。台阶块20a的第一台阶部201从上到下的台阶依次是308、306、304、302、300、298、296、294、292、290、288、286、284、282;台阶块20a的第二台阶部202从下到上的台阶依次是279、281、283、285、287、289、291、293、295、297、299、301、303、305。根据台阶块20a的第一台阶部201和第二台阶部202可知,台阶块20a缺乏台阶307和台阶280,存在台阶279。

71.台阶块20c的第一台阶部201从上到下的台阶依次是252、250、248、246、244、242、240、238、236、234、232、230、228、226;台阶块20c的第二台阶部202从下到上的台阶依次是229、231、233、235、237、239、241、243、245、247、249、251、253、255。根据台阶块20c的第一台阶部201和第二台阶部202可知,台阶块20c缺乏台阶227和台阶254,存在台阶255层。

72.即台阶块20b缺失的台阶279可通过台阶块20a的台阶279补充,台阶块20b缺失的台阶255可通过台阶块20c的台阶255补充。

73.从而,本技术不仅解决了单个堆叠对120的台阶在台阶角落里会残留有残留物,使得台阶块20后续的可操作空间较小的技术问题。而且,本技术的多个台阶块20可以相互弥补,半导体器件的台阶结构完整。

74.如图9中,顶部的台阶块20为台阶块20a,第一顶部选择栅(tsg)台阶块70的第一台阶部201从上到下的台阶依次是309、308、307、306,第一顶部选择栅(tsg)台阶块70的第二台阶部202从下到上的台阶依次是306、307、308、309。即第一顶部选择栅(tsg)台阶块70的台阶307可以补充台阶块20a缺失的台阶307。当然,第二顶部选择栅(tsg)台阶块20的台阶

也可以补充台阶块20a的台阶。

75.从而,即使位于最顶部的台阶块20缺失的台阶也可以通过第一顶部选择栅(tsg)台阶块70和第二顶部选择栅(tsg)台阶块20的任一个补充,实现了半导体器件的台阶结构的完整。

76.如图10中,底部的台阶块20e的第一台阶部201从上到下的台阶依次是33、31、29、27、25、23、21、19、17、15、13、11、9、7,底部的台阶块20e的第二台阶部202从下到上的台阶依次是4、6、8、10、12、14、16、18、20、22、24、26、28、30。底部的台阶块20e缺失的两个台阶为台阶5和台阶33,第一底部选择栅(bsg)台阶块90和第二底部选择栅(bsg)台阶块20的台阶可以为0、1、2、3、4、5、6、7。第一底部选择栅(bsg)台阶块90和第二底部选择栅(bsg)台阶块20的台阶5可以补充底部的台阶块20e的台阶5。底部的阶梯块e的台阶33可以通过与底部的阶梯块e相邻的台阶块20补充。

77.从而,即使位于最底部的底部台阶块20e缺失的台阶也可以通过第一底部选择栅(bsg)台阶块90和第二底部选择栅(bsg)台阶块20的任一个补充,实现了半导体器件的台阶结构的完整。

78.在一个具体的实施例中,在形成台阶块20之后,制备方法还包括:

79.在第一阵列区50上的堆叠结构和在第二阵列区60上的堆叠结构内形成沟道结构,其中,沟道结构穿过多个堆叠对120伸入到衬底110内。可以理解的是,第一阵列区50和第二阵列区60主要用于存储。

80.请参阅图11,在一个具体的实施例中,堆叠结构还包括多个桥接区域802,桥接区域802在第二方向上位于子连接区域101之间;在刻蚀多个子连接区域101上的堆叠结构之前,制备方法还包括:

81.在堆叠结构上形成掩膜层320,其中,掩膜层320覆盖多个桥接区域802上的堆叠结构。可以理解的是,第二方向y与第一方向x垂直。多个台阶块20位于桥接结构之间的空间内,第一阵列区50通过桥接结构与台阶块20连接,第二阵列区60通过桥接结构与台阶块20连接。桥接结构中的字线以桥接台阶块20和阵列区域(第一阵列区50和第二阵列区60)上的字线触点,以便实现双向字线驱动方案。如图14中,可以通过掩膜层320来形成第一阵列区50和第二阵列区60,可以通过掩膜层320来形成桥接结构。在图2中,桥接结构分别为第一桥接结构170和第二桥接结构180。可以在掩膜层320之间的缝隙330形成第一顶部选择栅(tsg)台阶块70和第二顶部选择栅(tsg)台阶块20。可以在掩膜层320之间的间隙340形成台阶块20。

82.在一个具体的实施例中,制备方法还包括:

83.在第一方向x上形成穿过第二连接区30、第一阵列区50、第一连接区10、第二阵列区60以及第三连接区40的分隔结构,其中,分隔结构伸入到衬底110内。可以理解的是,分隔结构用于将堆叠结构分隔为至少两个存储块。图2中,分隔结构分别为第一分隔结构210、第二分隔结构220和第三分隔结构230。第一分隔结构210与第二分隔结构220之间的结构为第一存储块,第二分隔结构220和第三分隔结构230之间的结构为第二存储块。多个台阶块20可以由第二分隔结构220分隔成第一连接台阶块240和第二连接台阶块250。第一连接台阶块240通过第一桥接结构170连接至第一阵列区50,第二连接台阶块250通过第二桥接结构180连接至第二阵列区60。分隔结构(例如,第一分隔结构210)可以形成在图14中的虚线350

中。因此,可以通过分隔结构来限定多个存储块。

84.请参阅图3,除了上述半导体器件的制备方法,本发明实施例还提供了一种半导体器件。本发明实施例的半导体器件及半导体器件的制备方法都可以实现本发明的优点,二者可以一起使用,当然也可以单独使用,本发明对此没有特别限制。在一种具体的实施例中,半导体器件由上述的半导体器件的制备方法制备形成。可选地,半导体器件为三维存储器。

85.半导体器件包括:衬底110;多个依次设置的台阶块20,位于衬底110上,台阶块20中的台阶包括至少两个堆叠对120。

86.本技术中,通过设置台阶块20的每个台阶包括两个堆叠对120,即在对堆叠结构刻蚀的过程中,每次以两个堆叠对120为刻蚀单元进行刻蚀,两个堆叠对120形成一个台阶,相邻台阶的台阶角落里不会有残留物残留,台阶块20后续的操作空间较大。本技术改善了由单个堆叠对120与多个堆叠对120(如三个堆叠120与n个堆叠对120)形成的台阶,在去除台阶角落里的残留物时,由多个堆叠对120(如三个堆叠120与n个堆叠对120)形成的台阶在台阶角落里的残留物清除干净时,由单个堆叠对120形成的台阶在台阶角落里的残留物仍然存在,台阶块20后续的可操作空间较小的技术问题。

87.在一个具体的实施例中,台阶块20包括第一台阶部201与第二台阶部202,第一台阶部201与第二台阶部202相对设置,且第一台阶部201中的台阶与第二台阶部202中的台阶错位排布。第一台阶部201中的台阶与第二台阶部202中的台阶错位排布,可以使得台阶块20中的台阶形成连续的台阶。

88.在一个具体的实施例中,在第一方向上,台阶块20包括相邻的第一台阶块与第二台阶块,第二台阶块的起始台阶比第一台阶块的尾端台阶至少高一个堆叠对120的高度。第二台阶块的起始台阶比第一台阶块的尾端台阶至少高一个堆叠对120的高度,可以使得相邻的两个台阶块20中的台阶形成连续的台阶,方便于将所有的台阶引出。

89.在一个具体的实施例中,半导体器件还包括第一顶部选择台阶块70和第二顶部选择阶梯块,多个台阶块20在第一方向上位于第一顶部选择栅台阶块70和第二顶部选择栅台阶块之间;位于顶部的台阶块20的起始台阶比第一顶部选择栅台阶块70和/或第二顶部选择栅台阶块的尾端台阶至少高一个堆叠对120的高度。本技术中,位于顶部的台阶块20的不连续的台阶可以通过第一顶部选择栅台阶块70和/或第二顶部选择栅台阶块中的台阶进行补充。可以理解的是,第一顶部选择栅(tsg)台阶块70、多个台阶块20和第二顶部选择栅(tsg)台阶块20沿第一方向x方向依次布置。第一顶部选择栅(tsg)台阶块70、多个台阶块20和第二顶部选择栅(tsg)台阶块20还沿衬底110的第二方向y方向设置在第一桥接结构170和第二桥接结构180之间。第一顶部选择栅(tsg)台阶块70和第二顶部选择栅(tsg)台阶块20可以形成在第二组堆叠对120中,例如,形成在一个或多个顶部字线层和顶部绝缘层中。另外,多个台阶块20中的每个可以形成在多个堆叠对120的相应的字线层和绝缘层中。

90.在一个具体的实施例中,半导体器件还包括第一底部选择栅台阶块和第二底部选择栅台阶块,第一底部选择栅阶梯块位于第一顶部选择栅台阶块70远离台阶块20的一侧,第二底部选择栅台阶块位于第二顶部选择栅台阶块远离台阶块20的一侧;所述第一底部选择栅台阶块和/或所述第二底部选择栅台阶块的顶端台阶比位于底部的所述台阶块的尾端台阶至少高一个堆叠对的高度。可以理解的是,第一底部选择栅(bsg)台阶块90形成在与衬

底110相邻的堆叠对120中,例如,形成在与衬底110相邻的一个或多个最底部字线层和最底部绝缘层中。类似地,第二底部选择栅(bsg)台阶块20也可以形成在与衬底110相邻的第一组堆叠对120中。

91.本技术中,位于底部的台阶块20的不连续的台阶可以通过第一底部选择栅台阶块和/或第二底部选择栅台阶块中的台阶进行补充。

92.在一个具体的实施例中,半导体器件还包括第一存储阵列与第二存储阵列,第一存储阵列位于第一底部选择栅台阶块与第一顶部选择栅台阶块70之间,第二存储阵列位于第二底部选择栅台阶块与第二顶部选择栅台阶块之间,第一存储阵列与第二存储阵列上均形成有沟道结构,沟道结构穿过多个堆叠对120伸入到衬底110内。第一存储阵列与第二存储阵列用于存储。沟道结构150中的每个还可以包括沟道层、围绕沟道层的隧道层、围绕隧道层的电荷陷阱层以及围绕电荷陷阱层的阻挡层。此外,沟道结构150可以与字线层直接接触。

93.在一个具体的实施例中,半导体器件还包括多个桥接结构,在第二方向上,多个桥接结构间隔设置,多个台阶块20位于多个桥接结构之间。桥接结构中的字线以桥接台阶块20和阵列区域(第一阵列区50和第二阵列区60)上的字线触点,以便实现双向字线驱动方案。

94.半导体器件可以包括第一分隔结构210。第一分隔结构210可以延伸穿过多个堆叠对120伸入到衬底110中并且沿第一方向x延伸。

95.半导体器件还可以具有第二分隔结构220。第二分隔结构220可以沿第一方向x形成并且延伸穿过多个堆叠对120伸入到衬底110。在一些实施例中,多个阶梯块20可以由第二分隔结构220分隔成第一连接台阶240和第二连接台阶250。第二分隔结构220可以进一步将第一底部选择栅(bsg)台阶块90划分为第一子bsg台阶块901和第二子bsg台阶块902。第二分隔结构220可以进一步将第一顶部选择栅(bsg)台阶块70划分为第一子tsg台阶块701和第二子tsg台阶块702。

96.半导体器件可以包括第三分隔结构230。第三分隔结构230可以进一步延伸穿过多个堆叠对120进入到衬底110并沿第一方向x延伸。

97.在一些实施例中,第一分隔结构210、第二分隔结构220和第三分隔结构230可以是栅缝隙(gls)结构。在一些实施例中,gls结构可以由导电材料制成并且定位于阵列公共源(acs)区上以用作触点,其中acs区形成在衬底110中以用作公共源极。在一些实施例中,gls结构可以由电介质材料制成以用作分隔结构。在一些实施例中,使用后栅极制造技术来形成半导体器件。因此,形成gls结构以帮助去除牺牲字线层(也称为牺牲层)以及形成真正的栅极。

98.在一些实施例中,可以在图2中形成两个存储块,其中可以在第一分隔结构210和第二分隔结构220之间限定第一存储块,并且可以在第二分隔结构220和第三分隔结构230之间限定第二存储块。例如,如图2所示,第一桥接结构170、第一连接台阶块240和第一子bsg台阶块901被包括在第一存储块中。第二桥接结构180、第二连接台阶块250和第二子bsg台阶块902包括在第二存储块中。

99.以上所揭露的仅为本发明较佳实施例而已,当然不能以此来限定本发明之权利范围,本领域普通技术人员可以理解实现上述实施例的全部或部分流程,并依本发明权利要

求所作的等同变化,仍属于发明所涵盖的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。