1.本实用新型涉及半导体领域,更具体地涉及一种大功率集成电路芯片封装装置。

背景技术:

2.集成电路芯片的制造过程主要包括以下几个阶段:集成电路芯片的设计阶段、集成电路芯片的制作阶段、集成电路芯片的封装阶段、以及集成电路芯片的测试阶段。当集成电路芯片制作完成后,集成电路芯片上通常有多个焊垫。在集成电路芯片的封装阶段,通常会把集成电路芯片上的这些焊垫与对应的引线框架互相电连接。集成电路芯片通常是通过粘接胶(导电类或绝缘类)或焊锡膏、焊线、或者以植球结合的方式连接到引线框架上,使得集成电路芯片的这些焊垫与引线框架的接点电连接,从而实现集成电路芯片的封装结构内部的电气连接。

3.随着功率类集成电路芯片越来越多地被使用,如何实现大功率集成电路芯片的高散热性能的封装成为半导体行业普遍关心的问题。

技术实现要素:

4.本实用新型提供了一种新颖的大功率集成电路芯片封装装置以及应用于该封装装置中的引线框架。

5.根据本实用新型的实施例,提供了一种集成电路芯片封装装置,包括大功率集成电路芯片、引线框架、以及封装体。其中,引线框架包括载片台和多个引脚;多个引脚中的至少两个同侧相邻引脚及引脚间距空间被连接在一起并被加宽以形成加宽引脚,与加宽引脚同侧相邻的至少一个引脚被空置,并且加宽引脚与载片台相连接,形成大功率集成电路芯片与外界环境的散热通道;并且载片台具有相对于多个引脚所在平面打凹下沉的平面,用于承载大功率集成电路芯片,并且载片台的下沉部的至少一部分暴露于封装体的外部。

6.在一个实施例中,多个引脚包括至少十二个引脚,并且至少十二个引脚中的一组至少六个引脚和另一组至少六个引脚被分别设置在载片台的两侧。

7.在一个实施例中,多个引脚中的部分相邻引脚、或者全部相邻引脚之间的间距大于0.85mm。

8.在一个实施例中,加宽引脚跨被空置的至少一个引脚到同侧相邻的未被空置的引脚的距离大于1mm。

9.在一个实施例中,多个引脚中的四个同侧相邻引脚及引脚间距空间被连接在一起并被加宽以形成加宽引脚。

10.在一个实施例中,载片台的下沉部暴露在封装体的表面的面积占封装体的同侧表面积的30%以上。

11.在一个实施例中,大功率集成电路芯片封装装置被配置为贴片式结构或双列直插式结构。

12.在一个实施例中,大功率集成电路芯片为电源管理类芯片。

13.根据本实用新型的实施例,还提供了一种引线框架,包括载片台和多个引脚。其中,载片台具有相对于多个引脚所在平面打凹下沉的平面,用于承载大功率集成电路芯片;并且多个引脚中的至少两个同侧相邻引脚及引脚间距空间被连接在一起并被加宽以形成加宽引脚,与加宽引脚同侧相邻的至少一个引脚被空置,并且加宽引脚与载片台相连接,形成大功率集成电路芯片与外界环境的散热通道。

14.根据本实用新型实施例的集成电路芯片封装装置与同类结构相比,具有更好的散热性能、同时制造成本较低,因此可以用于大功率集成电路芯片的设计封装、规模化制造和应用。

附图说明

15.从下面结合附图对本实用新型的具体实施方式的描述中可以更好地理解本实用新型,其中:

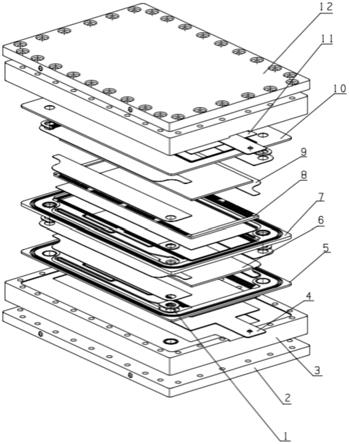

16.图1a示出了根据本实用新型实施例的示例性大功率集成电路芯片封装装置的俯视图;

17.图1b示出了图1a所示的大功率集成电路芯片封装装置沿a-a的截面图;

18.图2a示出了根据本实用新型实施例的示例性大功率集成电路芯片封装装置中的引线框架的俯视图;

19.图2b示出了图2a所示的引线框架沿b-b的截面图;

20.图3a示出了根据本实用新型的另一实施例的示例性大功率集成电路芯片封装装置的俯视图;

21.图3b示出了图3a所示的大功率集成电路芯片封装装置沿c-c的截面图;

22.图4示出了根据本实用新型实施例的示例性大功率集成电路芯片封装装置的内部封装结构的俯视图;

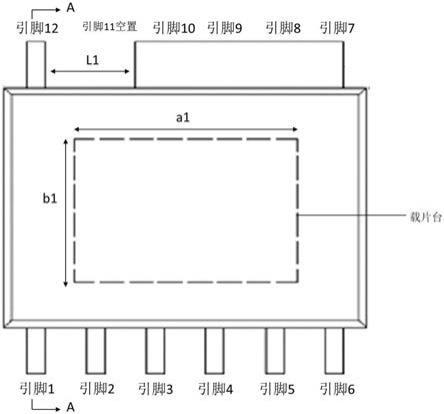

23.图5示出了根据本实用新型实施例的一种示例性电源管理类芯片封装装置的引脚示意图。

24.图6示出了应用如图5所示的示例性电源管理类芯片封装装置的反激式功率变换器的示意性电路连接图。

具体实施方式

25.下面将详细描述本实用新型的各个方面的特征和示例性实施例。在下面的详细描述中,提出了许多具体细节,以便提供对本实用新型的全面理解。但是,对于本领域技术人员来说很明显的是,本实用新型可以在不需要这些具体细节中的一些细节的情况下实施。下面对实施例的描述仅仅是为了通过示出本实用新型的示例来提供对本实用新型的更好的理解。本实用新型决不限于下面所提出的任何具体配置和算法,而是在不脱离本实用新型的精神的前提下覆盖了元素、部件和算法的任何修改、替换和改进。在附图和下面的描述中,没有示出公知的结构和技术,以便避免对本实用新型造成不必要的模糊。

26.随着功率类集成电路芯片越来越多地被使用,如何实现大功率集成电路芯片的高散热性能的封装成为半导体行业普遍关心的问题。鉴于该问题,本实用新型提供了一种新颖的大功率集成电路芯片封装装置。

27.下面结合附图,详细描述根据本实用新型实施例的大功率集成电路芯片封装装置以及应用于该封装装置中的引线框架。

28.图1a示出了根据本实用新型实施例的示例性大功率集成电路芯片封装装置的俯视图。图1b示出了图1a所示的大功率集成电路芯片封装装置沿a-a的截面图。该大功率集成电路芯片封装装置可以应用如图2a和2b 所示的引线框架。该大功率集成电路芯片封装装置例如为贴片式结构,可以包括大功率集成电路芯片、引线框架和封装体,其中引线框架包括引脚 1、引脚2、

…

、引脚10、引脚11、引脚12共12个引脚、以及用于承载大功率集成电路芯片的载片台。如图1a所示,12个引脚中的一组六个引脚(引脚1至引脚6)和另一组六个引脚(引脚7至引脚12)被分别设置在载片台的两侧,位于载片台的一侧的引脚7、引脚8、引脚9、引脚10 及引脚间距空间连接在一起并被加宽以形成一个整体的加宽引脚,并且与该加宽引脚同侧相邻的引脚11被空置,从而该加宽引脚实际上与未被空置的引脚12同侧相邻。由于引脚11被空置,加宽引脚跨被空置的引脚11 到同侧相邻的未被空置的引脚12的距离l1较大。

29.这里需要注意的是,图1a只是示出了根据本实用新型实施例的一种示例性大功率集成电路芯片封装装置,根据本实用新型的大功率集成电路芯片封装装置并不限于图1a所示的引脚结构。例如,根据本实用新型的大功率集成电路芯片封装装置中的引线框架可以包括更少或更多的引脚,加宽引脚可以连接两个、三个或更多个同侧相邻引脚及其引脚间距空间,并且与加宽引脚同侧相邻的被空置的引脚也可以不止一个。

30.结合图1a和1b可以看出,载片台具有相对于引脚1至引脚12所在平面打凹下沉的平面。该打凹下沉的平面在封装体以内,并且用于承载所述大功率集成电路芯片,而载片台的下沉部的至少一部分(例如,与载片台的打凹下沉的平面相对的面)可以被暴露在大功率集成电路芯片封装装置的封装体的外部以形成大功率集成电路芯片与外界环境的散热通道。此外,引脚7、引脚8、引脚9、引脚10连接在一起形成的加宽引脚可以与载片台相连接,进一步扩展大功率集成电路芯片与外界环境的散热通道。该表面贴装结构既能适用于pcba组装类工厂的传统回流焊工艺,又能适用于被传统用于插件结构的波峰焊工艺,可在大中小各类组装加工工厂应用组装贴片,大大降低组装成本。

31.下面结合图2a和图2b更详细地描述应用于根据本实用新型实施例的大功率集成电路芯片封装装置中的引线框架的结构。如图2a所示,引线框架2a包括引脚1、引脚2、

…

、引脚10、引脚11、引脚12共12个引脚、以及载片台2a-1;载片台2a-1与引脚7、引脚8、引脚9、引脚10 连接在一起;引脚7、引脚8、引脚9、引脚10本身也连接在一起并被加宽形成一个整体的加宽引脚;与该加宽引脚同侧相邻的引脚11被空置。

32.图2b示出了图2a所示的引线框架沿b-b的截面图。结合图2a和 2b可以看出,载片台2a-1具有相对于引脚1至引脚12所在平面打凹下沉的平面,并且与引脚7、引脚8、引脚9、引脚10连接在一起,而没有与其他引脚连接在一起。

33.当引线框架2a被应用到大功率集成电路芯片封装装置中时,由于载片台2a-1与引脚7、引脚8、引脚9、引脚10连接在一起,所以承载在载片台2a-1上的大功率集成电路芯片与外界环境的散热通道包括四个引脚。进一步地,由于引脚7、引脚8、引脚9、引脚10本身连接在一起并被加宽,所以进一步扩大了承载在载片台2a-1上的大功率集成电路芯片与外界环境的散热通道。

34.此外,在引线框架2a被应用到大功率集成电路芯片封装装置中时,可以通过把载片台2a-1的下沉部的至少一部分暴露在集成电路芯片封装装置的外部,来进一步扩大承载在载片台2a-1上的大功率集成电路芯片与外部环境的散热通道。为了使载片台2a-1的下沉部暴露在集成电路芯片封装装置的外部,可以将集成电路芯片封装装置的厚度减小。

35.在一些实施例中,引线框架2a的部分相邻引脚或者全部相邻引脚之间的间距可以被调整为更大的间距。例如,可以将该间距设计为大于 0.85mm(例如在0.85-3.6mm的范围内),以预防某些应用条件尤其是潮湿环境下相邻引脚(特别是高压与低压引脚)间的打火问题,从而保证应用引线框架2a的集成电路芯片封装装置的可靠性和安全性。另外,可以将与加宽引脚同侧相邻的至少一个引脚空置,以使得加宽引脚与实际同侧相邻的未被空置的引脚的距离变大,进一步提高集成电路芯片封装装置的可靠性和安全性。例如,加宽引脚跨被空置的至少一个引脚到实际同侧相邻的未被空置的引脚的距离可以被设计为大于1mm。

36.此外,在一些实施例中,可以将载片台2a-1的尺寸做得更大,例如,其面积占集成电路芯片封装装置的封装体的总面积的10%-90%,从而承载更大尺寸的大功率集成电路芯片,同时可以有更大的暴露在集成电路芯片封装装置外部的散热面积。例如,载片台2a-1的下沉部暴露在封装体的表面的面积可以占封装体的同侧表面积的30%以上。

37.图3a示出了根据本实用新型另一实施例的集成电路芯片封装装置的俯视图。图3b示出了图3a所示的集成电路芯片封装装置沿c-c的截面图。图3a和3b所示的集成电路芯片封装装置为双列直插式结构,此结构可方便应用于单面pcba设计的插件组装,对组装工厂的设计和工艺要求及限制较小,生产和制造过程简单。其他方面与结合图1a和1b描述的集成电路芯片封装装置类似,这里不再赘述。

38.图4示出了根据本实用新型实施例的大功率集成电路芯片封装装置的内部封装结构的俯视图。如图4所示,载片台4-3被实现为具有更大的尺寸(可根据实际需求放大),以承载更大的大功率集成电路芯片4-1,该大功率集成电路芯片4-1上可以粘贴尺寸较小的控制类集成电路芯片4-2;载片台4-3与引脚7、引脚8、引脚9、引脚10连接在一起,使得大功率集成电路芯片4-1与外界环境的散热通道包括四个引脚;引脚7、引脚8、引脚9、引脚10本身连接在一起,进一步扩大了大功率集成电路芯片4-1 与外界环境的散热通道。

39.如上所述,根据本实用新型实施例的大功率集成电路芯片封装装置适用于功率较大的功率类集成电路芯片的封装。例如,大功率集成电路芯片可以是电源管理类芯片。图5示出了根据本实用新型实施例的一种示例性电源管理类芯片封装装置的引脚示意图。

40.如图5所示,该电源管理类芯片封装装置具有12个引脚,其中引脚1、引脚2、引脚3、引脚4、引脚5、引脚6和引脚12为六个独立引脚,而引脚7、引脚8、引脚9和引脚10连接在一起形成一个整体的加宽引脚,与该加宽引脚相邻的引脚11被空置。

41.图6示出了应用如图5所示的示例性电源管理类芯片封装装置的反激式功率变换器的示意性电路连接图。如图5和图6所示,引脚1被设置为 vdd引脚,即原边供电引脚;引脚2被设置为sw引脚,即过温检测和保护引脚;引脚3被设置为aux引脚,即辅助电源引脚;引脚4被设置为 fb引脚,即环路补偿引脚;引脚5被设置为gnd引脚,即芯片接地引脚;引脚6被设置为cs引脚,即功率开关管电流检测引脚;引脚12被设置为hv引脚,即高压启动引脚;引脚7、引脚8、引脚9和引脚10形成的整体的加宽引脚被设置为drain引脚,即连接电源管理类芯片中的功率开关管漏极的引脚;引脚11空缺,以增加高压drain引脚和相邻其他引脚的高压

隔离间距。

42.以上以大功率电源管理类芯片为示例对根据本实用新型实施例的集成电路芯片封装装置和引线框架的引脚设置进行了描述。但是应理解,根据本实用新型实施例的集成电路芯片封装装置和引线框架可以用于各种大功率集成电路芯片的封装。

43.此外,虽然以上是以十二个引脚的封装结构为示例来描述根据本实用新型实施例的集成电路芯片封装装置的引脚设置,但是应理解,根据本实用新型实施例的集成电路芯片封装装置不限于仅包括十二个引脚,而是可以包括更少或更多的引脚。

44.此外,相关领域的技术人员在应用根据本实用新型实施例的引线框架时,可以在本文中所示出或描述的引线框架的基础上增加任意大小和形状的孔、角落部位的倒角设计、和框架表面镀层设置等。

45.此外,所描述的特征、结构或特性可以以任何合适的方式结合在一个或更多实施例中。在以上的描述中,提供了许多具体细节从而给出对本实用新型的实施例的充分理解。然而,本领域技术人员将意识到,可以实践本实用新型的技术方案而没有所述特定细节中的一个或更多,或者可以采用其它的方法、组元、材料等。在其它情况下,不详细示出或描述公知结构、材料或者操作以避免模糊本实用新型的主要技术创意。

46.本领域技术人员应能理解,上述实施例均是示例性而非限制性的。在不同实施例中出现的不同技术特征可以进行组合,以取得有益效果。本领域技术人员在研究附图、说明书及权利要求书的基础上,应能理解并实现所揭示的实施例的其他变化的实施例。某些技术特征出现在不同的从属权利要求中并不意味着不能将这些技术特征进行组合以取得有益效果。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。