一种用于芯片封装的载板和芯片的封装结构

[技术领域]

[0001]

本发明涉及芯片封装,尤其涉及一种用于芯片封装的载板和芯片的封装结构。

[

背景技术:

]

[0002]

封装载板(引线框架)是ic封装的关键专用基础材料。申请号为cn202011273348.x的发明公开了一种用于芯片封装的引线框架及制备方法和芯片封装结构。引线框架包括承载片、第一阻焊油墨层和复数个按矩阵布置的单元电路,单元电路包括复数个电极,电极包括顶电极和底电极;顶电极布置在第一阻焊油墨层的顶面;对应于每个单元电路,第一阻焊油墨层包括与电极对应的底电极孔,底电极布置在底电极孔中,底电极的顶部固定在顶电极的底面上;承载片可剥离地粘贴在第一阻焊油墨层和底电极的底面上。该发明的引线框架制备过程需要对工件上下面反复加工,加工过程中对工件进行翻转,增加了工艺难度和制备成本;另外,该发明的引线框架当线路较为复杂时,线路难以布局。

[

技术实现要素:

]

[0003]

本发明要解决的技术问题是提供一种在尺寸较小的空间中便于布置复杂线路的芯片封装载板。

[0004]

本发明进一步要解决的技术问题是提供一种制备过程中不需要翻转,工艺过程简单的芯片封装载板。

[0005]

本发明另一个要解决的技术问题是提供一种载板制备工艺简单的芯片封装结构。

[0006]

为了解决上述技术问题,本发明采用的技术方案是,一种用于芯片封装的载板,包括承载片、基板和复数个按矩阵布置的单元电路,单元电路包括复数个电极,电极包括顶电极和底电极,承载片可剥离地粘贴在基板的底面上,所述的基板包括n个基板层,n为大于或等于1的整数;所述的基板层包括可沉铜树脂层和线路层,线路层布置在可沉铜树脂层的顶面,可沉铜树脂层中包括复数个铜柱;铜柱的下端与下一基板层顶面线路层的线路连接,上端与本基板层顶面线路层的线路连接;顶部基板层的线路层包括所述的顶电极,底部基板层的铜柱与对应的底电极连接。

[0007]

以上所述的载板,包括与顶电极对应的过梁连接铜柱,过梁连接铜柱布置在对应顶电极的上方,过梁连接铜柱的底部与对应的顶电极连接;顶部基板层的线路层包括固定芯片的基岛。

[0008]

以上所述的载板,包括阻焊油墨层,阻焊油墨层覆盖在顶部基板层的上面,阻焊油墨层包括与单元电路对应的窗口,单元电路顶电极的焊盘裸露在所述的窗口中。

[0009]

以上所述的载板,载板的制作过程包括以下步骤:

[0010]

401)承载片的顶面覆盖抗粘层,在抗粘层上制作出与所述底电极形状对应的镂空图形,在抗粘层镂空图形区域电镀形成所述的底电极;

[0011]

402)在抗粘层和底电极的顶面设置第一可沉铜树脂层,在第一可沉铜树脂层上光刻或激光打孔制作出与底电极对应的第一通孔,第一通孔的底面为对应的底电极的顶面;

或在抗粘层和底电极的顶面覆盖第一铜柱感光膜,在第一铜柱感光膜上光刻出与底电极对应的第一通孔,第一通孔的底面为对应的底电极的顶面;

[0012]

403)在第一可沉铜树脂层上的第一通孔中镀铜,形成底面与对应底电极连接的、顶面与第一可沉铜树脂层顶面平齐的第一铜柱;或在第一铜柱感光膜上的第一通孔中镀铜,形成底面与对应底电极连接的第一铜柱,去除第一铜柱感光膜后在抗粘层和底电极的顶面设置第一可沉铜树脂层,研磨第一可沉铜树脂层,使第一铜柱的顶面在第一可沉铜树脂层的表面露出;

[0013]

404)在第一可沉铜树脂层和第一铜柱的顶面沉铜,制作第一线路层,第一可沉铜树脂层和第一线路层组成最下层的基板层;

[0014]

405)当n等于1时,第一线路层即顶面线路层,顶面线路层包括所述的顶电极,第一铜柱的顶部与对应的顶电极连接。

[0015]

以上所述的载板,步骤404在第一可沉铜树脂层的顶面沉铜后制作第一线路包括以下步骤:

[0016]

501)在第一可沉铜树脂层的顶面和第一铜柱的顶面沉铜,形成第一种子铜层;在第一种子铜层的顶面覆盖第一线路感光膜;

[0017]

502)在第一线路感光膜上光刻出与第一线路层对应的第一镂空图形,在第一线路感光膜的第一镂空图形区域镀铜,形成第一线路层的主体;

[0018]

503)去除第一线路感光膜,将第一种子铜层位于第一第一线路层主体以外的种子铜蚀刻掉,形成第一线路层。

[0019]

以上所述的载板,步骤404在第一可沉铜树脂层的顶面沉铜后制作第一线路包括以下步骤:

[0020]

601)在第一可沉铜树脂层的顶面和第一铜柱的顶面沉铜后镀铜;在镀铜层的顶面覆盖第二线路感光膜;

[0021]

602)在第二线路感光膜上光刻出与第一线路层对应的第二镂空图形,第二镂空图形的实体部分与第一线路层的实体部分形状相同;

[0022]

603)对第一可沉铜树脂层的顶面的镀铜层蚀刻;

[0023]

604)去除第二线路感光膜,形成第一线路层。

[0024]

以上所述的载板,当n大于1时,载板的制作过程包括以下步骤:

[0025]

701)在下方基板层的顶面设置第二可沉铜树脂层,在第二可沉铜树脂层上光刻或激光打孔制作出复数个第二通孔,第二通孔的底面为下方基板层线路层的顶面;

[0026]

702)在第二通孔中镀铜,形成底面与下方基板层线路层连接的、顶面与第二可沉铜树脂层顶面平齐的第二铜柱;

[0027]

703)在第二可沉铜树脂层及第二铜柱的顶面沉铜后制作第二线路层,第二可沉铜树脂层、第二铜柱和第二线路层组成所述的第二基板层;

[0028]

704)重复步骤701至703,直到基板层的数量达到n,第n基板层的第二线路层即顶面线路层,顶面线路层包括所述的顶电极,顶部基板层中的第二铜柱与对应的顶电极连接。

[0029]

以上所述的载板,可以在载板的一个或多个基板层嵌入芯片,其载板的制作过程包括以下步骤:

[0030]

801)在步骤502形成第一线路层的主体的上方第覆盖第三铜柱感光膜,在第三铜

柱感光膜上光刻出复数个第三通孔,第三通孔的底面为下方第一线路层的主体的顶面;

[0031]

802)在第三通孔中镀铜,形成底面与下方第一线路层的主体连接的、顶面与第三铜柱感光膜顶面平齐的第三铜柱;

[0032]

803)去除第一线路感光膜和第三铜柱感光膜,露出第一线路层的主体和第三铜柱;将第一种子铜层位于第一线路层主体以外的种子铜蚀刻掉,形成第一线路层;当n等于1嵌入正装芯片时,第一线路层包括固定芯片的基岛。

[0033]

一种芯片的封装结构,包括芯片、单元载板和封装层,单元载板包括基板和单元电路,单元电路包括复数个电极,电极包括顶电极和底电极,芯片的电极与顶电极电连接;所述的基板包括n个基板层,n为大于或等于1的整数;所述的基板层包括可沉铜树脂层和线路层,线路层布置在可沉铜树脂层的顶面,可沉铜树脂层中包括与电极对应的铜柱;铜柱的下端与下一基板层顶面线路层的线路连接,上端与本基板层顶面线路层的线路连接;顶部基板层的线路层包括所述的顶电极,底部基板层的铜柱与对应的底电极连接。

[0034]

以上所述的封装结构,所述的芯片为正装芯片,顶部基板层的线路层包括固定芯片的基岛,正装芯片固定在基岛的顶面上;单元电路包括与顶电极对应的金属过梁和过梁连接铜柱,过梁连接铜柱布置在对应顶电极的上方,过梁连接铜柱的底部与对应的顶电极连接;所述的封装层包括第四可沉铜树脂层和塑封胶层,第四可沉铜树脂层覆盖在顶部基板层、正装芯片和过梁连接铜柱的上方;第四可沉铜树脂层的顶部包括与复数个过梁连接铜柱对应的第一立孔和复数个与正装芯片电极对应的第二立孔;金属过梁布置在第四可沉铜树脂层的顶面上,金属过梁的第一端穿过第一立孔与对应的过梁连接铜柱连接,金属过梁的第二端穿过第二立孔与对应的正装芯片电极连接;塑封胶层覆盖在第四可沉铜树脂层和金属过梁的上方。

[0035]

以上所述的封装结构,正装芯片的封装过程包括以下步骤:

[0036]

1101将正装芯片固定在所述的基岛上;

[0037]

1102在顶部基板层、正装芯片和过梁连接铜柱的上方覆盖第四可沉铜树脂层;

[0038]

1103在第四可沉铜树脂层上光刻或激光打孔,露出正装芯片电极的顶面和过梁连接铜柱的顶面;

[0039]

1104在第四可沉铜树脂层的顶面、正装芯片电极的顶面和过梁连接铜柱的顶面沉铜并电镀,形成第二金属层,对第二金属层采用蚀刻工艺处理形成复数个所述的金属过梁;

[0040]

1105在第四可沉铜树脂层和金属过梁的上方覆盖塑封胶层。

[0041]

本发明可以根据线路的复杂程度调整基板层的数量,以便在尺寸较小的空间中布置下较为复杂的线路。

[附图说明]

[0042]

下面结合附图和具体实施方式对本发明作进一步详细的说明。

[0043]

图1是本发明实施例2芯片封装载板制备方法步骤1的示意图。

[0044]

图2是本发明实施例2芯片封装载板制备方法步骤2的示意图。

[0045]

图3是本发明实施例2芯片封装载板制备方法步骤3的示意图。

[0046]

图4是本发明实施例2芯片封装载板制备方法步骤4的示意图。

[0047]

图5是本发明实施例2芯片封装载板制备方法步骤5的示意图。

[0048]

图6是本发明实施例2芯片封装载板制备方法步骤6的示意图。

[0049]

图7是本发明实施例2芯片封装载板制备方法步骤7的示意图。

[0050]

图8是本发明实施例2芯片封装载板制备方法步骤8的示意图。

[0051]

图9是本发明实施例2芯片封装载板制备方法步骤9的示意图。

[0052]

图10是本发明实施例1芯片封装载板载板单元的结构示意图。

[0053]

图11是本发明实施例3芯片封装载板制备方法步骤3第一步的示意图。

[0054]

图12是本发明实施例3芯片封装载板制备方法步骤3第二步的示意图。

[0055]

图13是本发明实施例3芯片封装载板制备方法步骤4的示意图。

[0056]

图14是本发明实施例3芯片封装载板制备方法步骤5的示意图。

[0057]

图15是本发明实施例5芯片封装载板制备方法步骤6的示意图。

[0058]

图16是本发明实施例5芯片封装载板制备方法步骤7的示意图。

[0059]

图17是本发明实施例5芯片封装载板制备方法步骤8的示意图。

[0060]

图18是本发明实施例5芯片封装载板制备方法步骤9的示意图。

[0061]

图19是本发明实施例5芯片封装载板制备方法步骤10的示意图。

[0062]

图20是本发明实施例5芯片封装载板制备方法步骤11的示意图。

[0063]

图21是本发明实施例5芯片封装载板制备方法步骤12的示意图。

[0064]

图22是本发明实施例4芯片封装载板载板单元的结构示意图。

[0065]

图23是本发明实施例7芯片封装载板制备方法步骤8第一步的示意图。

[0066]

图24是本发明实施例7芯片封装载板制备方法步骤8第二步的示意图。

[0067]

图25是本发明实施例7芯片封装载板制备方法步骤9的示意图。

[0068]

图26是本发明实施例7芯片封装载板制备方法步骤10的示意图。

[0069]

图27是本发明实施例6芯片封装载板载板单元的结构示意图。

[0070]

图28是本发明实施例9芯片封装载板制备方法步骤1的示意图。

[0071]

图29是本发明实施例9芯片封装载板制备方法步骤2的示意图。

[0072]

图30是本发明实施例9芯片封装载板制备方法步骤3的示意图。

[0073]

图31是本发明实施例8芯片封装载板载板单元的结构示意图。

[0074]

图32是本发明实施例11正装芯片封装方法步骤1的示意图。

[0075]

图33是本发明实施例11正装芯片封装方法步骤2的示意图。

[0076]

图34是本发明实施例11正装芯片封装方法步骤3的示意图。

[0077]

图35是本发明实施例11正装芯片封装方法步骤4的示意图。

[0078]

图36是本发明实施例11正装芯片封装方法步骤5的示意图。

[0079]

图37是本发明实施例11正装芯片封装方法步骤6的示意图。

[0080]

图38是本发明实施例10正装芯片封装结构的示意图。

[0081]

图39是本发明实施例12倒装芯片封装结构的示意图。

[0082]

图40是本发明实施例13芯片封装载板制备方法步骤12的示意图。

[0083]

图41是本发明实施例13芯片封装载板制备方法步骤13的示意图。

[0084]

图42是本发明实施例13芯片封装载板制备方法步骤14的示意图。

[0085]

图43是本发明实施例13芯片封装载板制备方法步骤15的示意图。

[0086]

图44是本发明实施例13芯片封装载板制备方法步骤16的示意图。

[0087]

图45是本发明实施例13芯片封装载板制备方法步骤17的示意图。

[0088]

图46是本发明实施例13芯片封装载板载板单元的结构示意图。

[0089]

图47是本发明实施例14芯片封装载板制备方法步骤9的示意图。

[0090]

图48是本发明实施例14芯片封装载板制备方法步骤10的示意图。

[0091]

图49是本发明实施例14芯片封装载板制备方法步骤11的示意图。

[0092]

图50是本发明实施例14芯片封装载板制备方法步骤12的示意图。

[0093]

图51是本发明实施例14芯片封装载板制备方法步骤13的示意图。

[0094]

图52是本发明实施例14芯片封装载板制备方法步骤14的示意图。

[0095]

图53是本发明实施例14芯片封装载板制备方法步骤15的示意图。

[0096]

图54是本发明实施例14芯片封装载板制备方法步骤16的示意图。

[0097]

图55是本发明实施例14芯片封装载板制备方法步骤17的示意图。

[0098]

图56是本发明实施例14芯片封装载板载板单元的结构示意图。

[具体实施方式]

[0099]

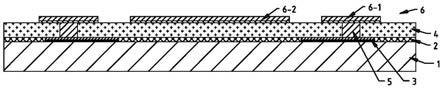

本发明实施例1芯片封装载板用于正装芯片的封装,结构如图10所示,包括不锈钢的承载片1、基板和多个按矩阵布置的单元电路。承载片1通过抗粘层2可剥离地粘贴在基板的底面上,单元电路包括多个电极,电极包括顶电极和底电极3。抗粘层2上有与底电极3对应的底电极孔,底电极3电镀在底电极孔中。基板可以有n个基板层,n为大于等于1的整数。每个基板层包括可沉铜树脂层4和线路层6,线路层6布置在可沉铜树脂层4的顶面上,可沉铜树脂层4中有与电极对应的铜柱5。

[0100]

可沉铜树脂可以采用太阳(taiyo)公司psr-4000bn black/ca-40bn或psr-4000lew3/ca-40lew3的可沉铜树脂油墨,可以光刻打孔或激光打孔。

[0101]

如图10所示,本实施例n=1。如果n≥2,基板层铜柱5的下端与下方基板层顶面线路层的线路连接,上端与本基板层顶面线路层的线路连接,底部基板层的铜柱5与对应的底电极3连接。

[0102]

本实施例n=1。铜柱5的下端与对应的底电极3连接,基板层为顶部基板层,其上的线路层6包括顶电极6-1和基岛6-2。

[0103]

本发明实施例2为实施例1芯片封装载板的制备方法,包括以下步骤:

[0104]

1)如图1所示,不锈钢承载片1的顶面覆盖可感光的抗粘层2。在抗粘层2上制作出与底电极3形状对应的镂空图形。镂空图形有镂空区域(底电极孔)2-1。

[0105]

2)如图2所示,在抗粘层2镂空图形的镂空区域(底电极孔)2-1中电镀形成底电极3。

[0106]

3)如图3所示,在抗粘层2和底电极3的顶面印刷第一可沉铜树脂层4。

[0107]

4)如图4所示,在第一可沉铜树脂层4上光刻或激光打孔制作出与底电极3对应的第一通孔4-1,第一通孔4-1的底面为对应的底电极3的顶面。

[0108]

5)如图5所示,在第一可沉铜树脂层4上的第一通孔4-1中镀铜,形成底面与对应底电极3连接的、顶面与第一可沉铜树脂层4顶面平齐的第一铜柱5。

[0109]

6)如图6所示,在第一可沉铜树脂层4的顶面和第一铜柱5的顶面化学沉铜,形成第一种子铜层6-3。在第一种子铜层6-3的顶面覆盖第一线路感光膜7。

[0110]

7)如图7所示,在第一线路感光膜7上光刻出与第一线路层6对应的第一镂空图形7-1,

[0111]

8)如图8所示,在第一线路感光膜7的第一镂空图形7-1的镂空区域镀铜,形成第一线路层6的主体6-4。

[0112]

9)如图9所示,通过药水浸泡,去除第一线路感光膜7。

[0113]

10)如图10所示,将第一种子铜层6-3位于第一线路层6主体6-4以外的种子铜蚀刻掉,形成第一线路层6,第一线路层6的单元电路包括复数个顶电极6-1和用于固定正装芯片的基岛6-2。至此,得到实施例1的芯片封装载板。

[0114]

本发明实施例3为实施例1芯片封装载板的又一种制备方法,包括以下步骤:

[0115]

实施例3芯片封装载板的制备方法的步骤1和2与实施例2的步骤1和2相同。

[0116]

3)如图11所示,在抗粘层2和底电极3的顶面覆盖第一铜柱感光膜7’。如图12所示,在第一铜柱感光膜7’上光刻出与底电极3对应的第一通孔7

’‑

1,第一通孔7

’‑

1的底面为对应的底电极3的顶面。

[0117]

4)如图13所示,在第一铜柱感光膜7’上的第一通孔7

’‑

1中镀铜,形成底面与对应底电极3连接的第一铜柱5。

[0118]

5)如图14所示,去除第一铜柱感光膜7’后在抗粘层2和底电极3的顶面印刷第一可沉铜树脂层4,研磨第一可沉铜树脂层4,使第一铜柱5的顶面在第一可沉铜树脂层4的表面露出。

[0119]

6)实施例3芯片封装载板的制备方法的步骤6至9与实施例2的步骤6至9相同。

[0120]

本发明实施例4芯片封装载板用于倒装芯片的封装,结构如图22所示,与实施例1的区别是,本实施例n=2,顶部基板层铜柱5的下端与下方基板层顶面线路层的线路连接,顶部基板层铜柱5上端与本基板层顶面线路层的线路连接,底部基板层的铜柱5与对应的底电极3连接。另外,还包括阻焊油墨层15,阻焊油墨层15覆盖在顶部基板层的上面,阻焊油墨层15包括与单元电路对应的窗口,单元电路顶电极6-1的焊盘12裸露在阻焊油墨层15的窗口中。

[0121]

本发明实施例5为实施例4芯片封装载板的制备方法,包括以下步骤:

[0122]

实施例5芯片封装载板的制备方法的步骤1至5与实施例2的步骤1至5或实施例3的步骤1至5相同。

[0123]

6)如图15所示,在第一可沉铜树脂层4的顶面和第一铜柱5的顶面沉铜后镀铜。在镀铜层6-5的顶面覆盖第二线路感光膜8。

[0124]

7)如图16所示,在第二线路感光膜8上光刻出与第一线路层6对应的第二镂空图形8-1,第二镂空图形8-1的实体部分与第一线路层6的实体部分形状相同。

[0125]

8)如图17所示,对第一可沉铜树脂层4顶面的镀铜层6-5进行蚀刻。

[0126]

9)如图18所示,去除第二线路感光膜8,形成第一线路层6。

[0127]

10)如图19所示,在下方基板层的顶面印刷第二可沉铜树脂层4a,在第二可沉铜树脂层4a上光刻或激光打孔制作出与电极对应的第二通孔4a-1,第二通孔4a-1的底面为下方基板层线路层6的顶面。

[0128]

11)如图20所示,在第二通孔4a-1中镀铜,形成底面与下方基板层线路层6连接的、顶面与第二可沉铜树脂层4a顶面平齐的第二铜柱5a。

[0129]

12)如图21所示,在第二可沉铜树脂层4a的顶面沉铜后镀铜,并蚀刻,形成第二线路层6a。

[0130]

13)如果n>2,则重复步骤6至12,直到基板层的数量达到n,顶部基板层顶面的第二线路层6a即顶面线路层,顶面线路层包括顶电极6-1,顶部基板层中的第二铜柱5a与对应的顶电极6-1连接。

[0131]

14)如图22所示,在顶部基板层的上方印刷阻焊油墨层15,通过光刻将焊接区域开窗裸露出来。对顶电极6-1的焊盘12镀可焊性金属,至此,完成实施例4芯片封装载板的制作过程。

[0132]

本发明实施例6芯片封装载板用于正装芯片的埋容方式封装,结构如图27所示,实施例6的芯片封装载板在实施例1的基础上,还包括与顶电极6-1对应的过梁连接铜柱5b,过梁连接铜柱5b布置在对应顶电极6-1的上方,过梁连接铜柱5b的底部与对应的顶电极6-1连接。顶部基板层的线路层6包括固定芯片的基岛6-2。

[0133]

本发明实施例7为实施例6芯片封装载板的制备方法,实施例5芯片封装载板的制备方法的步骤1至7与实施例2的步骤1至7相同,在实施例2的步骤7的基础上包括以下步骤:

[0134]

8)如图23所示,在实施例2步骤7形成的第一线路感光膜的第一镂空图形7-1和第一线路层6的主体6-4的上方覆盖第三铜柱感光膜9,第三铜柱感光膜9的高度要大于正装芯片的厚度5-10μm,如图24所示,在第三铜柱感光膜9上光刻出与电极对应的第三通孔9-1,第三通孔9-1的底面为下方第一线路层6的主体6-4的顶面。

[0135]

9)如图25所示,在第三通孔9-1中镀铜,形成底面与下方第一线路层6的主体6-4连接的、顶面与第三铜柱感光膜9顶面平齐的过梁连接铜柱(第三铜柱)5b。

[0136]

10)如图26所示,通过药水浸泡去除第三铜柱感光膜9和第一线路感光膜7,露出第一线路层6的主体6-4、部分种子铜层6-3和过梁连接铜柱(第三铜柱)5b。

[0137]

11)如图27所示,将第一种子铜层6-3位于第一线路层6主体6-4的种子铜蚀刻掉,形成第一线路层6。当n等于1、芯片采用埋容方式时,第一线路层6包括顶电极6-1和基岛6-2,至此,完成了本发明实施例6芯片封装载板的制备过程。

[0138]

本发明实施例8芯片封装载板用于正装芯片封装,结构如图31所示,实施例8的芯片封装载板在实施例1的基础上,多了一个基板层,即基板层的数量n等于2。顶部基板层的第三可沉铜树脂层4b覆盖在底部基板层的上方。顶部基板层的线路层6b包括与复数个顶电极6-1和固定芯片的基岛6-2。顶部基板层铜柱5b的下端与底部基板层顶面的线路层6的线路连接,上端与本基板层顶面线路层6b对应的顶电极6-1连接。

[0139]

本发明实施例9为实施例8芯片封装载板的制备方法,实施例9芯片封装载板的制备方法在实施例7的基础上进行,并包括以下步骤:

[0140]

901)如图28所示,在底部基板层的上方,即第一可沉铜树脂层4、第一线路层6和第三铜柱5b的上方填充第三可沉铜树脂层4b。

[0141]

902)如图29所示,在第三可沉铜树脂层4b上光刻或激光打孔使第三铜柱5b的顶面裸露。

[0142]

903)如图30所示,在第三可沉铜树脂层4b的顶面和第三铜柱5b的顶面沉铜并镀铜,形成铜层6c。

[0143]

904)如图31所示,对铜层6c采用蚀刻工艺处理形成顶面线路层6b,顶面线路层6b

包括顶电极6-1和固定芯片的基岛6-2。在顶电极6-1和固定芯片的基岛6-2的顶面电镀可焊金属层,完成本发明实施例8的芯片封装载板。

[0144]

本发明实施例10正装芯片的封装结构如图38所示,包括正装芯片10a、单元载板和封装胶层。单元载板包括基板和单元电路,单元电路包括多个电极,电极包括顶电极6-1、底电极3和连接顶电极6-1与底电极3的铜柱5。基板可以包括n个基板层,本实施例的n等于1。

[0145]

基板层包括可沉铜树脂层4和线路层6,线路层6布置在可沉铜树脂层4的顶面,包括固定正装芯片10a的基岛和顶电极6-1。可沉铜树脂层4中有与电极对应的铜柱5。铜柱5的上端与对应的顶电极6-1连接。下端与对应的底电极3连接。正装芯片10a固定在基岛的顶面上。

[0146]

单元电路还包括与顶电极6-1对应的金属过梁和过梁连接铜柱5b,过梁连接铜柱5b布置在对应顶电极6-1的上方,过梁连接铜柱5b的底部与对应的顶电极6-1连接。封装胶层包括第四可沉铜树脂层4c和塑封胶层14,第四可沉铜树脂层4c覆盖在基板层、正装芯片10a和铜柱5b的之间和上方。第四可沉铜树脂层4c的顶部包括与多个过梁连接铜柱5b对应的第一立孔和多个与正装芯片10a电极对应的第二立孔。金属过梁13-1布置在第四可沉铜树脂层4c的顶面上,金属过梁13-1的第一端穿过第一立孔与对应的过梁连接铜柱5b连接,金属过梁13-1的第二端穿过第二立孔与对应的正装芯片10a的电极10-1连接。塑封胶层14覆盖在第四可沉铜树脂层4c和金属过梁13-1的上方。

[0147]

本发明实施例11是实施例10正装芯片的封装步骤,实施例10的正装芯片在实施例6芯片封装载板上进行封装,包括以下步骤:

[0148]

1)如图32所示,将多个正装芯片10a按矩阵的形式固定在实施例6整张的芯片封装载板对应的基岛6-2上。

[0149]

2)如图33所示,在顶部基板层、正装芯片10a和过梁连接铜柱5b的之间和上方填充第四可沉铜树脂层4c。

[0150]

3)如图34所示,在第四可沉铜树脂层4c上光刻或激光打孔,露出正装芯片10a电极10-1的顶面和过梁连接铜柱5b的顶面。

[0151]

4)如图35所示,在第四可沉铜树脂层4c的顶面、正装芯片10a电极10-1的顶面和过梁连接铜柱5b的顶面沉铜并电镀,形成第二金属层13,

[0152]

5)如图36所示,对第二金属层13采用蚀刻工艺处理形成多个连接过梁连接铜柱5b和正装芯片10a电极的顶面的金属过梁13-1。

[0153]

6)如图37所示,在第四可沉铜树脂层4c和金属过梁13-1的上方覆盖塑封胶层14。

[0154]

7)如图38所示,将承载片1连同抗粘层2从基板的底面剥离,对塑封好的封装体进行切割,得到实施例10单粒的芯片封装结构。

[0155]

本发明实施例12倒装芯片的封装结构采用实施例4芯片封装载板进行封装。本发明实施例12倒装芯片的封装结构如图39所示,包括倒装芯片10b、单元载板和封装胶层14。单元载板包括基板、阻焊油墨层15和单元电路,单元电路包括多个电极,电极包括顶电极6-1和底电极3。基板可以包括n个基板层,本实施例的n等于2,即包括底部基板层和顶部基板层。

[0156]

底部基板层包括可沉铜树脂层4和线路层6,线路层6布置在可沉铜树脂层4的顶面,可沉铜树脂层4中有与电极对应的铜柱5。铜柱5的上端与线路层中6对应的线路连接。下

端与对应的底电极3连接。

[0157]

顶部基板层包括可沉铜树脂层4a和线路层6a,线路层6a布置在可沉铜树脂层4a的顶面,可沉铜树脂层4a中有与电极对应的铜柱5a。铜柱5a的上端与线路层6a对应的顶电极6a-1连接。下端与底部线路层中6中对应的线路连接。

[0158]

阻焊油墨层15覆盖在顶部基板层的上面,阻焊油墨层15包括与单元电路对应的窗口,单元电路顶电极6a-1的焊盘12裸露在阻焊油墨层15的窗口中。

[0159]

倒装芯片10b坐落在顶电极6a-1的焊盘12上,倒装芯片10b的电极分别与对应顶电极6a-1的焊盘12焊接。封装胶层14封装在阻焊油墨层15和倒装芯片10b的上方。

[0160]

本发明实施例13芯片封装载板的制备方法如图40至图46所示,基板层的数量n等于2,可以在本发明实施例7芯片封装载板的制备方法步骤11(如图27所示)的基础上进行,载板的制作过程包括以下步骤:

[0161]

12)如图40所示,在第一可沉铜树脂层4、第一线路层6和第三铜柱5b的上方填充第五可沉铜树脂层4d。研磨第五可沉铜树脂层4d使第三铜柱5b的顶面裸露。

[0162]

13)如图41所示,在第五可沉铜树脂层4d的顶面和第三铜柱5b的顶面沉铜,形成第二种子铜层6d-3.

[0163]

14)如图42所示,在第二种子铜层6d-3的顶面覆盖第四线路感光膜21。

[0164]

15)如图43所示,在第四线路感光膜21上光刻出与第三线路层6d对应的第三镂空图形21-1。

[0165]

16)如图44所示,在第四线路感光膜21的第三镂空图形21-1的镂空区域镀铜,形成第三线路层6d的主体6d-4,在第三线路层的主体6d-4的表面镀可焊金属层6d-5。

[0166]

17)如图45所示,去除第四线路感光膜21,露出第三线路层6d的主体和第三线路层6d主体区域外的种子铜6d-3。

[0167]

18)如图46所示,将第三线路层主体6d-4区域外的种子铜6d-3蚀刻掉,形成第三线路层6d。第三线路层6d为载板的顶面线路层,第一线路层6为载板的中间线路层,至此完成了本实施例的芯片封装载板。

[0168]

本发明实施例14芯片封装载板的制备方法如图6至图8,以及图47至图56所示。本发明实施例14封装载板基板层的数量n等于3,可以在本发明实施例2芯片封装载板的制备方法步骤6至步骤8的基础上进行,载板的制作过程包括以下步骤:

[0169]

6)如图6所示,在下层可沉铜树脂层(第一可沉铜树脂层)4的顶面和下层铜柱(第一铜柱)5的顶面化学沉铜,形成下层种子铜层(第一种子铜层)6-3。在第一种子铜层6-3的顶面覆盖下层线路感光膜(第一线路感光膜)7。

[0170]

7)如图7所示,在下层线路感光膜(第一线路感光膜)7上光刻出与下层线路层(第一线路层)6对应的下层镂空图形(第一镂空图形)7-1,

[0171]

8)如图8所示,在下层线路感光膜(第一线路感光膜)7的第一镂空图形7-1的镂空区域镀铜,形成下层线路层的主体(第一线路层6的主体)6-4。

[0172]

9)如图47所示,在下层线路层6的主体6-4的上方覆盖第二铜柱感光膜8’,在第二铜柱感光膜8’上光刻出多个上层通孔8-1,上层通孔8-1的底面为下层线路层6的主体6-4的顶面。

[0173]

10)如图48所示,在上层通孔8-1中镀铜,形成底面与下层线路层6的主体6-4连接

的、顶面与第二铜柱感光膜8’顶面平齐的多个上层铜柱5a。

[0174]

11)如图49所示,用药水浸泡去除下层第一线路感光膜7和上层第二铜柱感光膜8’,露出下层线路层的主体6-4和上层铜柱5a。将下层种子铜层位于第下层路层主体以外的种子铜6-3蚀刻掉,形成下层线路层6。

[0175]

12)如图50所示,在下层可沉铜树脂层4、下层线路层6和上层铜柱5a的上方填充上层可沉铜树脂层4a,研磨上层可沉铜树脂层4a使上层铜柱5a的顶面裸露。

[0176]

13)如图51所示,重复步骤6至12,使基板层的数量达到3。

[0177]

14)如图52所示,在最上层的可沉铜树脂层4a2的顶面和最上层铜柱5a2的顶面沉铜,形成顶层种子铜层6a-3。

[0178]

15)如图53所示,在顶层种子铜层的顶面覆盖顶层第三线路感光膜17。

[0179]

16)如图54所示,在顶层第三线路感光膜17上光刻出与顶层线路层6a对应的镂空图形,在顶层第三线路感光膜17的镂空图形的镂空区域镀铜,形成顶面线路层6a的主体6a-4,在顶面线路层主体6a-4的表面镀可焊金属层6a-5。

[0180]

17)如图55所示,去除顶层第三线路感光膜17,露出顶面线路层的主体6a-4和顶面线路层主体6a-4区域外的种子铜6a-3。

[0181]

如图56所示,将顶面线路层主体6a-4区域外的种子铜6a-3蚀刻掉,形成顶面线路层6a,顶面线路层6a包括顶电极6-1,最上层铜柱5a2与对应的顶电极6-1连接,至此完成了本实施例的芯片封装载板。本发明以上实施例具有以下有益效果:

[0182]

1)芯片封装载板的制备过程中利用层层叠加完成,不需要翻转,工艺过程简单,工艺难度小,制备成本较低。

[0183]

2)可以根据线路的复杂程度调整基板层的数量,便于在尺寸较小的空间中布置下较为复杂的线路。

[0184]

3)采用可沉铜树脂制作基板,利用可沉铜树脂表面可以金属化的特点,实现多层走线叠加的结构。

[0185]

4)n层基板可以实现任意相邻两层或两层以上的电性网络之间的互连,从而满足复杂线路网络的布局。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。