半导体装置及光掩模

1.相关申请案的交叉参考

2.本技术案基于并主张2020年8月25日提出申请的第2020-141795号日本专利申请案的优先权权益;所述日本专利申请案的全部内容以引用方式并入本文中。

技术领域

3.本文中所描述的实施例大体来说涉及一种半导体记忆装置及一种光掩模。

背景技术:

4.举例来说,半导体装置具有由多个阶层组成的堆叠结构。由于半导体装置的每一层中的应力影响,布置在不同阶层中的结构之间可出现不对准,且在这些结构之间可出现不良连接。

技术实现要素:

5.实施例的半导体装置包含布置在第一阶层中的第一结构及第二结构,其中所述第一结构及所述第二结构在第一方向上沿着第一阶层的平面重复地布置,且在所述第一结构及所述第二结构的最小重复单元中第一结构的几何中心与所述第二结构的几何中心之间的距离在所述第一方向上的第一位置及第二位置之间是不同的。

6.根据实施例,可抑制布置在不同阶层中的结构之间的不良连接。

附图说明

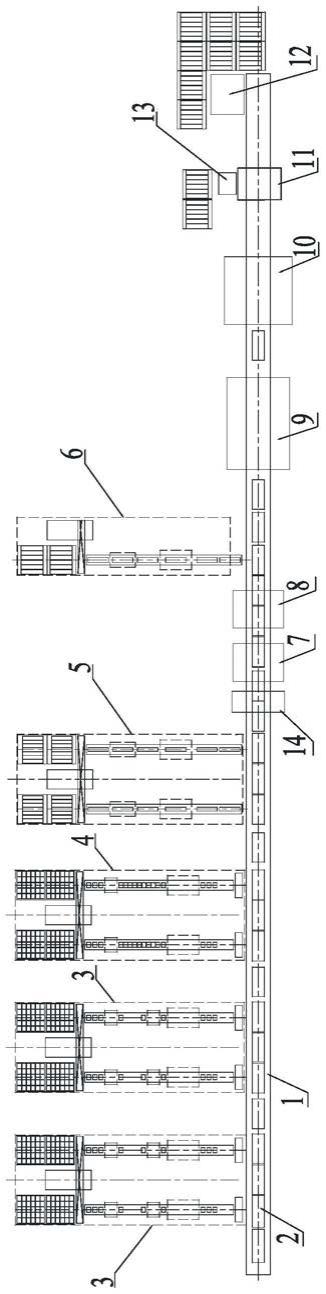

7.图1a及1b是图解说明根据第一实施例的半导体装置的示意性配置实例的图解;

8.图2是包含根据第一实施例的半导体装置的穿透接触件区的区的水平横截面图;

9.图3aa到3db是描述使用第一实施例的光掩模进行不对准校正的图解;

10.图4a及4b是图解说明用于形成根据第一实施例的半导体装置的接触件的光掩模的配置的实例的示意图;

11.图5a及5b是图解说明根据第一实施例的第一修改实例的半导体装置的平面布置的一些实例的图解;

12.图6是图解说明根据第一实施例的第二修改实例的半导体装置的最小单元的实例的图解;

13.图7aa到7cb是描述使用第二实施例的光掩模进行不对准校正的图解;

14.图8a及8b是图解说明用于形成根据第二实施例的半导体装置的接触件及狭缝的光掩模的配置的实例的示意图;且

15.图9aa到9bb是描述使用第二实施例的修改实例的光掩模进行不对准校正的图解。

具体实施方式

16.在后文中,将参考图式详细描述本发明。另外,本发明不受下文所描述的实施例限

制。另外,以下实施例中的组分包含所属领域的技术人员可容易呈现的组分或基本上相同的组分。

17.[第一实施例]

[0018]

在后文中,将参考图式详细描述第一实施例。

[0019]

(半导体装置的配置实例)

[0020]

图1a及1b是图解说明根据第一实施例的半导体装置1的示意性配置实例的图解。图1a是半导体装置1沿着x方向的横截面图,且图1b是图解说明可能在半导体装置1中产生的应力的示意性平面图。然而,在图1a中,省略上层配线中的一些。此外,同时也图解说明在相同区段上不存在的结构。

[0021]

如图1a中所图解说明,半导体装置1包含位于衬底sb上的外围电路cua及堆叠主体lm。

[0022]

衬底sb是半导体衬底,例如硅衬底。包含晶体管tr、接触件等的外围电路cua布置在衬底sb上。晶体管tr布置在作用区域aa上,作用区域aa设置在衬底sb的表面层上。外围电路cua布置在布置有多个存储器单元的存储器区mr下方,且促成将在稍后描述的存储器单元的操作。

[0023]

外围电路cua被绝缘层51覆盖。源极线sl布置在绝缘层51上的部分区中。此外,堆叠有多个字线wl的堆叠主体lm经由源极线sl布置在绝缘层51上的部分区中,其中多个字线wl之间夹置有绝缘层。

[0024]

堆叠主体lm包含存储器区mr、穿透接触件区tpc与tpw及阶梯区sr。

[0025]

举例来说,存储器区mr布置在堆叠主体lm的中心附近。在存储器区mr中布置有多个柱pl,所述多个柱pl在堆叠方向上穿透字线wl而到达源极线sl。连接柱pl与上层配线(例如,位线)的插塞ch布置在柱pl的上部端部处。多个存储器单元形成在柱pl与字线wl的相交处。通过对从字线wl电连接到对应字线wl的存储器单元施加预定电压来从存储器单元读取数据及将数据写入到存储器单元等。

[0026]

如此一来,半导体装置1被配置为例如存储器单元三维地布置在存储器区mr中的三维非易失性存储器。

[0027]

字线wl在x方向上终止于堆叠主体lm的两个端部处。字线wl的一个端侧是阶梯区sr,且字线wl的另一端侧是穿透接触件区tpw。

[0028]

阶梯区sr具有所述多个字线wl在阶梯图案中露出的配置。连接字线wl与上层配线等的接触件cc布置在在阶梯图案中露出的所述多个字线wl中的每一者的平台部分上,且接触件cc经配置以能够经由字线wl对存储器单元施加预定电压。

[0029]

在本说明书中,阶梯区sr的每一阶梯的平台表面面向的方向在半导体装置1中被界定为向上方向。

[0030]

在x方向上布置在堆叠主体lm的另一端侧上的穿透接触件区tpw及布置在堆叠主体lm的存储器区mr之间的穿透接触件区tpc中的每一者包含不具有字线wl的绝缘区。

[0031]

堆叠主体lm的字线wl是通过使用导电材料替换由绝缘材料等制成的牺牲层而形成的层。当对材料进行替换时,通过阻止替换部分区中的材料来形成绝缘区(例如,穿透接触件区tpw及tpc)。在所述绝缘区中,布置有连接布置在下侧上的在衬底sb上的外围电路cua与各种上层配线等的接触件c4。

[0032]

更具体来说,经由多个接触件及配线等电连接到外围电路cua的配线d2连接到接触件c4的下端。电连接到上层配线等的插塞ch连接到接触件c4的上端。

[0033]

外围区pr布置在堆叠主体lm周围。外围区pr被绝缘层52覆盖,绝缘层52具有达到至少堆叠主体lm的上表面的高度的厚度。然而,连接外围电路cua与上层配线等的接触件c3也布置在外围区pr中。

[0034]

更具体来说,经由多个接触件及配线等电连接到外围电路cua的配线d2连接到接触件c3的下端。电连接到上层配线等的插塞vy连接到接触件c3的上端。

[0035]

此外,板状部分bp可布置在外围区pr中,在板状部分bp中用于放松作用在外围区pr与堆叠主体lm之间的应力的凹口填充有绝缘层等。板状部分bp在厚度方向上穿透绝缘层52且在y方向上延伸。在半导体装置1中,在制造的中间阶段,在填充绝缘层之前是凹口的板状部分bp将外围区pr与堆叠主体lm分隔开,以使得放松从外围区pr到堆叠主体lm的应力。

[0036]

图1b图解说明半导体装置1的平面pn中的应力分布。举例来说,平面pn含有至少一个堆叠主体lm,且包含能够独立地用作存储电路的最小配置当中属于存储器区mr、阶梯区sr及穿透接触件区tpc及tpw的每一配置,但不包含外围电路cua。在此,连接到穿透接触件区tpc及tpw的接触件c4的配线d2也可包含在平面pn中。半导体装置1可包含一或多个平面pn。在半导体装置1包含多个平面pn的情形中,这些平面pn可并行地操作。

[0037]

如图1b中所图解说明,由于构成外围区pr及平面pn的结构及材料存在差异,外围区pr与平面pn之间可能会产生应力。举例来说,至少在于使用字线wl进行替换之前包含牺牲层的堆叠主体lm中,产生朝向堆叠主体lm的中心的压缩应力,如图1b中的向内箭头所指示。另一方面,在布置有厚绝缘层52的外围区pr中,产生从外围区pr的中心朝向外侧的张应力,如图1b中的向外箭头所指示。

[0038]

由于此应力的影响,图1a中所图解说明的各种结构可与期望形成位置不对准。此外,举例来说,在连接多个不同阶层之间的结构的接触件c3及c4等中,在与下层上的配线d2的连接及与上层上的插塞vy及ch的连接中的一或两者处可能出现不良连接。

[0039]

在图1a的实例中,不同阶层包含例如:阶层hib,其作为包含堆叠主体lm的第一阶层;阶层hia,其作为第二阶层,定位于阶层hib下方,夹置在包含外围电路cua的阶层与阶层hib之间且由包含配线d2的绝缘层51组成;及阶层hic,其作为第三阶层,是包含堆叠主体lm的阶层hib的上层且包含插塞vy及ch等。

[0040]

此外,能够独立地用作存储电路或更广泛来说上文所描述的半导体电路的最小配置是图1a中所图解说明的配置,以第一实施例的半导体装置1为例。即,图1a包含:存储器区mr,其中布置有存储器单元;外围电路cua,其促成所述存储器单元的操作;及各种配线,其包含电连接存储器单元与外围电路cua的字线wl、接触件c4及c3等。在这些配置下,图1a中所图解说明的配置可以是能够独立地用作半导体电路的最小配置。图1a中所图解说明的配置也被称为第一实施例的半导体装置1中的独立操作元件。第一实施例的半导体装置1包含至少一个独立操作元件。

[0041]

第一实施例的结构可适用于例如具有穿透接触件区tpc及tpw中的接触件c4、配线d2及插塞ch的连接结构以及具有上文所描述的外围区pr中的接触件c3、配线d2及插塞vy的连接结构。在后文中,将描述具有穿透接触件区tpc中的接触件c4、配线d2及插塞ch的连接结构来作为实例。

[0042]

(对半导体装置进行不对准校正的实例)

[0043]

图2是包含根据第一实施例的半导体装置1的穿透接触件区tpc的区的水平横截面图。如图2中所图解说明,包含穿透接触件区tpc的区构成多个最小单元ru,在所述多个最小单元ru中作为第一结构的接触件c4在y方向上重复地布置。

[0044]

一个最小单元ru夹置在在y方向上位于两个端部处作为第二结构的两个接触件li之间,且包含接触件c4、板状部分br及布置在穿透接触件区tpc中的柱状部分hr、布置在存储器区mr中的柱pl及布置在穿透接触件区tpc及存储器区mr中的分隔层she。尽管图2中未图解说明,但最小单元ru也包含作为第三结构的配线d2及作为第四结构的插塞ch,所述配线d2及插塞ch连接到接触件c4。另外,最小单元ru中还可包含分割一个最小单元ru的两个接触件li。

[0045]

接触件li具有在x方向上的纵向方向,且具有如下结构:穿透堆叠主体lm到达源极线sl的狭缝填充有具有绝缘层衬层的导电层。形成有接触件li的狭缝在y方向上将堆叠主体lm分隔开以在半导体装置1的平面pn中形成块。在制造时的半导体装置1中,通过移除液体等经由狭缝移除堆叠主体lm的牺牲层,然后再使用导电层进行填充。此外,经由狭缝将导电材料气体供应至通过移除堆叠主体lm的牺牲层获得的间隙中,以使得形成字线wl。

[0046]

接触件li的导电层经由插塞ch连接到上层配线等。在此,连接到接触件li的插塞ch可被称为作为第五结构的插塞ch,且可与作为第四结构连接到上文所描述的接触件c4的插塞ch区分。此外,连接到柱pl的插塞ch可被称为作为第六结构的插塞ch且可与其它插塞ch区分。

[0047]

如上文所描述,在在制造之后的半导体装置1中,接触件li通过连接到上层配线的结构等用作源极线接触件。然而,代替接触件li,可通过使用绝缘层填充狭缝等形成不连接到插塞ch且不用作源极线接触件的结构。

[0048]

分隔层she布置在两个接触件li之间,所述分隔层she通过替换掉牺牲层来将一或多个导电层分隔开,所述一或多个导电层至少包含形成在堆叠主体lm中的导电层当中的最上部导电层。分隔层she在x方向上延伸且将堆叠主体lm的一或多个导电层分割成选择栅极线sgd图案,所述选择栅极线sgd图案在y方向上布置在分隔层she的两侧上。

[0049]

即,选择栅极线sgd布置在堆叠主体lm的所述多个字线wl的上层上。选择栅极线也可布置在堆叠主体lm的所述多个字线wl的下层上。图2图解说明堆叠主体lm的在选择栅极线sgd的高度位置处的水平区段。

[0050]

选择栅极(未图解说明)形成在柱pl与上层上的选择栅极线sgd及下层上的选择栅极线的相交处,且通过接通或关断这些选择栅极来选择或不选择这些选择栅极所属的柱pl的存储器单元。

[0051]

如上文所描述,接触件c4布置在包含阻止被导电材料替换的牺牲层的绝缘区nr中。在图2的实例中,布置在x方向上的多个接触件c4布置在绝缘区nr内。然而,代替x方向或除x方向之外,多个接触件c4可布置在y方向上。

[0052]

阻止使用字线wl等替换牺牲层的板状部分br布置在绝缘区nr在y方向上的两个端部中的每一者处。板状部分br具有在x方向上的纵向方向,且穿透堆叠主体lm以到达源极线sl。板状部分br内部填充有绝缘层。

[0053]

通过此结构,当使用字线wl等替换牺牲层时,板状部分br阻止牺牲层的移除液体

及来自狭缝的导电材料气体内流到绝缘区nr,且在堆叠主体lm的部分区中保全了绝缘区nr。通过将接触件c4布置在绝缘区nr中,例如可抑制接触件c4与字线wl之间发生电传导。

[0054]

多个柱状部分hr布置在不包含绝缘区nr的穿透接触件区tpc中。柱状部分hr穿透堆叠主体lm以到达源极线sl。柱状部分hr内部填充有例如绝缘层等。

[0055]

如上文所描述,当使用字线wl等替换牺牲层时,堆叠主体lm具有在绝缘层之间具有间隙的脆弱结构。在此时,柱状部分hr用作在穿透接触件区tpc中支撑堆叠主体lm的支撑件。另外,所述多个柱状部分hr可布置在上述阶梯区sr中,且这些柱状部分hr可用作支撑阶梯区sr的支撑件。柱状部分hr的布置可以是正交晶格状(矩阵状)布置或交叠周期性布置、没有上述周期性布置的一部分的布置、周期部分地不同于上述周期性布置的布置等。

[0056]

如上文所描述,所述多个柱pl布置在存储器区mr中。存储器单元形成在所述多个柱pl与所述多个字线wl的相交处,且当使用字线wl等替换牺牲层时,柱pl用作在存储器区mr中支撑堆叠主体lm的支撑件。柱pl的布置是二维周期性晶格状布置。从存储器单元的积累密度的角度看,交叠布置与柱pl的布置一样高效。

[0057]

上述配置例如通过以下方式来形成:形成使每一结构的图案在堆叠主体lm上多次出现的光致抗蚀剂膜等,并重复将所述图案转移至堆叠主体lm的过程。例如通过透过光掩模施加曝光光以将光致抗蚀剂膜等的一部分暴露于光来执行在光致抗蚀剂膜等上形成图案。

[0058]

图3aa到3cb是描述使用第一实施例的光掩模进行不对准校正的图解。

[0059]

图3aa是示意性地图解说明未进行不对准校正的光掩模的俯视图以及在使用光掩模的情形中形成的每一结构的俯视图及横截面图的图解。在图3aa中,光掩模及每一结构的俯视图在垂直方向上自上侧开始示意性地图解说明以下各项的状态:在平面pn内在y方向上的一个端部、平面pn内的一个端部与中心部分之间的中间位置、平面pn内的中心部分、平面pn内的中心部分与另一端部之间的中间位置及在平面pn内在y方向上的另一端部。

[0060]

如图3aa中所图解说明,光掩模上用于形成配线d2的配线图案d2p在一个平面pn中在y方向上按照基本上相等的间隔布置。类似地,光掩模上用于形成接触件c4的接触件图案c4p及光掩模上用于形成插塞ch的插塞图案chp也在一个平面pn中在y方向上按照基本上相等的间隔布置。

[0061]

此外,在这些光掩模上,配线图案d2p之间的间隔、接触件图案c4p之间的间隔及插塞图案chp之间的间隔基本上相等。因此,当叠加这些光掩模时,配线图案d2p、接触件图案c4p及插塞图案chp的几何中心的位置在平面pn内在y方向上的任何位置处皆基本上匹配。

[0062]

然而,当使用这些光掩模在衬底sb上依序形成配线d2、接触件c4及插塞ch时,配线d2、接触件c4及插塞ch的不对准量随着朝向平面pn在y方向上的两个端部而增大。

[0063]

这是由于在阶层hia至hic中的每一者中在依序形成配线d2、接触件c4及插塞ch的同时,作用在平面pn内的应力发生改变,且以相等间隔形成的结构不对准。因此,图案之间在光掩模中彼此相等的间隔在实际衬底sb上的结构之间变得不同。因此,结构之间的几何中心的位置不匹配。

[0064]

在图3aa的实例中,在衬底sb上,在平面pn内在y方向上在中心附近消除应力,且配线d2、接触件c4及插塞ch的几何中心的位置基本上匹配。然而,接触件c4之间的间隔增大得比配线d2之间的间隔多,且插塞ch之间的间隔增大地比接触件c4之间的间隔多。因此,接触

件c4的几何中心与配线d2的几何中心之间的距离及接触件c4的几何中心与插塞ch的几何中心之间的距离两者在平面pn内在y方向上朝向两个端部皆增大。

[0065]

参考平面pn在y方向上的一个端部的a-a截面,接触件c4在y方向上自配线d2的中心位置向外移位的位置处连接到配线d2,且插塞ch刚刚能连接到在y方向上位于外侧上的接触件c4的端部。

[0066]

图3ab是示意性地图解说明在使用光掩模的情形中在未进行不对准校正的情况下每一结构的不对准量的图形。图形的水平轴线是平面pn中的y坐标位置,且垂直轴线是y方向上的不对准量。

[0067]

如图3ab中所图解说明,在平面pn内在y方向上在中心附近,配线d2、接触件c4及插塞ch的几何中心的位置基本上匹配,且因此接触件c4与配线d2之间的不对准量msb及接触件c4与插塞ch之间的不对准量mst皆具有最低值。

[0068]

然而,随着在平面pn内在y方向上朝向两个端部,不对准量msb及mst两者皆增大。因此,尽管不对准量msb处于不对准量msb的设计容差avb内,但不对准量mst在y方向上的两个端部处偏离不对准量mst的设计容差avt。

[0069]

图3ba是示意性地图解说明其中接触件c4相对于插塞ch的不对准得到100%校正的光掩模的俯视图以及在使用光掩模的情形中形成的每一结构的俯视图及横截面图的图解。

[0070]

如图3ba中所图解说明,光掩模上用于形成配线d2的配线图案d2p及光掩模上用于形成插塞ch的插塞图案chp在一个平面pn中在y方向上按照基本上相等的间隔布置。此外,在这些光掩模上,配线图案d2p之间的间隔以及插塞图案chp之间的间隔基本上相等。

[0071]

另一方面,根据实际半导体装置1中的衬底sb上的插塞ch的位置100%校正光掩模上用于形成接触件c4的接触件图案c4p。在此情形中,接触件图案c4p的校正量被设定成与在未执行校正的情形中接触件c4与插塞ch之间的不对准量基本上匹配。

[0072]

插塞ch的位置可基于设计数据来确定,且可视需要基于从半导体装置1的原型等获得的统计值或考虑到可出现在半导体装置1中的应力的模拟值来估计。

[0073]

通过相对于插塞ch的位置100%校正接触件图案c4p,随着朝向与平面pn在y方向上的两侧对应的位置,光掩模上的接触件图案c4p之间的间隔增大到大于其它光掩模上的配线图案d2p之间的间隔及插塞图案chp之间的间隔。

[0074]

如此一来,当叠加这些光掩模时,配线图案d2p与插塞图案chp的几何中心的位置在平面pn内在y方向上的任何位置处均基本上匹配,且仅接触件图案c4p的几何中心的位置在y方向上随着朝向在平面pn内在y方向上的两侧向外移位。

[0075]

当使用这些光掩模来在衬底sb上依序形成配线d2、接触件c4及插塞ch,由于接触件c4的位置经调整以与插塞ch的位置匹配,因此插塞ch连接到接触件c4在平面pn内在y方向上的整个位置上的基本上中心位置。

[0076]

然而,由于接触件c4根据插塞ch向外布置,因此随着朝向平面pn在y方向上的两个端部接触件c4与配线d2之间的不对准量增大。

[0077]

参考平面pn在y方向上的一个端部的a-a截面,尽管插塞ch连接到接触件c4的基本上中心位置,接触件c4的下端的一部分在y方向上向配线d2外侧偏离。

[0078]

图3bb是示意性地图解说明在使用其中接触件c4相对于插塞ch的不对准得到

100%校正的光掩模的情形中每一结构的不对准量的图形。

[0079]

如图3bb中所图解说明,接触件c4与插塞ch之间的不对准量mst在平面pn上在y方向上的整个位置上具有最低值。然而,接触件c4与配线d2之间的不对准量msb朝向平面pn内在y方向上的两个端部增大,且极大地偏离在y方向上的两个端部处的不对准量msb的设计容差avb。

[0080]

图3ca是示意性地图解说明接触件c4相对于插塞ch的不对准得到40%校正的光掩模的俯视图以及在使用光掩模情形中形成的每一结构的俯视图及横截面图的图解。

[0081]

如图3ca中所图解说明,光掩模上用于形成配线d2的配线图案d2p及光掩模上用于形成插塞ch的插塞图案chp在一个平面pn中在y方向上按照基本上相等的间隔布置,且配线图案d2p之间的间隔及插塞图案chp之间的间隔基本上相等。

[0082]

另一方面,光掩模上用于形成接触件c4的接触件图案c4p布置在相对于实际半导体装置1中的衬底sb上的插塞ch的位置而被校正的位置处,其中校正因子不到100%。

[0083]

通过相对于插塞ch的位置校正接触件图案c4p不到100%,掩模上的接触件图案c4p之间的间隔小于在上述100%校正情形中的间隔且随着朝向平面pn在y方向上的两个端部而增大到大于其它光掩模上的配线图案d2p之间的间隔及插塞图案chp之间的间隔。

[0084]

在图3ca的实例中,接触件图案c4p相对于插塞ch的校正因子被设定为例如40%。在接触件图案c4p相对于插塞ch被校正达例如40%的情形中,接触件图案c4p的校正量被设定为在未执行校正的情形中接触件c4与插塞ch之间的不对准量的40%。

[0085]

在用于形成图3aa、3ba及3ca中所图解说明的接触件c4的光掩模当中,图3ca中所图解说明的光掩模对应于第一实施例的光掩模。

[0086]

当使用图3ca中所图解说明的这些光掩模在衬底sb上依序形成配线d2、接触件c4及插塞ch时,尽管接触件c4的中心位置与塞ch的中心位置在平面pn内在y方向上的整个位置上不是完全对准,但可避免接触件c4极大地偏离配线d2。

[0087]

参考平面pn在y方向上的一个端部的a-a截面,插塞ch连接到在y方向上从接触件c4的中心位置稍微向外移位的位置,且接触件c4的整个下端连接到配线d2。

[0088]

图3cb是示意性地图解说明在使用其中接触件c4的不对准被校正40%的光掩模的情形中每一结构的不对准量的图形。

[0089]

如图3cb中所图解说明,在平面pn内y方向上的整个位置上,接触件c4与配线d2之间的不对准量msb及接触件c4与插塞ch之间的不对准量mst分别处于容差avb及容差avt内。

[0090]

如此一来,代替通过100%校正将接触件c4相对于插塞ch完全对准,通过按照不到100%的预定校正因子将接触件c4相对于插塞ch对准,接触件c4与配线d2之间的不对准量及接触件c4与插塞ch之间的不对准量两者皆可保持在容差内。

[0091]

另外,在上文所描述的图3ab、3bb及3cb中,结构之间在y方向上的不对准量的改变由线性图形表示,但所述图形中的每一者仅是示意图形。因此,结构之间的不对准量并不是始终皆线性地改变,且即使在此情形中,仍可使用以上校正方法。

[0092]

将更详细地描述上文所描述的执行校正不到100%的方法。

[0093]

在以上说明中,说明已聚焦于平面pn内y方向上的不对准校正,但以上方法也可适用于x方向上的不对准校正。因此,接下来,将描述在相对于插塞ch的位置(x,y)校正接触件c4达不到100%的预定比率α(α《1)的情形中的校正量δd(x,y),插塞ch的位置(x,y)是由平

面pn内的x坐标及y坐标表示。

[0094]

在此,比率α是基于例如实际衬底sb上的接触件c4与配线d2之间的不对准量、实际衬底sb上的接触件c4与插塞ch之间的不对准量、不对准量中的每一者的容差值等来确定。在一些情形中,不对准量、不对准趋势等在平面pn中的x方向与y方向之间是不同的。在此情形中,可针对x方向及y方向使用不同比率α。

[0095]

此外,在其中接触件c4相对于插塞ch的位置(x,y)被100%校正的情形中的校正量δd0(x,y)小于阈值δdth的情形中,期望不实施以上校正。阈值δdth是基于接触件c4与插塞ch之间的不对准量的设计容差的值等来确定。

[0096]

在接触件c4相对于插塞ch被100%校正时的校正量δd0(x,y)等于或大于阈值δdth(即当δd0(x,y)≥δdth)的情形中,通过将超过阈值δdth的不对准量乘以比率α获得的值被界定为实际校正量δd(x,y)。具体来说,例如由以下方程式(1)表达此时的校正量δd(x,y)。

[0097]

δd(x,y)=δdth α(δd0(x,y)-δdth)

ꢀꢀ

(1)

[0098]

然而,上文所描述的方程式(1)可为高阶方程。可通过依据高阶方程获得校正量δd(x,y)来进行更精确校正。

[0099]

此外,根据方程式(1),无论上文所描述的图3cb的实例如何,平面pn内可存在执行不对准校正的区及不执行不对准校正的区。即,在平面pn内存在在接触件c4相对于插塞ch得到100%校正时的校正量δd0(x,y)小于阈值δdth(δd0(x,y)《δdth)的区的情形中,不执行所述区中相对于接触件c4的不对准校正。图3da及3db中图解说明实例。

[0100]

在图3db中所图解说明的实例中,区处于在平面pn内在y方向上从中心朝向端部的预定距离内的区是不执行不对准校正的区,原因在于校正量δd0(x,y)小于阈值δdth。如上文所描述,阈值δdth是基于例如接触件c4与插塞ch之间的不对准量mst的设计容差avt的值等来确定。因此,在校正量δd0(x,y)小于阈值δdth的情形中,即使在不执行校正的情形中仍可抑制不对准量mst超过容差avt。

[0101]

另一方面,平面pn内在y方向上从所述预定距离到端部的区是执行不对准校正的区,原因在于校正量δd0(x,y)等于或大于阈值δdth。由于接触件c4相对于插塞ch的不对准得到校正,因此在平面pn内在y方向上从中心到端部往往会上升的不对准量mst的斜度变得缓和。另一方面,在平面pn内在y方向上从中心到端部也往往会上升的不对准量msb的斜度变得更陡。通过以此方式校正接触件的不对准,如图3da中所图解说明,接触件c4与插塞ch之间的连接及接触件c4与配线d2之间的连接即使在平面pn内在y方向上的端部处也得以保全。

[0102]

如上文所描述,在平面pn内存在执行不对准校正的区及不执行不对准校正的区两者的情形中,在所述区之间的边界处,接触件c4的不对准量mst及msb(即,接触件c4的几何中心与插塞ch的几何中心之间的距离及接触件c4的几何中心与配线d2的几何中心之间的距离两者)具有改变趋势不连续的不连续点dst及dsb。这些不连续点dst及dsb出现在平面pn内在y方向上校正量δd0(x,y)与阈值δdth相等(δd0(x,y)=δdth)的位置附近。然而,改变趋势的不连续性并不意味着几何中心的距离从增大趋势改变为减小趋势或从减小趋势改变为增大趋势。即,举例来说,改变趋势的增大或减小在平面pn内在y方向上的中心位置处反转,但此处所描述的不连续点不包含此点。

[0103]

另外,在以上说明中,相对于上层上的插塞ch校正下层上的接触件c4的位置,但可相对于下层上的配线d2校正上层上的接触件c4的位置达预定比率α。

[0104]

在使用上文所描述的方程式(1)形成接触件c4的情形中,第一实施例的半导体装置1具有以下配置中的至少一者。

[0105]

即,接触件c4与配线d2之间的不对准量和接触件c4与插塞ch之间的不对准量具有关联。即,接触件c4与配线d2之间的不对准量及接触件c4与插塞ch之间的不对准量随着朝向平面pn的外侧而一起增大。

[0106]

在此情形中,举例来说,在预定方向(例如,x方向或y方向)上的两个位置处,对接触件c4与配线d2之间的不对准量进行比较的量值关系、量值比率等与对接触件c4与插塞ch之间的不对准量进行比较的量值关系、量值比率等具有关联。

[0107]

在此,预定方向上的所述两个位置可任意选择,且举例来说在平面pn内,可选择平面pn的中心位置及端部的位置。然而,在跨越平面pn选择两个位置的情形中,假定选择除在平面pn之间彼此对应的位置之外的位置,而非例如平面pn的中心位置等相同位置。

[0108]

另外,在接触件c4与配线d2之间及接触件c4与插塞ch之间出现预定不对准量。即,举例来说,如图3ba及3bb中所图解说明,在相对于插塞ch 100%地校正接触件c4的情形中,接触件c4与插塞ch之间的不对准量例如应为基本上零。另一方面,在不到100%地执行以上校正的情形中,接触件c4与配线d2之间的不对准量及接触件c4与插塞ch之间的不对准量两者均具有除零之外的预定值。

[0109]

此外,如上文所描述,在接触件c4相对于插塞ch的校正量是40%等且接触件c4相对于配线d2的对准准确性的比重增大的情形中,接触件c4与配线d2之间的不对准量被设定为处于更有限范围内,且接触件c4与插塞ch之间的不对准量往往会随着朝向平面pn的外侧而增大。

[0110]

然而,除受应力影响的不对准量之外,接触件c4与配线d2之间的不对准量及接触件c4与插塞ch之间的不对准量还可包含由于例如不同光刻过程等之间的覆叠(重叠)不对准等过程所致的不对准量。

[0111]

上文所描述的接触件c4与配线d2之间的位置关系、接触件c4与插塞ch之间的位置关系等可以是在对接触件c4的上端、配线d2的上表面及插塞ch的上端进行比较的情形中的位置关系。

[0112]

另外,在一个最小单元ru内,与在多个接触件c4不仅布置在x方向上而且布置在y方向上的情形中一样,在多个结构布置在一个最小单元ru中的情形中,上文所描述的几何中心的位置可以是最小单元ru的所述多个结构的整个的几何中心的位置。

[0113]

此外,在使用上述校正方法中的方程式(1)形成接触件c4的情形中,第一实施例的光掩模具有例如下文在图4a及4b中所图解说明的配置。

[0114]

图4a及4b是图解说明在形成根据第一实施例的半导体装置1的接触件c4时使用的光掩模10的配置的实例的示意图。图4a是光掩模10的沿着y方向的横截面图,且图4b是光掩模10的部分放大横截面图。图4a及4b中的y方向与上述半导体装置1的y方向一致。

[0115]

如图4a中所图解说明,光掩模10包含作为掩模衬底的透明衬底ts及形成在透明衬底ts上的不透明膜sd。当使用光掩模10时,将透明衬底ts的上面形成有不透明膜sd的表面定向成朝向衬底sb上的光致抗蚀剂膜,且然后从透明衬底ts侧施加曝光光。

[0116]

透明衬底ts是由例如石英制成。在此,“透明”意指至少对具有曝光光的波长的光透明,且更具体来说,意指曝光光的透射可达到足以使在光致抗蚀剂膜等暴露于所述光的程度。

[0117]

不透明膜sd由例如铬等组成,且在使光致抗蚀剂膜等不暴露于光的程度上阻挡曝光光。

[0118]

如图4b中所图解说明,光掩模10的不透明膜sd具有作为布置在y方向上的第一图案的多个接触件图案c4p。每一接触件图案c4p具有上文所描述的接触件c4的横截面形状,且是设置在不透明膜sd中的穿孔。使用曝光光穿过穿孔对形成在堆叠主体lm上的光致抗蚀剂膜进行辐射,且将所述部分中的光致抗蚀剂膜暴露于光且移除。通过对移除光致抗蚀剂膜等而暴露出的堆叠主体lm执行蚀刻处理,在堆叠主体lm中形成用于形成接触件c4的孔。

[0119]

图4b图解说明光掩模10的与在例如一个平面pn(即一个堆叠主体lm)在y方向上的中心附近的部分对应的区段。在一个平面pn内,对应于布置在y方向上的多个最小单元ru在y方向区段上各自具有一个接触件c4的事实,不透明膜sd的多个接触件图案c4p也以预定距离布置在y方向上。包含一个接触件图案c4p且对应于衬底sb上的两个接触件li之间的区的每一区是光掩模10中的最小单元rup。

[0120]

在此,在对应于一个平面pn的光掩模10的区内,作为一个接触件图案c4p的中心点的几何中心cgc与邻近所述一个接触件图案c4p的接触件图案c4p的几何中心cgc之间的距离(即,邻近接触件图案c4p的几何中心之间的距离pta、ptb)随着在y方向上朝向外侧而增大。即,pta《ptb《

…

.

[0121]

根据上文所描述的方程式(1),光掩模10上的校正量δd(x,y)包含将超过阈值δdth的不对准量乘以比率α而获得的值α(δd0(x,y)-δdth)。此外,在图3aa的上述实例中,在不执行不对准校正的情形中,插塞ch之间的间隔大于接触件c4之间的间隔。因此,光掩模10上的校正量δd(x,y)随着在平面pn内在y方向上朝向外侧而增大,且几何中心之间的距离pta、ptb、...具有上述关系。

[0122]

因此,举例来说,在光掩模10中,邻近接触件图案c4p的几何中心之间的距离在y方向上的两个位置之间是不同的。在此,可任意选择y方向上的两个位置,且只要所述两个位置处于与光掩模10的平面pn对应的区内即可,可选择区的中心位置及端部的位置。然而,在跨越平面pn的区中选择两个位置的情形中,假定选择除在区之间彼此对应的位置之外的位置,而不是例如区的中心位置等相同位置。

[0123]

此外,在对用于形成配线d2的光掩模及用于形成插塞ch的光掩模与光掩模10进行比较时,在光掩模上配线图案d2p的几何中心之间的距离、插塞图案chp的几何中心之间的距离及接触件图案c4p的几何中心之间的距离在平面pn内的中心位置附近的区中基本上相等。另一方面,随着在y方向上朝向两个端部,接触件图案c4p的几何中心之间的距离增大到大于其它图案的几何中心之间的距离。

[0124]

所属领域的技术人员明了,第一实施例的配置并不仅限于使用作为在光学光刻中用于在透明衬底ts上形成不透明膜sd的典型光掩模的上述二元掩模的情形。

[0125]

在光学光刻中,可使用相移掩模代替二元掩模。相移掩模具有如下结构:作为不透明膜的替代,在透明衬底上形成基于适当光学设计的半透明膜。可在通过适当地设计并制造出半透明膜的光学特性及膜厚度(例如,复折射率)而使光刻的曝光过程余裕大于二元掩

模的曝光过程余裕的情形中选择相移掩模。

[0126]

此外,可使用极紫外线(euv)光刻来代替使用紫外线或深紫外线执行曝光的光学光刻。当前euv光刻的波长在软x射线区中是13.5nm,且不存在适当透明衬底。为此,euv光刻使用利用多层堆叠在透明衬底上的金属氧化物膜的多重干涉的反射光掩模。典型结构是不透明膜图案形成在金属氧化物膜的多层堆叠膜上的结构。在必要时,可使用在不透明膜之间挖蚀出多层膜的结构。尽管反射光学系统用作以上光掩模及曝光设备的光学系统,但euv光刻通常也被视为一种类型的光学光刻。

[0127]

此外,可使用纳米压印光刻(nil)技术来代替光学光刻技术。在nil中,使用在表面上挖蚀出图案的模具,且具体来说在模具与衬底之间填充可固化材料且冲压所述可固化材料。在通过光或热量将可固化材料固化之后移除模具,且在衬底表面上形成图案。使用固化材料图案作为处理掩模来处理衬底的点与在光学光刻中相同等。

[0128]

此外,在电子束光刻中,可根据第一实施例的配置的用途来校正每一图案的图式数据位置。

[0129]

如上文所描述,在以上说明中,光学光刻的二元掩模可被视为光学光刻的相移掩模、euv光刻的反射光掩模及nil的模具。此外,也在电子束光刻中,可针对第一实施例的配置的用途来处置图式数据。

[0130]

在半导体装置(例如,三维非易失性存储器)中,阶层(例如,多个层布置成高堆叠的结构的混合物)之间在机械强度及残余应力上可存在差异,且差异可积累。为此,举例来说,由于在平面内根据平面上的位置的失真及不同光刻过程之间应力的改变,布置在不同阶层中的结构之间可出现不对准。在这些结构互连的情形中,可能会出现不良连接。

[0131]

因此,为抑制布置在上部阶层及下部阶层中的结构的不良连接,举例来说,在一些情形中,根据上层的结构或下层的结构对布置在中间层中的结构执行不对准校正。

[0132]

然而,在仅根据上层的结构或仅根据下层的结构对中间层的结构执行校正的情形中,可出现另一结构的不良连接。在增大上层及下层中的任一者的结构的连接表面的面积以维持上阶层及下阶层两者的连接的情形中,可增大平面的面积且可增大半导体装置的大小。

[0133]

根据第一实施例的半导体装置1,在最小单元ru中,接触件c4的几何中心与配线d2的几何中心之间的距离及接触件c4的几何中心与插塞ch的几何中心之间的距离中的每一者在y方向上的任何两个位置之间是不同的。即,根据第一实施例的半导体装置1,按照不到100%的校正因子相对于配线d2或插塞ch的位置来校正接触件c4的位置。

[0134]

因此,可抑制布置在不同阶层中的结构之间的不良连接。此外,举例来说,由于可在不增大配线d2等的大小的情况下抑制不良连接,因此可减小半导体装置1的大小。

[0135]

在上述第一实施例中,不到100%执行校正的上述方法已应用于半导体装置1中的穿透接触件区tpc及tpw中的接触件c4、配线d2及插塞ch的连接结构、外围区pr中的接触件c3、配线d2及插塞vy的连接结构等。然而,上述方法可应用于其它结构,只要结构是接到布置在上部阶层及下部阶层中的两个结构的结构即可。

[0136]

举例来说,将给出其它半导体装置的实例。在半导体装置中,举例来说采用以下配置:举例来说,堆叠有字线的堆叠主体布置在衬底上,且在堆叠主体的外侧上被绝缘层覆盖直到堆叠主体的上表面的高度位置的外围电路与堆叠主体布置在同一阶层中。在此情形

中,第一实施例的上述方法可应用于通过穿透绝缘层形成且连接上层配线与包含在外围电路中的晶体管的栅极或作用区域的接触件。

[0137]

由于应力在被接触件穿透的绝缘层与布置在同一阶层中的堆叠主体之间产生,因此可通过应用上述方法来抑制接触件与栅极或作用区域之间的不良连接及接触件与上层配线之间的不良连接。

[0138]

在此,在第一实施例的结构应用于布置在平面pn之外的区中的连接结构(例如,半导体装置1的接触件c3及连接上层配线与另一半导体装置的外围电路的接触件)的情形中,以上说明中的平面pn可被视为具有布置在外围区pr中的接触件c3、外围电路cua等添加到平面pn的配置的上述独立操作元件。

[0139]

此外,在上述第一实施例中,在穿透接触件区tpc及tpw中,绝缘区nr是通过阻止使用字线wl替换牺牲层而形成。然而,在堆叠主体中保全绝缘区的方法并不仅限于此。举例来说,在与绝缘区对应的区中,也可在使用字线wl替换之前对堆叠主体进行挖蚀并在其中嵌置绝缘层(例如,氧化硅层)来在堆叠主体中形成绝缘区。另一选择为,代替形成绝缘区nr,可使用厚绝缘层覆盖接触件c4的导电部件的外周界以将接触件c4与周围的字线wl等绝缘。

[0140]

(第一修改实例)

[0141]

接下来,将参考图5a及5b描述第一实施例的第一修改实例的半导体装置。在以下第一修改实例中,将通过一些实例描述确定比率α的方法。

[0142]

图5a及5b是图解说明根据第一实施例的第一修改实例的半导体装置的平面布置的一些实例的图解。图5a图解说明在一个半导体装置中平面在y方向上是平移对称布置的情形的实例。图5b是在一个半导体装置中平面在y方向上是镜像对称且平移对称布置的情形的实例。

[0143]

在图5a的实例中,第一修改实例的半导体装置包含在半导体装置的芯片区cpa内的16个平面。四个芯片区cpa构成一个投射区sha,且在半导体装置的制造过程中,将包含四个芯片区cpa中所包含的总共64个平面的区共同地曝光及显影。

[0144]

在一个投射区sha内的y方向上,举例来说,往往由于收缩应力而缩小的堆叠主体lm及往往由于拉伸应力而扩张的外围区pr交替地布置,且平面成平移对称地布置,即在y方向上周期性地布置。

[0145]

因此,在图5a中所图解说明的第一修改实例的半导体装置中,可在一个投射区sha内在整个y方向上使用例如恒定比率α执行不对准校正。

[0146]

注意,多个对准标记mkd、mkr、mks、mkc、mkh等布置在例如一个投射区sha内的四个拐角处。这些对准标记mkd、mkr、mks、mkc及mkh用于在将用于形成预定结构的图案转移到抗蚀剂膜时使光掩模与衬底sb之间对准。

[0147]

对准标记mkd是用于形成配线d2的标记,对准标记mkr是用于形成柱状部分hr的标记,对准标记mks是用于形成接触件li的标记,对准标记mkc是用于形成接触件c4的标记,且对准标记mkh是用于形成插塞ch的标记。

[0148]

如此一来,例如针对一个光掩模在衬底sb上逐个形成对准标记mkd、mkr、mks、mkc及mkh。

[0149]

也在图5b的实例中,第一修改实例的半导体装置包含半导体装置的芯片区cpb内的16个平面,且四个芯片区cpb构成一个投射区shb。

[0150]

在一个投射区shb内的y方向上,所述平面被布置成在每一行中上下镜像对称。即,在y方向上彼此邻近的两个堆叠主题lm及在y方向上彼此邻近的两个外围区pr交替地布置。

[0151]

因此,在图5b中所图解说明的第一修改实例的半导体装置中,考虑应力平衡根据一个投射区shb内y方向上的位置而不同。在此情形中,可根据一个投射区shb内或一个平面内在y方向上的位置而使比率α的值有所偏倚。即,举例来说,可针对两个堆叠主体lm彼此邻近的一侧上的端部及邻近外围区pr的一侧上的端部设定不同的比率α

in

及α

out

。

[0152]

(第二修改实例)

[0153]

接下来,将参考图6描述第一实施例的第二修改实例的半导体装置。在第二修改实例的半导体装置中,与上文所描述的第一实施例的半导体装置1中的区不同的区是最小单元。

[0154]

在上述第一实施例中,已描述两个接触件li之间的区是y方向上的最小单元ru的实例,但可根据半导体装置的各种配置的布置改变与最小单元对应的配置。

[0155]

图6是图解说明根据第一实施例的第二修改实例的半导体装置的最小单元rux的实例的图解。如图6中所图解说明,在第二修改实例的半导体装置中,其中有四个区rua及rub布置在y方向上而所述四个区rua及rub中的每一者位于两个接触件li之间的区对应于最小单元rux。

[0156]

第二修改实例的半导体装置在两个接触件li之间包含配置str-a、配置str-b及配置str-ca或str-cb。在这些配置在x方向上的布置次序在每一者位于两个接触件li之间的区rua及rub中有所不同的情形中,在具有跨越一个接触件li布置的配置的情形等,有多个区布置在y方向上而所述多个区中的每一者位于两个接触件li之间的区可以是最小单元。

[0157]

在第二修改实例的半导体装置中,在区rua中,配置是从纸张的右侧开始按照配置str-a、配置str-b及配置str-ca或str-cb的次序布置。另一方面,在区rub中,配置是从纸张的右侧开始按照配置str-a、配置str-ca或str-cb及配置str-b的次序布置。另外,配置str-ca及str-cb是跨越一个接触件li布置。

[0158]

因此,在第二修改实例的半导体装置中,布置在y方向上的四个区rua、rua、rub及rub构成一个最小单元rux。

[0159]

因此,在第一实施例的校正方法应用于第二修改实例的半导体装置的情形中,就上层、中间层及下层中的每一者的结构来说,在最小单元rux中,中间层的结构的几何中心与下层的结构的几何中心之间的距离及中间层的结构的几何中心与上层的结构的几何中心之间的距离中的每一者在y方向上的任何两个位置处是不同的。

[0160]

上述配置str-a可以是例如存储器区。配置str-b可以是例如穿透接触件区。配置str-ca及str-cb例如可以是布置在堆叠主体的中心区中而非端部中的阶梯区。在阶梯区布置在堆叠主体的中心区中的情形中,通过将堆叠主体挖蚀成类臼形状、将阶梯图案中的每一层的字线引出且通过接触件li将所述字线分离来使配置str-ca及str-cb跨越例如两个区rua及rua或两个区rub及rub布置。

[0161]

[第二实施例]

[0162]

在后文中,将参考图式详细描述第二实施例。第二实施例与第一实施例的不同之处在于对布置在同一阶层中的多个结构执行不对准校正。

[0163]

(半导体装置的配置实例)

[0164]

将引用上述第一实施例的图1a、1b及2来描述第二实施例的半导体装置。如所引用的图1a、1b及2中所图解说明,第二实施例的半导体装置也与上述第一实施例的半导体装置1具有例如相同的配置。

[0165]

然而,在第二实施例的半导体装置中,举例来说,用于形成作为第二结构的接触件li的狭缝及用于形成作为第一结构的接触件c4的孔在同一光学光刻过程中共同地形成。

[0166]

即,在第二实施例的半导体装置中,为形成接触件c4以及连接到接触件c4的上端及下端的作为第三结构的配线d2及作为第四结构的插塞ch,使用总共三种类型的光掩模(用于形成配线d2的光掩模、用于形成接触件c4及接触件li的光掩模及用于形成插塞ch的光掩模)。用于形成连接到接触件c4的插塞ch的光掩模也是用于形成作为第五结构及第六结构的分别连接到接触件li及柱pl的插塞ch的光掩模。

[0167]

在此时,如上文所描述,由于不对准,接触件c4可与配线d2及插塞ch具有不良连接。由于接触件li也连接到上文所描述的插塞ch,因此由于接触件li的不对准可出现与插塞ch的不良连接。此外,接触件li的不对准可造成存储器区mr中的接触件li与邻近柱pl之间接触。

[0168]

因此,在第二实施例的半导体装置中,举例来说,相对于插塞ch对接触件c4及接触件li两者执行不对准校正。

[0169]

在此,如上文所描述,由于柱pl的上表面连接到插塞ch,因此执行不对准校正以使得例如柱pl与插塞ch的几何中心的位置基本上彼此重叠。因此,通过校正接触件li相对于插塞ch的不对准,可间接校正接触件li与柱pl之间的不对准。

[0170]

(半导体装置的不对准校正的实例)

[0171]

图7aa到7cb是描述使用第二实施例的光掩模进行不对准校正的图解。图7aa到7cb的实例图解说明未校正接触件c4相对于插塞ch的位置的情形、接触件c4相对于插塞ch的位置被100%校正的情形及接触件c4相对于插塞ch的位置被校正40%的情形。

[0172]

在以下说明中,为将接触件c4与接触件li彼此区分开,将与接触件li相关的配置描述为狭缝st。这是由于将光掩模上的狭缝图案stp转移到堆叠主体lm以形成狭缝st,且填充狭缝st以形成接触件li。

[0173]

此外,在图7aa到7cb中,在未校正接触件c4相对于插塞ch的位置的情形、接触件c4相对于插塞ch的位置被100%校正的情形及接触件c4相对于插塞ch的位置被校正40%的情形中,光掩模上的配线图案d2p、接触件图案c4p及插塞图案chp的配置以及衬底sb上的配线d2、接触件c4及插塞ch当中的的位置关系及不对准量与上述第一实施例的图3aa到3cb的实例中的配置以及位置关系及不对准量相同。

[0174]

因此,在以下说明中,将主要描述光掩模上的接触件图案c4p与狭缝图案stp之间的位置关系以及衬底sb上的接触件c4与狭缝st之间的位置关系及不对准量。

[0175]

图7aa是示意性地图解说明未校正接触件c4及狭缝st相对于插塞ch的不对准的光掩模的俯视图以及在使用光掩模的情形下形成的每一结构的俯视图及横截面图的图解。在图7aa中,光掩模及每一结构的俯视图在垂直方向上从上侧开始示意性地图解说明平面pn内在y方向上的一个端部、平面pn内的中心部分及平面pn内在y方向上的另一端部的状态。

[0176]

如图7aa中所图解说明,在用于形成接触件c4及狭缝st的光掩模中,类似于接触件图案c4p,狭缝图案stp在一个平面pn中也以基本上相等的间隔布置在y方向上,且狭缝图案

stp的几何中心的位置也与配线图案d2p及插塞图案chp的几何中心的位置基本上匹配。

[0177]

在此,与光掩模中的最小单元ru对应的区内包含两个狭缝图案stp。因此,狭缝图案stp的几何中心的位置是整个的两个狭缝图案stp的几何中心的位置。即,两个狭缝图案stp的几何中心的位置是所述两个狭缝图案stp在y方向上的中心位置。

[0178]

当使用这些光掩模来在衬底sb上依序形成配线d2、接触件c4、狭缝st及插塞ch时,由于接触件c4及狭缝st布置在同一阶层中且具有基本上相同的不对准量,因此接触件c4及狭缝st相对于插塞ch的位置关系在平面pn内在y方向上的整个位置上基本上相等。

[0179]

参考平面pn在y方向上的一个端部的a-a截面,接触件c4在y方向上的两侧上的狭缝st相对于接触件c4基本上等距地布置,但相对于插塞ch不对准。

[0180]

图7ab是示意性地图解说明在使用未校正接触件c4及狭缝st相对于插塞ch的不对准的光掩模的情形中每一结构的不对准量的图形。图形的水平轴线是平面pn中的y坐标位置,且垂直轴线是在y方向上的不对准量。

[0181]

如图7ab中所图解说明,在平面pn内在y方向上的整个位置上,狭缝st与插塞ch之间的不对准量mss和接触件c4与插塞ch之间的不对准量mst基本上匹配。

[0182]

图7ba是示意性地图解说明接触件c4及狭缝st相对于插塞ch的不对准被100%校正的光掩模的俯视图以及在使用所述光掩模的情形中形成的每一结构的俯视图及横截面图的图解。

[0183]

如图7ba中所图解说明,根据实际半导体装置1中的衬底sb上的插塞ch的位置对用于形成接触件c4及狭缝st的光掩模上的接触件图案c4p及狭缝图案stp进行100%校正。

[0184]

因此,随着朝向与平面pn在y方向上的两侧对应的位置,在光掩模上接触件图案c4p之间的间隔及狭缝图案stp之间的间隔增大到大于在其它光掩模上配线图案d2p之间的间隔及插塞图案chp之间的间隔。

[0185]

如此一来,当将光掩模叠加时,配线图案d2p及插塞图案chp的几何中心的位置在平面pn内在y方向上的任何位置处皆基本上匹配,且随着朝向平面pn内在y方向上的两侧,接触件图案c4p及狭缝图案stp的几何中心的位置在y方向上向外移位。

[0186]

在此时,接触件图案c4p之间的间隔及狭缝图案stp之间的间隔相关地增大,且在一个最小单元ru内接触件图案c4p的几何中心的位置与狭缝图案stp的几何中心的位置之间的间隔平面pn中在整个y方向上基本上匹配。

[0187]

当使用这些光掩模来在衬底sb上依序形成配线d2、接触件c4、狭缝st及插塞ch时,由于调整接触件c4及狭缝st的位置以与插塞ch的位置匹配,因此插塞ch连接到接触件c4的基本上中心位置,且在平面pn内在y方向上的整个位置上的布置在一个最小单元ru内的两个狭缝st之间的基本上中心位置处。因此,认为插塞ch自身也在几乎不存在不对准的位置(未图解说明)处连接到接触件li。也认为狭缝st与柱pl之间的接触得到抑制。

[0188]

参考平面pn在y方向上的一个端部的a-a截面,插塞ch也布置在接触件c4及狭缝st的基本上中心位置处。

[0189]

图7bb是示意性地图解说明使用在接触件c4及狭缝st相对于插塞ch的不对准被100%校正的光掩模的情形中每一结构的不对准量的图形。

[0190]

如图7bb中所图解说明,狭缝st与插塞ch之间的不对准量mss在平面pn中y方向上的整个位置上具有最低值,这与接触件c4与插塞ch之间的不对准量mst类似。

[0191]

图7ca是示意性地图解说明接触件c4相对于插塞ch的不对准被校正40%的光掩模的俯视图以及在使用所述光掩模的情形中形成的每一结构的俯视图及横截面图的图解。另一方面,举例来说,由于狭缝st与柱pl之间的不对准量的容差是小的,因此对狭缝st相对于插塞ch的不对准进行100%校正。

[0192]

如图7ca中所图解说明,根据实际半导体装置1中的衬底sb上的插塞ch的位置对用于形成接触件c4及狭缝st的光掩模的狭缝图案stp进行100%校正。

[0193]

因此,随着朝向与平面pn在y方向上的两侧对应的位置,光掩模上的狭缝图案stp之间的间隔增大到大于根据实际半导体装置1中的衬底sb上的插塞ch的位置而被校正了不到100%的接触件图案c4p之间的间隔。

[0194]

如此一来,随着朝向平面pn内在y方向上的两侧,狭缝图案stp的几何中心的位置在y方向上向外移位得要比接触件图案c4p的几何中心的位置多。因此,随着朝向平面pn在y方向上的两侧,在一个最小单元ru内接触件图案c4p的几何中心与狭缝图案stp的几何中心之间的距离增大。

[0195]

在用于形成图7aa、7ba及7ca中所图解说明的接触件c4及狭缝st的光掩模当中,图7ca中所图解说明的光掩模对应于第二实施例的光掩模。

[0196]

当使用图7ca中所图解说明的这些光掩模来在衬底sb上依序形成配线d2、接触件c4、狭缝st及插塞ch时,尽管接触件c4的中心位置与插塞ch的中心位置在平面pn内在y方向上的整个位置上不完全匹配,但狭缝st的中心位置与插塞ch的中心位置在平面pn内在y方向上的整个位置上基本上匹配。

[0197]

参考平面pn在y方向上的一个端部的a-a截面,插塞ch在y方向上从接触件c4的中心位置稍微向外移位,但布置在最小单元ru中的两个狭缝st的基本上中心处。

[0198]

图7cb是示意性地图解说明在使用接触件c4相对于插塞ch的不对准被校正40%且狭缝st相对于插塞ch的不对准被100%校正的光掩模的情形中每一结构的不对准量的图形。

[0199]

如图7cb中所图解说明,狭缝st与插塞ch之间的不对准量mss在平面pn中在y方向上的整个位置内具有最低值。

[0200]

另外,在上文所描述的图7ab、7bb及7cb中,结构在y方向上的不对准量的改变由线性图形表示,但所述图形中的每一者仅是示意图形。

[0201]

如在第二实施例的校正方法中,可基于所述多个校正目标结构中的每一者的不对准的容差而以不同的校正量校正多个校正目标结构(例如,接触件c4及狭缝st)。更具体来说,基于上文所描述的方程式(1)校正接触件c4。方程式(1)中的比率α是小于1的数值。

[0202]

此外,在于相对于插塞ch对狭缝st进行100%校正时校正量δd0’

(x,y)等于或大于阈值δdth’的情形中,基于下文所描述的方程式(2)按照校正量δd’(x,y)对狭缝st进行校正。

[0203]

δd’(x,y)=δdth’ β(δd0’

(x,y)-δdth’)

ꢀꢀ

(2)

[0204]

在此,在上述实例中比率β是1,但更通常比率β可以是与比率α不同的小于1的数值(β≤1,α≠β)。比率β是基于例如实际衬底sb上的狭缝st与插塞ch之间的不对准量、实际衬底sb上的狭缝st与柱pl之间的不对准量及这些不对准量的容差值而确定。

[0205]

此外,正如在方程式(1)的情形中一样,上文所描述的方程式(2)可以是高阶方程。

此外,在平面pn内的x方向与y方向之间在不对准量、不对准趋势等方面有所不同的情形中,可针对x方向及y方向使用不同的比率β。

[0206]

使用上文所描述的方程式(1)形成接触件c4,以使得第二实施例的半导体装置也具有以下配置中的至少一者。

[0207]

即,接触件c4与配线d2之间的不对准量和接触件c4与插塞ch之间的不对准量具有关联。另外,接触件c4与配线d2之间及接触件c4与插塞ch之间出现除零之外的预定不对准量。

[0208]

使用上文所描述的方程式(1)形成接触件c4且使用上文所描述的方程式(2)形成狭缝st,以使得第二实施例的半导体装置具有以下配置中的至少一者。

[0209]

即,接触件c4与接触件li具有以下关系:使得一个最小单元ru内接触件c4的几何中心与接触件li的几何中心之间的距离随着朝向一个平面pn内在y方向上的两侧而增大。

[0210]

在此情形中,一个最小单元ru内接触件c4的几何中心与接触件li的几何中心之间的距离在预定方向(例如,x方向或y方向)上的在两个位置之间不同。在此,可任意选择预定方向上的所述两个位置,且举例来说在平面pn内可选择平面pn的中心位置及端部位置。然而,在跨越平面pn选择两个位置的情形中,假定选择除在平面pn之间彼此对应的位置之外的位置,而非例如平面pn的中心位置等相同位置。

[0211]

另外,通过相对于插塞ch将接触件c4校正不到100%且相对于插塞ch 100%地校正狭缝st,在一个最小单元ru内接触件c4的几何中心的位置与接触件li的几何中心的位置之间的不对准量基本上等于接触件c4与插塞ch之间的不对准量。

[0212]

然而,除受应力影响的不对准量之外,这些结构的不对准量可包含由于过程(例如,不同光刻过程之间的覆叠(重叠)不对准)所致的不对准量。

[0213]

如在第二实施例的半导体装置中,接触件c4与接触件li在同一光学光刻过程中共同地形成的事实可通过例如分析留在半导体装置上的对准标记来确定。

[0214]

即,在上文所描述的图5a及5b中所图解说明的对准标记mkd、mkr、mks、mkc、mkh等当中,接触件c4及接触件li的对准标记mkc与mks合在一起的事实可被视为接触件c4与接触件li是共同形成的证明。

[0215]

接触件c4与配线d2之间的位置关系、接触件c4与插塞ch之间的位置关系、接触件c4与接触件li之间的位置关系等可以是在对接触件c4的上端、配线d2的上表面、插塞ch的上端及接触件li的上端进行比较的情形中的位置关系。

[0216]

此外,由于一个最小单元ru内包含两个接触件li,因此接触件li的几何中心的位置是如上文所描述的整个两个接触件li的几何中心的位置。在一个最小单元ru内,甚至在多个其它结构布置在一个最小单元ru中的情形中,正如在多个接触件c4不仅布置在x方向上而且布置在y方向上的情形中一样,上文所描述的几何中心的位置可为其整个的所述多个结构的几何中心的位置。

[0217]

此外,在使用上文所描述的方程式(1)形成接触件c4且使用上文所描述的方程式(2)形成狭缝st的情形中,第二实施例的光掩模具有例如下文在图8a及8b中所图解说明的配置。

[0218]

图8a及8b是图解说明用于根据第二实施例的半导体装置的接触件c4及狭缝st的光掩模20的配置的实例的示意图。图8a是光掩模20沿着y方向的横截面图,且图8b是光掩模

20的部分地放大横截面图。图8a及8b中的y方向与第二实施例的半导体装置的y方向重合。

[0219]

此外,图8a及8b图解说明方程式(2)中的比率β大于方程式(1)中的比率α(β≤1,α《β)的情形的实例。即,假定狭缝st相对于插塞ch的不对准的校正量被设定为大于接触件c4相对于插塞ch的不对准的校正量。

[0220]

如图8a中所图解说明,光掩模20也包含透明衬底ts作为掩模衬底及形成在透明衬底ts上的不透明膜sd。

[0221]

如图8b中所图解说明,光掩模20的不透明膜sd具有布置在y方向上的多个接触件图案c4p作为第一图案及布置在y方向上的多个狭缝图案stp作为第二图案。接触件图案c4p是设置在不透明膜sd中的穿孔,且狭缝图案stp是在x方向上延伸且设置在不透明膜sd中的贯穿凹口。

[0222]

图8b图解说明光掩模20的与例如一个平面pn(即,一个堆叠主体lm)在y方向上的中心附近的部分对应的区段,且布置在y方向上的两侧上的两个狭缝图案stp之间的区对应于光掩模20中的最小单元rup,其中一个接触件图案c4p夹置在所述两个狭缝图案stp之间。

[0223]

在此,光掩模20中的接触件图案c4p的配置与上文所描述的第一实施例的光掩模10中的接触件图案c4p的配置相同。

[0224]

在光掩模20中,一个最小单元rup内的狭缝图案stp的几何中心cgs与邻近最小单元rup内的狭缝图案stp的几何中心cgs之间的距离(即,邻近最小单元rup内的狭缝图案stp的几何中心之间的距离ptm、ptn、

…

)在光掩模20的与一个平面pn对应的区内随着朝向y方向上的外侧而增大。即,ptm《ptn《

…

.

[0225]

此外,在一个平面pn内,狭缝图案stp的几何中心之间的距离ptm、ptn、

…

大于接触件图案c4p的几何中心之间的距离pta、ptb、

…

。即,pta《ptm,ptb《ptn

…

.

[0226]

因此,在衬底sb上,在一个最小单元rup内接触件图案c4p的几何中心cgc与狭缝图案stp的几何中心cgs之间的距离(即,接触件图案c4p的几何中心与狭缝图案stp的几何中心之间的距离dsa、dsb、dsc、...)在光掩模20的与平面pn对应的区内随着朝向y方向上的外侧而增大。即,dsa《dsb《dsc....

[0227]

因此,举例来说,在光掩模20中,接触件图案c4p的几何中心与狭缝图案stp的几何中心之间的距离在y方向上的两个位置之间是不同的。在此,可任意选择y方向上的两个位置,且只要所述两个位置位于与光掩模20的平面pn对应的区内即可,且可选择区的中心位置及端部位置。然而,在跨越平面pn的区中选择两个位置的情形中,假定选择除在区之间彼此对应的位置之外的位置,而不是例如区的中心位置等相同位置。

[0228]

此外,在用于形成配线d2的光掩模及用于形成插塞ch的光掩模与光掩模20之间进行比较时,在所述光掩模上配线图案d2p的几何中心的距离、插塞图案chp的几何中心的距离、接触件图案c4p的几何中心的距离及狭缝图案stp的几何中心之间的距离在平面pn内的中心位置附近的区中基本上相等。另一方面,随着朝向y方向上的两个端部,在其它光掩模上接触件图案c4p的几何中心之间的距离增大到大于其它图案的几何中心之间的距离,且随着朝向y方向上的两个端部狭缝图案stp的几何中心之间的距离增大到大于接触件图案c4p的几何中心之间的距离。

[0229]

第二实施例的配置并不仅限于上文所描述的二元掩模,且可适用于相移掩模、euv光刻的反射光掩模、nil的模具、用于电子束光刻的图式数据等。

[0230]

根据第二实施例的半导体装置,在最小单元ru中,接触件c4的几何中心与接触件li的几何中心之间的距离在y方向上的两个位置之间是不同的。即,根据第二实施例的半导体装置,相对于插塞ch的位置使用不同的比率α及β来校正接触件c4及接触件li。

[0231]

因此,可抑制布置在不同阶层中的结构之间的不良连接。此外,甚至在相对于共同连接目标(例如插塞ch)具有不同容差的结构(例如接触件c4及接触件li等)是共同地形成的情形中,可使用适合于相应结构的校正量执行不对准校正。

[0232]

根据第二实施例的光掩模20,在最小单元rup中,接触件图案c4p的几何中心与狭缝图案stp的几何中心之间的距离在y方向上的任何两个位置之间是不同的。因此,可抑制布置在不同阶层中的结构之间的不良连接,且可使用适合于相应结构的校正量执行不对准校正。

[0233]

在上述第二实施例中,在将连接到插塞ch的接触件c4与li是共同地形成的情形中,以不同的比率校正接触件c4及li。

[0234]

然而,在狭缝st被填充绝缘层等的结构是由与接触件c4共同形成的狭缝st形成的情形中,可应用以上校正方法。在此情形中,尽管由狭缝st形成的结构不连接到插塞ch,但期望抑制结构与相对于插塞ch的不对准得到校正的柱pl之间的接触,且优选地以预定比率校正结构相对于插塞ch的不对准。

[0235]

另外,在布置有接触件c4的绝缘区nr的两个端部处作为第二结构的板状部分br及在堆叠主体lm的外侧上作为第二结构的板状部分bp(参考图1a)中的一者或两者可在同一光学光刻过程中与接触件c4及接触件li一起共同形成。甚至在此情形中,可以不同的比率校正接触件li、板状部分br及板状部分bp的不对准。

[0236]

此外,接触件c4可与例如柱状部分hr在同一光学光刻过程中共同地形成。优选地抑制柱状部分hr与接触件li之间的接触,且优选地抑制柱状部分hr与阶梯区sr中的接触件cc之间的接触。因此,为抑制与这些接触件li及cc的接触,例如可按照预定比率校正柱状部分hr相对于插塞ch的不对准。

[0237]

此外,接触件c4可不仅是以上实例中的穿透接触件区tpc中的接触件c4,而且是布置在穿透接触件区tpw中的接触件c4。此外,以上校正方法甚至可适用于以下情形:取代接触件c4或除接触件c4之外,作为第二结构的上述接触件c3、接触件li及板状部分br及bp等是共同形成。在此情形中,在以上说明中的平面pn可被视为除平面pn之外还包含例如接触件c3等配置的独立操作元件。

[0238]

如上文所描述,第二实施例的校正方法可适用于例如以下情形:将连接到布置在上部阶层及下部阶层中的结构的结构与将连接到布置在上部阶层及下部阶层中的一者中的结构的结构在同一光学光刻过程中共同地形成。此外,第二实施例的校正方法可适用于例如以下情形:将连接到布置在上部阶层及下部阶层中的结构的结构与和同一阶层中的另一结构相距一定间隔布置的结构在同一光学光刻过程共同地形成。

[0239]

(修改实例)

[0240]

接下来,将使用图9aa到9bb描述第二实施例的修改实例的配置。修改实例的配置与上述第二实施例的不同之处在于在接触件c4及狭缝st当中,接触件c4的不对准未被校正且狭缝st的不对准得到校正。

[0241]

图9aa到9bb是描述使用第二实施例的修改实例的光掩模进行不对准校正的图解。

[0242]

图9aa及9ab图解说明接触件c4及狭缝st相对于插塞ch的不对准未被校正的情形的实例。

[0243]

如图9aa及9ab中所图解说明,接触件c4相对于配线d2及插塞ch不对准,但接触件c4的不对准量mst及msb处于设计容差avt及avb内。

[0244]

另一方面,狭缝st相对于插塞ch不对准,且狭缝st的不对准量mss超过设计容差avs。

[0245]

在此情形中,基于上文所描述的方程式(2)校正狭缝st的不对准,但可不校正接触件c4的不对准。

[0246]

图9ba及9bb图解说明接触件c4相对于插塞ch的不对准未被校正且狭缝st相对于插塞ch的不对准得到校正的情形的实例。在图9ba及9bb中,考虑到狭缝st与插塞ch之间的不对准量mss的容差avs,对狭缝st进行100%校正。

[0247]

在此工艺中,接触件c4与插塞ch之间的不对准量mst、接触件c4与配线d2之间的不对准量msb及狭缝st与插塞ch之间的不对准量mss全部均可分别处于容差avt、avb及avs内。

[0248]

在此工艺中所使用的光掩模中,相对关系(例如,狭缝图案的几何中心的距离、接触件图案的几何中心与狭缝图案的几何中心之间的距离等)类似于第二实施例的光掩模20中的相对关系。

[0249]

在通过此工艺制造的半导体装置中,相应配置(例如,接触件c4、狭缝st、插塞ch及配线d2)的相对位置关系类似于第二实施例的半导体装置中的相对位置。

[0250]

虽然已描述某些实施例,但这些实施例仅以实例方式呈现,且并不旨在限制本发明的范围。实际上,可以各种其他形式来体现本文中所描述的新颖实施例;此外,可在不背离本发明的精神的情况下对本文中所描述的实施例的形式做出各种省略、替代及改变。随附权利要求书及其等效内容旨在涵盖将归属于本发明的范围及精神内的此类形式或修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。