1.本发明有关于一种半导体结构及其形成方法,且特别有关于一种接触垫具有双重保护层的半导体结构及其形成方法。

背景技术:

2.在半导体结构的制造和封装过程中,半导体元件上方的金属层(例如最上层的金属层)包含多个裸露的区域以做为接触垫(bonding pads)。通过接触垫可将封装的半导体元件电连接至一外部电路。再者,一般在金属层上方还形成有抗反射涂层(anti-reflective coating layer),当金属层上方的光刻胶以光学光刻工艺进行图案化时,抗反射涂层可以减少来自金属层表面的反射光线。然而,存储和使用半导体结构的环境中存在着水气,水气可能通过裸露的这些接触垫而进入封装件,进而对于金属层及/或金属层上的抗反射涂层产生腐蚀,而影响制得半导体结构的电性表现以及可靠度(reliability)。

3.再者,随着集成电路(ic)不断的快速发展,为了符合消费者对于小型化电子装置的需求,装置中的半导体元件的尺寸下降,集成度(integration degree)也随之增加。半导体元件的尺寸下降,各材料层的厚度以及各部件之间的距离亦随之缩小,若是半导体元件的阻挡水气的能力不佳,在半导体元件使用之前(例如贩售之前的存储状态)和使用一段时间之后,水气进入半导体元件中所造成的腐蚀将更剧烈的影响半导体元件的电性表现与可靠度。

4.虽然现存的半导体结构及其形成方法可以应付它们原先预定的用途,但目前它们在结构和制法上仍有需要克服的问题。如何改良半导体结构,以避免上述情形的发生,且改良的半导体结构亦适合包含具有不同电子特性元件的电子装置的制作,对于相关业者而言实为一重要议题。

技术实现要素:

5.本发明的一些实施例揭示一种半导体结构,包括一基底、位于前述基底上方的一介电层、以及位于介电层上方的一导电层。一些实施例的半导体结构亦包括位于前述导电层上的一堆叠结构,且前述堆叠结构暴露出前述导电层的顶面的至少一区域。一些实施例的半导体结构中,前述堆叠结构包括位于前述导电层上方的一抗反射涂层(anti-reflective coating layer,arc layer)、位于前述抗反射涂层的上方的一第一保护层(first passivation layer)、以及位于前述第一保护层的上方的一第二保护层(second passivation layer),其中前述第二保护层更延伸至前述第一保护层的内侧边缘(inner edge)及前述抗反射涂层的内侧边缘,并覆盖前述第一保护层的前述内侧边缘及前述抗反射涂层的前述内侧边缘。

6.本发明的一些实施例揭示一种半导体结构的形成方法,包括提供一基底,以及形成一介电层于前述基底的上方。一些实施例中,半导体结构的形成方法亦包括形成一导电层于前述介电层的上方,以及形成一堆叠结构于前述导电层上,且前述堆叠结构暴露出前

述导电层的顶面的至少一接触垫区(bonding pad region)。根据本揭露的一些实施例,前述堆叠结构包括位于前述导电层上方的一抗反射涂层(arc layer)、位于前述抗反射涂层上方的一第一保护层(first passivation layer)、以及位于前述第一保护层的上方的一第二保护层(second passivation layer),其中前述第二保护层更延伸至前述第一保护层的内侧边缘(inner edge)及前述抗反射涂层的内侧边缘,并覆盖前述第一保护层的前述内侧边缘及前述抗反射涂层的前述内侧边缘。

7.本发明提出的半导体结构和形成方法具有许多优点,可借由形成双层的保护层,解决了传统半导体结构中因抗反射涂层受水气腐蚀而变色、析出使整体结构产生的缺陷的问题,进而大幅提升制得半导体结构的电性表现以及可靠度。再者,本发明的实施例所提出的半导体结构的形成方法,可以简单地完成半导体结构的制作,而且可以与现有工艺相容,并不会提升工艺复杂度或/及大幅增加生产成本,但又可明显提高制得半导体结构的电性表现以及可靠度。因此,本揭露实施例提出的半导体结构和形成方法极具应用价值。

附图说明

8.图1为根据本揭露的一些实施例的半导体结构中的一个接触垫区的上视图。

9.图2a、图2b、图2c、图2d、图2e、图2f、图2g是根据本揭露的一些实施例,显示形成如图1所示的半导体结构的各个中间阶段的剖面示意图。其中,图2a-图2g对应于图1的剖面线c-c所绘制。

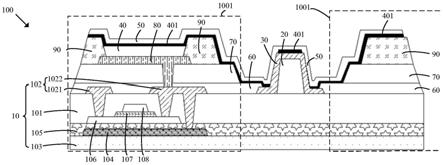

10.图3为根据本揭露的一些实施例的一种半导体结构的剖面示意图。

11.附图标记:

12.20:基底

13.21:晶体管

14.22:介电层

15.24:导电层

16.24a:导电层的顶面

17.241:第一导电层

18.242:第二导电层

19.243:第三导电层

20.26:抗反射涂层

21.260:抗反射材料层

22.26p:第一开口

23.26a:抗反射涂层的顶面

24.27:第一保护层

25.270:第一保护材料层

26.27p:第二开口

27.27a:第一保护层的顶面

28.28:第二保护层

29.280:第二保护材料层

30.28p:第三开口

31.26ei、27ei、28ei:内侧边缘

32.29:堆叠结构

33.31:图案化第一光刻胶层

34.311:第一光刻胶材料层

35.331:第一遮罩

36.32:图案化第二光刻胶层

37.332:第二遮罩

38.d1:第一内径

39.d2:第二内径

40.d3:第三内径

41.r

b:

接触垫区

42.r1:第一区域

43.r2:第二区域

44.t1,t2:厚度

45.g:栅极

46.gd:栅极介电层

47.s:源极

48.d:漏极

具体实施方式

49.以下揭露提供了许多的实施例或范例,用于实施所提供的半导体结构的不同元件。各元件和其配置的具体范例描述如下,以简化本发明实施例的说明。当然,这些仅仅是范例,并非用以限定本发明实施例。举例而言,叙述中若提及第一元件形成在第二元件之上,可能包含第一和第二元件直接接触的实施例,也可能包含额外的元件形成在第一和第二元件之间,使得它们不直接接触的实施例。此外,本发明实施例可能在不同的范例中重复参考数字及/或字母。如此重复是为了简明和清楚,而非用以表示所讨论的不同实施例之间的关系。

50.再者,在以下叙述中可使用空间上相关措辞,例如“在

……

之下”、“在

……

下方”、“下方的”、“在

……

上方”、“上方的”和其他类似的用语,以简化一元件或部件与其他元件或其他部件之间如图所示的关系的陈述。此空间相关措辞除了包含图式所描绘的方向,还包含装置在使用或操作中的不同方位。装置可以朝其他方向定位(旋转90度或在其他方向),且在此使用的空间相关描述可依此相应地解读。

51.以下描述实施例的一些变化。在不同图式和说明的实施例中,相似的元件符号被用来标明相似的元件。可以理解的是,在方法的前、中、后可以提供额外的步骤,且一些叙述的步骤可为了该方法的其他实施例被取代或删除。

52.本揭露内容的实施例提供了半导体结构及其形成方法。一些实施例中,借由形成双层的保护层以完全包覆金属层上方的抗反射涂层,可有效防止水气自金属层的接触垫区进入半导体结构中而造成抗反射涂层的腐蚀,进而提升制得半导体结构的电性表现以及可靠度(reliability)。

53.本揭露的半导体结构并不特别限制可应用的元件类型。在基底上形成的一个或多个集成电路元件(ic devices)可包含不同型态的半导体元件,包含平面式元件(planar device)和非平面式元件(non-planar device)。因此,平面式结构或是三维式结构(three-dimensionalstructure)的元件,例如金属氧化物半导体场效应晶体管,(mosfet),都可设置于本揭露一些实施例的基底中,而上方金属层的接触垫区(bonding pad region)可与前述元件完成电连接。

54.图1是根据本揭露的一些实施例的半导体结构中的一个接触垫区的上视图。在一些实施例中,于基底上完成半导体元件的制作,并且于后续堆叠绝缘层和导电层(例如金属层)之后,暴露出导电层的顶面的部分区域,以作为接触垫区(bonding pad region)rb,如图1所示。根据本揭露的一些实施例,利用双层的保护层设置于金属层的上方,如图1中示出的位于上方的保护层(即以下实施例提出的第二保护层28)的内侧边缘28ei以及位于下方的保护层(即以下实施例提出的第一保护层27)的内侧边缘27ei,以达到防止水气腐蚀的效果,进而增进半导体结构的电性表现与可靠度。

55.值得注意的是,图1中仅示出一个六角形的接触垫区rb,但此仅为其中一示例,应用的半导体结构中可包含多个接触垫区rb,且实施例的接触垫区rb的俯视形状和排列方式并不特别限制,而是依实际应用的需求做相应的变化和调整。

56.图2a-图2g是根据本揭露的一些实施例,显示形成如图1所示的半导体结构的各个中间阶段的剖面示意图。图2a-图2g例如是对应于图1的剖面线c-c所绘制的工艺各阶段的剖面示意图。再者,为简化图式以利清楚说明,图2a-图2g是绘制关于一半导体结构中,根据本揭露的一些实施例的一个接触垫区的形成双层保护层的制造方法。

57.请参照图2a,提供一基底20。基底20上可形成有一或多个集成电路元件(未示出),前述集成电路元件例如包含晶体管,并以一介电层22覆盖前述集成电路元件。为简化图式以利清楚说明,图2a-图2g中仅示出基底20与基底20上的介电层22。在一些实施例中,基底20的材料可包含硅、砷化镓、氮化镓、硅化锗、绝缘层上覆硅、其他合适的材料或前述的组合。

58.接着,在一些实施例中,于介电层22的上方形成导电层24,导电层24可以是单层或多层的导电结构,且可以是包含金属的材料层(metal-containing layers)。为简化图式以利清楚说明,图2a-图2g中仅示出单层的导电层24,但本揭露并不以此为限制。一些实施例中,导电层24包含铝(aluminum,al)、铜(copper,cu)、钛(titanium,ti)、氮化钛(titanium nitride,tin)、前述材料的组合、或其他类似材料。

59.然后,于导电层24的上方形成一抗反射材料层(anti-reflective material layer)260。一些实施例中,抗反射材料层260包含钛(ti)、氮化钛(titanium nitride,tin)、氮化钽(tantalum nitride,tan)、钨钛(titanium tungsten,tiw)、前述材料的组合、或其他类似材料。于一些实施例中,抗反射材料层260可由原子层沉积(atomic layer deposition,ald)、化学气相沉积(chemical vapor deposition,cvd)、物理气相沉积(physical vapor deposition,pvd)、溅射、或类似工艺形成。

60.之后,于抗反射材料层260上方形成第一保护材料层(first passivation material layer)270,并且对第一保护材料层270及抗反射材料层260进行第一图案化工艺(first patterning process),以定义出第一保护层以及抗反射涂层。第一图案化工艺例

如是光学光刻工艺。

61.在一些实施例中,第一保护材料层270的材料例如是氧化硅、氮化硅、氮氧化硅、氮碳化硅、其他保护材料、或前述材料的组合。在一示例中,第一保护材料层270包含氧化硅,但本揭露并不以此为限。再者,第一保护材料层270可借由化学气相沉积(cvd)工艺、物理气相沉积(pvd)工艺、原子层沉积(ald)工艺、高密度电浆化学气相沉积(hdpcvd)工艺、或前述工艺的组合而形成。

62.如图2a所示,在一些实施例中,于抗反射材料层260上方形成第一保护材料层270之后,于第一保护材料层270上形成第一光刻胶材料层311,以及提供第一遮罩331于第一光刻胶材料层311的上方。

63.请参照图2b,接着,在一些实施例中,通过第一遮罩331对第一光刻胶材料层311(图2a)进行图案化,例如曝光和显影工艺,以将第一遮罩331的图案转移至第一光刻胶材料层311,而形成图案化第一光刻胶层31。

64.请参照图2c,接着,根据图案化第一光刻胶层31对下方的第一保护材料层270及抗反射材料层260进行图案化工艺,以形成第一保护层27以及抗反射涂层26,并暴露出导电层24的顶面24a的第一区域(first region)r1。在一些实施例中,例如是在同一道工艺中,根据第一保护材料层270及抗反射材料层260的材料选用适当的刻蚀气体而进行图案化工艺。

65.请参照图2d,之后,例如实施一灰化工艺(ashing process),以移除图案化第一光刻胶层31。

66.如图2d所示,在一些实施例中,在进行如图2c所示的图案化工艺之后,第一保护层27的内侧边缘27ei与抗反射涂层26的内侧边缘26ei大致上对齐(或共平面)。如图2d所示,此抗反射涂层26包含具有第一内径(first diameter)d1的第一开口(first opening)26p,第一保护层27包含具有第二内径(second diameter)d2的第二开口(second opening)27p。且抗反射涂层26的第一开口26p与第一保护层27的第二开口27p的位置相应于后续形成的接触垫区。在此示例中,第二开口27p与第一开口26p具有相同尺寸(/面积),且皆大于后续形成的接触垫区的开口尺寸(/面积)。

67.请参照图2e,接着,在一些实施例中,顺应性的沉积一第二保护材料层(second passivation material layer)280于第一保护层27上,且此第二保护材料层280沿着第一保护层27的内侧边缘27ei以及抗反射涂层26的内侧边缘26ei沉积,并覆盖导电层24的顶面24a所暴露出的第一区域r1。

68.在一些实施例中,第二保护材料层280的材料例如是氧化硅、氮化硅、氮氧化硅、氮碳化硅、其他保护材料、或前述材料的组合。第二保护材料层280可借由化学气相沉积(cvd)工艺、物理气相沉积(pvd)工艺、原子层沉积(ald)工艺、高密度电浆化学气相沉积(hdpcvd)工艺、或前述工艺的组合而形成。

69.再者,相较于第一保护材料层270,可以选择具有更高的阻挡水气能力的材料以形成第二保护材料层280。在一示例中,第二保护材料层280例如包含氮化硅,第一保护材料层270例如包含氧化硅,但本揭露并不限制于此。

70.之后,对第二保护材料层280进行第二图案化工艺(second patterning process),以形成第二保护层,并形成本揭露一些实施例的半导体结构的一接触垫区。

71.请参照图2f,在一些实施例中,于第二保护材料层280的上方形成一图案化第二光

刻胶层32。形成方法例如是,先在第二保护材料层280上形成第二光刻胶材料层(未示出),并提供第二遮罩332于第二光刻胶材料层的上方,之后以第二遮罩332对第二光刻胶材料层进行图案化,而形成此图案化第二光刻胶层32。为简化图式,图2f仅示出第二保护材料层280上方的图案化第二光刻胶层32及第二遮罩332。再者,于一些实施例中,第一遮罩331的图案可不同于第二遮罩332的图案。

72.请参照图2g,接着,在一些实施例中,对第二保护材料层进行第二图案化工艺(second patterning process),以形成第二保护层28,并暴露出导电层24的顶面24a的第二区域(second region)r2。一些实施例中,第二区域r2位于前述第一区域r1内并与第一区域r1重叠,且第二区域r2的面积小于第一区域r1。而此处形成的第二区域r2即为图1所示的本揭露一些实施例的半导体结构的一接触垫区rb。之后,例如实施一灰化工艺(ashing process),以移除图案化第二光刻胶层32。

73.如图2g所示,根据一些实施例,进行前述的第二图案化工艺之后,第二保护层28包含具有第三内径(third diameter)d3的第三开口28p。且此第三开口28p小于第一保护层27的第二开口27p,也小于抗反射涂层26的第一开口26p。再者,在一些实施例中,第二保护层28、第一保护层27及抗反射涂层26可形成一堆叠结构29,此堆叠结构29可暴露出导电层24的顶面24a的接触垫区,而此处形成的第三开口28p即为堆叠结构29所暴露出的导电层24的顶面24a的接触垫区rb。

74.一般来说,在半导体元件完成制作和封装后,需进行一系列的元件可靠度测试(reliability tests),例如高/低温操作寿命测试(high/low temperature operating life)、高温度高湿度测试等等多种相关测试,以模拟半导体元件于使用前(例如储存)和使用后在一定湿度和温度条件下的可靠度。

75.以加速式温湿度及偏压测试(temperature humidity bias test,thb)为例,其目的是评估元件产品在高温、高湿、偏压条件下对湿气的抵抗能力,加速其失效进程;其测试条件举例来说是在温度85℃和相对湿度85%的条件下,施加偏压1.1v

cc

,进行例如168小时、5000小时、1000小时的测试,以评价试样抵抗水气长期渗透的能力。

76.以高压加速温湿度及偏压测试(highly accelerated stress test,hast)为例,其目的是评估元件产品在偏压下高温、高湿、高气压条件下对湿度的抵抗能力,加速其失效进程;举例来说,其测试条件是在温度130℃、相对湿度85%和气压2.3atm的条件下,施加偏压1.1v

cc

,进行例如两次个别96小时,加总共192小时的hast测试。相较于thb测试,hast测试是在于100℃以上且是在高密度的水蒸气高压环境中进行的试验,hast利用试验槽内的水蒸气压力远远高于试样内部的水蒸气分压的特点,可加速水分侵入试样内部,以进行元件的封装密封性的评价。

77.如图2g所示的金属层24上方的抗反射涂层26,若受到水气侵入则容易被腐蚀,而可能在元件使用一段时间后材料变质及扩散至原形成位置之外。以氮化钛层作为抗反射涂层26为例,氮化钛在水气的侵扰之下,可能产生氮氧化钛(银色或银白色固体)。化学反应式如下。

78.2tin

(s)

4h2o

(g)

→

2tion

x(s)

2nh

3(g)

h

2(g)

79.若以电子显微镜进行细部检视,可以观察到析出而扩散开来的银色或银白色的氮氧化钛。

80.请同时参照图1和图2g。根据一些实施例,堆叠结构29中的抗反射涂层26直接接触导电层24,第一保护层27设置于抗反射涂层26上并直接接触抗反射涂层26的顶面26a。再者,第二保护层28直接接触并完全覆盖第一保护层27的顶面27a、第一保护层27的内侧边缘27ei以及抗反射涂层26的内侧边缘26ei。根据本揭露的一些实施例,借由形成双层的保护层,包括第一保护层27和第二保护层28,且第二保护层28更包覆第一保护层27以及抗反射涂层26的侧壁,可以有效防止水气自第二区域r2/接触垫区rb渗透进入抗反射涂层26而造成腐蚀,解决了传统半导体结构中因抗反射涂层26受水气腐蚀而变色、析出使整体结构产生的缺陷的问题。根据实际检验测试,根据本揭露一些实施例的半导体结构可以通过多项高温高湿度测试,包括上述的加速式温湿度及偏压测试(thb)以及高压加速温湿度及偏压测试(hast)。

81.在一些实施例中,第二保护层28可以与第一保护层27包含不同材料。例如,相较于第一保护层27,第二保护层28可包含具有更高的阻挡水气能力的材料。但本揭露并不限制于此。第二保护层28也可以与第一保护层27包含相同材料,例如都选用具有良好阻挡水气能力的相同材料进行保护层的制作。

82.再者,如图2g所示,上述第二保护层28覆盖第一保护层27的顶面27a的厚度为t1,第二保护层28覆盖第一保护层27的内侧边缘27ei以及抗反射涂层26的内侧边缘26ei的厚度为t2。于一些实施例中,厚度t2可以小于、或者大致上等于厚度t1,本揭露对此并不多做限制。第二保护层28覆盖第一保护层27及抗反射涂层26的厚度越厚,越可阻挡水气进入而腐蚀抗反射涂层26,厚度t2以不影响接触垫区rb所需的接触面积以及其他部件的设置为主。在一些实施例中,第二保护层28覆盖第一保护层27的内侧边缘27ei以及抗反射涂层26的内侧边缘26ei的厚度t2大于等于约3μm。在一些其他实施例中,此厚度t2大于等于约5μm。在一些其他实施例中,此厚度t2在约3μm~约8μm的范围。值得注意的是,前述厚度数值及/或范围仅为一部份示例的态样,本揭露并不仅限于前述数值及/或范围。

83.再者,本揭露的实施例的半导体结构亦可根据实际设计的条件需求而稍做修饰或变化。图3为根据本揭露的一些实施例的一种半导体结构的剖面示意图。图3与图2g中相同或类似的元件沿用相同或类似的标号,且为了简化说明,关于相同或类似于前述图示的部件及其形成工艺步骤,在此不再详述。

84.如图3所示,一些实施例中,在基底20上形成一晶体管21,且介电层22覆盖晶体管21。在此示例中,晶体管21例如包括了栅极g、位于栅极g与基底20之间的栅极介电层gd、形成于基底20中且分别位于栅极g两侧的源极s和漏极d。当然,图3中所绘示的晶体管21仅为其中一种示例,其他结构型态或/及更多数量的集成电路元件亦可应用于实施例的半导体结构中,本揭露对此并不多做限制。

85.再者,于介电层22的上方形成导电层24。在此示例中,导电层24包括多层导电结构,例如包括位于介电层22上方的第一导电层241、位于第一导电层241上方的第二导电层242、以及位于第二导电层242上方的第三导电层243。第一导电层241、第二导电层242以及第三导电层243包含铝(aluminum,al)、铜(copper,cu)、钛(titanium,ti)、氮化钛(titanium nitride,tin)、前述材料的组合、或其他类似材料。

86.如图3所示的半导体结构中,更包括如前述的堆叠结构29形成于第三导电层243上,且此堆叠结构29可暴露出导电层24的顶面24a的接触垫区。一些实施例中,堆叠结构29

自上到下依序包含第二保护层28、第一保护层27以及抗反射涂层26。其中,抗反射涂层26包含具有第一内径d1的第一开口26p,第一保护层27包含具有第二内径d2的第二开口27p,第二保护层28包含具有第三内径d3的第三开口28p。如图3所示,第二开口27p与第一开口26p具有大致相同的尺寸,而第三开口28p则小于第一保护层27的第二开口27p以及小于抗反射涂层26的第一开口26p。第三开口28p所暴露出的第三导电层243的顶面的区域r2即为本揭露一些实施例的半导体结构的一接触垫区(如图1所示的接触垫区rb)。再者,上述导电层24可电连接至晶体管21,而堆叠结构29所暴露出的导电层24(/第三导电层243)的顶面的接触垫区作为半导体结构的焊垫(bonding pad)而可与一导线(未示出)连接。

87.根据上述,根据本揭露一些实施例提出的半导体结构和形成方法具有许多优点。借由形成双层的保护层,例如包括上述的第一保护层27和第二保护层28,且第二保护层28更完全包覆第一保护层27及抗反射涂层26的侧壁,如图2g、图3所示的第二保护层28完全覆盖第一保护层27的内侧边缘27ei以及抗反射涂层26的内侧边缘26ei,以有效防止水气自第二区域r2/接触垫区rb渗透进入抗反射涂层26而造成抗反射涂层26的腐蚀,解决了传统半导体结构中因抗反射涂层26受水气腐蚀而变色、析出使整体结构产生的缺陷的问题,进而大幅提升制得半导体结构的电性表现以及可靠度。再者,本揭露的实施例所提出的半导体结构的形成方法,可以简单地完成半导体结构的制作,而且可以与现有工艺相容,并不会提升工艺复杂度或/及大幅增加生产成本,但又可明显提高制得半导体结构的电性表现以及可靠度。因此,本揭露实施例提出的半导体结构和形成方法极具应用价值。

88.虽然本发明已以数个较佳实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中技术人员在不脱离本发明的精神和范围内,当可作任意的更动与润饰,因此本发明的保护范围当视权利要求所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。